Professional Documents

Culture Documents

High Speed PCB

Uploaded by

Sandip Paul0 ratings0% found this document useful (0 votes)

13 views1 pageAll byte lanes should be the same length to control impedance and minimize noise, with a solid reference plane and no vias. The data group must be separated from other signals by at least five times the trace width. Dielectric losses from signal energy absorption can be reduced using materials with lower loss tangents or dissipation factors.

Original Description:

Original Title

high speed pcb

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentAll byte lanes should be the same length to control impedance and minimize noise, with a solid reference plane and no vias. The data group must be separated from other signals by at least five times the trace width. Dielectric losses from signal energy absorption can be reduced using materials with lower loss tangents or dissipation factors.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

13 views1 pageHigh Speed PCB

Uploaded by

Sandip PaulAll byte lanes should be the same length to control impedance and minimize noise, with a solid reference plane and no vias. The data group must be separated from other signals by at least five times the trace width. Dielectric losses from signal energy absorption can be reduced using materials with lower loss tangents or dissipation factors.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 1

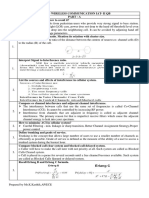

Guidelines for High speed Flex PCB

• All byte lanes should be of the same length to each other. It is

also important that the board designer provide these signals

with a solid reference plane to control the characteristic

impedance and have a smaller loop area between the signals

and the return currents. Preferably, no vias should be used on

these signals, avoiding additional capacitive loading.

• The data group must be kept away from all other groups by at

least five times the trace width.

• Dielectric losses result from molecular vibrations of the

dielectric near the conductors carrying electrons. These cause

some of the energy of the electrons to be absorbed by the

dielectric, producing attenuation. These losses can be reduced

by using advanced materials with lower loss tangents or

dissipation factor.

• Because the address/command group is captured by the

memory clock, they must also maintain a length relationship

with the CKs, depending on the application.

You might also like

- It Is Quite Another Electricity: Transmitting by One Wire and Without GroundingFrom EverandIt Is Quite Another Electricity: Transmitting by One Wire and Without GroundingRating: 4.5 out of 5 stars4.5/5 (2)

- EMC Printed Circuit Board PCB TipsDocument6 pagesEMC Printed Circuit Board PCB TipsCarlos TrustNo ratings yet

- EMC Design and Interconnection Techniques: Cable Routing and ConnectionDocument27 pagesEMC Design and Interconnection Techniques: Cable Routing and ConnectionMurali MohanNo ratings yet

- Transmission Line and SubstationDocument76 pagesTransmission Line and SubstationAyman MustafaNo ratings yet

- High Frequency PCB LayoutDocument26 pagesHigh Frequency PCB LayoutJaime Sebastian CardenasNo ratings yet

- EMC Design Considerations - ArticleDocument4 pagesEMC Design Considerations - Articlethangaraj_icNo ratings yet

- EMI EMC PT 4Document62 pagesEMI EMC PT 4Vishu VishwajaNo ratings yet

- Adss Cables For High Voltage InstallationsDocument4 pagesAdss Cables For High Voltage Installations199311056No ratings yet

- Pin AssignmentDocument39 pagesPin AssignmentDebdatta PraharajNo ratings yet

- Micrel PCB Design ConsiderationsDocument0 pagesMicrel PCB Design Considerationstomscribd18No ratings yet

- Clock Generation and DistributionDocument57 pagesClock Generation and Distributionmanohar487100% (1)

- Protection SchemesDocument20 pagesProtection SchemesMohamed Wahid100% (1)

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsFrom EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsNo ratings yet

- RF PCB DesignDocument47 pagesRF PCB DesignMahima ArrawatiaNo ratings yet

- EHVHV Cable Sheath EarthingDocument11 pagesEHVHV Cable Sheath EarthingJignesh Parmar100% (1)

- How To Avoid EMC Problems in PCB DesignDocument16 pagesHow To Avoid EMC Problems in PCB DesignChaitali Choudhary100% (1)

- Sheath Bonding Design Guide For High Voltage Cables - ELEK SoftwareDocument1 pageSheath Bonding Design Guide For High Voltage Cables - ELEK SoftwareKamila WehbeNo ratings yet

- EC8652 WC III YEAR ECE IAT2 QB Ans PartialDocument12 pagesEC8652 WC III YEAR ECE IAT2 QB Ans PartialkkarthikecNo ratings yet

- Gigabit Ethernet Design Guide: Author: Kiet Tran Microchip Technology IncDocument13 pagesGigabit Ethernet Design Guide: Author: Kiet Tran Microchip Technology IncLarbi BelazizNo ratings yet

- Design and Implementation of VLSI Systems InterconnectDocument49 pagesDesign and Implementation of VLSI Systems InterconnectĐàm PhượngNo ratings yet

- Chip IO Circuit Design - Input Ouput CircuitryDocument9 pagesChip IO Circuit Design - Input Ouput CircuitryVăn CôngNo ratings yet

- Lower-Power: LayoutDocument11 pagesLower-Power: LayoutmturadagiNo ratings yet

- Distributed-Element Circuit PDFDocument16 pagesDistributed-Element Circuit PDFahmedNo ratings yet

- Lectrure 5.microstrip AntennasDocument57 pagesLectrure 5.microstrip AntennasSśēmǾǿ Ŕämáďañ100% (1)

- Low Power Vlsi Design: Assignment-1 G Abhishek Kumar Reddy, M Manoj VarmaDocument17 pagesLow Power Vlsi Design: Assignment-1 G Abhishek Kumar Reddy, M Manoj VarmamanojNo ratings yet

- 8.my RecentDocument53 pages8.my RecentRaoNo ratings yet

- 22 - EEE - 2023 - Underground CablesDocument16 pages22 - EEE - 2023 - Underground CablesAmbadiNo ratings yet

- Ehv Bonding CableDocument9 pagesEhv Bonding CablemazzoffaNo ratings yet

- Lecture 2A: - Bernhard (Chapter 2)Document28 pagesLecture 2A: - Bernhard (Chapter 2)meoconhs2612No ratings yet

- EMI-EMC Engineering TipsDocument6 pagesEMI-EMC Engineering TipsAbdullah RafiqueNo ratings yet

- Data Communication Media: Chapter - 2Document4 pagesData Communication Media: Chapter - 2lvsaruNo ratings yet

- Power Transmission Over Long Distances With CablesDocument8 pagesPower Transmission Over Long Distances With CablesramsesiNo ratings yet

- Module 2 - Microwave Passive DevicesDocument25 pagesModule 2 - Microwave Passive DevicessudarshanNo ratings yet

- EC202Document7 pagesEC202razuNo ratings yet

- Overview of GSM Cellular Network and OperationsDocument90 pagesOverview of GSM Cellular Network and OperationsscribdmithunNo ratings yet

- Wireless Sensor NetworksDocument32 pagesWireless Sensor NetworksSumeet ChauhanNo ratings yet

- Low Power Design LimitsDocument10 pagesLow Power Design LimitsMy NameNo ratings yet

- Gate Driver PDFDocument3 pagesGate Driver PDFMarcel BlinduNo ratings yet

- Wave GuidesDocument21 pagesWave GuidesJerryNo ratings yet

- How To Solve Electrical Ground Loop ProblemsDocument5 pagesHow To Solve Electrical Ground Loop ProblemsVraja KisoriNo ratings yet

- Ti80 0011 Emv Gerechte Installation Von Nord Komponenten en 3917 ScreenDocument8 pagesTi80 0011 Emv Gerechte Installation Von Nord Komponenten en 3917 Screenolivier.bigouretNo ratings yet

- Grund - Et - Al. 2019 Jicable Proceedings C3 6 Integral Sensing of HV Cable JointsDocument6 pagesGrund - Et - Al. 2019 Jicable Proceedings C3 6 Integral Sensing of HV Cable Jointsatif_aman123No ratings yet

- CDMA Solutions: Smart Antenna Technology: Wei-Chiang WuDocument53 pagesCDMA Solutions: Smart Antenna Technology: Wei-Chiang WuMohammedKhalifaNo ratings yet

- Low-Pro Le Antennas and Personal Communication Antennas - NewDocument20 pagesLow-Pro Le Antennas and Personal Communication Antennas - NewabdalazizNo ratings yet

- College of Engineering Trivandrum: Seminar On Reconfigurable CircuitDocument18 pagesCollege of Engineering Trivandrum: Seminar On Reconfigurable Circuitujjawal singhNo ratings yet

- IoT WSN Module 5 2018 by Prof SV 1 PDFDocument43 pagesIoT WSN Module 5 2018 by Prof SV 1 PDFmanju0071No ratings yet

- IoT WSN Module 5 2018 by Prof SV 1 PDFDocument43 pagesIoT WSN Module 5 2018 by Prof SV 1 PDFmanju0071No ratings yet

- IoT & WSN - Module 5 - 2018 by Prof - SVDocument43 pagesIoT & WSN - Module 5 - 2018 by Prof - SVVignesh MJ83% (6)

- Mod5 Transport LayerDocument27 pagesMod5 Transport Layerbronzeboy737No ratings yet

- High Speed PCB Design Guidelines You Must KnowDocument30 pagesHigh Speed PCB Design Guidelines You Must KnowjackNo ratings yet

- Handout 04Document32 pagesHandout 04Shivam GaunsNo ratings yet

- EC5401 - TLWG - Unit 5Document42 pagesEC5401 - TLWG - Unit 5GeethakshayaNo ratings yet

- Performance Enhancement by Bidirectional Buffer Insertion in Vlsi InterconnectsDocument9 pagesPerformance Enhancement by Bidirectional Buffer Insertion in Vlsi Interconnectsrajnid_1No ratings yet

- An Introduction To Test CablesDocument5 pagesAn Introduction To Test CablesArun KumarNo ratings yet

- Session - 3 - Transmission LinesDocument73 pagesSession - 3 - Transmission LineseshanraoNo ratings yet

- 3.2 Uee2521 RRPDocument54 pages3.2 Uee2521 RRPmohammad2110959No ratings yet

- Tanjila 08 11 2017Document19 pagesTanjila 08 11 2017Wondale KebedeNo ratings yet

- Functions of Image PlanesDocument5 pagesFunctions of Image PlanesSanket PatilNo ratings yet

- Automated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsFrom EverandAutomated Broad and Narrow Band Impedance Matching for RF and Microwave CircuitsNo ratings yet