Professional Documents

Culture Documents

Difference Between SRAM DRAM

Uploaded by

Sneha Pal0 ratings0% found this document useful (0 votes)

65 views2 pagesEach cell which can store a single bit requires six transistors. 3. Does not need to be refreshed periodically as flips flops retain the data. 4. Faster access time compared to DRAM, therefore used as caches mostly. 5. Low density / less memory per chip due to more circuitry capacitor leaks. 6. Less costly than SRAM because of high chip density and because of simple required for a single cell.

Original Description:

Original Title

24831338 Difference Between SRAM DRAM

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentEach cell which can store a single bit requires six transistors. 3. Does not need to be refreshed periodically as flips flops retain the data. 4. Faster access time compared to DRAM, therefore used as caches mostly. 5. Low density / less memory per chip due to more circuitry capacitor leaks. 6. Less costly than SRAM because of high chip density and because of simple required for a single cell.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

65 views2 pagesDifference Between SRAM DRAM

Uploaded by

Sneha PalEach cell which can store a single bit requires six transistors. 3. Does not need to be refreshed periodically as flips flops retain the data. 4. Faster access time compared to DRAM, therefore used as caches mostly. 5. Low density / less memory per chip due to more circuitry capacitor leaks. 6. Less costly than SRAM because of high chip density and because of simple required for a single cell.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 2

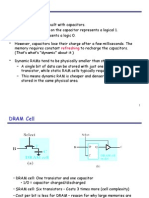

Difference between Static RAM & Dynamic RAM

SRAM DRAM

1. Stores bits in memory cells 1. Memory cells are composed of

composed of flip flops. capacitors and transistors.

2. Each cell which can store a 2. Each cell requires a capacitor

single bit requires six (which stores bit as charge) & a

transistors. transistor.

3. Does not need to be refreshed 3. Needs to be refreshed every

periodically as flips flops retain few milliseconds to retain data

the data. because the charge of the

4. Faster access time compared to capacitor leaks.

DRAM, therefore used as caches 4. Slower access time compared to

mostly. SRAM as it cannot be read while

5. Low density/less memory per being refreshed.

chip due to more circuitry 5. High chip density/more memory

required for a single cell. per chip compared to SRAM due

6. More power consumption than to less circuitry for a single cell.

DRAM because of low chip 6. Less power consumption than

density. SRAM because of simple

7. More costly in terms of cost per circuitry.

bit compared to DRAM due to 7. Less costly than SRAM because

low chip density. of high chip density and

therefore used as main memory

in PCs.

You might also like

- Difference Between SRAM & DRAMDocument2 pagesDifference Between SRAM & DRAMmy_scribd_docs90% (21)

- Difference Between Static RAM & Dynamic RAM: Sram DramDocument1 pageDifference Between Static RAM & Dynamic RAM: Sram DramYogesh Kumar DewanganNo ratings yet

- Difference Between Static RAM & Dynamic RAM: Sram DramDocument4 pagesDifference Between Static RAM & Dynamic RAM: Sram Dramamol maliNo ratings yet

- What Is A Neural Network?Document3 pagesWhat Is A Neural Network?Abhisek SarkarNo ratings yet

- SRAM and DRAMDocument2 pagesSRAM and DRAMBiju AngaleesNo ratings yet

- Computer Memory Is A Temporary Storage AreaDocument3 pagesComputer Memory Is A Temporary Storage AreaMilitary BaseNo ratings yet

- Group ReportDocument10 pagesGroup ReportDK SevenNo ratings yet

- Random Access MemoryDocument37 pagesRandom Access MemorysalmanabkpNo ratings yet

- Coa Unit-4Document27 pagesCoa Unit-4singhshiva8082No ratings yet

- Lecture 15Document19 pagesLecture 157t854s6wd2No ratings yet

- 14-RAM&ROM - Dynamic Memory Is Built With Capacitors. A Stored Charge On The Capacitor Represents A Logical 1. No Charge Represents A Logic 0.Document8 pages14-RAM&ROM - Dynamic Memory Is Built With Capacitors. A Stored Charge On The Capacitor Represents A Logical 1. No Charge Represents A Logic 0.Nava KrishnanNo ratings yet

- 20BSCS010 Presentation of Types of RamDocument18 pages20BSCS010 Presentation of Types of RamAmeer JaanNo ratings yet

- Memory Related To VLSIDocument63 pagesMemory Related To VLSIIndrajeet GautamNo ratings yet

- UNIT 2 Managing Storage DevicesDocument34 pagesUNIT 2 Managing Storage Devicesprashantkumarmuz2004No ratings yet

- Chapter (4) Upgrading MemoryDocument80 pagesChapter (4) Upgrading MemoryGame TekaNo ratings yet

- What Are The Differences Between SRAM and Dram?Document1 pageWhat Are The Differences Between SRAM and Dram?yaheewNo ratings yet

- Unit 5 Memory OrganizationDocument104 pagesUnit 5 Memory OrganizationNarsingh Pal YadavNo ratings yet

- Random Access MemoryDocument8 pagesRandom Access MemoryTuan Anh NguyenNo ratings yet

- How RAM Works 28 by NafeesDocument10 pagesHow RAM Works 28 by NafeesnafeesNo ratings yet

- E2805 B 43Document4 pagesE2805 B 43Verma JagdeepNo ratings yet

- Ca Unit 5 PrabuDocument37 pagesCa Unit 5 Prabu6109 Sathish Kumar JNo ratings yet

- How RAM WorksDocument9 pagesHow RAM WorksPablo Miguel FelsteadNo ratings yet

- Difference Between Static and Dynamic RAMDocument2 pagesDifference Between Static and Dynamic RAMMamun RassalNo ratings yet

- Ram & Rom: Random Access MemoryDocument3 pagesRam & Rom: Random Access MemoryRudra ShrikumarNo ratings yet

- "Memory Interface" in (Microprocessor Systems and Interfacing)Document22 pages"Memory Interface" in (Microprocessor Systems and Interfacing)MUHAMMAD ABDULLAHNo ratings yet

- Chapter 4 Memory ElementDocument87 pagesChapter 4 Memory ElementWann FarieraNo ratings yet

- Computer Hardware Image GalleryDocument7 pagesComputer Hardware Image Gallerymathur1995No ratings yet

- "Memory Interface" in (Microprocessor and Assembly Language)Document22 pages"Memory Interface" in (Microprocessor and Assembly Language)MUHAMMAD ABDULLAHNo ratings yet

- Types of RAMDocument2 pagesTypes of RAMAdrian BarrenoNo ratings yet

- Primary MemoryDocument20 pagesPrimary MemoryAayushmanNo ratings yet

- Chapter 2Document66 pagesChapter 2mayazyounasNo ratings yet

- Computer Memory2Document8 pagesComputer Memory2Rajeev DebnathNo ratings yet

- Capter 10Document35 pagesCapter 10Roha CbcNo ratings yet

- Dram VS SramDocument2 pagesDram VS SramEvan SubediNo ratings yet

- RAMDocument9 pagesRAMSourin SahaNo ratings yet

- Different Types of MemoryDocument34 pagesDifferent Types of MemoryPirapuraj PonnampalamNo ratings yet

- SRAM&DRAMDocument8 pagesSRAM&DRAMSayan SarkarNo ratings yet

- EC304Document14 pagesEC304api-3853441No ratings yet

- Semiconductor Memory DesignDocument27 pagesSemiconductor Memory Designkavita_1992No ratings yet

- Memory OrganizationDocument70 pagesMemory OrganizationrahqansayeedNo ratings yet

- Piyush PPT of ZRAMDocument16 pagesPiyush PPT of ZRAMPiyush SharmaNo ratings yet

- Memory DevicesDocument20 pagesMemory DevicesMD AZIZUL HOQUENo ratings yet

- Ram TypesDocument23 pagesRam TypesرمقالحياةNo ratings yet

- Microsoft Office Word Document جديد (3) Document3 pagesMicrosoft Office Word Document جديد (3) anon_21074691No ratings yet

- 04 - Internal Memory - StudDocument17 pages04 - Internal Memory - Studtipu tipuNo ratings yet

- William Stallings Computer Organization and Architecture 7th Edition Internal MemoryDocument37 pagesWilliam Stallings Computer Organization and Architecture 7th Edition Internal Memoryagustin92No ratings yet

- RAM & Its TypesDocument4 pagesRAM & Its TypesdoferiNo ratings yet

- Volatile Memory - WikipediaDocument5 pagesVolatile Memory - WikipediaAhmed IlyasNo ratings yet

- MemoryDocument87 pagesMemoryrajkumarNo ratings yet

- Reading Practice A. Read The Following Text: Computer - MemoryDocument6 pagesReading Practice A. Read The Following Text: Computer - MemoryMiele Jm-No ratings yet

- Random Access MemoryDocument2 pagesRandom Access MemoryジョージNo ratings yet

- Computer Assignment 1Document6 pagesComputer Assignment 1Muhammad Hassnain AhmadNo ratings yet

- Memory Hierarchy Levels: Block (Aka Line) : Unit of Copying If Accessed Data Is Present in Upper LevelDocument16 pagesMemory Hierarchy Levels: Block (Aka Line) : Unit of Copying If Accessed Data Is Present in Upper LevelalexNo ratings yet

- Types of MemoryDocument14 pagesTypes of MemorySriram RamakrishnanNo ratings yet

- Presentation1 LOCDocument10 pagesPresentation1 LOCanjliNo ratings yet

- Assignment: Embedded SystemsDocument6 pagesAssignment: Embedded SystemsSudarshanNo ratings yet

- Sram Memory Cell: By:-Udit Shah & Rajdeep KandiyalDocument13 pagesSram Memory Cell: By:-Udit Shah & Rajdeep KandiyalSrasVelNo ratings yet

- Building HPE Gen10 Memory CFG 22MAY2019Document78 pagesBuilding HPE Gen10 Memory CFG 22MAY2019Guillermo García GándaraNo ratings yet

- Non Volatile Random Access MemoryDocument4 pagesNon Volatile Random Access MemoryDhanssekaNo ratings yet

- Storage Systems: Organization, Performance, Coding, Reliability, and Their Data ProcessingFrom EverandStorage Systems: Organization, Performance, Coding, Reliability, and Their Data ProcessingNo ratings yet