Professional Documents

Culture Documents

BJT

Uploaded by

Mohd Nasrul Shafiq MnsOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BJT

Uploaded by

Mohd Nasrul Shafiq MnsCopyright:

Available Formats

6.

012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-1

Lecture 21 - Multistage Ampliers (I) Multistage Amplifiers November 22, 2005 Contents: 1. Introduction 2. CMOS multistage voltage amplier 3. BiCMOS multistage voltage amplier 4. BiCMOS current buer 5. Coupling amplier stages Reading assignment: Howe and Sodini, Ch. 9, 9.1-9.3

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-2

Key questions

How can one build a wide range of high-performance ampliers using the single-transistor stages studied so far? What are the most important considerations when assembling mulstistage ampliers: regarding interstage loading?

regarding interstage biasing?

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-3

1. Introduction Amplier requirements are often demanding: must adapt to specic kinds of signal source and load,

must deliver sucient gain Single-transistor amplier stages are very limited in what they can accomplish multistage amplier.

VDD

signal source RS + vs vOUT VS VSS signal load RL

Issues: What amplifying stages should be used and in what order? What devices should be used, BJT or MOSFET?

How is biasing to be done?

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-4

2 Summary of single stage characteristics:

stage Avo , Gmo , Aio Rin Rout key function

CS

Gmo = gm

gm gm +gmb

1 gm +gmb

ro //roc

1 gm +gmb

transcond. amp.

CD

Avo

voltage buer

CG

Aio

roc //[ro (1 + gm RS )]

current buer

CE

Gmo

gm

ro //roc

1 gm RS

transcond. amp.

CC

Avo

r + (ro //roc //RL )

voltage buer

CB

Aio

1 gm

roc //{ro [1 + gm (r //RS )]} current buer

2 Key dierences between BJTs and MOSFETs: BJT C IB = I gm = ro =

qIC kT VA IC

MOSFET IG = 0 > gm = 2 W CoxID L > ro =

1 ID

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-5

2. CMOS multistage voltage amplier

2 Goals: high voltage gain high Rin low Rout 2 Good starting point: CS stage

RS

+ + + -

ro//roc

+

vs

vin

-

-gm(ro//roc)vin

vout

-

RL

Rin = Avo = gm(ro //roc ), probably insucient Rout = ro//roc, too high

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-6

2 Add second CS stage to get more gain:

RS

+ + + -

ro1//roc1

+

ro2//roc2

+ + -

vs

vin1

-

-gm1(ro1//roc1)vin1 vout1=vin2

-

-gm2(ro2//roc2)vin2 vout2

-

RL

Rin = Avo = gm1(ro1 //roc1 )gm2 (ro2 //roc2 ) but Rout = ro2//roc2 , still high 2 Add CD stage at output:

RS + vs + vin CS CS + Avovin ro2 roc2 + vin3 CD + v 1 gm3 + gmb3 + vout gm3 in3 gm3 + gmb3 RL

Rin =

m3 Avo = gm1(ro1 //roc1 )gm2 (ro2 //roc2 ) gm3g+g mb3

, still high

Rout =

1 , gm3 +gmb3

now small

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-7

3. BiCMOS multistage voltage amplier

2 Avo (CE) > Avo (CS) because ro(BJ T ) > ro(M OSF ET )

and gm (BJ T ) > gm(M OSF ET ) but...

CS stage is best rst stage, since Rin = .

2 Add CE stage following CS stage?

RS + vs + vin1 CS + Avo1vin1 ro1 roc1 + vin2 CE ro2 roc2 + r2 + Avo2vin2 vout RL

Trouble is interstage loading degrades gain: Rout1 = ro1 //roc1 Rin2 = r2 Voltage divider between stages: r2 Rin2 = Rout1 + Rin2 ro1 //roc1 + r2 r2 ro1 //roc1 1

Additional gain provided by CE stage more than lost in interstage loading.

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-8

2 Use two CS stages, but add CC stage at output:

RS + vs + vin CS CS CC + Avo1Avo2vin ro2 roc2 + vin3 ro2 roc2 1 gm3 + 3 + r3 + 3(ro3 roc3 RL) + vin3 vout RL

Interstage loading: Rout2 = ro2//roc2 , Rin3 = r3 + 3(ro3 //roc3 //RL) Then, interstage loss: r3 + 3(ro3 //roc3 //RL ) Rin3 =

Rout2 + Rin3 ro2 //roc2 + r3 + 3(ro3 //roc3 //RL) better than trying to use a CE stage, but still pretty bad. Benet is that Rout has improved: Rout = Rout3 = 1 gm3 Rout2 1 ro2 //roc2 + = + 3 gm3 3

Since, in general, gm (BJ T ) > gm (M OSF ET ), Rout could be better than CD output stage if ro2//roc2 is not too large. Otherwise, CD stage output is better.

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-9

2 Better voltage buer: cascade CC and CD output stages. What is best order? Since Rin(CD) = , best to place CD rst:

RS + vs + vin CS CS + ro2 roc2 + Avo1Avo2vin vin3 + vin3 1 gm3 + gmb3 + vin4 CD CC r4 + 4(RL ro4 roc4) 1 1 gm4 + (g + g ) 4 m3 mb3 + + vin4 vout RL

Interstage loading: Rin3 =1 Rout2 + Rin3 Rin4 = Rout3 + Rin4 r4 + 4(ro4 //roc4 //RL) 1 + r4 + 4(ro4//roc4 //RL ) gm3 +g

mb3

and excellent output resistance: Rout = Rout4 = 1 gm4 + 1 1 Rout3 = + 4 gm4 4(gm3 + gmb3 )

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-10

4. BiCMOS current buer

2 Goals: Unity current gain very low Rin very high Rout Start with common-base stage:

iin iout

is

RS

1/gm

-iin

roc//(ro)

RL

Aio = 1 Rin =

1 gm

Rout = roc//{ro [1 + gm(r //RS )]}

Note that if RS is not too low, Rout roc //(ro).

Can we further increase Rout by adding a second CB stage?

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-11

2 CB-CB current buer:

iin1 iin2 iout

is

RS

1 gm1

iin1

1ro1 roc1

1 gm2

iin2

RL

CB

CB [ gm2ro2(r2 1ro1 roc1)] roc2

Now Rout = Rout2 = roc2 //{ro2 [1 + gm2 (r2 //Rout1 )]} Plugging in Rout1 roc1//(1 ro1 ),

Rout = roc2//{ro2 [1 + gm2 (r2 //roc1 //1 ro1)]} But, since r2 Rout roc1 //(1 ro1), then roc2 //(2ro2 )

roc2 //[ro2 (1 + gm2r2 )]

Did not improve anything! The base current limits the number improve number of CB stages that improve Rout to just one. Since CG stage has no gate current, cascade it behind CB stage.

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-12

2 CB-CG current buer:

iin1 iin2 iout

is

RS

1 gm1

iin1

1ro1 roc1

1 gm2

iin2

RL

CB

CG [gm2ro2(1ro1 roc1)] roc2

Rout = Rout2 = roc2//[ro2 (1 + gm2 Rout1 )] with Rout1 roc1 //(1 ro1), Rout = roc2 //[ro2 gm2 (roc1 //1ro1 )] Now Rout has improved by about gm2ro2 , but only to the extent that roc2 is high enough...

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-13

5. Coupling amplier stages

2 Capacitive coupling Capacitors of large enough value behave as AC short, so

signal goes through but bias is independent for each stage.

Example, CD-CC voltage buer:

5.0 V 5.0 V

4.0 V 2.5 V ISUP1

3.2 V 2.5 V ISUP2 Assumes VBE = 0.7 V VGS = 1.5 V

Advantages: can select bias point for optimum operation can select bias point close to middle of rails for maximum signal swing Disadvantages:

to approximate AC short, need large capacitors that consume signicant area

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-14

2 Direct coupling: share bias points across stages. Example, CD-CC voltage buer:

5.0 V 5.0 V

4.7 V

3.2 V 2.5 V ISUP1 ISUP2 Assumes VBE = 0.7 V VGS = 1.5 V

Advantages: no capacitors: compact Disadvantages: bias point shared: constrains design

bias shifts from stage to stage and can stray too far from center of range

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-15

Solution: use PMOS CD stage:

5.0 V ISUP1 5.0 V

3.2 V 2.5 V ISUP2 Assumes VBE = 0.7 V VGS = 1.5 V

1.7 V

Trade-o: gm(PMOS)< gm (NMOS) higher Rout In BiCMOS voltage amplier: Rout = 1 gm4 1

+ 4(gm3 + gmb3 )

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-16

2 Summary of DC shifts through amplier stages:

Transistor Type NMOS V+ iSUP Common Source/ Common Emitter (CS/CE ) OUT IN iSUP V V+ iSUP Common Gate/ Common Base (CG/CB) IN V V+ IN Common Drain/ Common Collector (CD/CC ) iSUP OUT OUT IN iSUP V V iSUP V V OUT OUT OUT iSUP V V+ IN OUT IN IN V V+ iSUP OUT iSUP V V+ OUT V V+ IN iSUP V V+ IN iSUP OUT IN OUT iSUP V V+ IN IN OUT PMOS V+ npn V+ pnp V+

Amplifier Type

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-17

Important dierence in bias shift between stages in BJT and MOSFET amps: In BJT (for npn): VBE VBE,on

rather independent of transistor size and current level.

In MOSFET (for nMOSFET): VGS = VT +

2ID L nCox W

Can be engineered through bias current and transistor geometry.

5.0 V 5.0 V

4.7 V

3.2 V 2.5 V ISUP1 ISUP2 Assumes VBE = 0.7 V VGS = 1.5 V

6.012 - Microelectronic Devices and Circuits - Fall 2005

Lecture 21-18

Key conclusions

To achieve amplier design goals, several stages often needed. In multistage ampliers, dierent stages used to accomplish dierent goals: voltage gain: common-source, common emitter

voltage buer: common-drain, common collector

current buer: common-gate, common base In multistage ampliers must pay attention to interstage loading to avoid unnecessary losses. In direct-coupled ampliers, bias is shared between adjoining stages: must select compromise bias, must pay attention to bias shift from stage to stage.

You might also like

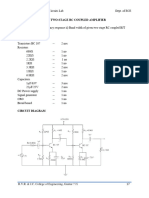

- Two StageDocument6 pagesTwo StageSiphosethuSidloyiNo ratings yet

- Lecture 20 Transistor Amplifiers (II) : Other Amplifier Stages November 17, 2005Document20 pagesLecture 20 Transistor Amplifiers (II) : Other Amplifier Stages November 17, 2005srabon1059No ratings yet

- Chap05 (7 5 06)Document60 pagesChap05 (7 5 06)Amar NathNo ratings yet

- Multistage Amplifiers: Bipolar Junction Transistor: MosfetDocument16 pagesMultistage Amplifiers: Bipolar Junction Transistor: MosfetRomelDianonNo ratings yet

- CMOS Cascode Transconductance Amplifier: Basic TopologyDocument10 pagesCMOS Cascode Transconductance Amplifier: Basic TopologyPriyantanuNo ratings yet

- Lec 21Document18 pagesLec 21Edwin HapsahNo ratings yet

- Ecen 607 CMFB-2011Document44 pagesEcen 607 CMFB-2011Girish K NathNo ratings yet

- ENG 571 - Lecture - Notes - Weeks - 10 - 11Document23 pagesENG 571 - Lecture - Notes - Weeks - 10 - 11Md. Atiqul Haque ,160021010No ratings yet

- Lecture21 Multistage AmplifiersDocument10 pagesLecture21 Multistage AmplifierscitraumariNo ratings yet

- Two Stage Opamp BerkeleyDocument25 pagesTwo Stage Opamp BerkeleyCircuit CruzNo ratings yet

- Switched Capacitor 2898320923Document36 pagesSwitched Capacitor 2898320923pardeep184No ratings yet

- ADC Pipeline LectureDocument29 pagesADC Pipeline LectureInJune YeoNo ratings yet

- Devices and Circuits Ii: Lecture GoalsDocument4 pagesDevices and Circuits Ii: Lecture GoalsMạnh Cường TrầnNo ratings yet

- Cmos Delay TimeDocument17 pagesCmos Delay TimeCuong LaidangNo ratings yet

- Euler's PathDocument10 pagesEuler's PathSatish Kumar0% (1)

- 2019S Lec Ch9 CascodeStage&CurrentMirrors RevDocument29 pages2019S Lec Ch9 CascodeStage&CurrentMirrors Revp.비둘기폴더의비밀No ratings yet

- 2.diode Clipper and ClamperDocument12 pages2.diode Clipper and ClamperMounika AllagaddaNo ratings yet

- Summary Last Lecture - Continuous-Time Filters (Continued)Document32 pagesSummary Last Lecture - Continuous-Time Filters (Continued)Jo KontNo ratings yet

- Lecture 17 - Linear Amplifier Basics - Outline: - AnnouncementsDocument14 pagesLecture 17 - Linear Amplifier Basics - Outline: - Announcementsishanksinghthandi100% (2)

- NPN BJT Amplifier Stages: Common-Emitter (CE) : EE 105 Spring 2000 Week 11, Lecture 25Document9 pagesNPN BJT Amplifier Stages: Common-Emitter (CE) : EE 105 Spring 2000 Week 11, Lecture 25nathan_siva8833No ratings yet

- Chapter-10 OP CircuitsDocument78 pagesChapter-10 OP CircuitsDebo LafuenteNo ratings yet

- MIT6 012S09 Ex03 Final 07Document18 pagesMIT6 012S09 Ex03 Final 07Gopi KrishnaNo ratings yet

- Cmos Inverter CharacterizationDocument54 pagesCmos Inverter CharacterizationVivekNo ratings yet

- Lesson 4 - RL RS EffectDocument35 pagesLesson 4 - RL RS EffectditmemayNo ratings yet

- Linear Wave Shaping: Department of Electronics and Communication EngineeringDocument0 pagesLinear Wave Shaping: Department of Electronics and Communication EngineeringanishadandaNo ratings yet

- 05 BJT-Amplifiers PDFDocument40 pages05 BJT-Amplifiers PDFMd ArifNo ratings yet

- SC IntegratorsDocument13 pagesSC Integratorsguitarfrido100% (1)

- Chapter06-2UP (4 23 02)Document79 pagesChapter06-2UP (4 23 02)Nelor Jane Robles LagunaNo ratings yet

- EE42 100 Wb-Lecture19 080713-FDocument37 pagesEE42 100 Wb-Lecture19 080713-FozanistzNo ratings yet

- Low-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationDocument4 pagesLow-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationwhamcNo ratings yet

- Designing of Combinational Logic Gates in Cmos: G.Susmitha Roll No:06Document49 pagesDesigning of Combinational Logic Gates in Cmos: G.Susmitha Roll No:06kumarbsnspNo ratings yet

- LIC Lab ManualDocument89 pagesLIC Lab ManualTAMILAN XEROX VtmNo ratings yet

- Bicmos Logic GatesDocument25 pagesBicmos Logic GatesRavi Chandra KumarNo ratings yet

- 689 Track HoldDocument35 pages689 Track HoldShiva KumarNo ratings yet

- Cascode AmplifierDocument6 pagesCascode AmplifierRajesh NatarajanNo ratings yet

- L060 Push Pull (2UP)Document10 pagesL060 Push Pull (2UP)srikanthkmsNo ratings yet

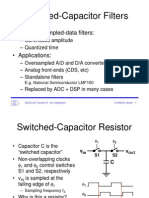

- Switched-Capacitor Filters: - "Analog" Sampled-Data FiltersDocument24 pagesSwitched-Capacitor Filters: - "Analog" Sampled-Data FiltersPushpendra DwivediNo ratings yet

- EEEB273 N05 - Diff Amp BJT x6 PDFDocument7 pagesEEEB273 N05 - Diff Amp BJT x6 PDFNur AdhiraaNo ratings yet

- AIC Sample ProblemsDocument3 pagesAIC Sample Problemsruchi0690No ratings yet

- Logic Gates: Power and Other Logic FamilyDocument36 pagesLogic Gates: Power and Other Logic FamilybhawnaNo ratings yet

- Low Power CMOS AD ConvertersDocument53 pagesLow Power CMOS AD ConvertersguitarfridoNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument78 pagesDigital Integrated Circuits: A Design Perspectiveapi-127299018No ratings yet

- Multi Stage Transistero AmplifierDocument7 pagesMulti Stage Transistero Amplifierkaran007_mNo ratings yet

- 10.two Stage RCDocument4 pages10.two Stage RCShivaNo ratings yet

- Differential and Multistage AmplifiersDocument85 pagesDifferential and Multistage AmplifiersShino JosephNo ratings yet

- Recitation 050814Document5 pagesRecitation 050814William Zhuang100% (1)

- Course: Electronic Circuit Devices Lab No: 12 Title: Cascode Amplifier CID: - DateDocument5 pagesCourse: Electronic Circuit Devices Lab No: 12 Title: Cascode Amplifier CID: - DateAamir ChohanNo ratings yet

- Chapter 6 - Cmos Operational AmplifiersDocument79 pagesChapter 6 - Cmos Operational AmplifierssanjayorcaNo ratings yet

- Continuous-Time OTA-C Filters: Advantages: OTA-C Filters Have The Advantages of High Frequency or Wide BandwidthDocument12 pagesContinuous-Time OTA-C Filters: Advantages: OTA-C Filters Have The Advantages of High Frequency or Wide BandwidthAshraf DeenNo ratings yet

- References: (Used For Creation of The Presentation Material)Document35 pagesReferences: (Used For Creation of The Presentation Material)Kumar BsnspNo ratings yet

- Multistage Opamp PresentationDocument58 pagesMultistage Opamp PresentationgirishknathNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument78 pagesDigital Integrated Circuits: A Design Perspectiveدانشجویان فوق لیسانس الکترونیک 91 سیرجانNo ratings yet

- Lab10 2011Document5 pagesLab10 2011Venkat RamananNo ratings yet

- Electronic Circuits - II Lab ManualDocument26 pagesElectronic Circuits - II Lab Manualbalabasker100% (1)

- Lecture17 Fully Diff Amps CMFBDocument28 pagesLecture17 Fully Diff Amps CMFBmohamedNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)