Professional Documents

Culture Documents

Rr321202vlsisystemsdesign

Rr321202vlsisystemsdesign

Uploaded by

mylu_homeOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Rr321202vlsisystemsdesign

Rr321202vlsisystemsdesign

Uploaded by

mylu_homeCopyright:

Available Formats

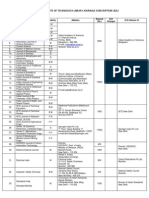

Code No: RR321202

Set No. 1

III B.Tech II Semester Supplimentary Examinations, Apr/May 2008 VLSI SYSTEMS DESIGN (Information Technology) Time: 3 hours Max Marks: 80 Answer any FIVE Questions All Questions carry equal marks 1. Implement the following logic functions using CMOS logic (a) Y = {(A + B).C}1 (b) Y = {(A.B + C).D}1 [8+8]

2. Dene an integrated circuit and explain clearly dierent Integrated Circuit design techniques using suitable examples. [16] 3. Design a stick diagram for two-input N-MOS NAND and NOR gates. 4. Design a layout for CMOS 2-input NAND gate. [16] [16]

5. (a) With respect to testability of a Digital design dene controllability and observability . (b) Explain the properties of testable digital circuit. [8+8]

6. Draw the Architecture of PLA and explain how dierent logic functions can be implemented using PLA. [16] 7. How would you translate a register - transfer structure into a legal two - phase latched sequential machine? [16] 8. Explain about design methodology for 1BM ASICS. [16]

1 of 1

Code No: RR321202

Set No. 2

III B.Tech II Semester Supplimentary Examinations, Apr/May 2008 VLSI SYSTEMS DESIGN (Information Technology) Time: 3 hours Max Marks: 80 Answer any FIVE Questions All Questions carry equal marks 1. Implement the following gates with n-MOS transistors only and explain its working (a) 2 - Input NAND gate. (b) 3 - Input NOR gate. [8+8]

2. Dene dierent current parameters of Digital IC and explain their signicance.[16] 3. Design a stick diagram for two-input N-MOS NAND and NOR gates. [16]

4. Compute the high-to-low delay of a two-input static complementary NOR gate with minimum-sized transistor driving these loads. (a) An inverter with minimum-sized pull up and pull down. (b) An inverter whose pull up and pull down are both of size W = 10 L = 10. [8+8] 5. Explain how wire delay are calculate using El-more - delay model and RC Trees. [16] 6. Draw the structure of a carry look ahead adder and explain its working principle. [16] 7. Explain clearly the detailed routing phase of the oor planning of the chip with few examples by considering all constraints. [16] 8. Sketch the architecture of the kitchen timer chip and explain about its architecture design. [16]

1 of 1

Code No: RR321202

Set No. 3

III B.Tech II Semester Supplimentary Examinations, Apr/May 2008 VLSI SYSTEMS DESIGN (Information Technology) Time: 3 hours Max Marks: 80 Answer any FIVE Questions All Questions carry equal marks 1. Implement the following gates with n-MOS transistors only and explain its working (a) 2 Input AND gate (b) 4 Input NOR gate. [8+8]

2. Explain clearly about each step of typical design abstraction ladder for digital integrated circuits. [16] 3. What is a stick diagram and explain about dierent symbols used for components in stick diagram. [16] 4. Implement 3-input NOR gate and 2 input AND gates using static complementary logic. [16] 5. Give tests for struck-open fault for each transistor in a two-input static NOR gate. [16] 6. Draw the structure of carry select adder and explain its working principle. [16]

7. How would you translate a register - transfer structure into a legal two - phase latched sequential machine? [16] 8. Draw the state transition graph for the kitchen timer chips controller. [16]

1 of 1

Code No: RR321202

Set No. 4

III B.Tech II Semester Supplimentary Examinations, Apr/May 2008 VLSI SYSTEMS DESIGN (Information Technology) Time: 3 hours Max Marks: 80 Answer any FIVE Questions All Questions carry equal marks 1. Implement the following gates with CMOS Logic and explain its working (a) Ex-OR gate. (b) 2 Input NOR gate. [8+8]

2. What are the key advantages of ICs? And explain how these advantages of ICs translate in to advantages at the system level. [16] 3. Explain with neat sketches CMOS fabrication using P - well process. 4. Design a layout for CMOS 3-input NAND gate. [16] [16]

5. Explain in detail the path - delay measurement of the combinational logic circuits. [16] 6. Draw the circuit diagram of four transistor DRAM cell with storage nodes and explain its working. [16] 7. Explain about the data - path controller architecture of register transfer machine. [16] 8. Explain about dierent types in the register le based data-path. [16]

1 of 1

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- OLICO NBT AQL Booklet (QL Notes, Practice, Info)Document46 pagesOLICO NBT AQL Booklet (QL Notes, Practice, Info)Bradley Katamba100% (2)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Analytic Geometry 2Document3 pagesAnalytic Geometry 2Wayne VillarozaNo ratings yet

- JNTUH MCA Syllabus 2013Document107 pagesJNTUH MCA Syllabus 2013SRINIVASA RAO GANTANo ratings yet

- JNTUH MBA Course Structure and Syllabus 2013Document80 pagesJNTUH MBA Course Structure and Syllabus 2013SRINIVASA RAO GANTANo ratings yet

- JNTUH Syllabus 2013 M.Tech EPSDocument23 pagesJNTUH Syllabus 2013 M.Tech EPSSRINIVASA RAO GANTANo ratings yet

- JNTUH Syllabus 2013 M.Tech CSEDocument33 pagesJNTUH Syllabus 2013 M.Tech CSESRINIVASA RAO GANTANo ratings yet

- JNTUH M.TECH PEDS 2013 SyllabusDocument24 pagesJNTUH M.TECH PEDS 2013 SyllabusSRINIVASA RAO GANTA100% (1)

- JNTUH Syllabus 2013 M.tech Communication SysDocument26 pagesJNTUH Syllabus 2013 M.tech Communication SysSRINIVASA RAO GANTANo ratings yet

- Paper-I Set-WDocument16 pagesPaper-I Set-WKaran AggarwalNo ratings yet

- r05011801 Metallurgical AnalysisDocument4 pagesr05011801 Metallurgical AnalysisSRINIVASA RAO GANTANo ratings yet

- JNTUH Syllabus 2013 Civil Engg Course StructureDocument2 pagesJNTUH Syllabus 2013 Civil Engg Course StructureSRINIVASA RAO GANTANo ratings yet

- IP Addresses and SubnettingDocument16 pagesIP Addresses and SubnettingHusnainNo ratings yet

- Kvs Librarypolicy2012Document59 pagesKvs Librarypolicy2012SRINIVASA RAO GANTANo ratings yet

- Guidelines For Open Educational Resources (OER) in Higher EducationDocument27 pagesGuidelines For Open Educational Resources (OER) in Higher EducationSRINIVASA RAO GANTANo ratings yet

- Ready Reckoner Radar EwDocument27 pagesReady Reckoner Radar EwSRINIVASA RAO GANTANo ratings yet

- Library Quality Criteria For NBA AccreditationDocument3 pagesLibrary Quality Criteria For NBA AccreditationSRINIVASA RAO GANTA100% (6)

- NET EXAM Paper 1Document27 pagesNET EXAM Paper 1shahid ahmed laskar100% (4)

- Dspace On WindowsDocument15 pagesDspace On WindowsSRINIVASA RAO GANTANo ratings yet

- Vbit Journals 2011-12Document6 pagesVbit Journals 2011-12SRINIVASA RAO GANTANo ratings yet

- Librarian Is Teaching or Non TeachingDocument1 pageLibrarian Is Teaching or Non TeachingSRINIVASA RAO GANTANo ratings yet

- Code - No: 25042: Freespace Guide CutoffDocument8 pagesCode - No: 25042: Freespace Guide CutoffSRINIVASA RAO GANTANo ratings yet

- Reg Pay Degree 020110Document16 pagesReg Pay Degree 020110SRINIVASA RAO GANTANo ratings yet

- Code No: 25022Document4 pagesCode No: 25022SRINIVASA RAO GANTANo ratings yet

- Code No: 25056Document8 pagesCode No: 25056SRINIVASA RAO GANTANo ratings yet

- Code No: 25079Document8 pagesCode No: 25079SRINIVASA RAO GANTANo ratings yet

- r05311902 Computer GraphicsDocument4 pagesr05311902 Computer GraphicsSRINIVASA RAO GANTANo ratings yet

- Rr322305 ImmunologyDocument4 pagesRr322305 ImmunologySRINIVASA RAO GANTANo ratings yet

- Code No: 35051Document8 pagesCode No: 35051SRINIVASA RAO GANTANo ratings yet

- Code No: 35060Document4 pagesCode No: 35060SRINIVASA RAO GANTANo ratings yet

- Rr322105-High Speed AerodynamicsDocument8 pagesRr322105-High Speed AerodynamicsSRINIVASA RAO GANTANo ratings yet

- Chapter 3Document87 pagesChapter 3nns100% (1)

- Spoken English Class 1Document26 pagesSpoken English Class 1Gourob JoysoyalNo ratings yet

- Bodmas - MBAtutesDocument4 pagesBodmas - MBAtutesMbatutesNo ratings yet

- Cat 2 Year 8Document7 pagesCat 2 Year 8mwagweNo ratings yet

- SOM Part 2Document71 pagesSOM Part 2Lee chanNo ratings yet

- Trig Cheat SheetDocument3 pagesTrig Cheat SheetEdm27No ratings yet

- Continuity Property of ProbabilityDocument1 pageContinuity Property of ProbabilityThảo NguyễnNo ratings yet

- Lecture 8: ROM & Programmable Logic Devices: Points Addressed in This LectureDocument5 pagesLecture 8: ROM & Programmable Logic Devices: Points Addressed in This LectureiwsisNo ratings yet

- Classroom Observation-2Document2 pagesClassroom Observation-2api-378191670No ratings yet

- 73-213 Winter 2011 Microsoft Excel In-Lab Tutorial #1: Part A: Download and Prepare The File For The TutorialDocument5 pages73-213 Winter 2011 Microsoft Excel In-Lab Tutorial #1: Part A: Download and Prepare The File For The Tutorialujju7No ratings yet

- Seminar2 Student Copy SUSSDocument6 pagesSeminar2 Student Copy SUSSmelodyNo ratings yet

- Mathematics ReflectioniozonesDocument367 pagesMathematics Reflectioniozonesvrun100% (2)

- WNCP List of Recommended Learning Resources For Grade 9 To Grade 12 MathematicsDocument3 pagesWNCP List of Recommended Learning Resources For Grade 9 To Grade 12 MathematicswoodycoquinNo ratings yet

- Algebra - Quadratic Equation - 1 - DPP 04 - (MBA PIONEER 2023)Document10 pagesAlgebra - Quadratic Equation - 1 - DPP 04 - (MBA PIONEER 2023)Jaiveer Singh RekhiNo ratings yet

- Physics Sa1 Study Material PDFDocument73 pagesPhysics Sa1 Study Material PDFUditSharma100% (1)

- Atiq Ur RehmanDocument11 pagesAtiq Ur RehmanMirza AatifNo ratings yet

- FallacyDocument6 pagesFallacyDea Novieann OliverosNo ratings yet

- Machine Learning BasicsDocument68 pagesMachine Learning BasicsvishalNo ratings yet

- Entropy Change For Chemical ReactionDocument11 pagesEntropy Change For Chemical ReactiongtdomboNo ratings yet

- Pre TestDocument4 pagesPre Testビリャルズ カイルNo ratings yet

- AMO Exercise 1Document2 pagesAMO Exercise 1Jonell Chan Xin RuNo ratings yet

- LR - Logical Reasoning A First CourseDocument349 pagesLR - Logical Reasoning A First CourseHamza MujahidNo ratings yet

- Grade 10 Singapore and Asian Schools Math Olympiad: Choose Correct Answer(s) From The Given ChoicesDocument2 pagesGrade 10 Singapore and Asian Schools Math Olympiad: Choose Correct Answer(s) From The Given ChoicesBao TrinhNo ratings yet

- Inventory ModelsDocument42 pagesInventory ModelsGabby MaravillaNo ratings yet

- Indirapuram Public School, Indirapuram: Ref. No/IPS/CIR/2022-034 Dated: 21.05.22Document4 pagesIndirapuram Public School, Indirapuram: Ref. No/IPS/CIR/2022-034 Dated: 21.05.22Manyya SinghNo ratings yet

- Visual Basic 2022 Made Easy A Comprehensive Guide To Visual Basic 2022 ProgrammingDocument384 pagesVisual Basic 2022 Made Easy A Comprehensive Guide To Visual Basic 2022 ProgrammingPhillip Jabu MambaNo ratings yet

- Compound Interest DiscussionDocument8 pagesCompound Interest DiscussionBaoooNo ratings yet

- IE405 System DynamicsDocument2 pagesIE405 System DynamicsloshidhNo ratings yet