Professional Documents

Culture Documents

Compal Confidential Schematics for AMD S1G4/RS880M/SB820M Mobile Platform

Uploaded by

Edu palaciosOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Compal Confidential Schematics for AMD S1G4/RS880M/SB820M Mobile Platform

Uploaded by

Edu palaciosCopyright:

Available Formats

A

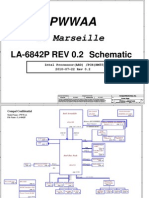

Compal confidential

LC-Marseille 10AD

PWWAE LA-6843P Schematics Document

Mobile AMD S1G4/ RS880M / SB820M

3

2010-08-16 Rev. 1.0

Compal Secret Data

Security Classification

2010-08-25

Issued Date

2010-08-25

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS,MB A6843

Rev

B

401982

Sheet

Wednesday, September 01, 2010

E

of

40

Compal Confidential

Thermal Sensor

ADM1032ARMZ

Model Name : PWWAA

Fan Control

page 5

page 7

AMD S1G4 CPU

Memory BUS(DDRIII)

Dual Channel

uFCPGA-638 Package

1.5V DDRIII 1066/1333MHZ

File Name : LA-6843P

200pin DDRIII-SO-DIMM X2

page 9,10

BANK 0, 1, 2, 3

page 5,6,7,8

Hyper Transport Link 2.6GHz

16X16

RTL8105E 10/100M

RJ45

PCIe port 3

page 24

page 24

AMD

CRT

page 16

RS880M

PCIe 4x

LCD Conn.

1.5V 2.5GHz(250MB/s)

page 17

WLAN

PCIe port 2

page 23

page 11,12,13,14,15

LAN

2

PCIe port 3

page 24

A-Link Express II

4X PCI-E

IO/B-- USB Right

USB port 0,1

page 23

USB

Card Reader

USB port 5

page 25

Int. Camera

SATA port 0

5V 480MHz

5V 1.5GHz(150MB/s)

AMD

USB port 9

page 17

SATA port 1

5V 1.5GHz(150MB/s)

SB820M

WLAN

SATA HDD

page 23

SATA ODD

page 23

USB

USB port 8

page 27

5V 480MHz

page 18,19,20,21,22

RTC CKT.

3.3V 33 MHz

LPC BUS

HD Audio

3.3V/1.5V 24MHz

HDA Codec

ALC259

page 26

Debug Port

Power On/Off CKT.

page 30

ENE KB926 E0

page 29

page 28

Power/B

Int.

MIC CONN

page 17

page 30

DC/DC Interface CKT.

Touch Pad

page 30

page 31

Int.KBD

page 29

MIC CONN

page 27

HP CONN

page 27

SPK CONN

page 27

EC ROM

page 29

Power Circuit DC/DC

4

page 31,32,33,34,35

36,37,38,39

Compal Secret Data

Security Classification

2010-08-25

Issued Date

2010-08-25

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS,MB A6843

Rev

B

401982

Wednesday, September 01, 2010

Sheet

E

of

40

DESIGN CURRENT 0.1A

+3VL

DESIGN CURRENT 0.1A

+5VL

DESIGN CURRENT 1A

+3VALW

DESIGN CURRENT 3.5A

+5VALW

B+

RT8205EGQW

SUSP

N-CHANNEL

SI4800

DESIGN CURRENT 2A

+5VS

DESIGN CURRENT 330mA

+3V_LAN

DESIGN CURRENT 1.5A

+3VS

DESIGN CURRENT 1A

+LCD_VDD

DESIGN CURRENT 300mA

+2.5VS

DESIGN CURRENT 2.5A

+1.8VS

DESIGN CURRENT 0.3A

+1.1VALW

DESIGN CURRENT 3.5A

+1.1VS

DESIGN CURRENT 6A

+NB_CORE

DESIGN CURRENT 18A

+CPU_CORE0

DESIGN CURRENT 18A

+CPU_CORE1

DESIGN CURRENT 4A

+VDDNB

DESIGN CURRENT 5A

+1.5V

DESIGN CURRENT 1A

+1.5VS

DESIGN CURRENT 1A

+0.75VS

DESIGN CURRENT 1.5A

+1.05VS

WOL_EN#

P-CHANNEL

AO-3413

SUSP

N-CHANNEL

SI4800

ENVDD

P-CHANNEL

AO-3413

APL5508

PWWAE LC-Marseille AMD

SUSP#

MP2121DQ

POK

RT8209BGQW

VLDT_EN#

N-CHANNEL

IRF8113

VLDT_EN#

N-CHANNEL

IRF8113

VR_ON

B

ISL6265A

SYSON

RT8209BGQW

SUSP

N-CHANNEL

IRF8113

SUSP

APL5331KAC

VR_ON#

APL5331KAC

Compal Secret Data

Security Classification

2010-08-25

Issued Date

2010-08-25

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS,MB A6843

Rev

B

401982

Sheet

Wednesday, September 01, 2010

1

of

40

Voltage Rails

Platform

O : ON

CPU

NB

S1G4

Danube

X : OFF

VGA

RS880M

NA

SB

Comment

SB820M

+5VS

1

+3VS

power

plane

+1.8VS

+1.5VS

State

+B

+5VALW

+3VL

+3VALW

+5VL

+1.1VALW

+1.1VS

+1.5V

+1.05VS

+0.75VS

+VGA_CORE

+RTCVCC

+VDDNB

+CPU_CORE

S0

S1

@ : just reserve , no build

SB820MR1@ : just reserve for SB820MR1 only

R3@ : just reserve for R3 only

CONN@ : just reserve for Connector only

CAM@ : just reserve for WebCam only

BT@ : just reserve for Blue Tooth only

880MR1@: just reserve for 880MR1 only

8105E_VC@: just reserve for 10/100 LAN VC version only

8105E_VB@: just reserve for 10/100 LAN VBversion only

+2.5VS

BTO (Build-To-Order)

Option Table

S3

S5 S4/AC

Function

Camera

Description

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

(C)

Explain

CAM@

BTO

SMBUS Control Table

3

I2C / SMBUS ADDRESSING

DEVICE

HEX

SOURCE

ADDRESS

DDR SO-DIMM 0

A0

10100000

DDR SO-DIMM 1

A2

10100010

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

DDC_CLK0

EC SM Bus2 address

HEX

Address

Device

Smart Battery

16H

0001 011X b

EMC1032-1 CPU 98H

EC KB926E0

HEX

DDC_DATA0

SCL0

Address

SDA0

1001 100X b

SCL1

EC KB926E0

SDA1

KB926

SODIMM

I / II

CLK

GEN

WLAN

LCD

DDC

ROM

KB926

RS880M

I2C_DATA

Device

CPU

THERMAL

SENSOR

EC_SMB_CK1

I2C_CLK

EC SM Bus1 address

BATT

RS880M

SB820

SB820

Compal Secret Data

Security Classification

2010-08-25

Issued Date

2010-08-25

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS,MB A6843

Rev

B

401982

Sheet

Wednesday, September 01, 2010

E

of

40

+1.1VS

250 mil

1

VLDT CAP.

1

C1

10U_0805_10V6K

Near CPU Socket

1

C2

10U_0805_10V6K

C3

0.22U_0603_16V4Z

C4

0.22U_0603_16V4Z

C5

180P_0402_50V8J

C6

180P_0402_50V8J

<11> H_CADIP[0..15]

<11> H_CADIN[0..15]

H_CADIP[0..15]

H_CADOP[0..15]

H_CADIN[0..15]

H_CADON[0..15]

H_CADOP[0..15]

<11>

H_CADON[0..15]

<11>

+1.1VS

+1.1VS

JCPUA

VLDT=500mA

< From NB >

H_CADIP0

H_CADIN0

H_CADIP1

H_CADIN1

H_CADIP2

H_CADIN2

H_CADIP3

H_CADIN3

H_CADIP4

H_CADIN4

H_CADIP5

H_CADIN5

H_CADIP6

H_CADIN6

H_CADIP7

H_CADIN7

H_CADIP8

H_CADIN8

H_CADIP9

H_CADIN9

H_CADIP10

H_CADIN10

H_CADIP11

H_CADIN11

H_CADIP12

H_CADIN12

H_CADIP13

H_CADIN13

H_CADIP14

H_CADIN14

H_CADIP15

H_CADIN15

HT LINK

D1

D2

D3

D4

VLDT_A0

VLDT_A1

VLDT_A2

VLDT_A3

E3

E2

E1

F1

G3

G2

G1

H1

J1

K1

L3

L2

L1

M1

N3

N2

E5

F5

F3

F4

G5

H5

H3

H4

K3

K4

L5

M5

M3

M4

N5

P5

L0_CADIN_H0

L0_CADIN_L0

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H15

L0_CADIN_L15

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

AE2

AE3

AE4

AE5

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

H_CADOP0

H_CADON0

H_CADOP1

H_CADON1

H_CADOP2

H_CADON2

H_CADOP3

H_CADON3

H_CADOP4

H_CADON4

H_CADOP5

H_CADON5

H_CADOP6

H_CADON6

H_CADOP7

H_CADON7

H_CADOP8

H_CADON8

H_CADOP9

H_CADON9

H_CADOP10

H_CADON10

H_CADOP11

H_CADON11

H_CADOP12

H_CADON12

H_CADOP13

H_CADON13

H_CADOP14

H_CADON14

H_CADOP15

H_CADON15

C7

2 10U_0805_10V6K

< VLDT_A & VLDT_B : HyperTransport I/O ring power >

< To NB >

<11>

<11>

<11>

<11>

H_CLKIP0

H_CLKIN0

H_CLKIP1

H_CLKIN1

J3

J2

J5

K5

L0_CLKIN_H0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

Y1

W1

Y4

Y3

H_CLKOP0

H_CLKON0

H_CLKOP1

H_CLKON1

<11>

<11>

<11>

<11>

<11>

<11>

<11>

<11>

H_CTLIP0

H_CTLIN0

H_CTLIP1

H_CTLIN1

N1

P1

P3

P4

L0_CTLIN_H0

L0_CTLIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

R2

R3

T5

R5

H_CTLOP0

H_CTLON0

H_CTLOP1

H_CTLON1

<11>

<11>

<11>

<11>

FOX_PZ6382A-284S-41F_Champlian

CONN@

< FAN Control Circuit : Vout = 1.6 x Vset >

+5VS

1A

<28> EN_DFAN1

C1120

10U_0805_10V4Z

U31

1

2

3

4

EN

VIN

VOUT

VSET

JFAN

+FAN1

GND

GND

GND

GND

8

7

6

5

@

C1121

1000P_0402_25V8J

1

2

3

4

5

1

2

3

+3VS

1

C1119

10U_0805_10V4Z

R795

10K_0402_5%

GND

GND

ACES_85204-0300N

CONN@

APL5607KI-TRG_SO8

+FAN1

@

C1122

0.01U_0402_25V7K

Compal Secret Data

Security Classification

2010-08-25

Issued Date

FAN_SPEED1 <28>

2

2010-08-25

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS,MB A6843

Rev

B

401982

Sheet

Wednesday, September 01, 2010

E

of

40

+1.5V

< Processor DDR3 Memory Interface >

< DDR2 VREF is 0.5 ratio >

< Close to CPU >

R1

JCPUC

<10> DDR_B_D[63..0]

1K_0402_1%

< From/To SO_DIMMB >

+MCH_REF

R2

C9

0.1U_0402_16V7K

C8

1000P_0402_25V8J

1K_0402_1%

+1.05VS

+1.05VS

JCPUB

Place them close to CPU within 1"

+1.5V

R4 1

R5 1

2 39.2_0402_1%

2 39.2_0402_1%

<9> MEM_MA_RST#

<9> DDR_A_ODT0

< To SO_DIMMA > <9> DDR_A_ODT1

< To SO_DIMMA >

<9> DDR_CS0_DIMMA#

<9> DDR_CS1_DIMMA#

<9> DDR_CKE0_DIMMA

< To SO_DIMMA > <9> DDR_CKE1_DIMMA

<9> DDR_A_CLK0

<9> DDR_A_CLK#0

MEM_P

MEM_N

<9> DDR_A_CLK1

<9> DDR_A_CLK#1

<9> DDR_A_BS#0

< To SO_DIMMA > <9> DDR_A_BS#1

<9> DDR_A_BS#2

< To SO_DIMMA >

<9> DDR_A_RAS#

<9> DDR_A_CAS#

<9> DDR_A_WE#

AF10

AE10

VDDR1 MEM:CMD/CTRL/CLK

VDDR5

VDDR2

VDDR6

VDDR3

VDDR7

VDDR4

VDDR8

VDDR9

MEMZP

MEMZN

VDDR_SENSE

W10

AC10

AB10

AA10

A10

Y10

VTT_SENSE

MEMVREF

W17

+MCH_REF

MB_RESET_L

B18

MB0_ODT0

MB0_ODT1

MB1_ODT0

W26

W23

Y26

DDR_B_ODT0

DDR_B_ODT1

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

V26

W25

U22

DDR_CS0_DIMMB#

DDR_CS1_DIMMB#

MB_CKE0

MB_CKE1

J25

H26

DDR_CKE0_DIMMB

DDR_CKE1_DIMMB

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

P22

R22

A17

A18

AF18

AF17

R26

R25

DDR_B_CLK0

DDR_B_CLK#0

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

MEM_MA_RST#

H16

MA_RESET_L

DDR_A_ODT0

DDR_A_ODT1

T19

V22

U21

V19

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

DDR_CS0_DIMMA# T20

DDR_CS1_DIMMA# U19

U20

V20

DDR_CKE0_DIMMA J22

DDR_CKE1_DIMMA J20

DDR_A_CLK0

DDR_A_CLK#0

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

MA_CKE0

MA_CKE1

< VTT regulator voltage >

MEM_MB_RST#

DDR_A_CLK1

DDR_A_CLK#1

N19

N20

E16

F16

Y16

AA16

P19

P20

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

N21

M20

N22

M19

M22

L20

M24

L21

L19

K22

R21

L22

K20

V24

K24

K19

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

DDR_A_BS#0

DDR_A_BS#1

DDR_A_BS#2

R20

R23

J21

MA_BANK0

MA_BANK1

MA_BANK2

MB_BANK0

MB_BANK1

MB_BANK2

R24

U26

J26

DDR_B_BS#0

DDR_B_BS#1

DDR_B_BS#2

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

R19

T22

T24

MA_RAS_L

MA_CAS_L

MA_WE_L

MB_RAS_L

MB_CAS_L

MB_WE_L

U25

U24

U23

DDR_B_RAS#

DDR_B_CAS#

DDR_B_WE#

< To SO_DIMMA >

< To SO_DIMMA > <9> DDR_A_MA[15..0]

D10

C10

B10

AD10

MA_CLK_H5

MA_CLK_L5

MA_CLK_H1

MA_CLK_L1

MA_CLK_H7

MA_CLK_L7

MA_CLK_H4

MA_CLK_L4

PAD

T1

MEM_MB_RST# <10>

DDR_B_ODT0 <10>

DDR_B_ODT1 <10>

< To SO_DIMMB >

DDR_CS0_DIMMB# <10>

DDR_CS1_DIMMB# <10><

To SO_DIMMB >

DDR_CKE0_DIMMB <10>

DDR_CKE1_DIMMB <10><

To SO_DIMMB >

DDR_B_CLK0 <10>

DDR_B_CLK#0 <10>

< To SO_DIMMB >

DDR_B_CLK1

DDR_B_CLK#1

DDR_B_CLK1 <10>

DDR_B_CLK#1 <10>

DDR_B_MA[15..0] <10>

<10> DDR_B_DM[7..0]

< To SO_DIMMB >

DDR_B_BS#0 <10>

DDR_B_BS#1 <10>

DDR_B_BS#2 <10>

< To SO_DIMMB >

DDR_B_RAS# <10>

DDR_B_CAS# <10>

DDR_B_WE# <10>

< To SO_DIMMB >

< To SO_DIMMB >

<10>

<10>

<10>

<10>

<10>

<10>

<10>

<10>

<10>

<10>

<10>

<10>

<10>

<10>

<10>

<10>

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS7

DDR_B_DQS#7

MEM:DATA

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

Y11

AE14

AF14

AF11

AD11

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

A12

B16

A22

E25

AB26

AE22

AC16

AD12

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS7

DDR_B_DQS#7

C12

B12

D16

C16

A24

A23

F26

E26

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

< From/To SO_DIMMB >

DDR_A_D[63..0]

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

E12

C15

E19

F24

AC24

Y19

AB16

Y13

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_DM[7..0]

<9>

< To SO_DIMMA >

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

<9>

< From/To SO_DIMMA >

FOX_PZ6382A-284S-41F_Champlian

CONN@

FOX_PZ6382A-284S-41F_Champlian

CONN@

<9>

< From/To SO_DIMMA >

Compal Secret Data

Security Classification

2010-08-25

Issued Date

2010-08-25

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS,MB A6843

Rev

B

401982

Sheet

Wednesday, September 01, 2010

E

of

40

JCPUD

+1.5V

+2.5VDDA

+2.5VS

+2.5VDDA

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

VDDA=300mA

L1 1

2 FBM_L11_201209_300L_0805

1

1

C12

C13

+2.5VDDA

1

C14

LDT_RST#

H_PWRGD

LDT_STOP#

+ C11

@

2

150U_B2_6.3VM_R45M

4.7U_0805_10V4Z

3300P_0402_50V7K

0.22U_0603_16V4Z

T2

+1.5V

+1.5V

< 200-MHz PLL Reference Clock >

1

C16

2 3900P_0402_50V7K

+1.1VS

CPU_CLKIN_SC_P

R15

R16

2 1K_0402_5%

2 1K_0402_5%

1

1

PAD

CPU_HTREF0

CPU_HTREF1

CPU_VDD0_RUN_FB_H

CPU_VDD0_RUN_FB_L

R10

Address:100_1100

C15

2 3900P_0402_50V7K

CPU_CLKIN_SC_N

Place close to CPU wihtin 1.5"

2 510_0402_5%

CPU_TEST25L

R29

1 1K_0402_5%

CPU_TEST12

R30

1 1K_0402_5%

CPU_TEST18

R31

1 1K_0402_5%

CPU_TEST19

R32

1 1K_0402_5%

CPU_TEST20

R33

1 1K_0402_5%

CPU_TEST21

R34

1 1K_0402_5%

CPU_TEST22

R265 2

1 1K_0402_5%

CPU_TEST23

R35

1 1K_0402_5%

CPU_TEST24

HT_REF0

HT_REF1

F6

E6

PAD

PAD

VDDNB_FB_H

VDDNB_FB_L

H6

G6

CPU_VDDNB_RUN_FB_H

CPU_VDDNB_RUN_FB_L

DBREQ_L

E10

CPU_DBREQ#

TDO

AE9

CPU_TDO

TEST23

TEST18

TEST19

TEST28_H

TEST28_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

C2

AA6

TEST9

TEST6

A3

A5

B3

B5

C1

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

1K_0402_5% 1

2 R20

D7

E7

F7

C7

TEST7

TEST10

C3

K8

TEST8

C4

TEST29_H

TEST29_L

C9

C8

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

CPU_VDDNB_RUN_FB_H

CPU_VDDNB_RUN_FB_L

+1.5V

CPU_TEST17

CPU_TEST16

CPU_TEST15

CPU_TEST14

2 300_0402_5%

@ R13 1

2 0_0402_5%

H_PROCHOT# <18>

route as differential

as short as possible

testpoint under package

T15

T16

J7

H8

TEST17

TEST16

TEST15

TEST14

TEST25_H

TEST25_L

AB8

AF7

AE7

AE8

AC8

AF8

CPU_SVD

W9

Y9

H10

G9

2 R19

CPU_PROCHOT#

VDDIO_FB_H

VDDIO_FB_L

CPU_TEST18

CPU_TEST19

R11

+1.5V

VDD0_FB_H

VDD0_FB_L

AD7

2 0_0402_5%

AF6 CPU_THERMTRIP#_R

AC7 CPU_PROCHOT#

AA8

PAD T3

THERMDC_CPU

THERMDA_CPU

CPU_TEST23

THERMTRIP_L

PROCHOT_L

MEMHOT_L

W7

W8

DBRDY

TMS

TCK

TRST_L

TDI

E9

E8

CPU_SVC <38>

CPU_SVD <38>

1K_0402_5% 1

< Serial VID Interface clock & data >

THERMDC

THERMDA

VDD1_FB_H

VDD1_FB_L

R24

R27

R6

P6

CPU_SVC

CPU_SVD

CPU_SVC

PAD

PAD

PAD

PAD

T4

T5

T6

T7

<38>

<38>

R6

10K_0402_5%

R7

2 1K_0402_5%

CPU_THERMTRIP#_R

Q1

1

H_THERMTRIP# <19>

R28

2

SIC

SID

ALERT_L

Y6

AB6

CPU_TEST21

CPU_TEST20

CPU_TEST24

CPU_TEST22

CPU_TEST12

CPU_TEST27

CPU_TEST25H

CPU_TEST27

AF4

AF5

AE6

A6

A4

2

2

1 510_0402_5%

1

1K_0402_5%

RESET_L

PWROK

LDTSTOP_L

LDTREQ_L

SVC

SVD

M11

W18

R22

CLKIN_H

CLKIN_L

G10

AA9

AC9

AD9

AF9

CPU_TEST25H

CPU_TEST25L

+1.5V

A9

A8

VSS

RSVD11

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

169_0402_1%

<18> CLK_CPU_BCLK#

VDDA1

VDDA2

B7

A7

F10

C6

CPU_SIC

CPU_SID

2 44.2_0402_1%

2 44.2_0402_1%

1

1

<38> CPU_VDD0_RUN_FB_H

<38> CPU_VDD0_RUN_FB_L

<18> CLK_CPU_BCLK

R12

R14

F8

F9

< Filtered PLL Supply Voltage >

MMBT3904_NL_SOT23-3

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

2

R25

1

80.6_0402_1%

H18

H19

AA7

D5

C5

FOX_PZ6382A-284S-41F_Champlian

CONN@

+1.5VS

R17

300_0402_5%

1

<18> LDT_RST#

LDT_RST#

C17

< Thermal Sensor >

@

2

0.01U_0402_25V7K

< HDT Connector >

U1

+3VS

JP2

+1.5VS

2

+1.5V

R21

300_0402_5%

<18,38> H_PWRGD

+1.5V

R40

2 300_0402_5%

1

R39

R38

R37

R36

1

1

1

1

2

2

2

2

H_PWRGD

+1.5V

C19

@

2

220_0402_5%

220_0402_5%

220_0402_5%

220_0402_5%

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

1

3

5

7

9

11

13

15

17

19

21

23

2

4

6

8

10

12

14

16

18

20

22

24

26

C20

VDD

SMCLK

EC_SMB_CK2

THERMDA_CPU

DP

SMDATA

EC_SMB_DA2

THERMDC_CPU

2

2200P_0402_50V7K

CPU_THERM#

DN

ALERT#

THERM#

GND

1

C21

0.1U_0402_16V7K

+3VS

R44

1

2

10K_0402_5%

1

R41

EC_SMB_CK2 <28>

EC_SMB_DA2 <28>

2

10K_0402_5%

@

+3VS

EMC1402-1-ACZL-TR_MSOP8

LDT_RST#

Address:0100_1100 EMC1402-1

Address:0100_1101 EMC1402-2

0.1U_0402_16V7K

SAMTEC_ASP-68200-07

CONN@

3/30 Change U1 ADM1032 to EMC1402 for cost down

+1.5VS

4

R18

300_0402_5%

<12,18> LDT_STOP#

LDT_STOP#

Compal Secret Data

Security Classification

C18

2010-08-25

Issued Date

@

0.01U_0402_25V7K

2010-08-25

Deciphered Date

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

Compal Electronics, Inc.

SCHEMATICS,MB A6843

Rev

B

401982

Sheet

Wednesday, September 01, 2010

E

of

40

JCPUE

+CPU_CORE

VDD decoupling : +CPU_CORE

+CPU_CORE

1

+ C90

2

1

+ C25

2

330U_6.3V_M_R15

+ C26

330U_X_2VM_R6M

330U_6.3V_M_R15

330U_X_2VM_R6M

+CPU_CORE

+CPU_CORE

C35

C34

C28

C29

C36

C37

C38

+ C96

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

0.22U_0603_16V4Z

0.01U_0402_25V7K

180P_0402_50V8J

Under CPU Socket

Under CPU Socket

Near CPU Socket

+ C23

2

1

+ C89

2

Near CPU Socket

1

+ C24

2

330U_6.3V_M_R15

330U_X_2VM_R6M

+CPU_CORE

330U_6.3V_M_R15

330U_X_2VM_R6M

+CPU_CORE

+CPU_CORE

C30

C31

C32

C33

C39

C40

C41

+ C95

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

Under CPU Socket

0.22U_0603_16V4Z

0.01U_0402_25V7K

180P_0402_50V8J

+VDDNB

Under CPU Socket

+1.5V

VDDIO decoupling : DDR SDRAM I/O ring power

+1.5V

C44

22U_0805_6.3V6M

C45

22U_0805_6.3V6M

C46

0.22U_0603_16V4Z

C47

0.22U_0603_16V4Z

C48

180P_0402_50V8J

C50

180P_0402_50V8J

Under CPU Socket

+1.5V

2

C54

0.22U_0603_16V4Z

C51

0.22U_0603_16V4Z

C52

0.22U_0603_16V4Z

0.01U_0402_25V7K

C65

0.01U_0402_25V7K

180PF Qt'y follow the distance between CPU socket and DIMM0. <2.5inch>

180P_0402_50V8J

C68

180P_0402_50V8J

C69

180P_0402_50V8J

Between CPU Socket and DIMM

C56 Co-layout with C75

+1.5V

3

1

1

C71

4.7U_0805_10V4Z

C72

4.7U_0805_10V4Z

C73

4.7U_0805_10V4Z

C74

4.7U_0805_10V4Z

C75

Between CPU Socket and DIMM

+1.05VS

+

2

+1.5V

1

C56 +

2

390U_2.5V_M_R10

C67

330U_D2E_2.5VM_R6M

180P_0402_50V8J

VDDR decoupling.

C57

4.7U_0805_10V4Z

C58

4.7U_0805_10V4Z

C59

0.22U_0603_16V4Z

C60

0.22U_0603_16V4Z

C61

1000P_0402_25V8J

C62

1000P_0402_25V8J

C63

180P_0402_50V8J

C1124 Co-layout with C1125

C70

C78

0.22U_0603_16V4Z

C79

0.22U_0603_16V4Z

C80

1000P_0402_25V8J

C81

1000P_0402_25V8J

C82

180P_0402_50V8J

C83

180P_0402_50V8J

1

+

2

390U_2.5V_M_R10

+1.05VS

C1124

C77

4.7U_0805_10V4Z

C1125

330U_D2E_2.5VM

Near CPU Socket Right side

C76

4.7U_0805_10V4Z

+1.05VS

180P_0402_50V8J

+1.05VS

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

AA4

AA11

AA13

AA15

AA17

AA19

AB2

AB7

AB9

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD6

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

B4

B6

B8

B9

B11

B13

B15

B17

B19

B21

B23

B25

D6

D8

D9

D11

D13

D15

D17

D19

D21

D23

D25

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

H21

H23

J4

+1.5V

C66

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

+1.5V

JCPUF

0.22U_0603_16V4Z

Between CPU Socket and DIMM

K16

M16

P16

T16

V16

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD1_11

VDD1_12

VDD1_13

VDD1_14

VDD1_15

VDD1_16

VDD1_17

VDD1_18

VDD1_19

VDD1_20

VDD1_21

VDD1_22

VDD1_23

VDD1_24

VDD1_25

VDD1_26

FOX_PZ6382A-284S-41F_Champlian

CONN@

+1.5V

C64

VDD0_1

VDD0_2

VDD0_3

VDD0_4

VDD0_5

VDD0_6

VDD0_7

VDD0_8

VDD0_9

VDD0_10

VDD0_11

VDD0_12

VDD0_13

VDD0_14

VDD0_15

VDD0_16

VDD0_17

VDD0_18

VDD0_19

VDD0_20

VDD0_21

VDD0_22

VDD0_23

C53

Between CPU Socket and DIMM

G4

H2

J9

J11

J13

J15

K6

K10

K12

K14

L4

L7

L9

L11

L13

L15

M2

M6

M8

M10

N7

N9

N11

+CPU_CORE

Near CPU Socket Left side

4

+VDDNB decoupling : Northbridge power

+VDDNB

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

FOX_PZ6382A-284S-41F_Champlian

CONN@

1

C42

22U_0805_6.3V6M

C43

22U_0805_6.3V6M

Compal Secret Data

Security Classification

C49

2010-08-25

Issued Date

22U_0805_6.3V6M

2010-08-25

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS,MB A6843

Rev

B

401982

Sheet

Wednesday, September 01, 2010

E

of

40

+1.5V

+1.5V

JDDRL

C10

DDR_A_DM0

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

<6> DDR_A_DQS#1

<6> DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

<6> DDR_A_DQS#2

<6> DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

CKE0

VDD1

NC1

BA2

VDD3

A12/BC#

A9

VDD5

A8

A5

VDD7

A3

A1

VDD9

CK0

CK0#

VDD11

A10/AP

BA0

VDD13

WE#

CAS#

VDD15

A13

S1#

VDD17

NCTEST

VSS27

DQ32

DQ33

VSS29

DQS#4

DQS4

VSS32

DQ34

DQ35

VSS34

DQ40

DQ41

VSS36

DM5

VSS37

DQ42

DQ43

VSS39

DQ48

DQ49

VSS41

DQS#6

DQS6

VSS44

DQ50

DQ51

VSS46

DQ56

DQ57

VSS48

DM7

VSS49

DQ58

DQ59

VSS51

SA0

VDDSPD

SA1

VTT1

VSS1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

RESET#

VSS12

DQ14

DQ15

VSS14

DQ20

DQ21

VSS16

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS#3

DQS3

VSS24

DQ30

DQ31

VSS26

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

DDR_A_D4

DDR_A_D5

DDR_A_DQS#0

DDR_A_DQS0

DDR_A_DQS#0 <6>

DDR_A_DQS0 <6>

DDR_A_D[0..63]

DDR_A_D6

DDR_A_D7

DDR_A_DM[0..7]

DDR_A_D[0..63]

<6>

DDR_A_DM[0..7]

<6>

1

DDR_A_D12

DDR_A_D13

DDR_A_MA[0..15]

DDR_A_DM1

MEM_MA_RST#

DDR_A_MA[0..15] <6>

MEM_MA_RST# <6>

DDR_A_D14

DDR_A_D15

DDR_A_D20

DDR_A_D21

DDR_A_DM2

DDR_A_D22

DDR_A_D23

DDR_A_D28

DDR_A_D29

+1.5V

+1.5V

DDR_A_DQS#3

DDR_A_DQS3

DDR_A_DQS#3 <6>

DDR_A_DQS3 <6>

DDR_A_D30

DDR_A_D31

R310

1K_0402_1%

R48

1K_0402_1%

1

DDR_A_D26

DDR_A_D27

VREF_DQ

VSS2

DQ0

DQ1

VSS4

DM0

VSS5

DQ2

DQ3

VSS7

DQ8

DQ9

VSS9

DQS#1

DQS1

VSS11

DQ10

DQ11

VSS13

DQ16

DQ17

VSS15

DQS#2

DQS2

VSS18

DQ18

DQ19

VSS20

DQ24

DQ25

VSS22

DM3

VSS23

DQ26

DQ27

VSS25

C85

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

1000P_0402_25V8J

C84

0.01U_0402_25V7K

4.7U_0805_10V4Z

DDR_A_D0

DDR_A_D1

+VREF_DQ

+VREF_DQ

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

<6> DDR_A_CLK0

<6> DDR_A_CLK#0

<6> DDR_A_BS#0

<6> DDR_A_WE#

<6> DDR_A_CAS#

<6> DDR_CS1_DIMMA#

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_MA10

DDR_A_BS#0

DDR_A_WE#

DDR_A_CAS#

DDR_A_MA13

DDR_CS1_DIMMA#

DDR_A_D32

DDR_A_D33

<6> DDR_A_DQS#4

<6> DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

<6> DDR_A_DQS#6

<6> DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

+3VS

+0.75VS

4

C91

0.1U_0402_16V4Z 2

205

206

G2

G1

DDR_A_MA15

DDR_A_MA14

DDR_A_MA6

DDR_A_MA4

DDR_A_MA2

DDR_A_MA0

DDR_A_CLK1

DDR_A_CLK#1

DDR_A_BS#1

DDR_A_RAS#

DDR_CS0_DIMMA#

DDR_A_ODT0

DDR_A_ODT1

< Close to JDDRH & JDDRL >

DDR_A_CLK1 <6>

DDR_A_CLK#1 <6>

DDR_A_BS#1 <6>

DDR_A_RAS# <6>

DDR_CS0_DIMMA# <6>

DDR_A_ODT0 <6>

DDR_A_ODT1 <6>

+VREF_CA

DDR_A_D36

DDR_A_D37

DDR_A_DM4

DDR_A_D38

DDR_A_D39

DDR_A_D44

DDR_A_D45

DDR_A_DQS#5

DDR_A_DQS5

1

C680

2

C235

2

C351

+1.5V

0.1U_0402_16V4Z

2

C87

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C88

C640

C641

1

0.1U_0402_16V4Z

DDR_A_DQS#5 <6>

DDR_A_DQS5 <6>

0.1U_0402_16V4Z

2

C642

1

0.1U_0402_16V4Z

C643

1

0.1U_0402_16V4Z

2

C644

1

0.1U_0402_16V4Z

C645

1

0.1U_0402_16V4Z

2

C646

1

0.1U_0402_16V4Z

C647

1

DDR_A_D46

DDR_A_D47

DDR_A_D52

DDR_A_D53

DDR_A_DM6

DDR_A_D54

DDR_A_D55

DDR_A_D60

DDR_A_D61

DDR_A_DQS#7

DDR_A_DQS7

+0.75VS

DDR_A_DQS#7 <6>

DDR_A_DQS7 <6>

DDR_A_D62

DDR_A_D63

0.1U_0402_16V4Z

2

C665

C664

1

0.1U_0402_16V4Z

C961

2

4.7U_0603_6.3V6K

SMB_CK_DAT0 <10,19>

SMB_CK_CLK0 <10,19>

+0.75VS

4

TYCO_2-2013289-1

CONN@

Compal Secret Data

Security Classification

DIMM_A STD H:5.2 mm

2010-08-25

Issued Date

2010-08-25

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

<Address: 00>

Date:

R315

1K_0402_1%

R49

1K_0402_1%

DDR_A_MA11

DDR_A_MA7

DDR_A_MA12

DDR_A_MA9

+VREF_CA

DDR_CKE1_DIMMA <6>

DDR_A_BS#2

DDR_CKE1_DIMMA

0.01U_0402_25V7K

<6> DDR_A_BS#2

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

4.7U_0805_10V4Z

CKE1

VDD2

A15

A14

VDD4

A11

A7

VDD6

A6

A4

VDD8

A2

A0

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

S0#

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

1000P_0402_25V8J

DDR_CKE0_DIMMA

<6> DDR_CKE0_DIMMA

SCHEMATICS,MB A6843

Rev

B

401982

Sheet

Wednesday, September 01, 2010

E

of

40

+1.5V

+1.5V

JDDRH

C92

1000P_0402_25V8J

0.1U_0402_16V4Z

4.7U_0805_10V4Z

+VREF_DQ

C93

DDR_B_D0

DDR_B_D1

1

DDR_B_DM0

C682

DDR_B_D2

DDR_B_D3

DDR_B_D8

DDR_B_D9

DDR_B_DQS#1

DDR_B_DQS1

<6> DDR_B_DQS#1

<6> DDR_B_DQS1

DDR_B_D10

DDR_B_D11

DDR_B_D16

DDR_B_D17

DDR_B_DQS#2

DDR_B_DQS2

<6> DDR_B_DQS#2

<6> DDR_B_DQS2

DDR_B_D18

DDR_B_D19

DDR_B_D24

DDR_B_D25

DDR_B_DM3

DDR_B_D26

DDR_B_D27

DDR_CKE0_DIMMB

<6> DDR_CKE0_DIMMB

2

DDR_B_BS#2

<6> DDR_B_BS#2

DDR_B_MA12

DDR_B_MA9

DDR_B_MA8

DDR_B_MA5

DDR_B_MA3

DDR_B_MA1

DDR_B_CLK0

DDR_B_CLK#0

<6> DDR_B_CLK0

<6> DDR_B_CLK#0

DDR_B_MA10

DDR_B_BS#0

<6> DDR_B_BS#0

DDR_B_WE#

DDR_B_CAS#

<6> DDR_B_WE#

<6> DDR_B_CAS#

DDR_B_MA13

DDR_CS1_DIMMB#

<6> DDR_CS1_DIMMB#

DDR_B_D40

DDR_B_D41

DDR_B_DM5

DDR_B_D42

DDR_B_D43

DDR_B_D48

DDR_B_D49

DDR_B_DQS#6

DDR_B_DQS6

<6> DDR_B_DQS#6

<6> DDR_B_DQS6

DDR_B_D50

DDR_B_D51

DDR_B_D56

DDR_B_D57

DDR_B_DM7

DDR_B_D58

DDR_B_D59

+3VS

+0.75VS

4

CKE0

VDD1

NC1

BA2

VDD3

A12/BC#

A9

VDD5

A8

A5

VDD7

A3

A1

VDD9

CK0

CK0#

VDD11

A10/AP

BA0

VDD13

WE#

CAS#

VDD15

A13

S1#

VDD17

NCTEST

VSS27

DQ32

DQ33

VSS29

DQS#4

DQS4

VSS32

DQ34

DQ35

VSS34

DQ40

DQ41

VSS36

DM5

VSS37

DQ42

DQ43

VSS39

DQ48

DQ49

VSS41

DQS#6

DQS6

VSS44

DQ50

DQ51

VSS46

DQ56

DQ57

VSS48

DM7

VSS49

DQ58

DQ59

VSS51

SA0

VDDSPD

SA1

VTT1

205

G1

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

64

66

68

70

72

CKE1

VDD2

A15

A14

VDD4

A11

A7

VDD6

A6

A4

VDD8

A2

A0

VDD10

CK1

CK1#

VDD12

BA1

RAS#

VDD14

S0#

ODT0

VDD16

ODT1

NC2

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

SCL

VTT2

74

76

78

80

82

84

86

88

90

92

94

96

98

100

102

104

106

108

110

112

114

116

118

120

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

202

204

G2

206

DDR_B_D4

DDR_B_D5

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_DQS#0 <6>

DDR_B_DQS0 <6>

DDR_B_D[0..63]

DDR_B_D6

DDR_B_D7

DDR_B_D[0..63]

DDR_B_DM[0..7]

DDR_B_DM[0..7]

<6>

<6>

1

DDR_B_D12

DDR_B_D13

DDR_B_MA[0..15]

DDR_B_MA[0..15]

DDR_B_DM1

MEM_MB_RST#

<6>

MEM_MB_RST# <6>

DDR_B_D14

DDR_B_D15

DDR_B_D20

DDR_B_D21

DDR_B_DM2

DDR_B_D22

DDR_B_D23

DDR_B_D28

DDR_B_D29

DDR_B_DQS#3

DDR_B_DQS3

DDR_B_DQS#3 <6>

DDR_B_DQS3 <6>

DDR_B_D30

DDR_B_D31

DDR_CKE1_DIMMB

DDR_CKE1_DIMMB <6>

DDR_B_MA15

DDR_B_MA14

DDR_B_MA11

DDR_B_MA7

DDR_B_MA6

DDR_B_MA4

DDR_B_MA2

DDR_B_MA0

DDR_B_CLK1

DDR_B_CLK#1

DDR_B_CLK1 <6>

DDR_B_CLK#1 <6>

DDR_B_BS#1

DDR_B_RAS#

DDR_B_BS#1 <6>

DDR_B_RAS# <6>

DDR_CS0_DIMMB#

DDR_B_ODT0

DDR_CS0_DIMMB# <6>

DDR_B_ODT0 <6>

DDR_B_ODT1

DDR_B_ODT1 <6>

+VREF_CA

DDR_B_D36

DDR_B_D37

DDR_B_DM4

DDR_B_D38

DDR_B_D39

DDR_B_D44

DDR_B_D45

DDR_B_DQS#5

DDR_B_DQS5

C683

0.1U_0402_16V4Z

DDR_B_D34

DDR_B_D35

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

VSS1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

RESET#

VSS12

DQ14

DQ15

VSS14

DQ20

DQ21

VSS16

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS#3

DQS3

VSS24

DQ30

DQ31

VSS26

4.7U_0805_10V4Z

DDR_B_DQS#4

DDR_B_DQS4

<6> DDR_B_DQS#4

<6> DDR_B_DQS4

VREF_DQ

VSS2

DQ0

DQ1

VSS4

DM0

VSS5

DQ2

DQ3

VSS7

DQ8

DQ9

VSS9

DQS#1

DQS1

VSS11

DQ10

DQ11

VSS13

DQ16

DQ17

VSS15

DQS#2

DQS2

VSS18

DQ18

DQ19

VSS20

DQ24

DQ25

VSS22

DM3

VSS23

DQ26

DQ27

VSS25

1000P_0402_25V8J

DDR_B_D32

DDR_B_D33

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

C352

C353

3

DDR_B_DQS#5 <6>

DDR_B_DQS5 <6>

DDR_B_D46

DDR_B_D47

+1.5V

DDR_B_D52

DDR_B_D53

0.1U_0402_16V4Z

2

DDR_B_DM6

C666

1

0.1U_0402_16V4Z

DDR_B_D54

DDR_B_D55

0.1U_0402_16V4Z

2

C667

1

C668

1

0.1U_0402_16V4Z

C669

1

0.1U_0402_16V4Z

2

C670

C671

1

0.1U_0402_16V4Z

DDR_B_DQS#7

DDR_B_DQS7

C674

C677

1

0.1U_0402_16V4Z

+0.75VS

+1.5V

DDR_B_D62

DDR_B_D63

DIMM_B STD H:9.2 mm

0.1U_0402_16V4Z

2

C676

SMB_CK_DAT0 <9,19>

SMB_CK_CLK0 <9,19>

1

0.1U_0402_16V4Z

+0.75VS

C675

1

+1.5V

1

+

C925

2

4.7U_0603_6.3V6K

1

C86

330U_X_2VM_R6M

C128

2

390U_2.5V_M_R10

4

Place near DIMM2

Compal Secret Data

2010-08-25

Issued Date

2010-08-25

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C673

C128 Co-layout with C86

DDR_B_DQS#7 <6>

DDR_B_DQS7 <6>

Security Classification

C672

DDR_B_D60

DDR_B_D61

LOTES_AAA-DDR-111-K01

CONN@

<Address: 01>

0.1U_0402_16V4Z

2

SCHEMATICS,MB A6843

Rev

B

401982

Sheet

Wednesday, September 01, 2010

E

10

of

40

U3B

<23>

<23>

<24>

<24>

< WLAN >

< LAN >

PCIE_PTX_C_IRX_P2

PCIE_PTX_C_IRX_N2

PCIE_PTX_C_IRX_P3

PCIE_PTX_C_IRX_N3

< From SB820 : x4 PCIE A-link >

<18>

<18>

<18>

<18>

<18>

<18>

<18>

<18>

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_RX2P

SB_RX2N

SB_RX3P

SB_RX3N

GFX_RX0P

GFX_RX0N

GFX_RX1P

GFX_RX1N

GFX_RX2P

GFX_RX2N

GFX_RX3P

GFX_RX3N

GFX_RX4P

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

GFX_RX7P

GFX_RX7N

GFX_RX8P

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

GFX_RX13P

GFX_RX13N

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

AE3

AD4

AE2

AD3

AD1

AD2

V5

W6

U5

U6

U8

U7

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

GPP_RX4P

GPP_RX4N

GPP_RX5P

GPP_RX5N

AA8

Y8

AA7

Y7

AA5

AA6

W5

Y5

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

SB_RX2P

SB_RX2N

SB_RX3P

SB_RX3N

880MR1@

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

A5

B5

A4

B4

C3

B2

D1

D2

E2

E1

F4

F3

F1

F2

H4

H3

H1

H2

J2

J1

K4

K3

K1

K2

M4

M3

M1

M2

N2

N1

P1

P2

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX4P

GPP_TX4N

GPP_TX5P

GPP_TX5N

AC1

AC2

AB4

AB3

AA2

AA1

Y1

Y2

Y4

Y3

V1

V2

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

AD7

AE7

AE6

AD6

AB6

AC6

AD5

AE5

SB_TX0P_C

SB_TX0N_C

SB_TX1P_C

SB_TX1N_C

SB_TX2P_C

SB_TX2N_C

SB_TX3P_C

SB_TX3N_C

PCE_CALRP(PCE_BCALRP)

PCE_CALRN(PCE_BCALRN)

AC8

AB8

PCIE_CALRP

PCIE_CALRN

PART 2 OF 6

PCIE I/F GFX

D4

C4

A3

B3

C2

C1

E5

F5

G5

G6

H5

H6

J6

J5

J7

J8

L5

L6

M8

L8

P7

M7

P5

M5

R8

P8

R6

R5

P4

P3

T4

T3

PCIE I/F GPP

PCIE I/F SB

PCIE PORT LIST

PCIE_ITX_PRX_P2

PCIE_ITX_PRX_N2

PCIE_ITX_PRX_P3

PCIE_ITX_PRX_N3

C129

C130

C131

C132

1

1

1

1

2

2

2

2

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

C133

C134

C135

C136

C137

C138

C139

C140

1

1

1

1

1

1

1

1

2

2

2

2

2

2

2

2

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

0.1U_0402_16V7K

PCIE_ITX_C_PRX_P2

PCIE_ITX_C_PRX_N2

PCIE_ITX_C_PRX_P3

PCIE_ITX_C_PRX_N3

<23>

<23>

<24>

<24>

PORT

DEVICE

PCIE-2 WLAN

PCIE-3 LAN

< WLAN >

< LAN >

R59

R58

1

1

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

1.27K_0402_1%

2K_0402_1%

2

2

<18>

<18>

<18>

<18>

<18>

<18>

<18>

<18>

< To SB820 : x4 PCEI A-link>

< TX Impedance Calibration. Connect to GND >

< RX Impedance Calibration. Connect to VDDPCIE >

+1.1VS

RS780M_FCBGA528

U3A

H_CADON[0..15]

H_CADOP[0..15]

<5>

H_CADON[0..15]

<5>

H_CADOP0

H_CADON0

H_CADOP1

H_CADON1

H_CADOP2

H_CADON2

H_CADOP3

H_CADON3

H_CADOP4

H_CADON4

H_CADOP5

H_CADON5

H_CADOP6

H_CADON6

H_CADOP7

H_CADON7

< From S1G4 CPU : x16 HT>

<5>

<5>

<5>

<5>

H_CLKOP0

H_CLKON0

H_CLKOP1

H_CLKON1

<5>

<5>

<5>

<5>

H_CTLOP0

H_CTLON0

H_CTLOP1

H_CTLON1

301_0402_1%1

Y25

Y24

V22

V23

V25

V24

U24

U25

T25

T24

P22

P23

P25

P24

N24

N25

H_CADOP8

H_CADON8

H_CADOP9

H_CADON9

H_CADOP10

H_CADON10

H_CADOP11

H_CADON11

H_CADOP12

H_CADON12

H_CADOP13

H_CADON13

H_CADOP14

H_CADON14

H_CADOP15

H_CADON15

2 R60

PART 1 OF 6

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

D24

D25

E24

E25

F24

F25

F23

F22

H23

H22

J25

J24

K24

K25

K23

K22

H_CADIP0

H_CADIN0

H_CADIP1

H_CADIN1

H_CADIP2

H_CADIN2

H_CADIP3

H_CADIN3

H_CADIP4

H_CADIN4

H_CADIP5

H_CADIN5

H_CADIP6

H_CADIN6

H_CADIP7

H_CADIN7

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

F21

G21

G20

H21

J20

J21

J18

K17

L19

J19

M19

L18

M21

P21

P18

M18

H_CADIP8

H_CADIN8

H_CADIP9

H_CADIN9

H_CADIP10

H_CADIN10

H_CADIP11

H_CADIN11

H_CADIP12

H_CADIN12

H_CADIP13

H_CADIN13

H_CADIP14

H_CADIN14

H_CADIP15

H_CADIN15

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

H24

H25

L21

L20

AC24

AC25

AB25

AB24

AA24

AA25

Y22

Y23

W21

W20

V21

V20

U20

U21

U19

U18

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD15P

HT_RXCAD15N

T22

T23

AB23

AA22

HT_RXCLK0P

HT_RXCLK0N

HT_RXCLK1P

HT_RXCLK1N

H_CTLOP0

H_CTLON0

H_CTLOP1

H_CTLON1

M22

M23

R21

R20

HT_RXCTL0P

HT_RXCTL0N

HT_RXCTL1P

HT_RXCTL1N

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

M24

M25

P19

R18

H_CTLIP0

H_CTLIN0

H_CTLIP1

H_CTLIN1

HT_RXCALP

HT_RXCALN

C23

A24

HT_RXCALP

HT_RXCALN

HT_TXCALP

HT_TXCALN

B24

B25

HT_TXCALP

HT_TXCALN

880MR1@ RS780M_FCBGA528

0718 Place within 1"

layout 1:2

HT_RXCAD0P

HT_RXCAD0N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD7P

HT_RXCAD7N

HYPER TRANSPORT CPU I/F

H_CADOP[0..15]

H_CADIP[0..15]

H_CADIN[0..15]

H_CADIP[0..15]

<5>

H_CADIN[0..15]

<5>

< To S1G4 CPU : x16 HT>

H_CLKIP0

H_CLKIN0

H_CLKIP1

H_CLKIN1

<5>

<5>

<5>

<5>

H_CTLIP0

H_CTLIN0

H_CTLIP1

H_CTLIN1

<5>

<5>

<5>

<5>

R61

2 301_0402_1%

< Transmitter Calibration Resistor to HT_TXCALN >

0718 Place within 1"

layout 1:2

Compal Secret Data

Security Classification

2010-08-25

Issued Date

2010-08-25

Deciphered Date

Title

Compal Electronics, Inc.

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS Custom

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

SCHEMATICS,MB A6843

Rev

B

401982

Sheet

Wednesday, September 01, 2010

E

11

of

40

+AVDD2

+AVDDQ

C144

2.2U_0603_6.3V4Z

+1.8VS

L4

+AVDD2

0_0603_5%

1

C142

C145

2.2U_0603_6.3V4Z

0.1U_0402_16V7K

+1.8VS

L6

2 BLM18PG121SN1D_0603

+AVDDQ

1

<16> UMA_CRT_R

<16> UMA_CRT_G

<16> UMA_CRT_B

<15,16>

<15,16>

<16>

<16>

UMA_CRT_HSYNC

UMA_CRT_VSYNC

UMA_CRT_CLK

UMA_CRT_DATA

R65 1

C148

2 715_0402_1%

+NB_PLLVDD

+NB_HTPVDD

2.2U_0603_6.3V4Z

+VDDA18HTPLL

+1.1VS

+VDDA18PCIEPLL

L2

2 BLM18PG121SN1D_0603

C141

2.2U_0603_6.3V4Z

R66 1

<15,18,23,24,28,29> PLT_RST#

<19> NB_PWRGD

NB_LDTSTOP#

<18> CPU_LDT_REQ#

L5

2 BLM18PG121SN1D_0603

+NB_HTPVDD

1

C146

2.2U_0603_6.3V4Z

LCD_EDID_CLK

LCD_EDID_DATA

<17> LCD_EDID_CLK

<17> LCD_EDID_DATA

T10 PAD

L7

2 BLM18PG121SN1D_0603

+VDDA18HTPLL

1

C150

T8

2.2U_0603_6.3V4Z

G18

G17

E18

F18

E19

F19

RED(DFT_GPIO0)

REDb(NC)

GREEN(DFT_GPIO1)

GREENb(NC)

BLUE(DFT_GPIO3)

BLUEb(NC)

A11

B11

F8

E8

DAC_HSYNC(PWM_GPIO4)

DAC_VSYNC(PWM_GPIO6)

DAC_SCL(PCE_RCALRN)

DAC_SDA(PCE_TCALRN)

G14

DAC_RSET(PWM_GPIO1)

A12

D14

B12

PLLVDD(NC)

PLLVDD18(NC)

PLLVSS(NC)

H17

VDDA18HTPLL

SYSRESETb

POWERGOOD

LDTSTOPb

ALLOW_LDTSTOP

<18> CLK_SBSRC_BCLK

<18> CLK_SBSRC_BCLK#

+1.8VS

C_Pr(DFT_GPIO5)

Y(DFT_GPIO2)

COMP_Pb(DFT_GPIO4)

VDDA18PCIEPLL1

VDDA18PCIEPLL2

NB_REFCLK_P

NB_REFCLK_N

R330 4.7K_0402_5%

2

1

2

1

R331 4.7K_0402_5%

<18> NB_REFCLK_P