Professional Documents

Culture Documents

Experiment 3 Time and Frequency Response of RC and RL Circuits

Uploaded by

Shashank SinghOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Experiment 3 Time and Frequency Response of RC and RL Circuits

Uploaded by

Shashank SinghCopyright:

Available Formats

ESc 201A: Introduction to Electronics

2013-2014 I Semester

Department of Electrical Engineering

Indian Institute of Technology Kanpur

Experiment 3

Time and Frequency Response of RC and RL Circuits

Introduction

Step response (or time response) of RC and RL circuits is of great importance in the design of pulse

(or digital) circuits. The aim of this experiment is to study the time response of RC and RL circuits.

In order to get the time response, square-wave signals are applied to the input of these circuits, and

the output measured as a function of frequency. The results obtained are then compared with the

theory.

RC Circuits

1.1 RC Integrator Circuit

R

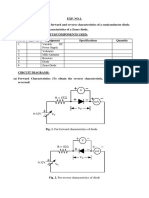

Wire the circuit of Fig.1. Connect signal from the

10 k

OUTPUT socket of the FG to the RC circuit, and

also to the CH-1 input of the DSO. Choose square

+5 V

+

+

wave signal and adjust the amplitude control to

C

Vi

T

V0

obtain a waveform going from 5 V to +5 V.

0.01 F

Connect the output of the RC circuit to CH-2 input

_

_

5 V

of the CRO. Be sure to choose the DC mode for both

CH-1and CH-2 inputs so as to observe the dc levels

of the signals. Use DSO to set the frequency of FG.

(i)

Time response when T << : Choose the

Figure 1 RC Integrator Circuit

waveform frequency (f) to be 25 kHz.

Observe and sketch Vi and V0 with respect to time. Note down the salient features of V0.

(ii) Time response when T : Choose f to be 5 kHz. Observe and sketch Vi and V0 with respect

to time. Note down the salient features of V0. Choose any two convenient points on the rising

and falling parts of V0 and measure the corresponding voltages and the time intervals. From

these readings, obtain the time constant of the circuit. Compare the result with that obtained

using the values of the components (R and C) used in the circuit.

(iii) Time response when T >> : Choose f = 500 Hz. Observe and sketch Vi and V0.

1.2 RC Differentiator Circuit

Wire the circuit of Fig.2. As in the case of the RC

integrator circuit, obtain time response of this circuit

for the following three cases. Sketch Vi and V0 for

each case.

(i)

(ii)

(iii)

(iv)

Step response when T << (use f = 25 kHz).

Step response when T (use f = 5 kHz).

Step response when T >> (use f = 500 Hz).

Increase the input signal frequency beyond 40

kHz and note the minimum frequency at

which the linear tilt (droop) seen in the V0

waveform is negligible.

C

0.01 F

5 V

+5 V

Vi

+

R

10 k

Figure 2 RC Differentiator Circuit

V0

_

ESc 201A: Introduction to Electronics

2013-2014 I Semester

RL Circuits

2.1

RL Integrator Circuit

Department of Electrical Engineering

Indian Institute of Technology Kanpur

Wire the circuit of Fig.3. Connect signal

from the OUTPUT socket of the FG to the

RL circuit, and also to the CH-1 input of the

DSO. Choose square wave signal and adjust

the amplitude control to obtain a waveform

going from 1 V to +1 V. Connect the output

of the RL circuit to CH-2 input of the DSO.

Be sure to choose the DC mode for both CH1 and CH-2 inputs so as to observe the dc

levels of the signals.

(i)

(ii)

2.2

Figure 3 RL Integrator Circuit

Choose the following waveform frequencies (f): 10 kHz, 40 kHz and 100 kHz. In each case

observe and sketch Vi and V0 with respect to time. Note down the salient features of V0.

Choose a convenient frequency, say f = 40 kHz. Observe and sketch Vi and V0 with respect to

time. Choose any two convenient points on the rising and falling parts of V0 and measure the

corresponding voltages and the time intervals. From these readings, obtain the time constant

of the circuit and estimate the value of L. Compare the result with that obtained using the

values of the components (R and L) used in the circuit.

RL Differentiator Circuit

Wire the circuit of Fig.4. As in the case of the RL

integrator circuit, obtain the time response of this

circuit for the following three frequencies: 10

kHz, 40 kHz and 100 kHz. In each case sketch Vi

and V0 with respect to time. Note down the

salient features of V0.

Figure 4 RL Differentiator Circuit

C Frequency Response

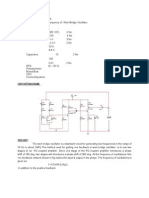

1. Connect up the circuit in Fig.5(a) (this is also called an RC lowpass filter).

2. Set up the scope to display on both channels and connect the points indicated in Fig.1(a) to the

respective channels.

3. Apply a sine wave from the MAIN output of the FG to the input point of the circuit. Ensure that

input coupling mode for both channels is ac (both ac/dc coupling buttons pressed OUT). Let the

sine wave be 2V p-p with zero dc offset.

4. At frequencies of 200Hz, 500Hz, 1kHz, 2kHz, 5kHz, 10kHz, 20kHz, 50kHz, 100kHz, 200kHz,

note the amplitudes of vo and vi. In the range 1kHz to 2kHz, take readings every 100Hz.

5. For each of the above frequency settings, also display vo vs vi in X-Y mode. You will need to first

ground the two inputs, set the scope in X-Y mode, center the dot on the screen, and then

ESc 201A: Introduction to Electronics

2013-2014 I Semester

Department of Electrical Engineering

Indian Institute of Technology Kanpur

reintroduce the channel inputs for this. You should see a figure such as shown in Fig.6.

Calculate the phase angle between vo and vi using the cursors in the DSO to measure the

time difference between two corresponding zero crossings on vo and vi. if this is T and

the period is T, the the phase difference (positive or negative) is given (in deg.)by 360T/T.

6. From the table of amplitudes and phase readings obtained from 4, 5 above, plot the

logarithmic gain AV = 20 log[vo/vi] and the phase against frequency on semilog graph

paper.

7. Repeat the above steps. for the RL circuit in Fig.1(b). Now take readings of amplitude and

phase at 2kHz, 5kHz, 10kHz, 20kHz, 50kHz, 100kHz, 200kHz, 500kHz.

(a)

(b)

Fig.5

Fig.6

You might also like

- Experiment 3 Time and Frequency Response of RC and RL CircuitsDocument3 pagesExperiment 3 Time and Frequency Response of RC and RL CircuitsSai SaurabNo ratings yet

- RL RC Frequency Response ExpDocument3 pagesRL RC Frequency Response ExpDustin GrahamNo ratings yet

- EC Lab ManualDocument27 pagesEC Lab ManualMohan KumarNo ratings yet

- Ec FinalDocument46 pagesEc FinalManjunath YadavNo ratings yet

- Electronic Circuits Lab Manual Clippers and AmplifiersDocument29 pagesElectronic Circuits Lab Manual Clippers and AmplifiersAshwath NadahalliNo ratings yet

- Mit Aec Labmanula 10esl37Document45 pagesMit Aec Labmanula 10esl37anon_70724250No ratings yet

- 1.RC CircuitsDocument7 pages1.RC CircuitsNaveen ChNo ratings yet

- Lab ManualDocument17 pagesLab ManualSatyam Govila100% (1)

- Measure and Design a RC Phase Shift OscillatorDocument4 pagesMeasure and Design a RC Phase Shift OscillatorNA NANo ratings yet

- Wein Bridge Oscillator FrequencyDocument6 pagesWein Bridge Oscillator Frequencyinspectornaresh100% (1)

- RC Phase Shift OscillatorDocument4 pagesRC Phase Shift OscillatorReddyvari Venugopal67% (3)

- Electronic Circuits & Logic Design Lab ManualDocument83 pagesElectronic Circuits & Logic Design Lab ManualsunandaalurNo ratings yet

- lab_manualDocument38 pageslab_manualsivaNo ratings yet

- Pulse and Digital Circuits Lab MANUAL ONLY FOR REFERENCE: Linear Wave Shaping AimDocument78 pagesPulse and Digital Circuits Lab MANUAL ONLY FOR REFERENCE: Linear Wave Shaping AimAditya SusurlaNo ratings yet

- Common Emitter Amplifier: S.No Name of The Component/ Equipment Specifications QtyDocument0 pagesCommon Emitter Amplifier: S.No Name of The Component/ Equipment Specifications Qtyagama1188No ratings yet

- RC Circuits: Study Frequency Response of FiltersDocument11 pagesRC Circuits: Study Frequency Response of Filters2456903No ratings yet

- Eca Lab-Min PDFDocument87 pagesEca Lab-Min PDFAkashita SharmaNo ratings yet

- Electronics and Communication Engineering: Department ofDocument39 pagesElectronics and Communication Engineering: Department ofMohit MeenaNo ratings yet

- RC OscillatorDocument8 pagesRC OscillatorRavi TejaNo ratings yet

- Linear Wave Shaping: Name of The Component/Equipment Specifications QuantityDocument61 pagesLinear Wave Shaping: Name of The Component/Equipment Specifications QuantitySainadh YerrapragadaNo ratings yet

- Linear Wave Shaping: Department of Electronics and Communication EngineeringDocument0 pagesLinear Wave Shaping: Department of Electronics and Communication EngineeringanishadandaNo ratings yet

- Capacitors and Time-Dependent Signals: ConceptDocument6 pagesCapacitors and Time-Dependent Signals: ConceptsriNo ratings yet

- Time Responseof RL and RC NetworksDocument5 pagesTime Responseof RL and RC Networkskudupudinagesh100% (1)

- Astable CircuitsDocument9 pagesAstable CircuitsRavindranath ShrivastavaNo ratings yet

- Full Wave Rectifier Characteristics LabDocument36 pagesFull Wave Rectifier Characteristics LabTushar Kush100% (4)

- Design A RC Coupled CE Transistor AmplifierDocument7 pagesDesign A RC Coupled CE Transistor AmplifierSudeep Nayak100% (1)

- RC Differentiator & IntegratorDocument6 pagesRC Differentiator & IntegratorMatt Imri100% (1)

- Objectives:: Electronics I Laboratory - EXPERIMENT 10 Common Emitter AmplifierDocument6 pagesObjectives:: Electronics I Laboratory - EXPERIMENT 10 Common Emitter AmplifierRabindraMaharanaNo ratings yet

- Electronic Circuits & Logic Design Laboratory ManualDocument61 pagesElectronic Circuits & Logic Design Laboratory ManualSrihari Y.sNo ratings yet

- PULSE AND DIGITAL CIRCUITS ASSIGNMENTDocument4 pagesPULSE AND DIGITAL CIRCUITS ASSIGNMENTathomeNo ratings yet

- Eca Lab-Manual PDFDocument87 pagesEca Lab-Manual PDFdedoga9086No ratings yet

- Low - Pass FilterDocument8 pagesLow - Pass FilterSaurabh BhiseNo ratings yet

- AEC NotesDocument271 pagesAEC Notes1DS19EC726- Pankaj Ashok M.No ratings yet

- PDC Lab ManualDocument46 pagesPDC Lab ManualKumar Goud.K90% (10)

- F =1/ (2Лrc√6+4K) Where, K=R /R≥1: By: Mr.L.Kumaraswamy M.E. (Iisc), Associate Professor, Mce, HassanDocument4 pagesF =1/ (2Лrc√6+4K) Where, K=R /R≥1: By: Mr.L.Kumaraswamy M.E. (Iisc), Associate Professor, Mce, HassanShweta GadgayNo ratings yet

- Lic May-June 2017Document15 pagesLic May-June 2017santhosh sekarNo ratings yet

- DLC Lab ManualDocument59 pagesDLC Lab ManualkulamangalamNo ratings yet

- Ee 352 Ec Ii LabDocument61 pagesEe 352 Ec Ii LabSatya SandeepNo ratings yet

- I C and Pulse and Digital Circuits LabvbDocument81 pagesI C and Pulse and Digital Circuits LabvbGarry MehrokNo ratings yet

- Practicas de OsciloscopioDocument9 pagesPracticas de OsciloscopiokarolcoNo ratings yet

- Answers FinalDocument20 pagesAnswers FinalMario HanyNo ratings yet

- RC Circuits: Charging, Discharging, Integration & DifferentiationDocument7 pagesRC Circuits: Charging, Discharging, Integration & DifferentiationMohmed Al NajarNo ratings yet

- RC, RL and RLC Circuit ResponseDocument3 pagesRC, RL and RLC Circuit Responsepuja maneNo ratings yet

- aeclAB 1Document41 pagesaeclAB 1ayjagadishNo ratings yet

- RC Circuit Frequency EsponseDocument5 pagesRC Circuit Frequency EsponseReddyvari VenugopalNo ratings yet

- Design and Test Wien and Colpitts OscillatorsDocument2 pagesDesign and Test Wien and Colpitts OscillatorsAlessio CapitanelliNo ratings yet

- Lab Assignment #2 Due: Oct. 5, 20 Materials Needed: Sep. 30, 20 Fall 2020Document5 pagesLab Assignment #2 Due: Oct. 5, 20 Materials Needed: Sep. 30, 20 Fall 2020api-482290211No ratings yet

- Experiment No.1: Hartley OscillatorDocument3 pagesExperiment No.1: Hartley OscillatorBhadresh RenukaNo ratings yet

- AEC Manual 2018-2019Document99 pagesAEC Manual 2018-2019Raza SikandarNo ratings yet

- Laboratory Manual FOR Lab Course EL 491 Electronics Circuit Design LaboratoryDocument15 pagesLaboratory Manual FOR Lab Course EL 491 Electronics Circuit Design LaboratoryNaushad AlamNo ratings yet

- Experiment 2 BJT SwitchDocument6 pagesExperiment 2 BJT Switchprop_kcp50% (2)

- RC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentDocument8 pagesRC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentMani BharathiNo ratings yet

- DC-DC BUCK AND BUCK-BOOST CONVERTERS: WAVEFORMS AND OUTPUT VOLTAGEDocument6 pagesDC-DC BUCK AND BUCK-BOOST CONVERTERS: WAVEFORMS AND OUTPUT VOLTAGEAlecsandra RusuNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- IIBCC-2022_Cellulose-refining-for-fibre-cement-part-2-length-reduction-and-other-effects-of-refiningDocument15 pagesIIBCC-2022_Cellulose-refining-for-fibre-cement-part-2-length-reduction-and-other-effects-of-refiningjuaanxpoonceNo ratings yet

- Cloud Computing Bangla-Ragib HassanDocument19 pagesCloud Computing Bangla-Ragib HassanShah Shishir100% (1)

- Independance of VariableDocument20 pagesIndependance of VariableKarimaNo ratings yet

- 1D Spring System SimulationDocument47 pages1D Spring System SimulationSandeep GogadiNo ratings yet

- Homework Solution: Investment Science: Solution Problem 5.2: The RoadDocument7 pagesHomework Solution: Investment Science: Solution Problem 5.2: The RoadAbdu AbdoulayeNo ratings yet

- Maths - Sample Paper1Document5 pagesMaths - Sample Paper1Arnav SudhindraNo ratings yet

- GVA62Document5 pagesGVA62kuazuNo ratings yet

- The Z Notation:: A Reference ManualDocument33 pagesThe Z Notation:: A Reference ManualSiti AisyahNo ratings yet

- Money WiseDocument62 pagesMoney Wisejei liNo ratings yet

- Barthes - S-ZDocument11 pagesBarthes - S-ZJavier Zamudio100% (1)

- Performance Indicator - Physics 2Document7 pagesPerformance Indicator - Physics 2lim chuan yangNo ratings yet

- OOP Lesson PlanDocument8 pagesOOP Lesson PlanPrema SelvamNo ratings yet

- Unesco Als Ls3 Math m05 SG (v1.3)Document24 pagesUnesco Als Ls3 Math m05 SG (v1.3)als midsayap1100% (2)

- EPayments Merchant Web Service (V. 0.3) - EngDocument25 pagesEPayments Merchant Web Service (V. 0.3) - EngRadusi ViorelNo ratings yet

- Sketching y X Transformations and Turning Point Form: Chapter 7 Parabolas and Other GraphsDocument1 pageSketching y X Transformations and Turning Point Form: Chapter 7 Parabolas and Other GraphsraNo ratings yet

- Nlight Hardware ManualDocument42 pagesNlight Hardware Manualtberg32No ratings yet

- D Block Notes StudymateDocument9 pagesD Block Notes StudymateArjun PasrichaNo ratings yet

- KPIs Subcounters 14apr15 V1-NOKBSC-SEG-hour-PM 10530-2018 04 15-15 49 41 855Document102 pagesKPIs Subcounters 14apr15 V1-NOKBSC-SEG-hour-PM 10530-2018 04 15-15 49 41 855AmMood GmrNo ratings yet

- Coclia EyelidDocument5 pagesCoclia EyelidFaradila HakimNo ratings yet

- RF Surge Device Installation GuideDocument3 pagesRF Surge Device Installation GuideThắng TrầnNo ratings yet

- Power Electronics Switch SelectionDocument32 pagesPower Electronics Switch SelectionSyed AfzalNo ratings yet

- User Guide: Newland Android PDA UHF ApplicationDocument14 pagesUser Guide: Newland Android PDA UHF ApplicationTunitrackNo ratings yet

- Gabion Walls Presentation FijiDocument38 pagesGabion Walls Presentation FijiHuy ChungNo ratings yet

- Calculating Angles Between Two 3-Space Sensor Devices On A Human BodyDocument24 pagesCalculating Angles Between Two 3-Space Sensor Devices On A Human BodyshravantataNo ratings yet

- Standard Test Method For Splitting Tensile Strength of Cylindrical Concrete Specimens1Document5 pagesStandard Test Method For Splitting Tensile Strength of Cylindrical Concrete Specimens1Lupita RamirezNo ratings yet

- Chapter 10 Explores Weathering, Soil Formation and Mass WastingDocument34 pagesChapter 10 Explores Weathering, Soil Formation and Mass WastingEverett Heart Pargad VNo ratings yet

- Inventory Record - FinalDocument6 pagesInventory Record - FinalParag WadekarNo ratings yet

- Ch2 Operating-System StructuresDocument88 pagesCh2 Operating-System Structurescs LiuNo ratings yet

- Waffle SlabsDocument5 pagesWaffle Slabseugenia omuhindiNo ratings yet

- Oracle Goldengate 12c Fundamentals For OracleDocument5 pagesOracle Goldengate 12c Fundamentals For OracleqaleeqNo ratings yet