100% found this document useful (1 vote)

1K views1 pageVlsi Question Papers

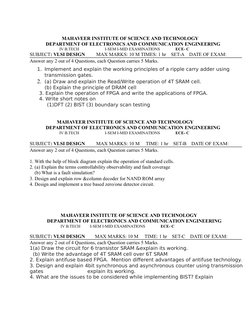

This document contains information about the mid-term examination for the VLSI Design subject for the Electronics and Communication Engineering department. It provides three different exam question paper sets (Set A, B and C) with four questions each to choose two questions from. The exam duration is 1 hour and the total marks are 10. The questions cover various topics related to VLSI design including ripple carry adder, SRAM cell operation, FPGA principles and applications, standard cell operation, fault testing concepts, ROM decoder design, zero/one detector design and BIST implementation issues.

Uploaded by

jahnaviCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd

100% found this document useful (1 vote)

1K views1 pageVlsi Question Papers

This document contains information about the mid-term examination for the VLSI Design subject for the Electronics and Communication Engineering department. It provides three different exam question paper sets (Set A, B and C) with four questions each to choose two questions from. The exam duration is 1 hour and the total marks are 10. The questions cover various topics related to VLSI design including ripple carry adder, SRAM cell operation, FPGA principles and applications, standard cell operation, fault testing concepts, ROM decoder design, zero/one detector design and BIST implementation issues.

Uploaded by

jahnaviCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd

- VLSI Design (B.Tech ECE-B): Exam paper for VLSI Design, detailing the questions and marks allocation for the exam.

- VLSI Design (ECE-C): Another exam paper for VLSI Design specifically for ECE-C with a different set of questions and instructions.