Professional Documents

Culture Documents

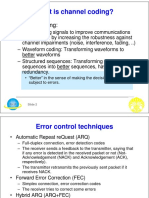

Engineering Journal New Hybrid Concatenated Codes

Uploaded by

Engineering JournalOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Engineering Journal New Hybrid Concatenated Codes

Uploaded by

Engineering JournalCopyright:

Available Formats

International Journal of Engineering Research & Science (IJOER)

ISSN: [2395-6992]

[Vol-2, Issue-3 March- 2016]

New Hybrid Concatenated Codes

Ya-Cheng Lu1, Chin-Wen Shin2, Chia-Jung Li3, Erl-Huei Lu4

Department of Electrical Engineering, Chang Gung University, Tao-Yuan, Taiwan

Abstract To improve the performance of hybrid concatenated convolutional codes (HCCC); a modified Log-MAP

algorithm and an enhanced HCCC are introduced and demonstrated to be efficient and practical by simulation results. The

new coding scheme achieves about 1.0 dB additional coding gain, compared to the general turbo coding scheme at a BER =

10-6, with a frame length of 8192-bit. The system complexity and decoding latency of the new scheme is lower than the

HCCC proposed by Divsalar and Pollara [6] within acceptable performance degradation. Since the bit-error-rate of the

proposed HCCC can be dramatically reduced by slightly increasing signal-to-noise ratio, the new hybrid concatenated

coding scheme is very suitable for those communication environments in which high reliability is important.

Keywords hybrid concatenated convolutional codes (HCCC), bit-error-rate, coding gain.

I.

INTRODUCTION

Turbo codes, proposed in 1993 [1], show outstanding error correction performance and thus are widely used in

communication areas, such as third-generation mobile and deep-space communications [2] [3]. The general encoder structure

of turbo code is a parallel concatenated convolutional code (PCCC). Two component encoders are used to code the same

input bits, but an interleaver is placed between the encoders. The decoder of PCCC is an iterative structure. Two component

decoders, two interleavers as well as one de-interleaver are needed. During the iterative decoding procedure, only the

extrinsic information of systematic bits is calculated and provided as the prior information of the decoded bits, however, the

prior information of the parity bits has not been retrieved. Detail discussions for the kind of turbo codes have been given in

[4].

Aiming for excellent BER performance, other concatenated codes, such as serial concatenated convolutional code (SCCC)

[5] and hybrid concatenated convolutional code (HCCC) [6], are proposed. In [5] and [6], not only the extrinsic information

of systematic bits, but also the extrinsic information of parity bits, is exchanged between the component decoders. Therefore,

the performances of SCCC and HCCC have been shown to be superior, in some cases, to a general turbo code.

In this work, modifications of Log-MAP algorithm are presented. Based on the modified Log-MAP algorithm, an enhanced

HCCC scheme is also proposed. Using the new scheme, both the extrinsic information of systematic bits and parity bits can

be retrieved during iterative decoding. Thus, the decoding performance can be improved dramatically when signal-to-noise

ratio (SNR) is slightly raised. With a frame length of 8192-bit, simulation results show that the enhanced scheme achieves an

additional coding gain about 1.0dB over the turbo coding scheme, at a bit-error-rate (BER) = 10-6. Moreover, the decoding

latency and system complexity is much lower than that of the Divsalar-Pollara HCCC [6] within acceptable performance

degradation.

II.

REVIEW OF LOG-MAP ALGORITHM

The performance of Log-MAP algorithm is almost same as that of MAP algorithm at a fraction of complexity [7]. Therefore

it is an attractive algorithm to design the component decoder of turbo codes. Let uk be the message bit at time k and

y ( y1 , y2 ,, yN ) be the sequence of the received symbols. The LLR (log likelihood ratio) of bit uk is the soft-output,

defined as:

exp[ Ak 1 ( s ') k ( s ', s) Bk ( s)]

( s ', s ) uk 1

ln

exp[

A

(

s

')

(

s

',

s

)

B

(

s

)]

k 1

k

k

( s ', s )

uk 1

(1)

Page | 136

International Journal of Engineering Research & Science (IJOER)

ISSN: [2395-6992]

[Vol-2, Issue-3 March- 2016]

where P(uk 1| y) is the a-posteriori probability (APP) of uk 1 or uk 1 , u (u1 , u2 ,, uN ) is the sequence of

message bits. The s and s denote states at the (k-1)th and the kth time stages in the trellis diagram, respectively. In Equation

(1), the logarithm ratio of probabilities of uk 1 to uk 1 refers to the state transitions from s ' Sk 1 to s Sk , denoted

as ( s ' Sk 1 , s Sk ), for 1 k N .

The branch metric k ( s ', s) can be computed by

L

1

k (s , s) C uk L(uk ) c

2

2

'

n 1

y

l 0

kl

xkl

(2)

where L( u k ) is the prior information of bit u k which was given by the other component decoder, Lc is the channel reliability

and xkl is the codeword. When the initial condition A0 ( s) and the received sequence y j k has been given, the forward metric

Ak (s ') is calculated by the forward recursive computation:

Ak ( s) ln exp[( Ak 1 ( s ' ) k ( s ' , s)]

all s'

(3)

When the BN ( s) and the received sequence y j k has been given, the backward metric Bk 1 ( s ) is calculated by the backward

recursive computation:

Bk 1 ( s ' ) ln exp[( Bk ( s ) k ( s ' , s)]

all s

(4)

For iterative decoding; Eq (2) can be decomposed as

L

L

1

k (s ' , s) C uk L(uk ) c yk 0 xk 0 c

2

2

2

n 1

y

l 1

kl

L

1

xkl C uk L(uk ) c yk 0 xk 0 k (s ', s)

2

2

(5)

Substituting Eqs (3), (4) and (5) into (1), we can get

L(uk | y) L(uk ) Lc yk 0 Le (uk )

(6)

The extrinsic information Le (uk ) , after interleaved (or de-interleaved), is to be used as the prior information L(uk ) of

systematic bit u k for the other component decoder. Notably, there is not any prior information (or extrinsic information) of

parity bits being calculated in the general Log-MAP algorithm. In the next section, we will modify Eqs (1) and (2) such that

both the extrinsic information of the systematic and the parity bits can be calculated and used as the prior information in the

iterative decoding.

III.

MODIFIED LOG-MAP ALGORITHM

Since the soft outputs of a general Log-MAP algorithm do not involve the prior information of parity bits, this motivates us

that the Log-MAP algorithm may be more efficient if both the prior information of systematic bits and parity bits can be

provided before decoding operation is executed. Investigating Eq (1), it is evident that the a-posterior LLR of each bit in a

codeword (including each of systematic bits and parity bits) can be computed by using the modified formula, as the

following equation:

exp[ Ak 1 ( s ') Bk ( s) k ( s ', s)]

( s ', s ) xkl 1

L( xkl | y) ln

exp[ Ak 1 ( s ') Bk ( s) k ( s ', s)]

( s ', s )

xkl 1

(7)

Page | 137

International Journal of Engineering Research & Science (IJOER)

ISSN: [2395-6992]

[Vol-2, Issue-3 March- 2016]

for k 1, 2,, N and l 0,1,, n 1 ; where N is the frame length and n is the number of codeword bits labeled on each

branch in the trellis diagram. To compute the branch metric, Eq (2) can be modified by joining the prior information of parity

bits as the following:

k ( s ' , s) C

L n 1

1 n 1

xkl L( xkl ) C ykl xkl

2 l 0

2 l 0

(8)

The computations for the forward metric Ak (s) and the backward metric Bk 1 ( s ) are same as Eqs (3) and (4).

There are two points to be addressed. First, the prior information of both systematic bits and parity bits, or only one of them,

can be used for computing branch metric by using Eq (8). Second, it needs to set L( xkl ) 0 in (8) if the prior information of

bit xkl is unavailable.

Substituting Eqs (3), (4) and (8) into (7), the formula for calculating the extrinsic information of bit xkl can be refined as

Le ( xkl ) L( xkl | y) L( xkl ) Lc ykl

IV.

(9)

ENHANCEMENT OF HCCC

The encoder of enhanced HCCC is shown in Fig. 1 which consists of three identical recursive systematic convolutioanl

(RSC) codes of code rate =1/2 (denoted by RSC1, RSC2 and RSC3, respectively) and two interleavers (denoted by ), as

well as a puncturing and multiplexing unit (denoted by PM). As an example to illustrate the proposed HCCC, the generator

polynomials of RSC codes are 1 D D 2 and 1 D 2 . In Fig. 1, the combination of RSC1 and RSC2 is exactly the same as a

general parallel concatenated code; but RSC1 and RSC3 are concatenated serially. Since RSC3 encodes the interleaved parity

output of RSC1, the prior information of the parity bits xkl (where l 1 ) can be produced by the corresponding component

decoder, as the following description.

The iterative HCCC decoder of the new scheme consists of three modified Log-MAP component decoders (denoted by D1 ,

D2 and D3 ), four interleavers (denoted by ), and two de-interleavers (denoted by 1 ), as shown in Fig. 2. Each of

component decoders is designed based on the modified Log-MAP algorithm in Section3.

FIG.1 THE ENHANCED HCCC ENCODER SCHEME

Page | 138

International Journal of Engineering Research & Science (IJOER)

ISSN: [2395-6992]

[Vol-2, Issue-3 March- 2016]

FIG.2 THE DECODER OF THE ENHANCED HCCC

First, D1 generates the extrinsic information Le ( xk 0 ) and Le ( xk1 ) using yk 0 and yk1 , for k 1, 2,, N , as well as the prior

information L( xk 0 ) and L( xk1 ) , where L( xk 0 ) and L( xk1 ) are the extrinsic information generated by D2 and D3 . The

extrinsic information Le ( xk 0 ) and Le ( xk1 ) of D1 are sent to D2 and D3 as the prior information. Then, D2 and D3

generate the extrinsic information Le ( xk 0 ) and Le ( xk1 ) using the related received sequence and the prior information. The

detail iterative decoding procedure is as following:

In the first phrase of the first iteration, D1 set L( xk 0 ) L( xk1 ) 0 and takes the received systematic bits Lc yk 0 as well as

parity bits Lc yk1 . Then D1 computes L(x k 0 | y) and L(x k1 | y) using Eq (7). The extrinsic information Le ( xk 0 ) and Le ( xk1 )

are computed using Eq (9) and sent to D2 and D3 as the prior information of systematic bits xk 0 and parity bits xk 1 ,

respectively.

In the second phrase of the first iteration, D2 and D3 can operate simultaneously. That is, D2 takes Lc yk 0 , Lc yk 2 and

L( xk 0 ) , and D3 takes Lc yk1 , Lc yk 3 and L( xk1 ) , as soft inputs to generate L(x k 0 | y) and L(x k1 | y) using Eqs (3), (4), (8)

and (7), simultaneously. Then the extrinsic information Le ( xk 0 ) and Le ( xk1 ) are calculated using Eq (9), respectively.

Finally, the Le ( xk 0 ) and Le ( xk1 ) are sent to D1 and taken as the prior information L( xk 0 ) and L( xk1 ) of D1 .

During the second iteration, the enhanced HCCC decoder has the same decoding procedure as the first iteration, except D1

receives Le ( xk 0 ) and Le ( xk1 ) from D2 and D3 , respectively, and taken them as its prior information. Once the second

iteration is finished, other iterations can be continued until all predetermined iterations are performed or the decoding

Page | 139

International Journal of Engineering Research & Science (IJOER)

ISSN: [2395-6992]

[Vol-2, Issue-3 March- 2016]

performance meets its stopping criteria [8]. Finally, the enhanced HCCC decoder decides message bits xk 0 from L(x k 0 | y)

using a hard-decision operation.

There are several points to be addressed. First, the computation complexity of D1 is only slightly heavier than that of a

general Log-MAP decoder because all metrics for computing the LLR L(x k 0 | y) and L(x k1 | y) are identical. Thus the

overall system complexity of the new decoder is about 1.5 times compared with a general turbo decoder. Second, if the

proposed decoder is implemented with a parallel architecture, the decoding latency is almost the same as a general turbo code

because D2 and D3 can decode received sequences simultaneously.

V.

SIMULATION RESULTS

This section presents the performances of the proposed HCCC (PHCCC). The generator polynomials of component codes are

G0 111 and G1 101 . The length of random interleavers are N=1024, 4096 and 8192 bits and BPSK modulation over

AWGN channel is used for simulation. And the Divsalar-Pollara HCCC of code rate = 1/4 [6] is constructed by an outer NSC

code, a parallel RSC code and an inner RSC code, as well as two interleavers of length N and 2N.

Fig. 3 shows the BER performance of PHCCC and GTC with the frame length of 1024, 4096 and 8192 bits, in 8 iterations.

For the frame of same length, the BER curve of PHCCC intersects that of GTC at a very low SNR. For example, the BER

curves of GTC-8k and PHCCC-8k intersect at 0.7dB. Also, the BER performance of PHCCC is slightly worse than that of

GTC when the SNR is below the intersection.

However, the PHCCC is much better than the GTC if SNR is larger than the intersection. For example, with the frame length

of N=8192 bits, the PHCCC achieves about 1.0 dB additional coding gain compared to the GTC at a BER 106 .

Furthermore, the BER of PHCCC can be dramatically reduced when the SNR is increased slightly. This advantage is useful

for applications in which high reliability is required.

FIG.3 BER PERFORMANCE OF PHCCC, R=1/3

Page | 140

International Journal of Engineering Research & Science (IJOER)

ISSN: [2395-6992]

[Vol-2, Issue-3 March- 2016]

FIG.4 BER PERFORMANCE OF PHCCC, R=1/4

From Fig. 4, the BER performance of PHCCC is slightly worse than that of the HCCC in [6]. However, comparing the

decoder structure of the PHCCC with that of the Divsalar-Pollara HCCC, there are some points worthy to be noted. The

length of interleavers in the Divsalar-Pollara HCCC is different (i.e., N and 2N). Therefore, for each iteration, the decoding

latency caused by interleavers and de-interleavers in the Divsalar-Pollara HCCC is 4N. Furthermore, if we assume the

computation complexity of decoding a four-state convolutional code is u, the computation complexity of the Divsalar-Pollara

HCCC is 6u. The comparisons are summarized in Table. Thus, the system complexities and decoding latency of the PHCCC

are lower than that of HCCC in [6] within acceptable BER degradation.

TABLE1

COMPARISONS OF THE PROPOSED HCCC SCHEME WITH THE HCCC IN [6]

VI.

CONCLUSIONS AND REMARKS

An enhanced hybrid concatenated convolutional code (HCCC) is proposed based on a modified Log-MAP algorithm.

Simulation results are given to demonstrate these modifications being efficient and practical to construct the HCCC.

Although the BER of the proposed HCCC is slightly worse than a general turbo code when the SNR is very low, it is much

better than the latter when the SNR is increased slightly. Comparisons of the proposed HCCC with the Divsalar-Pollara

HCCC are given in Table1. From the table, it is easy to see that both the system complexity and the decoding latency of the

proposed HCCC are much lower than the latter, with slight BER degradation.

REFERENCES

[1] C. Berrou, A. Glavieux and P. Thitimajshima, Near Shannon limit error-correcting coding and decoding: Turbo codes (1), Proc.

IEEE Int. Conf. Comm., pp. 10641070, Geneva, Switzerland, May 1993.

Page | 141

International Journal of Engineering Research & Science (IJOER)

ISSN: [2395-6992]

[Vol-2, Issue-3 March- 2016]

[2] Third Generation Partnership Project, www.3gpp.org.

[3] S. Benedetto, D. Divsalar, G. Montorsi, and F. Pollara, Soft-output decoding algorithms in iterative decoding of turbo codes, JPL

TDA Progress Rep. 42-124, pp. 63-87, Feb. 15 1996.

[4] L. Hanzo, T. H. Liew and B. L. Yeap, Turbo Coding, Turbo Equalisation and Space-Time Coding for Transmission over Fading

Channels, John Wiley & Sons Ltd, 2002.

[5] S. Benedetto, D. Divsalar, G. Montorsi, and F. Pollara, Serial concatenation of interleaved codes: performance analysis, design and

iterative decoding, IEEE Trans. Info. Theory, vol. 44, no. 3, pp. 909926, May 1998.

[6] D. Divsalar and F. Pollara, Hybrid concatenated codes and iterative decoding, JPL TDA Progress Rep. 42-130, pp. 1-23, Aug. 15

1997.

[7] P. Robertson, P. Hoeher and E. Villebrun, Optimal and sub-optimal Maximum a Posteriori algorithms suitable for turbo decoding,

European Transactions on Telecomm. (ETT), vol. 8, no. 2, 1997, pp.119-125.

[8] D. H. Kim and S. W. Kim, Bit-level stopping of turbo decoding, IEEE Comm. Lett., vol. 10, pp. 183185, Mar. 2006.

Page | 142

You might also like

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyFrom EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo ratings yet

- Constant Log BCJR Turbo Decoder With Pipelined ArchitectureDocument5 pagesConstant Log BCJR Turbo Decoder With Pipelined ArchitectureInternational Journal of Scientific Research and Engineering StudiesNo ratings yet

- Rate MatchingDocument5 pagesRate MatchingvgguhaNo ratings yet

- Iterative Data Detection and Channel Estimation for SPC-PC Coded MIMO SystemsDocument5 pagesIterative Data Detection and Channel Estimation for SPC-PC Coded MIMO SystemsIsa FirmantoNo ratings yet

- STBCDocument25 pagesSTBCNagarjuna SiddhuNo ratings yet

- Review Paper On Performance Evaluation of BPSK and QPSK Modulation With LDPC CodesDocument5 pagesReview Paper On Performance Evaluation of BPSK and QPSK Modulation With LDPC CodesSatyendra 'Best Among Truths'No ratings yet

- Output Feedback Stabilization of Wireless Networked Control System With Packet DropoutDocument6 pagesOutput Feedback Stabilization of Wireless Networked Control System With Packet DropoutMicuko OšinokoNo ratings yet

- High-Speed OpticalDocument4 pagesHigh-Speed OpticalRini KamilNo ratings yet

- Engineering Journal Controller Design For Nonlinear Networked Control Systems With Random Data Packet DropoutDocument6 pagesEngineering Journal Controller Design For Nonlinear Networked Control Systems With Random Data Packet DropoutEngineering JournalNo ratings yet

- 2009 Ko 02Document5 pages2009 Ko 02Stratos PsNo ratings yet

- Illuminating the Structure and Decoder of Parallel Concatenated Turbo CodesDocument6 pagesIlluminating the Structure and Decoder of Parallel Concatenated Turbo Codessinne4No ratings yet

- RK4 MethodDocument6 pagesRK4 MethodfurqanhamidNo ratings yet

- Low-Power, High-Speed FFT Processor For MB-OFDM UWB ApplicationDocument10 pagesLow-Power, High-Speed FFT Processor For MB-OFDM UWB ApplicationPhuc HoangNo ratings yet

- Modified Carry Select Adder Using Binary Adder As A BEC-1Document18 pagesModified Carry Select Adder Using Binary Adder As A BEC-1Sesharatnam KoppulaNo ratings yet

- RC LDPC Dec OpexDocument7 pagesRC LDPC Dec OpexAyodele Emmanuel SonugaNo ratings yet

- Performance of COFDM Using Turbo Codes: Primary Technical Subject Area: Radio CommunicationDocument11 pagesPerformance of COFDM Using Turbo Codes: Primary Technical Subject Area: Radio Communicationmsachemo1No ratings yet

- Comparative Study of Turbo Codes Decoding Methods (MAP and SOVADocument14 pagesComparative Study of Turbo Codes Decoding Methods (MAP and SOVAyemineniraj33No ratings yet

- FPGA Implementation of Encoder For (15, K) Binary BCH Code Using VHDL and Performance Comparison For Multiple Error Correction ControlDocument5 pagesFPGA Implementation of Encoder For (15, K) Binary BCH Code Using VHDL and Performance Comparison For Multiple Error Correction ControlDaniel Meton da SilvaNo ratings yet

- High Throughput, Parallel, Scalable LDPC Encoder/Decoder Architecture For Ofdm SystemsDocument4 pagesHigh Throughput, Parallel, Scalable LDPC Encoder/Decoder Architecture For Ofdm Systemssandeepkarnati11No ratings yet

- Performance of Coded Offset Quadrature Phase-Shift Keying (OQPSK) and MIL-STD Shaped OQPSK (SOQPSK) With Iterative DecodingDocument25 pagesPerformance of Coded Offset Quadrature Phase-Shift Keying (OQPSK) and MIL-STD Shaped OQPSK (SOQPSK) With Iterative Decodingmohamed MostafaNo ratings yet

- Low-Cost Design of Serial-Parallel Multipliers Over GF (2) Using Hybrid Pass-Transistor Logic (PTL) and CMOS LogicDocument4 pagesLow-Cost Design of Serial-Parallel Multipliers Over GF (2) Using Hybrid Pass-Transistor Logic (PTL) and CMOS LogicRamadasu PoornimaNo ratings yet

- Design and Implementation of Early-Late Gate Bit Synchronizer For Satellite CommunicationDocument4 pagesDesign and Implementation of Early-Late Gate Bit Synchronizer For Satellite CommunicationMatthew CarterNo ratings yet

- International Journal of Engineering Research and Development (IJERD)Document7 pagesInternational Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- Carrier Modulation: Version 2 ECE IIT, KharagpurDocument9 pagesCarrier Modulation: Version 2 ECE IIT, KharagpurRupaShaw100% (1)

- Inner and Outer Decoding Performance of Convolutional Codes: MelindaDocument6 pagesInner and Outer Decoding Performance of Convolutional Codes: MelindaAiShaKhanNo ratings yet

- An Analysis of Pilot Symbol Assisted Modulation Rayleigh Fading ChannelsDocument8 pagesAn Analysis of Pilot Symbol Assisted Modulation Rayleigh Fading ChannelsBrijesh GuptaNo ratings yet

- Question Bank For DLCDocument8 pagesQuestion Bank For DLCAvina AshNo ratings yet

- Fast Parallel Decoding of Generalized LDPC Codes Using FFTDocument3 pagesFast Parallel Decoding of Generalized LDPC Codes Using FFTYue MinNo ratings yet

- Diversity and Multiplexing Techniques of 802.11n WLAN: Maciej KrasickiDocument5 pagesDiversity and Multiplexing Techniques of 802.11n WLAN: Maciej Krasickizizo1921No ratings yet

- Coded Modulation in Optical Communications: Otho1.Pdf Otho1 PDFDocument3 pagesCoded Modulation in Optical Communications: Otho1.Pdf Otho1 PDFAnthony WellsNo ratings yet

- QPSK Modulation and Error Correcting CodesDocument21 pagesQPSK Modulation and Error Correcting CodesSIRISHASIRIINo ratings yet

- Stefanica 2019 - VolatilityDocument29 pagesStefanica 2019 - VolatilitypukkapadNo ratings yet

- Uwb Isbc2010 Full PaperDocument5 pagesUwb Isbc2010 Full PaperUche ChudeNo ratings yet

- Comparison of SIR Estimation Techniques For Closed-Loop Power Control in The W-CDMA SystemDocument5 pagesComparison of SIR Estimation Techniques For Closed-Loop Power Control in The W-CDMA SystemTran Quang ThanhNo ratings yet

- Analog FFT Interface For Ultra-Low Power Analog Receiver ArchitecturesDocument4 pagesAnalog FFT Interface For Ultra-Low Power Analog Receiver ArchitecturesNathan ImigNo ratings yet

- Performance of An L-SC Receiver Over Kappa-Mu and Eta-Mu Fading ChannelsDocument5 pagesPerformance of An L-SC Receiver Over Kappa-Mu and Eta-Mu Fading ChannelsAhmad Husain HijaziNo ratings yet

- Performance Analysis of Incremental Redundancy Hybrid ARQ Schemes With Parallel Concatenated LDPC CodesDocument3 pagesPerformance Analysis of Incremental Redundancy Hybrid ARQ Schemes With Parallel Concatenated LDPC Codesawais04No ratings yet

- Reduced-Latency SC Polar Decoder Architectures: Chuan Zhang, Bo Yuan, and Keshab K. ParhiDocument5 pagesReduced-Latency SC Polar Decoder Architectures: Chuan Zhang, Bo Yuan, and Keshab K. ParhiFebru ekoNo ratings yet

- An Analysis of Pilot Symbol Assisted Modulation Rayleigh Fading ChannelsDocument8 pagesAn Analysis of Pilot Symbol Assisted Modulation Rayleigh Fading ChannelsjdnfjngsNo ratings yet

- Design A Scalable RSA and ECC Crypto-ProcessorDocument4 pagesDesign A Scalable RSA and ECC Crypto-ProcessorVinayak KumarNo ratings yet

- An Efficient Modified High Speed Square Root Carry Select AdderDocument4 pagesAn Efficient Modified High Speed Square Root Carry Select Addervanchip28No ratings yet

- Carrier Modulation: Version 2 ECE IIT, KharagpurDocument13 pagesCarrier Modulation: Version 2 ECE IIT, KharagpurRupaShawNo ratings yet

- Fast Liste DecodingDocument7 pagesFast Liste DecodingMohamed LamriniNo ratings yet

- DCT From NptelDocument17 pagesDCT From NptelFarooq BhatNo ratings yet

- Low-Density Parity-Check Codes Over Gaussian Channels With ErasuresDocument9 pagesLow-Density Parity-Check Codes Over Gaussian Channels With ErasuresBoazShuvalNo ratings yet

- 32 Bit Kogge Stone Based Hybrid Adder Implemented Using Standard Cells of Different Logic FamiliesDocument9 pages32 Bit Kogge Stone Based Hybrid Adder Implemented Using Standard Cells of Different Logic FamiliesDivya DewkatheNo ratings yet

- Self-Cancellation Method of Ofdm Ici: Ze Zhu, Xiang Tang, Jizhang ZuoDocument5 pagesSelf-Cancellation Method of Ofdm Ici: Ze Zhu, Xiang Tang, Jizhang ZuoShaimaa El SayedNo ratings yet

- Parallel Implementation of A 4 X 4-Bit MultiplierDocument4 pagesParallel Implementation of A 4 X 4-Bit MultiplierMathew GeorgeNo ratings yet

- Concatenated Turbo/LDPC Codes For Deep Space Communications: Performance and ImplementationDocument6 pagesConcatenated Turbo/LDPC Codes For Deep Space Communications: Performance and ImplementationmkawserNo ratings yet

- Karunya University: End Semester Examination - April/May 2011Document2 pagesKarunya University: End Semester Examination - April/May 2011Catherine JoyNo ratings yet

- Decoding of The Extended Golay Code by The Simplified Successive-Cancellation List Decoder Adapted To Multi-Kernel Polar CodesDocument9 pagesDecoding of The Extended Golay Code by The Simplified Successive-Cancellation List Decoder Adapted To Multi-Kernel Polar CodesTELKOMNIKANo ratings yet

- Convolutional Coding and Viterbi Decoding ExplainedDocument30 pagesConvolutional Coding and Viterbi Decoding ExplainedEmNo ratings yet

- EECT6306 Miidterm Project Harshit VamshiDocument13 pagesEECT6306 Miidterm Project Harshit Vamshiafrica threeNo ratings yet

- Integrated Digital Architecture For JPEG Image Compression: Luciano Agostini and Sergio BampiDocument4 pagesIntegrated Digital Architecture For JPEG Image Compression: Luciano Agostini and Sergio Bampielhenshire_hNo ratings yet

- Optimization: MVSIS V/s AIG Rewriting (ABC)Document5 pagesOptimization: MVSIS V/s AIG Rewriting (ABC)International Journal of Electrical and Electronics EngineeringNo ratings yet

- Neural Network Based Receiver For Multiuser Detection in MC-CDMA SystemsDocument10 pagesNeural Network Based Receiver For Multiuser Detection in MC-CDMA SystemsAnubhavNo ratings yet

- Seampless Pipelined PDFDocument6 pagesSeampless Pipelined PDFCherry AnushaNo ratings yet

- Engineering Journal Comparative Study of Various Pre-Treatments Coupled To Vacuum Drying in Terms of Structural, Functional and Physical Properties of Carrot DaucusCarotaDocument15 pagesEngineering Journal Comparative Study of Various Pre-Treatments Coupled To Vacuum Drying in Terms of Structural, Functional and Physical Properties of Carrot DaucusCarotaEngineering JournalNo ratings yet

- Engineering Journal Preparation and Characterization of Cross-Linked Polymer Supports For Catalysts ImmobilizationDocument24 pagesEngineering Journal Preparation and Characterization of Cross-Linked Polymer Supports For Catalysts ImmobilizationEngineering JournalNo ratings yet

- Engineering Journal A Professional PID Implemented Using A Non-Singleton Type-1 Fuzzy Logic System To Control A Stepper MotorDocument8 pagesEngineering Journal A Professional PID Implemented Using A Non-Singleton Type-1 Fuzzy Logic System To Control A Stepper MotorEngineering JournalNo ratings yet

- Engineering Journal Role of Indian Spices in Cancer Prevention: A ReviewDocument2 pagesEngineering Journal Role of Indian Spices in Cancer Prevention: A ReviewEngineering JournalNo ratings yet

- Engineering Journal Micromechanics of Thermoelastic Behavior of AA6070 Alloy/Zirconium Oxide Nanoparticle Metal Matrix CompositesDocument3 pagesEngineering Journal Micromechanics of Thermoelastic Behavior of AA6070 Alloy/Zirconium Oxide Nanoparticle Metal Matrix CompositesEngineering JournalNo ratings yet

- Engineering Journal Thermo-Mechanical Fatigue Behavior of A Copper-Alumina Metal Matrix Composite With Interpenetrating Network StructureDocument9 pagesEngineering Journal Thermo-Mechanical Fatigue Behavior of A Copper-Alumina Metal Matrix Composite With Interpenetrating Network StructureEngineering JournalNo ratings yet

- Engineering Journal Online Tuning of The Fuzzy PID Controller Using The Back-Propagation AlgorithmDocument8 pagesEngineering Journal Online Tuning of The Fuzzy PID Controller Using The Back-Propagation AlgorithmEngineering JournalNo ratings yet

- Engineering Journal Numerical Study of Microbial Depolymerization Process With The Newton-Raphson Method and The Newton's MethodDocument12 pagesEngineering Journal Numerical Study of Microbial Depolymerization Process With The Newton-Raphson Method and The Newton's MethodEngineering JournalNo ratings yet

- Engineering Journal Estimation of Rolling-Contact Bearings Operational Properties by Electrical Probe MethodDocument7 pagesEngineering Journal Estimation of Rolling-Contact Bearings Operational Properties by Electrical Probe MethodEngineering JournalNo ratings yet

- Engineering Journal Effects of Soil Physical and Chemical Properties On The Distribution of Trees in Some Ecological Zones of Zalingei-Darfur SudanDocument9 pagesEngineering Journal Effects of Soil Physical and Chemical Properties On The Distribution of Trees in Some Ecological Zones of Zalingei-Darfur SudanEngineering JournalNo ratings yet

- Engineering Journal Isomorphic Transformation of The Lorenz Equations Into A Single-Control-Parameter StructureDocument9 pagesEngineering Journal Isomorphic Transformation of The Lorenz Equations Into A Single-Control-Parameter StructureEngineering JournalNo ratings yet

- Engineering Journal The Microorganism Contamination Affect The Physical and Chemical Composition of MilkDocument7 pagesEngineering Journal The Microorganism Contamination Affect The Physical and Chemical Composition of MilkEngineering JournalNo ratings yet

- Engineering Journal Controller Design For Nonlinear Networked Control Systems With Random Data Packet DropoutDocument6 pagesEngineering Journal Controller Design For Nonlinear Networked Control Systems With Random Data Packet DropoutEngineering JournalNo ratings yet

- Engineering Journal Strategic and Operational Scope of Foreign Subsidiary UnitsDocument11 pagesEngineering Journal Strategic and Operational Scope of Foreign Subsidiary UnitsEngineering JournalNo ratings yet

- Engineering Journal Analysis of Vibro-Isolated Building Excited by The Technical Seismicity of Traffic EffectsDocument6 pagesEngineering Journal Analysis of Vibro-Isolated Building Excited by The Technical Seismicity of Traffic EffectsEngineering JournalNo ratings yet

- Engineering Journal Securing of Elderly Houses in Term of Elderly's Vision DisordersDocument10 pagesEngineering Journal Securing of Elderly Houses in Term of Elderly's Vision DisordersEngineering JournalNo ratings yet

- Engineering Journal Impact of Texturing/cooling by Instant Controlled Pressure Drop DIC On Pressing And/or Solvent Extraction of Vegetal OilDocument12 pagesEngineering Journal Impact of Texturing/cooling by Instant Controlled Pressure Drop DIC On Pressing And/or Solvent Extraction of Vegetal OilEngineering JournalNo ratings yet

- Engineering Journal Alteration of Pelvic Floor Biometry in Different Modes of DeliveryDocument7 pagesEngineering Journal Alteration of Pelvic Floor Biometry in Different Modes of DeliveryEngineering JournalNo ratings yet

- Engineering Journal A Systematic Approach To Stable Components Synthesis From Legacy ApplicationsDocument10 pagesEngineering Journal A Systematic Approach To Stable Components Synthesis From Legacy ApplicationsEngineering JournalNo ratings yet

- Engineering Journal A Silicon-Containing Polytriazole Resin With Long Storage TimeDocument9 pagesEngineering Journal A Silicon-Containing Polytriazole Resin With Long Storage TimeEngineering JournalNo ratings yet

- Engineering Journal Study of Different Surface Pre-Treatment Methods On Bonding Strength of Multilayer Aluminum Alloys/Steel Clad MaterialDocument9 pagesEngineering Journal Study of Different Surface Pre-Treatment Methods On Bonding Strength of Multilayer Aluminum Alloys/Steel Clad MaterialEngineering JournalNo ratings yet

- Engineering Journal A Novel Oxygenator-Right Ventricular Assist Device Circuit Using The SYNERGY Micropump As Right Heart Support in A Swine Model of Pulmonary HypertensionDocument8 pagesEngineering Journal A Novel Oxygenator-Right Ventricular Assist Device Circuit Using The SYNERGY Micropump As Right Heart Support in A Swine Model of Pulmonary HypertensionEngineering JournalNo ratings yet

- Engineering Journal Power Improvement in 32-Bit Full Adder Using Embedded TechnologiesDocument8 pagesEngineering Journal Power Improvement in 32-Bit Full Adder Using Embedded TechnologiesEngineering JournalNo ratings yet

- Engineering Journal Bio-Oil Production by Thermal Cracking in The Presence of HydrogenDocument20 pagesEngineering Journal Bio-Oil Production by Thermal Cracking in The Presence of HydrogenEngineering JournalNo ratings yet

- Engineering Journal Factors Influencing Grid Interactive Biomass Power IndustryDocument12 pagesEngineering Journal Factors Influencing Grid Interactive Biomass Power IndustryEngineering JournalNo ratings yet

- Engineering Journal Extracorporal Shock Wave Induced Mechanical Transduction For The Treatment of Low Back Pain - A Randomized Controlled TrialDocument6 pagesEngineering Journal Extracorporal Shock Wave Induced Mechanical Transduction For The Treatment of Low Back Pain - A Randomized Controlled TrialEngineering JournalNo ratings yet

- Engineering Journal Salicylic Acid Enhanced Phytoremediation of Lead by Maize (Zea Mays) PlantDocument7 pagesEngineering Journal Salicylic Acid Enhanced Phytoremediation of Lead by Maize (Zea Mays) PlantEngineering JournalNo ratings yet

- Engineering Journal Studies On Stigma Receptivity of Grewia Asiatica L. With Reference To Esterase and Peroxidase ActivityDocument4 pagesEngineering Journal Studies On Stigma Receptivity of Grewia Asiatica L. With Reference To Esterase and Peroxidase ActivityEngineering JournalNo ratings yet

- Engineering Journal The Sinkhole Hazard Study at Casalabate (Lecce, Italy) Using Geophysical and Geological SurveysDocument11 pagesEngineering Journal The Sinkhole Hazard Study at Casalabate (Lecce, Italy) Using Geophysical and Geological SurveysEngineering JournalNo ratings yet

- Engineering Journal Estimation of Global Solar Radiation Using Artificial Neural Network in Kathmandu, NepalDocument9 pagesEngineering Journal Estimation of Global Solar Radiation Using Artificial Neural Network in Kathmandu, NepalEngineering JournalNo ratings yet

- SLU Lab Manual Activity on Error Control CodingDocument4 pagesSLU Lab Manual Activity on Error Control CodingSM MecregNo ratings yet

- Introduction To Information TheoryDocument178 pagesIntroduction To Information Theoryvoip5430150% (2)

- TCOM 370: NOTES 99-10 Data CompressionDocument19 pagesTCOM 370: NOTES 99-10 Data CompressionRohan BorgalliNo ratings yet

- Detect and Correct Errors with CodesDocument16 pagesDetect and Correct Errors with CodesnarendraNo ratings yet

- Gavotte - Tuba SoloDocument1 pageGavotte - Tuba SoloJesús David Pérez GarridoNo ratings yet

- KKJJJDocument2 pagesKKJJJAndrosabak communityNo ratings yet

- Linear Block Codes PDFDocument27 pagesLinear Block Codes PDFdup acountNo ratings yet

- Quiz Based On CO 3 Data Compression (RCS - 087) : Email AddressDocument4 pagesQuiz Based On CO 3 Data Compression (RCS - 087) : Email AddressAnchit AggarwalNo ratings yet

- 1 Lesson2 DigitalCommunicationDocument10 pages1 Lesson2 DigitalCommunicationQhadija JulkanainNo ratings yet

- Compression and DecompressionDocument19 pagesCompression and DecompressionkarthickamsecNo ratings yet

- Laboratory Journal: Signal Coding Estimation TheoryDocument63 pagesLaboratory Journal: Signal Coding Estimation Theoryrudra_1No ratings yet

- ECE Course ListDocument12 pagesECE Course Listkittyk2No ratings yet

- DLLDocument51 pagesDLLSohil SharmaNo ratings yet

- Coding TheoryDocument5 pagesCoding TheoryfiraszekiNo ratings yet

- Kick BackDocument3 pagesKick Backeric greenNo ratings yet

- LDPCDocument20 pagesLDPCRahul KumarNo ratings yet

- Gargi Sharma Viterbi Algorithm Term Paper EEL201Document4 pagesGargi Sharma Viterbi Algorithm Term Paper EEL201Gaurav NavalNo ratings yet

- HTML 101Document2 pagesHTML 101Isam el-laymounyNo ratings yet

- Lecture16 - Error DetectionDocument41 pagesLecture16 - Error DetectionrashmiNo ratings yet

- Data CompressionDocument49 pagesData CompressionAakash MahajanNo ratings yet

- Torrent Downloaded From ExtraTorrent - CCDocument2 pagesTorrent Downloaded From ExtraTorrent - CCjoaow95No ratings yet

- Chapter 0 IntroductionDocument18 pagesChapter 0 IntroductionGnitNo ratings yet

- Lab 3Document3 pagesLab 3viswanathrd45No ratings yet

- Course DescriptionDocument12 pagesCourse DescriptionEKS SANTIAGONo ratings yet

- EXP5Document10 pagesEXP51932-Aditi KiniNo ratings yet

- TraceDocument152 pagesTraceabdulhanif97No ratings yet

- ELEC1010 Homework 4 Huffman Coding and Parity Check CodeDocument3 pagesELEC1010 Homework 4 Huffman Coding and Parity Check CodeYuen Hei Max LeeNo ratings yet

- Sensebot LogDocument21 pagesSensebot Logarvika n.sNo ratings yet

- Experiment No 5 Aim: To Study and Implement Convolution Codes. Requirement: GCC C Compiler. TheoryDocument3 pagesExperiment No 5 Aim: To Study and Implement Convolution Codes. Requirement: GCC C Compiler. TheoryprajaktiNo ratings yet