Professional Documents

Culture Documents

LPFSM Report

Uploaded by

RAMIZKHAN1240 ratings0% found this document useful (0 votes)

17 views5 pagesrr

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentrr

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

17 views5 pagesLPFSM Report

Uploaded by

RAMIZKHAN124rr

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 5

Low Power Finite State Machines

K N Indraja Ramiz Mahaboob Shruti Narake

Dept. of ECE, MIT Dept. of ECE, MIT Dept. of ECE, MIT

Abstract Finite State Machines (FSM) are the high-Vth cells that uses fewer cells overall. It is for this

compact way to represent a set of complex rules and reason that these trade-offs should be considered early in

conditions, and to process various inputs. These are the synthesis process. A better approach for synthesis using

used in every digital logic nowadays for efficient logic multi Vth cells is to create a post-logic-synthesis routine

design. But the higher power consumption of latest that replaces low-Vth cells with high-Vth cells as long as

technology nodes has to be rectified by a different the timing constraints and other design rules and

design technique of FSM. In this paper, our focus is on constraints are not violated. A more sophisticated approach

reduction of power consumption by partitioning the used during synthesis incorporates the leakage power as a

FSM and make it into a different instance so that component of the optimizations objective function. Here,

Multiple Threshold Voltage and Multiple Supply it is important to have libraries that have been properly

Voltage for different instances can be easily characterized to perform this type of optimization.

implemented in the synthesis and physical design

stage. II. METHODOLOGY

Index Terms FSM, Multiple Threshold Voltage,

Multiple Supply Voltage, CPF

A. FSM Partitioning

I. INTRODUCTION

FSM can be partitioned into smaller pieces. The idea

The shift in the use of chips to consumer applications and here is to decompose a large FSM into several simpler

the change in the latest process technologies have made FSMs with smaller state registers and combinatorial logic

power one of the primary design criteria for a majority of blocks. Only the active FSM receives clock and switching

the chips worldwide. However, the industrys design inputs. The others are static and do not consume any

infrastructure has not evolved at the same pace. Now the dynamic power. We consider a large FSM that includes a

focus is to reduce both the dynamic and leakage power of small subroutine, which is used very often in a real

the end product. For the commercial success of the device, application scenario. We can easily partition the big FSM

low power design methodologies are very much needed. into two parts and isolate the subroutine loop. Figure 1

Since many of these applications are control-dominated, shows an FSM decomposed into two simpler FSMs. The

efficient low power realization of a controller as an FSM new FSMs are mutually exclusive; when one is operating,

has emerged as a challenging task. the other one remains off. In such a state, clock and inputs

A lot of work has been done in finite state machine can be gated to prevent any dynamic power (power supply

synthesis and state encoding targeting low power in [1,2, 3, could even be switched off to save leakage). The power

4, 5, 6]. Partitioning has been shown to be a very effective savings is even higher if we can isolate very small subsets

technique for reducing power in FSMs. Low power FSM of states where the initial FSM remains most of the time.

partition techniques have been addressed in a number of

references. The principle behind the partition technique is

that a main FSM is partitioned into a number of sub-FSMs

but only one machine is activated while others are disabled,

which could lead to power savings. The Active Sub-FSM

(ASFSM) is in control. When the next input signal comes,

the ASFSM either remains active or it is turned off while

the other one is turned on and set to a correct state.

Silicon foundries have started to offer multiple threshold

devices at the same process node to address the need to

control leakage current and enabling designers to trade off

leakage and performance. From the standard Vth, a low-

and high-Vth transistor may be offered. It is not uncommon

Figure 1: FSM Decomposition

for the low-Vth device to have an order of magnitude

higher leakage than the standard Vth device and the high-

Vth device to have leakage characteristics an order of B. Multiple Threshold voltage

magnitude below the standard. For special applications, a

special low-leakage device may exist that will reduce the

Leakage power is the power dissipated by current

leakage further by another order of magnitude. This

leaks in the transistors. The leakage power is usually

reduction in leakage comes at the expense of the speed of

modelled in the library as a constant. The availability of

the device. A design with a higher percentage of high-Vth

two or more threshold voltages on the same chip (multiple-

cells may appear to be better at first glance, but it could

Vth process) provides the opportunity to make trade-offs

also be inferior to a design with a lower percentage of

between power and performance. If you load multiple

libraries containing cells with different threshold voltages, When signals pass between portions of the design that are

the RC-LP engine can make tradeoffs between timing and operating at different voltages, level shifters are needed.

leakage power during synthesis. Level shifter are the interface circuit used when VDD low

When multiple threshold voltage (Vth) libraries are cells drive VDD high cells in order to avoid leakage.

provided, the synthesis tool can further optimize leakage The Common Power Format (CPF) file captures the

power by utilizing high Vth cells (low leakage power, slow information described above in a text file. The CPF file is a

timing performance) along the non-critical timing paths, power specification file. This implies that the functionality

and low Vth cells (higher leakage power, faster timing of the design does not change when sourcing a CPF file.

performance) on timing-critical paths. Depending on the The CPF file complements the HDL description of the

design requirements, you can choose different optimization design and can be used throughout the design creation,

effort levels for leakage power optimization with multiple design implementation, and design verification flow.

Vth libraries. This design includes partitioned FSM with a top module

If you set power constraints, Cadence Encounter RTL and an instance operating in two power domains: PD1

Compiler performs timing, area, and power optimization operating at 1.4V & PD2 operating at 1.62V. PD1 includes

simultaneously. The tool tries to meet timing constraints, the top module and PD2 includes the instance. A suitable

while balancing area and power. By allowing the area to level shifter is placed between these two domains. This

increase, you can get better power results. To control the design has 2 input pins clock and reset thus level shifters

tradeoff between area and power, the power optimization are placed in clock and reset pins belonging to different

effort root attribute can be set. power domains. A CPF file is written to capture this

information.

C. Multiple supply voltage design

III. EXPERIMENTAL RESULTS

One of the techniques to reduce dynamic power

consumption in system on chip is to reduce supply voltage.

A FSM Partitioning

Multiple Supply Voltage (MSV) design is one such

technique provided by low power engine in Cadence

Encounter RTL compiler to reduce the power supply. A The FSM design was partitioned into top module

Multiple Supply Voltage (MSV) design uses multiple and an instance and clock gated accordingly. The synthesis

supply voltages for the core logic and for the different was carried out using Cadence Encounter RTL Compiler.

instances in the design. A portion of the design that The partitioned design achieved 24% power saving without

operates at the same operating voltage (that is, uses the affecting the design timing constraints in 45nm technology.

same main power supply) belongs to the power domain Table 1 shows the power report comparison for different

that corresponds to that operating voltage. Standard cell technologies.

libraries are characterized based on operating conditions.

The blocks operating on a particular voltage need to use the

libraries characterized for that particular voltage. The

libraries which are operating at the same nominal operating

conditions are grouped under a library set. Figure 2 shows

FSM top module and partitioned instance with respective

power domains.

Table 1: Power report comparison of Non-partitioned and

Partitioned Design for different technology nodes.

B Multiple Threshold voltage

The partitioned FSM was constrained at 400MHz

(2.5ns time period). Using Cadence Encounter RTL

Figure 2: FSM top module and partitioned instance with

Compiler, the leakage power was reduced using multiple

respective power domains

threshold voltage cells available in the library at 45nm

technology. The method achieved 50% total power saving

and 77% leakage power saving. Table 2 shows Power

report comparison with and without Multiple Threshold

Voltage.

Table 2: Power report comparison with and without

Multiple Threshold Voltage

Figure 3: Synthesized design after insertion of level shifter

The critical path was analyzed before and after the cell

method was incorporated. As the slack was positive in the

critical path, the leakage power in the critical path was

reduced by using high Vth cells from library with an IV. CONCLUSION

increase in the delay. Table 3 shows the critical path delay

and leakage power comparison. In this work, an effective technique of Multiple supply

voltage considering the problem of partitioning of FSM for

low power has been explored. Significant amount of power

saving has been achieved using this technique. During the

execution of our method, power is being estimated using

Cadence Encounter RTL Compiler which gives leakage

power after the use of Multiple threshold voltage. The

partitioned FSM with separate power domains are

synthesized using Cadence synthesis tool at 45nm

technology and leakage power as well as switching power

Table 3: Critical path delay and leakage power for the sequential circuit has been reported. Our method

comparison achieved good leakage power saving also. In this work, the

area overhead is not considered. Our future work will focus

on these aspects with power gating.

C Multiple supply voltage design

REFERENCES

The proposed method was implemented using

Cadence Encounter RTL Compiler low power engine. The

partitioned design achieved 19% power saving without

affecting the design timing constraints in 180nm [1] F. Najm, A survey of Power Estimation Techniques in

technology. Table 4 shows the power reports. Level shifter VLSI Circuits (invited paper), IEEE Transaction on VLSI

standard cell LVLHLX8 was inserted between clock and Systems, 2(4):446-455, December 1994.

reset pins of the two power domains. Figure 3 shows the

synthesized design after insertion of level shifter cell. [2] S. Chattopadhyay, Low power state assignment and

flip-flop selection for finite state machine synthesis- A

Genetic Algorithm Approach, IEEE proceedings on

Computer and Digital Techniques vol.125, no. 4/5, pp. 124-

151, July 2001.

[3] L. Benini and G. De Micheli, State Assignment for

Low Power Dissipation, IEEE journal on Solid State

Table 4: Power report comparison with and without Circuits, pp.32- 40, March 1994.

Multiple Supply Voltage

[4] W. Noeth, R. Kolla. Spanning Tree-based State

Encoding for Low Power Dissipation, Design Automation

and Test in Europe, March 1999.

[5] Roy K., and S. Preasad, SYCLOP Synthesis of CMOS

Logic for Low Power Applications,. ICCD'92, pp.234-

237,1992. [8] Marco Terres, Cristina Meinhardt, Guilherme

Bontorin, Ricardo Reis - Exploring more efficient

[6] S. Devadas, H. K.T. Ma, A. R. Newton, and A.S. architectures for Multiple Dynamic Supply Voltage

Vincentelli, Mustang: State Assignment of Finite State designs. Circuits and Systems (LASCAS), 2014 IEEE 5th

Machines for Optimal Multilevel Logic Implementation, Latin American Symposium on

IEEE Transaction on Computer Aided Design, vol.7, No.

12,pp.1290-1300, December 1998. [9] Andrew B. Kahng. Jens LienigIgor L. Markov. Jin Hu

VLSI Physical Design: From Graph Partitioning to Timing

[7] Jui-Ming Chang-Energy minimization using multiple

Closure

supply voltage .IEEE Transactions on Very Large Scale

Integration (VLSI) Systems

[10] www.cadence.com/content/cadence

You might also like

- Ad VLSI Assignment Sheet 2 15112016Document1 pageAd VLSI Assignment Sheet 2 15112016RAMIZKHAN124No ratings yet

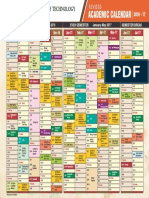

- AcademicCalender2016 17Document1 pageAcademicCalender2016 17RAMIZKHAN124No ratings yet

- S.R.Barath Apt TMN Street 1RKDocument3 pagesS.R.Barath Apt TMN Street 1RKRAMIZKHAN124No ratings yet

- Document outlines health and fitness topicsDocument9 pagesDocument outlines health and fitness topicsRAMIZKHAN124No ratings yet

- PG (ME) 2016-17 SyllabusDocument30 pagesPG (ME) 2016-17 SyllabusRAMIZKHAN124No ratings yet

- Assignment 3Document4 pagesAssignment 3RAMIZKHAN124No ratings yet

- Fpga V HDL C G: Erilog Oding UidelinesDocument9 pagesFpga V HDL C G: Erilog Oding UidelinesRAMIZKHAN124No ratings yet

- MinsocDocument22 pagesMinsocMunish JassiNo ratings yet

- Fin FetsDocument4 pagesFin FetsRAMIZKHAN124No ratings yet

- M.Jaseel Quest GlobalDocument25 pagesM.Jaseel Quest GlobalRAMIZKHAN124No ratings yet

- ADC and DAC Converters ExplainedDocument5 pagesADC and DAC Converters ExplainedMatthew AlexanderNo ratings yet

- Detecting PCI Devices: On Identifying The Peripheral Equipment Installed in Our PCDocument22 pagesDetecting PCI Devices: On Identifying The Peripheral Equipment Installed in Our PCRAMIZKHAN124No ratings yet

- Lec 30Document35 pagesLec 30RAMIZKHAN124No ratings yet

- HAL ReportGenerationDocument3 pagesHAL ReportGenerationRAMIZKHAN124No ratings yet

- Aicte Anti Ragging Notification - 1Document18 pagesAicte Anti Ragging Notification - 1RAMIZKHAN124No ratings yet

- Student Immunization RecordDocument2 pagesStudent Immunization RecordRAMIZKHAN124No ratings yet

- Print - Bill Gates - Wikipedia, The Free Encyclopedia PDFDocument16 pagesPrint - Bill Gates - Wikipedia, The Free Encyclopedia PDFRAMIZKHAN124No ratings yet

- Inmo 2015Document6 pagesInmo 2015Harshit KhardiaNo ratings yet

- Selected References: Ion ImplantationDocument34 pagesSelected References: Ion Implantationmskumar_554No ratings yet

- Anti Drugs DeclarationDocument1 pageAnti Drugs DeclarationGuru RaajNo ratings yet

- Lec 26Document31 pagesLec 26RAMIZKHAN124No ratings yet

- Colour Sensor PDFDocument3 pagesColour Sensor PDFRAMIZKHAN124No ratings yet

- DocumentDocument121 pagesDocumentRAMIZKHAN124No ratings yet

- Black Athena - Wikipedia, The Free EncyclopediaDocument6 pagesBlack Athena - Wikipedia, The Free EncyclopediaRAMIZKHAN124No ratings yet

- Best Way To LearnDocument3 pagesBest Way To LearnRAMIZKHAN124No ratings yet

- Mobile Colour Sensing Robot PDFDocument1 pageMobile Colour Sensing Robot PDFRAMIZKHAN124No ratings yet

- Anti Drugs DeclarationDocument1 pageAnti Drugs DeclarationGuru RaajNo ratings yet

- Final ReportDocument5 pagesFinal ReportRAMIZKHAN124No ratings yet

- William Montgomery Watt - Wikipedia, The Free EncyclopediaDocument3 pagesWilliam Montgomery Watt - Wikipedia, The Free EncyclopediaRAMIZKHAN124No ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- C2 - Enriched Viewing Comprehension - Ritu BhasinDocument2 pagesC2 - Enriched Viewing Comprehension - Ritu Bhasin4103511No ratings yet

- Response To Uluru StatementDocument7 pagesResponse To Uluru Statementapi-537450355No ratings yet

- HELE Grade 5 Worksheet#2Document2 pagesHELE Grade 5 Worksheet#2Roselyn NapatdanNo ratings yet

- Order ManagementDocument53 pagesOrder ManagementJamme CeraNo ratings yet

- Chapter Ten: Hebrew Weak VerbsDocument31 pagesChapter Ten: Hebrew Weak Verbssteffen han100% (5)

- Soal Uts English 1Document2 pagesSoal Uts English 1reshaseptiapNo ratings yet

- Red WheelbarrowDocument3 pagesRed WheelbarrowARJUN MURALINo ratings yet

- HD 2000 Sip - en - 2020Document51 pagesHD 2000 Sip - en - 2020Rodrígo escobarNo ratings yet

- Transformador de Estado SolidoDocument48 pagesTransformador de Estado SolidoBalo GrisNo ratings yet

- Sap-Press Cat 2016Document32 pagesSap-Press Cat 2016gowtham0% (1)

- MedicaljournalsDocument7 pagesMedicaljournalsH. MD EbrNo ratings yet

- Unit de Invatare RevizuitaDocument5 pagesUnit de Invatare RevizuitaMarioara CiobanuNo ratings yet

- Language Acquisition Guide UpdatedDocument83 pagesLanguage Acquisition Guide UpdatedMahesh BadgujarNo ratings yet

- Ozymandias Multiple Choice QuestionsDocument3 pagesOzymandias Multiple Choice QuestionsKumaresan Ramalingam80% (5)

- Equip Org Bahai Faith Bahai Christian Dialogue PDFDocument19 pagesEquip Org Bahai Faith Bahai Christian Dialogue PDFLuke HanscomNo ratings yet

- State of Stress and Strain in 2DDocument149 pagesState of Stress and Strain in 2DOloyede RidwanNo ratings yet

- Chyla, J. - Quarks, Partons and QCDDocument210 pagesChyla, J. - Quarks, Partons and QCDMarco FrascaNo ratings yet

- L A 1 L A 2 (PERSONAL LETTER) Devrina OliviaDocument9 pagesL A 1 L A 2 (PERSONAL LETTER) Devrina OliviaVina RohmatikaNo ratings yet

- General Audience AnalysisDocument4 pagesGeneral Audience AnalysisJohn Paul100% (8)

- J6-ARRAYS & String HandlingDocument29 pagesJ6-ARRAYS & String HandlingSri K.Gangadhar Rao Assistant ProfessorNo ratings yet

- SQL Interview Questions 2021Document18 pagesSQL Interview Questions 2021K RUKESHNo ratings yet

- Elena CicinskaiteDocument1 pageElena CicinskaiteAntonio AlvesNo ratings yet

- LDS Old Testament Notes 05: EnochDocument8 pagesLDS Old Testament Notes 05: EnochMike ParkerNo ratings yet

- Sci Cosim Octave-Scilab Co-Simulation Package: PKG Install - Forge SocketsDocument3 pagesSci Cosim Octave-Scilab Co-Simulation Package: PKG Install - Forge SocketsElias JNo ratings yet

- Oracle 9i Installation InstructionsDocument10 pagesOracle 9i Installation InstructionsGurusamy V100% (3)

- Control Break EventsDocument46 pagesControl Break EventsriteshNo ratings yet

- EASY Engineering Tools v3-0 ENDocument28 pagesEASY Engineering Tools v3-0 ENjujuescrNo ratings yet

- Referencing - Brief Guide To The Harvard System GreenwichDocument5 pagesReferencing - Brief Guide To The Harvard System GreenwichDerek LiowNo ratings yet

- Hartnell ENG 1A 4140 ReaderDocument52 pagesHartnell ENG 1A 4140 ReaderAndrew NavaNo ratings yet

- TNPSC General English MCQ PDFDocument137 pagesTNPSC General English MCQ PDFDiviya Pandiyan0% (1)