Professional Documents

Culture Documents

555 Application Circuits

555 Application Circuits

Uploaded by

gilmartCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

555 Application Circuits

555 Application Circuits

Uploaded by

gilmartCopyright:

Available Formats

css

Custom Silicon Solutions, Inc.

CSS555(C) Application Circuits

CSS555/CSS555C PART DESCRIPTION

The CSS555 is a micro-power version of the popular 555 Timer IC. It is pin-for-pin compatible with the

standard 555 timer and features an operating current under 5A. Its minimum supply voltage is 1.2V,

making it ideal for battery-operated applications. A six-decade programmable counter is included to

allow generation of long timing delays. The analog circuits are temperature compensated to provide

excellent stability over a wide temperature range. Configuration data for the counter is held in

EEPROM. A straightforward four-wire interface provides Read/Write access to the memory. The

CSS555C device includes an internal 100pF timing capacitor. Block diagrams of the standard 555 IC

and the CSS555C are shown below.

Standard 555 Timer Block Diagram

CSS555C Block Diagram

Custom Silicon Solutions, Inc. 2009 1 Version 1.0, May 2009

CSS555(C) Application Circuits

Application Circuits

The following 555 timer circuits have been assembled to help show the advantages of the CSS555C

timer. Its advanced features offer unique capabilities that can reduce power, decrease PCB area and

eliminate the external timing capacitor. These circuits demonstrate many of the basic 555 timer

functions. They can also be used as a starting point to improve existing timer circuits or to develop new

ones.

Miscellaneous Notes

Power Supply Bypassing: The original 555 Timer ICs were made using a bipolar technology and

required significant power supply bypassing (like early digital TTL ICs). Current spikes during output

transitions could exceed 250mA. The CSS555C employs a break-before-make CMOS output driver

that eliminates these spikes. Minimal supply bypassing is therefore required. A 0.001 uF capacitor is

usually adequate for most applications. If a large capacitive load needs to be driven by the Timer

Output, a larger bypass capacitor may be required.

Control Voltage: The Control Voltage input (pin 5) provides access to the upper level trip point. It is

derived from a high impedance resistive divider. As with any high impedance node, it should be

isolated from sources of DC leakage and high-level clock/data signals that might be capacitively

coupled into it. Keep this trace as short as possible. When possible, surround (shield) the Control

Voltage signal with an AC ground. In most applications it does not require a bypass capacitor.

Stray Capacitance: When using the CSS555C, it is important to minimize the stray capacitance on the

Threshold and Discharge pins. The internal timing capacitor is 100pF. Printed circuit boards typically

add several picofarads of stray capacitance if the routing is kept as short as possible. Timing resistors

RA and RB should be located as close to the IC as possible. The stray capacitance (CSTRAY) will be fairly

consistent from board-to-board and can be accounted for when selecting the timing resistors. (The

internal timing capacitor can be electronically trimmed to adjust for variations in CSTRAY, RA and RB.)

During development, remember that test sockets, proto-boards, connectors and cables can add

significant stray capacitance to these nodes. (A typical proto-board adds about 5pF per pin.) In most

prototype fixtures, the monostable delay times and astable periods will be longer than expected. After

a PCB is built, delay times will approach their expected values.

Micro-power Monostable & Delay Functions

Micro-power One Shot Long Range Delay Timer

Standard 555 configuration Extended range 1 msec to days

See Page 6 VDD See Page 7 VDD

CSS555 RA CSS555 RA

VSS VDD VSS VDD

Trigger Trigger Dischg Trigger Trigger Dischg

VTH VTH

Output Output Thresh Output Output Thresh

RB RB

Reset Reset Control Reset Reset Control

CT CT

Trigger Trigger

Output Output

tPW tPW

tPW = 1.1 x (RA+RB) x CT tPW = Multiplier x 0.695 x (RA+2RB) x CT

Custom Silicon Solutions, Inc. 2009 2 Version 1.0, May 2009

CSS555(C) Application Circuits

Micro-power Monostable & Delay Functions (continued)

One Shot with Internal CT Low Voltage One Shot

No external timing capacitor, PW MAX ~ 10 min. VDDMIN = 1.2V, trip levels = 10% & 90%

See Page 8 VDD See Page 9 VDD

CSS555C RA CSS555C RA

VSS VDD VSS VDD

Trigger Trigger Dischg Trigger Trigger Dischg

VTH VTH

Output Output Thresh Output Output Thresh

RB RB

Reset Reset Control Reset Reset Control

X No External

CT

Trigger

Optional

CT

Trigger

Output Output

tPW tPW

tPW = Multiplier x 0.695 x (RA+2RB) x CTI tPW = 2.3 x (RA+RB) x CT (if Mult = 1)

tPW = Multiplier x 2.2 x (RA+2RB) x CT

One Shot with Delay One Shot with Delay

Delay = Pulse Width Delay > Pulse Width

See Page 10 VDD See Page 11 VDD

CSS555C RA

CSS555C RA VSS VDD

VSS VDD

Trigger Trigger Dischg Trigger Trigger Dischg

VTH RB

VTH Output Output Thresh

Output Output Thresh

RB Optional

Reset Reset Control Reset Reset Control CTX

CT

Optional

CT RF

Trigger Trigger

tD tD

Output Output

tPW tPW

tD = 0.5 x Multiplier x 0.695 x (RA+2RB) x CT tD = 0.5 x Multiplier x 0.695 x (RA||RF+2RB) x CT

tPW = 0.5 x Multiplier x 0.695 x (RA+2RB) x CT tPW = see page 11

One Shot with Delay One Shot with Delay

Delay >> Pulse Width Delay << Pulse Width

See Page 12 VDD See Page 13 VDD VDD

CSS555C RA CSS555C RA RF

VSS VDD VSS VDD

Trigger Trigger Dischg Trigger Trigger Dischg MP1

VTH RB VTH RB (or PNP1

Output Output Thresh Output Output Thresh

+ Rbase)

Optional

Reset Reset Control CTX Reset Reset Control Optional

CT

CT

D1 RF

Trigger Trigger

tD tD

Output Output

tPW

tPW

tD = 0.5 x Multiplier x 0.695 x (RA+2RB) x CT tD = 0.5 x Multiplier x 0.695 x (RA||RF+2RB) x CT

tPW = 0.5 x Multiplier x 0.695 x (RA||RF+2RB) x CT tPW = 0.5 x Multiplier x 0.695 x (RA+2RB) x CT

Custom Silicon Solutions, Inc. 2009 3 Version 1.0, May 2009

CSS555(C) Application Circuits

Micro-power Astable Functions

Micro-power Clock Generator Minimum Component Clock Generator

Standard 555 configuration 50% duty cycle

See Page 14 VDD See Page 15 VDD

Mult = 1 Mult = 1

CSS555C RA CSS555C

VSS VDD VSS VDD

Trigger Dischg Trigger Dischg

VTH VTH

Output Output Thresh Output Output Thresh

RB

Reset Reset Control Reset Reset Control

Optional Optional

CT RA CT

Output Output

Reset Reset

Freq = 1.44 / [(RA+2RB) x CT] Freq = 1.44 / (2RA x CT)

Low Frequency Clock Generator Low Voltage Clock Generator

50% duty cycle, internal counter 50% duty cycle, 10% & 90% trip levels

See Page 16 VDD See Page 17 VDD

CSS555C RA CSS555C RA

VSS VDD VSS VDD

Trigger Trigger Dischg Trigger Trigger Dischg

VTH VTH

Output Output Thresh Output Output Thresh

RB RB

Reset Reset Control Reset Reset Control

Optional Optional

CT CT

Output Output

Trigger Trigger

Freq = 1.44 / [Multiplier x (RA+2RB) x CT] Freq = 0.455 / [Multiplier x (RA+2RB) x CT]

Astable with Adjustable Duty Cycle Astable with Adjustable Duty Cycle

Duty Cycle = 1% to 50% Duty Cycle = 50% to 99%

See Page 18 VDD See Page 19 VDD VDD

CSS555C RA CSS555C RA RF

VSS VDD VSS VDD

Trigger Trigger Dischg Trigger Trigger Dischg MP1

VTH RB VTH RB (or PNP1

Output Output Thresh Output Output Thresh

+ Rbase)

Optional

Reset Reset Control CTX Reset Reset Control Optional

CT

CT

D1 RF

Output Output

Trigger Trigger

If RB << RA and RF: If RB << RA and RF:

Duty Cycle ~ RF / (RA+2RF) Duty Cycle ~ (RA + RF) / (RA+2RF)

Custom Silicon Solutions, Inc. 2009 4 Version 1.0, May 2009

CSS555(C) Application Circuits

Applications with Special Requirements

High Humidity/High Leakage Applications Electronic Trimming

Low impedance Control Voltage Trim the internal 100 pF timing capacitor

VDD VDD See App Note 1

VDD

CSS555C RA CSS555

VSS VDD

RDV1 RA

VSS VDD

R1 TP1

Trigger Trigger Dischg Trigger Trigger Dischg

VTH RB TP2 RB

Output Output Thresh Timer Out Output Thresh

R2 TP3 TP4

Reset Reset Control

RDV2 Reset Reset Control

Optional Module

CT PCB

Test Port

VCONTROL = VDD x RDV2 / (RDV1+RDV2) Internal CT Range ~ 85 pF to 115 pF

For standard trip levels, RDV2 = 2 x RDV1 Internal CT Resolution ~ 1/8 pF

Isolated Power Supply High Voltage Power Supply

Capacitor isolation Simple diode regulator

VIN

(Clock or

AC Supply) CC D2

VDD ~ (Clock VP-P 1V) HV RS VDD

Supply

CDIV D1 CF LED CF

CSS555C CSS555C

(Optional) VSS VDD VSS VDD

Components

Components

Trigger Dischg Trigger Dischg

Typical Values

Timing

Timing

Typical Values Control Control

Output Thresh Output Thresh

Signals CF ~ 0.001uF Signals

CC ~ 0.001uF Reset Control Reset Control

RS ~ 100 K - 10 M

CF ~ 0.1uF

LED VON ~ 2.5V

CDIV used if VIN > 6V

+VPOS ~ 10V 100V

Clock Freq ~ 32 KHz RA, RLOAD > 1M RLOAD >> (VPOS 2.5) / RS

(Low IDD makes this practical with small caps.) LED acts as a Zener diode

1 Minute Watch-dog Timer

Solar Powered Timer (also Missing Pulse Detector)

Micro-power circuit Using Astable delayed pulse circuit

See Page 10

VDD VDD

VDD CSS555C RA=3.3M

RF=10K VSS VDD

Solar CF

Cell CSS555C Trigger Dischg

VSS VDD VTH

Output Output Thresh

Components

Trigger Dischg RB=1.1M

Timing

Control Reset Reset Control

Signals Output Thresh CF=1nF Mult = 100K

Reset Control Trip Levels = Low

Reset

tD=1 minute

RLOAD > 1 M

Output

Output = 1 if no Reset pulse for > 1 minute Output = 1 if no Reset pulse for > 1 minute

Custom Silicon Solutions, Inc. 2009 5 Version 1.0, May 2009

CSS555(C) Application Circuits

Monostable & Delay Circuits

The following circuits use the CSS555 and CSS555C to implement micro-power delay timers.

Micro-power One Shot

This circuit uses the CSS555 configured to mimic the classic 555 timer, but with an operating current

that is 10 times lower than any other 555 IC.

Design Example: Pulse Width (tPW ) = 1 second

Configuration Data (EEPROM):

Multiplier = 1 (counter disabled), Mode = X (Dont Care)

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components:

RA = 2.7 M, RB = 100 K, CT = 0.33 uF

RESET

TRIGGER

VDD

OUTPUT

CSS555 RA

VSS VDD tPW

Trigger Trigger Dischg

VTH VDD

Output Output Thresh

RB

Reset Reset Control

VTH

CT

0V

Timing Equations:

Output Pulse Width (tPW ) CSS555 Timer Calculator

tPW = 1.1 x (RA+RB) x CT

= 1.1 x (2.7M + 0.1M) x 0.33uF

= 1.015 seconds

Supply Current & Power:

Standby current (IDD0) (Discharge = 0)

At VDD = 3.0V, IDD0 = 4.2uA, Power = 12.6uW

At VDD = 5.0V, IDD0 = 6.1uA, Power = 30.5uW

Average current (IDD) (Output = 1)

At VDD = 3.0V, IDD = 3.6uA, Power = 10.8uW Note: A calculator is available for this circuit.

At VDD = 5.0V, IDD = 5.1uA, Power = 25.5uW See file CSS555_Timer_Delay_Calculator.xls

Monostable Delay Time Examples

Output Timing Components Supply Current (IDD0) Supply Power

Pulse Width RA RB CT 3.0V 5.0V 3.0V 5.0V

100 usec 0.5 M 0.4 M 100 pF 9.1 uA 14.3 uA 27.3 uW 71.5 uW

1 msec 2.7 M 0.1 M 330 pF 4.2 uA 6.1 uA 12.6 uW 30.5 uW

10 msec 2.7 M 0.1 M 3.3 nF 4.2 uA 6.1 uA 12.6 uW 30.5 uW

100 msec 2.7 M 0.1 M 33 nF 4.2 uA 6.1 uA 12.6 uW 30.5 uW

1 sec 2.7 M 0.1 M 0.33 uF 4.2 uA 6.1 uA 12.6 uW 30.5 uW

10 sec 2.7 M 0.1 M 3.3 uF 4.2 uA 6.1 uA 12.6 uW 30.5 uW

1 min 5.0 M 0.5 M 10 uF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

Custom Silicon Solutions, Inc. 2009 6 Version 1.0, May 2009

CSS555(C) Application Circuits

Monostable & Delay Circuits (continued)

Long Range Delay Timer

This circuit uses the CSS555s internal counter to multiply (and therefore reduce) the value of the timing

capacitor (CT) by the counter setting (10 to 106). At the maximum counter setting, very long delay times

are possible with small capacitor values.

Design Example: Pulse Width (tPW ) = 1 second

Configuration Data (EEPROM):

Multiplier = 1000, Mode = Monostable

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components:

RA = 2.4 M, RB = 1.0 M, CT = 330 pF

RESET

TRIGGER

VDD OUTPUT

CSS555 RA tPW

VSS VDD

1000 clock

Trigger Trigger Dischg

VTH cycles

Output Output Thresh

VDD

RB 2/3 VDD

Reset Reset Control

VTH

CT 1/3 VDD

0V

Timing Equations:

Output Pulse Width (tPW ) CSS555 Timer Calculator

tPW = Multiplier x 0.695 x (RA+2RB) x CT

= 1000 x 0.695 x (2.4M + 2x1M) x 330pF

= 1.007 seconds

Supply Current & Power:

Standby current (IDD0) (Discharge = 0)

At VDD = 3.0V, IDD0 = 4.4uA, Power = 13.2uW

At VDD = 5.0V, IDD0 = 6.4uA, Power = 32.0uW

Average current (IDD) (Output = 1)

At VDD = 3.0V, IDD = 3.5uA, Power = 10.5uW Note: A calculator is available for this circuit.

At VDD = 5.0V, IDD = 4.8uA, Power = 24.0uW See file CSS555_Timer_Delay_Calculator.xls

Monostable Delay Time Examples

Extended Period Mode & External Timing Capacitor

Output Configuration Data & Timing Components Supply Current (IDD0) Supply Power

Pulse

Width Multiplier RA RB CT 3.0V 5.0V 3.0V 5.0V

1 msec 10 240 K 100 K 330 pF 15.6 uA 25.1 uA 46.8 uW 125 uW

10 msec 10 2.4 M 1.0 M 330 pF 4.4 uA 6.4 uA 13.2 uW 30.5 uW

100 msec 100 2.4 M 1.0 M 330 pF 4.4 uA 6.4 uA 13.2 uW 30.5 uW

1 sec 1K 2.4 M 1.0 M 330 pF 4.4 uA 6.4 uA 13.2 uW 30.5 uW

10 sec 10K 2.4 M 1.0 M 330 pF 4.4 uA 6.4 uA 13.2 uW 30.5 uW

1 min 100K 2.4 M 1.0 M 200 pF 4.4 uA 6.4 uA 13.2 uW 26.5 uW

10 min 1M 2.4 M 1.0 M 200 pF 4.4 uA 6.4 uA 13.2 uW 26.5 uW

1 hour 1M 2.4 M 1.0 M 1.2 nF 4.4 uA 6.4 uA 13.2 uW 26.5 uW

1 day 1M 2.2 M 1.0 M 0.03 uF 4.5 uA 6.6 uA 13.5 uW 33.0 uW

Custom Silicon Solutions, Inc. 2009 7 Version 1.0, May 2009

CSS555(C) Application Circuits

Monostable & Delay Circuits (continued)

One Shot with Minimal Components

This circuit uses the CSS555Cs internal counter and timing capacitor to eliminate the external

capacitor.

Design Example: Pulse Width (tPW ) = 1 second

Configuration Data (EEPROM):

Multiplier = 1000, Mode = Monostable

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components:

RA = 5.0 M, RB = 4.7 M, CT = 100 pF

RESET

TRIGGER

VDD OUTPUT

CSS555C RA tPW

VSS VDD

1000 clock

Trigger Trigger Dischg

VTH cycles

VDD

Output Output Thresh

RB 2/3 VDD

Reset Reset Control VTH

X No External

CT 0V

1/3 VDD

Timing Equations:

Output Pulse Width (tPW ) CSS555 Timer Calculator

tPW = Multiplier x 0.695 x (RA+2RB) x CT

= 1000 x 0.695 x (5.0M + 2x4.7M) x 100pF

= 0.998 seconds

Supply Current & Power:

Standby current (IDD0) (Discharge = 0)

At VDD = 3.0V, IDD0 = 3.7uA, Power = 11.1uW

At VDD = 5.0V, IDD0 = 5.3uA, Power = 26.5uW

Average current (IDD) (Output = 1)

At VDD = 3.0V, IDD = 3.2uA, Power = 9.6uW Note: A calculator is available for this circuit.

At VDD = 5.0V, IDD = 4.5uA, Power = 22.5uW See file CSS555_Timer_Delay_Calculator.xls

Monostable Delay Time Examples

Extended Period Mode & Internal Timing Capacitor

Output Configuration Data & Timing Components Supply Current (IDD0) Supply Power

Pulse

Width Multiplier RA RB CT 3.0V 5.0V 3.0V 5.0V

1 msec 10 1.0 M 200 K 100 pF 6.1 uA 9.3 uA 18.3 uW 46.5 uW

10 msec 10 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

100 msec 100 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

1 sec 1K 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

10 sec 10K 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

1 min 100K 5.0 M 1.8 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

10 min 1M 5.0 M 1.8 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

Custom Silicon Solutions, Inc. 2009 8 Version 1.0, May 2009

CSS555(C) Application Circuits

Monostable & Delay Circuits (continued)

Low Voltage One Shot

The trip levels are configured for 10% and 90% of VDD, allowing operation down to 1.2V. These trip

levels may be used with or without the internal counter and timing capacitor.

Design Example: Pulse Width (tPW ) = 1 second

Configuration Data (EEPROM):

Multiplier = 1000, Mode = Monostable

Power Setting = Micro, Trip Levels = Low VDD (10%, 90%)

Timing Components:

RA = 2.6 M, RB = 1.0 M, CT = 100 pF

RESET

TRIGGER

VDD OUTPUT

CSS555C RA tPW

VSS VDD

1000 clock

Trigger Trigger Dischg

VTH cycles

VDD

Output Output Thresh 90% VDD

RB

Reset Reset Control VTH

Optional

10% VDD

CT 0V

Timing Equations:

Output Pulse Width (tPW ) CSS555 Timer Calculator

tPW = Multiplier x 2.197 x (RA+2RB) x CT

= 1000 x 2.197 x (2.6M + 2x1.0M) x 100pF

= 1.01 seconds

Supply Current & Power:

Standby current (IDD0) (Discharge = 0)

At VDD = 1.5V, IDD0 = 2.8uA, Power = 4.2uW

At VDD = 3.0V, IDD0 = 4.3uA, Power = 12.9uW

Average current (IDD) (Output = 1)

At VDD = 1.5V, IDD = 2.4uA, Power = 7.2uW Note: A calculator is available for this circuit.

At VDD = 3.0V, IDD = 3.5uA, Power = 10.5uW See file CSS555_Timer_Delay_Calculator.xls

Monostable Delay Time Examples

Low VDD Configuration (Trip levels = 10% & 90%)

Output Configuration Data & Timing Components Supply Current (IDD0) Supply Power

Pulse

Width Multiplier RA RB CT 1.5V 3.0V 1.5V 3.0V

1 msec 1 3.3 M 1.0 M 100 pF 2.7 uA 4.0 uA 4.1 uW 12.2 uW

10 msec 10 2.6 M 1.0 M 100 pF 2.8 uA 4.3 uA 4.2 uW 12.9 uW

100 msec 100 2.6 M 1.0 M 100 pF 2.8 uA 4.3 uA 4.2 uW 12.9 uW

1 sec 1K 2.6 M 1.0 M 100 pF 2.8 uA 4.3 uA 4.2 uW 12.9 uW

10 sec 10K 2.6 M 1.0 M 100 pF 2.8 uA 4.3 uA 4.2 uW 12.9 uW

1 min 100K 2.6 M 1.0 M 100 pF 2.8 uA 4.3 uA 4.2 uW 12.9 uW

10 min 1M 2.6 M 1.0 M 100 pF 2.8 uA 4.3 uA 4.2 uW 12.9 uW

Custom Silicon Solutions, Inc. 2009 9 Version 1.0, May 2009

CSS555(C) Application Circuits

Monostable & Delay Circuits (continued)

One Shot with Delayed Pulse

This circuit uses the CSS555s internal counter and astable operating mode to generate a delayed

pulse. In the astable mode, the timer output is derived from the MSB of the counter. It is low for the

first half of the counter cycle and high for the second half. The output pulse is therefore delayed by

Mult/2 clock cycles and has a pulse width of Mult/2 cycles. This circuit can be used with or without the

internal timing capacitor and Low VDD trip levels.

Design Example: Delay (tD) = 0.5 sec, Pulse Width (tPW ) = 0.5 sec

Configuration Data (EEPROM):

Multiplier = 1000 (for 0.5 second tD & tPW ), Mode = Astable

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components (for 0.5 sec pulse width & delay):

RA = 5.0 M, RB = 4.7 M, CT = 100 pF

RESET

TRIGGER

VDD OUTPUT

CSS555C RA tD tPW

VSS VDD

500+500

Trigger Trigger Dischg

VTH clock cycles

VDD

Output Output Thresh

RB 2/3 VDD

Reset Reset Control VTH

Optional 1/3 VDD

CT 0V

Timing Equations:

Output Pulse Width & Delay (tPW , tD) CSS555 Timer Calculator

tPW = 0.5 x Multiplier x 0.695 x (RA+2RB) x CT

= 500 x 0.695 x (5.0M + 2x4.7M) x 100pF

= 0.499 seconds

tD = tPW = 0.499 seconds

Supply Current & Power:

Standby current (IDD0) (Discharge = 0)

At VDD = 3.0V, IDD0 = 3.7uA, Power = 11.1uW

At VDD = 5.0V, IDD0 = 5.3uA, Power = 26.5uW

Average current (IDD) (Output = 1) Note: A calculator is available for this circuit.

At VDD = 3.0V, IDD = 3.2uA, Power = 9.6uW See file CSS555_Timer_Delay_Calculator.xls

At VDD = 5.0V, IDD = 4.5uA, Power = 22.5uW

Delayed-Pulse Examples

Astable Mode, Delay (tD) = Pulse Width (tPW )

Output Configuration Data & Timing Components Supply Current (IDD0) Supply Power

tD+tPW Multiplier RA RB CT 3.0V 5.0V 3.0V 5.0V

1 msec 10 1.0 M 200 K 100 pF 6.1 uA 9.3 uA 18.3 uW 46.5 uW

10 msec 10 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

100 msec 100 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

1 sec 1K 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

10 sec 10K 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

1 min 100K 5.0 M 1.8 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

10 min 1M 5.0 M 1.8 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

Custom Silicon Solutions, Inc. 2009 10 Version 1.0, May 2009

CSS555(C) Application Circuits

Monostable & Delay Circuits (continued)

One Shot with Delayed Pulse (tD > tPW)

This circuit uses the CSS555s internal counter and astable operating mode to generate a delayed

pulse. In the astable mode, the timer output is derived from the MSB of the counter. It is low for the

first Mult/2 clock cycles and high for the remaining Mult/2 cycles. Feedback from the Timer Output

increases the oscillator frequency when the output is high, allowing the pulse width to be reduced. This

circuit can be used with or without the internal timing capacitor.

Design Example: Delay (tD) = 0.66 sec, Pulse Width (tPW ) = 0.33 sec

Configuration Data (EEPROM):

Multiplier = 10K, Mode = Astable

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components:

RA = 1.0 M, RB = 90 K, RF = 3.8 M, CT = 100 pF

RESET

TRIGGER

tPW

VDD

OUTPUT

CSS555C RA

VSS VDD tD

Trigger Trigger Dischg 5000+5000

VTH RB

Output Output Thresh clock cycles

VDD

Reset Reset Control CTX 2/3 VDD

VTH

1/3 VDD

RF 0V

Timing Equations:

Output Delay & Pulse Width (tD, tPW ) CSS555 Timer Calculator

td0 = LN() LN(1- (RF+RA)/RF) (if Output = 0)

= 1.44

td1 = LN() LN() (if Output = 1)

= 0.693

tD = x Multiplier x C T [td0 (RA||RF+RB) + (td1 RB)]

= 5000 x 100pF x [1.44 x 882K + 0.693 x 90K]

= 666 msec

tPW = x Multiplier x C T x 0.693 x (RA||RF+2RB)

= 5000 x 100pF x 0.693 x (790K + 2x90K)

= 337 msec

Note: A calculator is available for this circuit.

See file CSS555_Adj_Duty_Calculator.xls

Supply Current & Power:

Maximum current (IDD0) (Discharge = 0)

At VDD = 3.0V, IDD0 = 4.7uA, Power = 11.1uW

At VDD = 5.0V, IDD0 = 6.5uA, Power = 26.5uW

Delayed-Pulse Examples (tD > tPW)

Astable Mode, Delay (tD) > Pulse Width (tPW )

Configuration Data & Timing Components Timing Values Supply Current (IDD0)

Multiplier RA RB RF CT Delay Pulse Width 3.0V 5.0V

1K 1.0 M 100 K 5.0 M 100 pF 59.6 msec 35.8 msec 6.3 uA 9.1 uA

1K 1.0 M 100 K 2.5 M 100 pF 97.2 msec 31.7 msec 6.3 uA 9.1 uA

1K 1.0 M 250 K 2.5 M 100 pF 119.7 msec 42.1 msec 6.3 uA 9.1 uA

Custom Silicon Solutions, Inc. 2009 11 Version 1.0, May 2009

CSS555(C) Application Circuits

Monostable & Delay Circuits (continued)

One Shot with Delayed Pulse (tD >> tPW)

This circuit uses the CSS555s internal counter and astable operating mode to generate a delayed

pulse. In the astable mode, the timer output is derived from the MSB of the counter. It is low for the

first Mult/2 clock cycles and high for the remaining Mult/2 cycles. Feedback from the Timer Output

increases the oscillator frequency when the output is high, allowing the pulse width to be reduced. This

circuit can be used with or without the internal timing capacitor.

Design Example: Delay (tD) = 0.8 sec, Pulse Width (tPW ) = 0.2 sec

Configuration Data (EEPROM):

Multiplier = 10K, Mode = Astable

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components:

RA = 2.1 M, RB = 100 K, RF = 380 K, CT = 100 pF

RESET

TRIGGER

tPW

VDD

OUTPUT

CSS555C RA

VSS VDD tD

Trigger Trigger Dischg 5000+5000

VTH RB

Output Output Thresh clock cycles

VDD

Reset Reset Control Optional 2/3 VDD

CT VTH

1/3 VDD

D1 RF 0V

Timing Equations:

Output Delay & Pulse Width (tD,tPW ) CSS555 Timer Calculator

tD = 0.5 x Multiplier x 0.695 x (RA+2RB) x CT

= 5000 x 0.695 x (2.1M + 2x0.1M) x 100pF

= 799 msec

tPW = 0.5 x Multiplier x 0.695 x (RA||RF+2RB) x CT

= 5000 x 0.695 x (0.32M + 2x0.1M) x 100pF

= 181 msec (if ideal diode)

~ 198 msec (adding diode voltage drop)

Supply Current & Power:

Maximum current (IDD0) (Discharge = 0) Note: A calculator is available for this circuit.

At VDD = 3.0V, IDD0 = 4.7uA, Power = 11.1uW See file CSS555_Adj_Duty_Calculator.xls

At VDD = 5.0V, IDD0 = 6.5uA, Power = 26.5uW

Delayed-Pulse Examples (tD >> tPW)

Astable Mode, Delay (tD) >> Pulse Width (tPW )

Configuration Data & Timing Components Timing Values Supply Current (IDD0)

Multiplier RA RB RF CT Delay Pulse Width 3.0V 5.0V

10 1.0 M 100 K 100 K 100 pF 416 usec 106 usec 6.3 uA 9.1 uA

10 5.0 M 100 K 100 K 100 pF 1.80 msec 0.11 msec 3.9 uA 5.1 uA

10 5.0 M 100 K 5.0 M 100 pF 1.80 msec 1.01 msec 3.7 uA 5.3 uA

10K 1.0 M 100 K 100 K 100 pF 416 msec 106 msec 6.3 uA 9.1 uA

10K 5.0 M 100 K 100 K 100 pF 1.80 sec 0.11 sec 3.7 uA 5.3 uA

10K 5.0 M 100 K 5.0 M 100 pF 1.80 sec 1.01 sec 3.7 uA 5.3 uA

Custom Silicon Solutions, Inc. 2009 12 Version 1.0, May 2009

CSS555(C) Application Circuits

Monostable & Delay Circuits (continued)

One Shot with Delayed Pulse (tD << tPW)

This circuit uses the CSS555s internal counter and astable operating mode to generate a delayed

pulse. In the astable mode, the timer output is derived from the MSB of the counter. It is low for the

first Mult/2 clock cycles and high for the remaining Mult/2 cycles. Feedback from the Timer Output

increases the oscillator frequency when the output is low, allowing the delay to be reduced. This circuit

can be used with or without the internal timing capacitor.

Design Example: Delay (tD) = 0.2 sec, Pulse Width (tPW ) = 0.8 sec

Configuration Data (EEPROM):

Multiplier = 10K, Mode = Astable

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components:

RA = 2.1 M, RB = 100 K, RF = 460 K, CT = 100 pF

RESET

TRIGGER

VDD VDD

OUTPUT tPW

CSS555C RA RF

VSS VDD tD

Trigger Trigger Dischg MP1 5000+5000

VTH RB (or PNP1

Output Output Thresh

+ Rbase) VDD

clock cycles

Reset Reset Control Optional 2/3 VDD

CT VTH

1/3 VDD

0V

Timing Equations:

Output Delay & Pulse Width (tD,tPW ) CSS555 Timer Calculator

tD = 0.5 x Multiplier x 0.695 x (RA||RF+2RB) x CT

= 5000 x 0.695 x (0.377M + 2x0.1M) x 100pF

= 200 msec

tPW = 0.5 x Multiplier x 0.695 x (RA+2RB) x CT

= 5000 x 0.695 x (2.1M + 2x0.1M) x 100pF

= 799 msec

Supply Current & Power:

Maximum current (IDD0) (Discharge = 0)

At VDD = 3.0V, IDD0 = 4.7uA, Power = 11.1uW Note: A calculator is available for this circuit.

At VDD = 5.0V, IDD0 = 6.5uA, Power = 26.5uW See file CSS555_Adj_Duty_Calculator.xls

Delayed-Pulse Examples (tD >> tPW)

Astable Mode, Delay (tD) >> Pulse Width (tPW )

Configuration Data & Timing Components Timing Values Supply Current (IDD0)

Multiplier RA RB RF CT Delay Pulse Width 3.0V 5.0V

10 1.0 M 100 K 100 K 100 pF 416 usec 106 usec 6.3 uA 9.1 uA

10 5.0 M 100 K 100 K 100 pF 1.80 msec 0.11 msec 3.9 uA 5.1 uA

10 5.0 M 100 K 5.0 M 100 pF 1.80 msec 1.01 msec 3.7 uA 5.3 uA

10K 1.0 M 100 K 100 K 100 pF 416 msec 106 msec 6.3 uA 9.1 uA

10K 5.0 M 100 K 100 K 100 pF 1.80 sec 0.11 sec 3.7 uA 5.3 uA

10K 5.0 M 100 K 5.0 M 100 pF 1.80 sec 1.01 sec 3.7 uA 5.3 uA

Custom Silicon Solutions, Inc. 2009 13 Version 1.0, May 2009

CSS555(C) Application Circuits

Astable Circuits

The following circuits use the CSS555 and CSS555C to implement micro-power astable timers.

Micro-power Clock Generator

This circuit uses the CSS555 configured to mimic the classic 555 Timer, but with an operating current

that is 10 times lower than all other 555 ICs.

Design Example: Output Frequency (FOUT) = 100 Hz

Configuration Data (EEPROM):

Multiplier = 1 (counter disabled), Mode = X (Dont Care)

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components:

RA = 2.0 M, RB = 1.2 M, CT = 3.3 nF

RESET

VDD

OUTPUT

CSS555C RA

VSS VDD

Trigger Dischg

VTH

Output Output Thresh VDD

RB VDD

Reset Reset Control

Optional VTH

CT VDD

0V

Timing Equations:

Output Period & Frequency (tPER, FOUT) CSS555 Timer Calculator

tPER = 0.695 x (RA+2RB) x CT

FOUT = 1.44 / [(RA+2RB) x CT]

= 1.44 / [(2.0M + 2x1.2M) x 3.3nF]

= 99.2 Hz

Duty Cycle = RB / (RA+2RB)

Supply Current & Power:

Standby current (IDD0) (Discharge = 0)

At VDD = 3.0V, IDD0 = 4.6uA, Power = 13.8uW

At VDD = 5.0V, IDD0 = 6.8uA, Power = 34.0uW Note: A calculator is available for this circuit.

Average current (IDD) (Output toggling) See file CSS555_Timer_Delay_Calculator.xls

At VDD = 3.0V, IDD = 3.5uA, Power = 10.5uW

At VDD = 5.0V, IDD = 4.8uA, Power = 24.0uW

Micro-power Astable Examples

Output Timing Components Supply Current (IDD) Supply Power

Frequency RA RB CT 3.0V 5.0V 3.0V 5.0V

100 KHz 70 KM 37 K 100 pF 13.2 uA 21.0 uA 39.6 uW 105.0 uW

10 KHz 700 KM 370 K 100 pF 4.1 uA 6.0 uA 12.3 uW 30.0 uW

1 KHz 2.0 M 1.2 M 330 pF 3.5 uA 4.8 uA 10.5 uW 24.0 uW

100 Hz 2.0 M 1.2 M 3.3 nF 3.5 uA 4.8 uA 10.5 uW 24.0 uW

10 Hz 2.0 M 1.2 M 0.033 uF 3.5 uA 4.8 uA 10.5 uW 24.0 uW

1 Hz 2.0 M 1.2 M 0.33 uF 3.5 uA 4.8 uA 10.5 uW 24.0 uW

Custom Silicon Solutions, Inc. 2009 14 Version 1.0, May 2009

CSS555(C) Application Circuits

Astable Circuits (continued)

Micro-power Clock Generator (minimum component)

This circuit uses the CSS555 configured to mimic the classic 555 Timer, but with an operating current

that is 10 times lower than all other 555 ICs. It requires just one timing resistor and has a 50% duty

cycle. This circuit can be used with or without the internal timing capacitor.

Design Example: Output Frequency (FOUT) = 100 Hz

Configuration Data (EEPROM):

Multiplier = 1 (counter disabled), Mode = X (Dont Care)

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components:

RA = 2.2 M, CT = 3.3 nF

RESET

VDD

OUTPUT

CSS555C

VSS VDD

Trigger Dischg

VTH

Output Output Thresh

VDD

Reset Reset Control VDD

Optional VTH

RA CT

0V VDD

Timing Equations:

Output Period & Frequency (tPER, FOUT) CSS555 Timer Calculator

tPER = 0.695 x 2RA x CT

FOUT = 1.44 / (2RA x CT)

= 1.44 / (2 x 2.2M x 3.3nF)

= 99.2 Hz

Duty Cycle = 50%

Supply Current & Power:

Standby current (IDD0) (Reset = 0)

At VDD = 3.0V, IDD0 = 3.1uA, Power = 9.3uW

Note: A calculator is available for this circuit.

At VDD = 5.0V, IDD0 = 4.3uA, Power = 21.5uW See file CSS555_Timer_Delay_Calculator.xls

Average current (IDD) (Output toggling) Worksheet Calculator_1X_50%

At VDD = 3.0V, IDD = 3.5uA, Power = 10.5uW

At VDD = 5.0V, IDD = 4.8uA, Power = 24.0uW

Minimal Component Astable Examples

Output Timing Components Supply Current (IDD) Supply Power

Frequency RA RB CT 3.0V 5.0V 3.0V 5.0V

100 KHz 70 K 100 pF 13.4 uA 21.5 uA 40.2 uW 107.5 uW

10 KHz 700 K 100 pF 4.2 uA 6.0 uA 12.6 uW 30.0 uW

1 KHz 2.2 M 330 pF 3.5 uA 4.8 uA 10.5 uW 24.0 uW

100 Hz 2.2 M 3.3 nF 3.5 uA 4.8 uA 10.5 uW 24.0 uW

10 Hz 2.2 M 0.033 uF 3.5 uA 4.8 uA 10.5 uW 24.0 uW

1 Hz 2.2 M 0.33 uF 3.5 uA 4.8 uA 10.5 uW 24.0 uW

Custom Silicon Solutions, Inc. 2009 15 Version 1.0, May 2009

CSS555(C) Application Circuits

Astable Circuits (continued)

Low Frequency Clock Generator

This circuit uses the CSS555s internal counter to multiply (and therefore reduce) the value of the timing

capacitor (CT) by the counter setting (10 to 106). At the maximum counter setting, very low frequency

clocks are possible with small capacitor values. The TRIGGER input acts as a gate for the clock. This

circuit can be used with or without the internal timing capacitor.

Design Example: Output Frequency (FOUT) = 1.0 Hz

Configuration Data (EEPROM):

Multiplier = 1000, Mode = Astable

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components:

RA = 5.0 M, RB = 4.7 M, CT = 100 pF

RESET

TRIGGER

VDD

OUTPUT

CSS555C RA

VSS VDD

Trigger Trigger Dischg

VTH

Output Output Thresh VDD

RB VDD

Reset Reset Control

Optional VTH

VDD

CT

0V

Timing Equations:

Output Period & Frequency (tPER, FOUT) CSS555 Timer Calculator

tPER = Multiplier x 0.695 x (RA+2RB) x CT

FOUT = 1.44 / [Multiplier x (RA+2RB) x CT]

= 1.44 / [1000 (5.0M + 2x4.7M) x 100pF]

= 1.00 Hz

Duty Cycle = 50%

Supply Current & Power:

Standby current (IDD0) (Discharge = 0)

At VDD = 3.0V, IDD0 = 3.7uA, Power = 11.1uW

At VDD = 5.0V, IDD0 = 5.3uA, Power = 26.5uW Note: A calculator is available for this circuit.

Average current (IDD) (Output toggling) See file CSS555_Timer_Delay_Calculator.xls

At VDD = 3.0V, IDD = 3.2uA, Power = 9.6uW

At VDD = 5.0V, IDD = 4.5uA, Power = 22.5uW

Low Frequency Astable Examples

Output Configuration Data & Timing Components Supply Current (IDD0) Supply Power

Frequency Multiplier RA RB CT 3.0V 5.0V 3.0V 5.0V

10 KHz 1 500 K 470 K 100 pF 9.1 uA 14.3 uA 27.3 uW 71.5 uW

1K Hz 1 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

100 Hz 10 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

10 Hz 100 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

1 Hz 1000 5.0 M 4.7 M 100 pF 3.7 uA 5.3 uA 11.1 uW 26.5 uW

Custom Silicon Solutions, Inc. 2009 16 Version 1.0, May 2009

CSS555(C) Application Circuits

Astable Circuits (continued)

Low Voltage Clock Generator

The trip levels are configured for 10% and 90% of VDD, allowing operation down to 1.2V. The

TRIGGER input acts as a gate for the clock. These trip levels may be used with or without the internal

counter and timing capacitor.

Design Example: Output Frequency (FOUT) = 60 Hz

Configuration Data (EEPROM):

Multiplier = 10, Mode = Astable

Power Setting = Micro, Trip Levels = Low VDD (10%, 90%)

Timing Components:

RA = 2.5 M, RB = 2.5 M, CT = 100 pF

RESET

TRIGGER

VDD

OUTPUT

CSS555C RA

VSS VDD

Trigger Trigger Dischg

VTH

Output Output Thresh VDD

RB 90% VDD

Reset Reset Control

Optional VTH

CT 10% VDD

0V

Timing Equations:

Output Period & Frequency (tPER, FOUT) CSS555 Timer Calculator

tPER = Multiplier x 2.197 x (RA+2RB) x CT

FOUT = 0.455 / [Multiplier x (RA+2RB) x CT]

= 0.455 / [10 (2.5M + 2x2.5M) x 100pF]

= 60.7 Hz

Duty Cycle = 50%

Supply Current & Power:

Standby current (IDD0) (Discharge = 0)

At VDD = 1.5V, IDD0 = 2.9uA, Power = 4.4uW

At VDD = 3.0V, IDD0 = 4.3uA, Power = 12.9uW Note: A calculator is available for this circuit.

Average current (IDD) (Output toggling) See file CSS555_Timer_Delay_Calculator.xls

At VDD = 1.5V, IDD = 2.3uA, Power = 3.5uW

At VDD = 3.0V, IDD = 3.3uA, Power = 9.9uW

Low Voltage Astable Examples

Output Configuration Data & Timing Components Supply Current (IDD0) Supply Power

Frequency Multiplier RA RB CT 1.5V 3.0V 1.5V 3.0V

10 KHz 1 200 K 120 K 100 pF 9.8 uA 18.1 uA 14.7 uW 54.3 uW

1K Hz 1 2.0 M 1.2 M 100 pF 3.0 uA 4.6 uA 4.5 uW 13.8 uW

100 Hz 10 2.0 M 1.2 M 100 pF 3.0 uA 4.6 uA 4.5 uW 13.8 uW

10 Hz 100 2.0 M 1.2 M 100 pF 3.0 uA 4.6 uA 4.5 uW 13.8 uW

1 Hz 1000 2.0 M 1.2 M 100 pF 3.0 uA 4.6 uA 4.5 uW 13.8 uW

Custom Silicon Solutions, Inc. 2009 17 Version 1.0, May 2009

CSS555(C) Application Circuits

Astable Circuits (continued)

Astable with Adjustable Duty Cycle (Duty cycle = 1% to 50%)

This circuit uses the CSS555s internal counter and astable operating mode to generate a continuous

clock. In the astable mode, the timer output is derived from the MSB of the counter. Feedback from

the Timer Output increases the oscillator frequency when the output is high, allowing the duty cycle to

be reduced. The TRIGGER input acts as a gate for the clock. This circuit can be used with or without

the internal timing capacitor.

Design Example: Output Frequency (FOUT) = 100 Hz

Configuration Data (EEPROM):

Multiplier = 100, Mode = Astable

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components:

RA = 2.1 M, RB = 150 K, RF = 150 K, CT = 100 pF

RESET

TRIGGER tDH

VDD

OUTPUT

CSS555C RA

VSS VDD tDL

Trigger Trigger Dischg

Mult/2+Mult/2

VTH RB

Output Output Thresh

VDD

clock cycles

Reset Reset Control Optional 2/3 VDD

CT VTH

1/3 VDD

D1 RF

0V

Timing Equations:

Output Period & Frequency (tPER, FOUT) CSS555 Timer Calculator

tDL = 0.5 x Multiplier x 0.695 x (RA+2RB) x CT

= 50 x 0.695 x (2.1M + 2x0.15M) x 100pF

= 8.34 msec

tDH = 0.5 x Multiplier x 0.695 x (RA||RF+2RB) x CT

= 50 x 0.695 x (140K + 2x150K) x 100pF

= 1.53 msec (if ideal diode)

~ 1.69 msec (adding diode voltage drop)

tPER = (tDL + tDH) = 8.34 + 1.69 = 10.03 msec

FOUT = 1 / tPER = 1/10.03 msec = 99.7 Hz

Duty Cycle = (tDH / tPER) = 1.69/10.03 = 16.8% Note: A calculator is available for this circuit.

Supply Current & Power: See file CSS555_Adj_Duty_Calculator.xls

Maximum current (IDD0) (Discharge = 0)

At VDD = 3.0V, IDD0 = 4.3uA, Power = 12.9uW

At VDD = 5.0V, IDD0 = 5.8uA, Power = 29.0uW

Astable with Adjustable Duty Cycle Examples (Duty Cycle < 50%)

Configuration Data & Timing Components Timing Values Supply Current (IDD0)

Multiplier RA RB RF CT Frequency Duty Cycle 3.0V 5.0V

10 1.0 M 100 K 100 K 100 pF 1898 Hz 21.1% 6.3 uA 9.1 uA

10 5.0 M 100 K 100 K 100 pF 522 Hz 6.0% 3.9 uA 5.1 uA

10 5.0 M 100 K 5.0 M 100 pF 348 Hz 37.2% 3.9 uA 5.1 uA

100 1.0 M 100 K 100 K 100 pF 190 Hz 21.1% 6.3 uA 9.1 uA

100 5.0 M 100 K 100 K 100 pF 52.2 Hz 6.0% 3.9 uA 5.1 uA

100 5.0 M 100 K 5.0 M 100 pF 34.8 Hz 37.2% 3.9 uA 5.1 uA

Custom Silicon Solutions, Inc. 2009 18 Version 1.0, May 2009

CSS555(C) Application Circuits

Astable Circuits (continued)

Astable with Adjustable Duty Cycle (Duty cycle = 50% to 99%)

This circuit uses the CSS555s internal counter and astable operating mode to generate a continuous

clock. In the astable mode, the timer output is derived from the MSB of the counter. Feedback from

the Timer Output increases the oscillator frequency when the output is low, allowing the duty cycle to be

raised. The TRIGGER input acts as a gate for the clock. This circuit can be used with or without the

internal timing capacitor.

Design Example: Output Frequency (FOUT) = 100 Hz

Configuration Data (EEPROM):

Multiplier = 100, Mode = Astable

Power Setting = Micro, Trip Levels = Standard (1/3, 2/3)

Timing Components:

RA = 2.1 M, RB = 150 K, RF = 150 K, CT = 100 pF

RESET

TRIGGER tDH

VDD VDD

CSS555C OUTPUT

RA RF

VSS VDD

tDL

Trigger Trigger Dischg MP1

VTH RB (or PNP1 Mult/2+Mult/2

Output Output Thresh

+ Rbase) clock cycles

VDD

Reset Reset Control Optional

2/3 VDD

CT VTH

1/3 VDD

0V

Timing Equations:

Output Period & Frequency (tPER, FOUT) CSS555 Timer Calculator

tDL = 0.5 x Multiplier x 0.695 x (RA||RF+2RB) x CT

= 50 x 0.695 x (140 K + 2x150K) x 100pF

= 1.52 msec

tDH = 0.5 x Multiplier x 0.695 x (RA+2RB) x CT

= 50 x 0.695 x (2.1 M + 2x0.15M) x 100pF

= 8.32 msec

tPER = (tDL + tDH) = 1.52 + 8.32 = 9.84 msec

FOUT = 1 / tPER = 1/9.84 msec = 101.6 Hz

Duty Cycle = (tDH / tPER) = 8.32/9.84 = 84.5%

Supply Current & Power: Note: A calculator is available for this circuit.

See file CSS555_Adj_Duty_Calculator.xls

Maximum current (IDD0) (Discharge = 0)

At VDD = 3.0V, IDD0 = 4.7uA, Power = 14.1uW

At VDD = 5.0V, IDD0 = 6.5uA, Power = 32.5uW

Astable with Adjustable Duty Cycle Examples (Duty Cycle > 50%)

Configuration Data & Timing Components Timing Values Supply Current (IDD0)

Multiplier RA RB RF CT Frequency Duty Cycle 3.0V 5.0V

10 1.0 M 100 K 100 K 100 pF 1935 Hz 80.5% 6.3 uA 9.1 uA

10 5.0 M 100 K 100 K 100 pF 525 Hz 94.6% 3.9 uA 5.1 uA

10 5.0 M 100 K 5.0 M 100 pF 365 Hz 65.8% 3.9 uA 5.1 uA

100 1.0 M 100 K 100 K 100 pF 193 Hz 80.5% 6.3 uA 9.1 uA

100 5.0 M 100 K 100 K 100 pF 52.5 Hz 94.6% 3.9 uA 5.1 uA

100 5.0 M 100 K 5.0 M 100 pF 36.5 Hz 65.8% 3.9 uA 5.1 uA

Custom Silicon Solutions, Inc. 2009 19 Version 1.0, May 2009

CSS555(C) Application Circuits

Applications with Special Requirements

Capacitor Isolated Power Supply

In applications that require an isolated power supply, a simple charge pump can provide a very

efficient, capacitively coupled supply. The exceptionally low supply current of the CSS555 allows the

values of the coupling and filter capacitors (CC & CF) to be very small (and low cost). Adding a third

capacitor (CDIV) attenuates the amplitude of the input clock, allowing this circuit to be used with high

voltage AC supplies.

Design Example 1: Design Example 2:

VIN = 3V Square wave or pulse: VIN = 24VRMS Sine wave:

Freq (FCLK) = 32 KHz, Amplitude (VP-P)= 3.0V Freq (FCLK) = 60 Hz, Amplitude (VP-P)= 67.9V

Charge Pump Components: Charge Pump Components:

CC = 0.001 uF, CF = 0.033 uF CC = 0.033 uF, CF = 10 uF

D1, D2 = 1N914 CDIV =0.47uF, D1, D2 = 1N914

CC D2 D2

VDD CC VDD

VIN VIN

D1 CF (Clock or

CDIV D1 CF

(Clock or CSS555C CSS555C

AC Supply) VSS VDD AC Supply) VSS VDD

Components

Components

Trigger Dischg Trigger Dischg

Timing

Control

Timing

Control

Output Thresh Output Thresh

Signals Signals

Reset Control CDIV added to Reset Control

reduce VDD

RA, RLOAD > 1M RA, RLOAD > 1M

Design Equations: Design Equations:

Thevenin equivalent voltage source: Thevenin equivalent voltage source:

VOC = VIN (2 x VD) (VD = diode VON) VOC = VP-P x CC / (CC + CDIV) (2 x VD)

= 3.0 (2 x 0.4) = 67.9 x (0.033 / (0.033+0.47)) (2 x 0.4)

= 2.2V = 3.65V

ISC = FCLK x VOC x CC ISC = FCLK x VOC x (CC + CDIV)

= 32K x 2.2 x 0.001 = 70.4uA = 60 x 3.65 x (0.033uF + 0.47uF) = 110.3uA

RTHV = VOC / ISC = 31.3 K RTHV = VOC / ISC = 33.1 K

If RLOAD = 500 K: If RLOAD = 500 K:

VDD = VOC x RLOAD / (RLOAD + RTHV) VDD = VOC x RLOAD / (RLOAD + RTHV)

= 2.2 x 500K / (500K + 31.3K) = 2.07V = 3.65 x 500K / (500K + 33.1K) = 3.43V

Output Ripple Voltage (VRIP): Output Ripple Voltage (VRIP):

VRIP = IDD / (FCLK x CF) VRIP = IDD / (FCLK x CF)

= VDD / (RLOAD x FCLK x CF) = VDD / (RLOAD x FCLK x CF)

= 2.07 / (500K x 32K x 0.033) = 3.9mV = 3.43 / (500K x 60 x 10uF) = 11.4mV

Capacitor Isolation Examples

VIN Charge Pump Components VDD Output

Amplitude Frequency CC CF CDIV RLOAD VOUT VRIP

3.0VP-P 1.0 MHz Clock 0.001 uF 0.001 uF - 500 K 2.20V 4mV

3.0VP-P 100 KHz Clock 0.001 uF 0.01 uF - 500 K 2.16V 4mV

3.0VP-P 32 KHz Clock 0.001 uF 0.033 uF - 500 K 2.07V 4mV

5.0VP-P 10 KHz Clock 0.001 uF 0.1 uF - 500 K 3.50V 7mV

5.0VP-P 1 KHz Clock 0.01 uF 0.47 uF - 500 K 3.50V 15mV

12VRMS 60 Hz Sine 0.033 uF 10 uF 0.22 uF 500 K 3.20V 11mV

24VRMS 60 Hz Sine 0.033 uF 10 uF 0.47 uF 500 K 3.43V 11mV

Custom Silicon Solutions, Inc. 2009 20 Version 1.0, May 2009

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Fredrick J. Hill - Gerald R. Peterson - Digital Logic and Microprocessors-John Wiley & Sons (1984)Document25 pagesFredrick J. Hill - Gerald R. Peterson - Digital Logic and Microprocessors-John Wiley & Sons (1984)M1050% (2)

- Device ModelingDocument199 pagesDevice Modelingchiyu10100% (1)

- 236 MR-C MitsubishiDocument10 pages236 MR-C MitsubishiemtelesNo ratings yet

- Trina Solar TSM PC05 EUDocument2 pagesTrina Solar TSM PC05 EUPaul BenvieNo ratings yet

- LM2907 LM2917 Conversor F - VDocument18 pagesLM2907 LM2917 Conversor F - VAlejandra Vasquez GiraldoNo ratings yet

- 7555 CNDocument9 pages7555 CNdsdsds4No ratings yet

- NCP1234AD65R2GDocument33 pagesNCP1234AD65R2GAndré Frota PaivaNo ratings yet

- TLC 5540Document18 pagesTLC 5540EdgarJCNo ratings yet

- Fan 7314Document14 pagesFan 7314Kamal NonekNo ratings yet

- HS-2420RH - Fast Sample and HolDocument8 pagesHS-2420RH - Fast Sample and HolDeepa DevarajNo ratings yet

- MC 14521Document12 pagesMC 14521rrebollarNo ratings yet

- BQ 24725Document40 pagesBQ 24725nameless2061No ratings yet

- BQ 24726Document38 pagesBQ 247268ctanoNo ratings yet

- CCFL Inverter IC OZ960Document12 pagesCCFL Inverter IC OZ960davesworkshopNo ratings yet

- CD4047Document9 pagesCD4047Haryadi VjNo ratings yet

- CQ1565Document24 pagesCQ1565liberthNo ratings yet

- CD4047Document15 pagesCD4047mohankumarktvrNo ratings yet

- CDP 1802 Data Sheet 2Document7 pagesCDP 1802 Data Sheet 2DaveNo ratings yet

- 5V-0.5A Very Low Drop Regulator With Reset: DescriptionDocument6 pages5V-0.5A Very Low Drop Regulator With Reset: DescriptionDan EsentherNo ratings yet

- NCP 43080Document36 pagesNCP 43080TestronicpartsNo ratings yet

- Fan 7313Document11 pagesFan 7313KathafiNo ratings yet

- Green Mode PWM Controller Ap384XgDocument13 pagesGreen Mode PWM Controller Ap384XgbaphometabaddonNo ratings yet

- CQ0765RT DatasheetDocument24 pagesCQ0765RT DatasheetSergio Daniel BarretoNo ratings yet

- ISL6565A, ISL6565B: Multi-Phase PWM Controller With Precision R or DCR Current Sensing For VR10.X Application FeaturesDocument28 pagesISL6565A, ISL6565B: Multi-Phase PWM Controller With Precision R or DCR Current Sensing For VR10.X Application FeaturesFranciscoGomezNo ratings yet

- Datasheet MC3334Document6 pagesDatasheet MC3334odipasNo ratings yet

- CD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionDocument10 pagesCD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionWillianNo ratings yet

- 1565 RTDocument24 pages1565 RTJose Samuel Robelto RNo ratings yet

- LC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778Document12 pagesLC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778tarpinoNo ratings yet

- 10-Bit Digital-To-Analog Converters: Features DescriptionDocument22 pages10-Bit Digital-To-Analog Converters: Features Descriptionwolvering2009No ratings yet

- Description Features: CMOS Low-Power Monostable/Astable MultivibratorDocument15 pagesDescription Features: CMOS Low-Power Monostable/Astable Multivibratorதினேஷ் குமார்No ratings yet

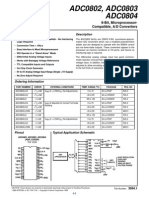

- ADC0802, ADC0803 ADC0804: Features DescriptionDocument17 pagesADC0802, ADC0803 ADC0804: Features DescriptionSuryananda PadmadinataNo ratings yet

- Irs27951s - RESONANT HALF-BRIDGE CONVERTER CONTROL ICDocument29 pagesIrs27951s - RESONANT HALF-BRIDGE CONVERTER CONTROL ICAnonymous R0s4q9X8No ratings yet

- U708Document28 pagesU708Sol De GabrielNo ratings yet

- Mc14541 Ic On Line - CNDocument8 pagesMc14541 Ic On Line - CNm_daneshvarNo ratings yet

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorDocument10 pagesSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiNo ratings yet

- D D D D D D D D D: DescriptionDocument36 pagesD D D D D D D D D: Descriptiongronci5410No ratings yet

- Ca3306 (A, C)Document17 pagesCa3306 (A, C)notaden1849No ratings yet

- ADMC201Document15 pagesADMC201Ariana Ribeiro LameirinhasNo ratings yet

- IC-ON-LINE - CN dm0365r 44840Document20 pagesIC-ON-LINE - CN dm0365r 44840MoscandoNo ratings yet

- Ad7524 Ep PDFDocument8 pagesAd7524 Ep PDFjlfepeNo ratings yet

- An 1138Document18 pagesAn 1138Marco Tulio Da SilvaNo ratings yet

- NCP 2171Document19 pagesNCP 2171mari_casuNo ratings yet

- sg3525 ONDocument10 pagessg3525 ONbob75No ratings yet

- BQ 24741Document30 pagesBQ 24741Aleksandar KeracNo ratings yet

- Intelligent CCFL Inverter Controller: FeaturesDocument12 pagesIntelligent CCFL Inverter Controller: FeaturesMirosław DżumakNo ratings yet

- Infineon TLE4270 2 DS v01 08 enDocument17 pagesInfineon TLE4270 2 DS v01 08 enGiapy Phuc TranNo ratings yet

- Max7490 Max7491Document18 pagesMax7490 Max7491xo9o6No ratings yet

- DPA001 - ATX-Dedicated PWM Controller DPA001: Customer Specific Device From ON SemiconductorDocument18 pagesDPA001 - ATX-Dedicated PWM Controller DPA001: Customer Specific Device From ON Semiconductorsontuyet82No ratings yet

- Ad9851 Cmos 180 MHZ Dds/Dac SynthesizerDocument24 pagesAd9851 Cmos 180 MHZ Dds/Dac SynthesizerVijay VigneshNo ratings yet

- DRV 103Document24 pagesDRV 103Rahul SharmaNo ratings yet

- NCP 1251Document22 pagesNCP 1251Cintya Cardozo100% (1)

- CQ 0765RTDocument24 pagesCQ 0765RTsonivitel100% (2)

- 9-0-9 Step Down TransformerDocument20 pages9-0-9 Step Down TransformerSarthak JoshiNo ratings yet

- MSM6544Document13 pagesMSM6544Shuvamay GuhaNo ratings yet

- Dual Bootstrapped 12 V MOSFET Driver With Output Disable ADP3418Document16 pagesDual Bootstrapped 12 V MOSFET Driver With Output Disable ADP3418Benny RoyNo ratings yet

- Octal Low-Side Driver For Bulb, Resistive and Inductive Loads With Serial Input Control, Output Protection and DiagnosticDocument19 pagesOctal Low-Side Driver For Bulb, Resistive and Inductive Loads With Serial Input Control, Output Protection and DiagnosticcqlNo ratings yet

- Board Resolution No 1 For ECT 2011Document21 pagesBoard Resolution No 1 For ECT 2011Reygie Bulanon MoconNo ratings yet

- 50 TOP TRANSISTORS Questions and Answers PDFDocument8 pages50 TOP TRANSISTORS Questions and Answers PDFamadullah janNo ratings yet

- User's Manual of Et-Stamp-Stm32Document12 pagesUser's Manual of Et-Stamp-Stm32ArturoCanalizoNo ratings yet

- Ece For RtuDocument65 pagesEce For RtuAnup BhowmickNo ratings yet

- VFD-M-D Manual enDocument169 pagesVFD-M-D Manual enmukeshsharmNo ratings yet

- LN 32 - 37 - 40 - 46 - 52A550P3F CH - GPRxxMUS (SM)Document201 pagesLN 32 - 37 - 40 - 46 - 52A550P3F CH - GPRxxMUS (SM)Roberd MihailovNo ratings yet

- Datasheet Circuito Integrado U643B FlasherDocument5 pagesDatasheet Circuito Integrado U643B FlasherZimp MSaulitosNo ratings yet

- HCPL 7710 300 AvagoDocument19 pagesHCPL 7710 300 Avagohanif khanNo ratings yet

- Guide To TannerEDA For VLSIDocument32 pagesGuide To TannerEDA For VLSINimit AroraNo ratings yet

- Solid State Physics Delhi University NotesDocument2 pagesSolid State Physics Delhi University Noteschandan Chaudhary50% (2)

- Crystal Resonator and OscillatorDocument4 pagesCrystal Resonator and OscillatorSatish MoorthyNo ratings yet

- Intelligent Automatic Plant Irrigation SystemDocument5 pagesIntelligent Automatic Plant Irrigation SystemIet TrichyNo ratings yet

- 52.13. The Real Diode: SolutionDocument1 page52.13. The Real Diode: SolutionBineilKcThapaNo ratings yet

- Ir1150 (S) (Pbf) Ir1150I (S) (Pbf) : Μpfc One Cycle Control Pfc IcDocument16 pagesIr1150 (S) (Pbf) Ir1150I (S) (Pbf) : Μpfc One Cycle Control Pfc IcBidu BiduNo ratings yet

- 24C32Document12 pages24C32SilviuCocoloșNo ratings yet

- Katalog Leistungselektronik KE03Document210 pagesKatalog Leistungselektronik KE03Bernardo RaphaelNo ratings yet

- SRPP PowerDocument9 pagesSRPP PowerCatalin Pancescu100% (1)

- Optoelectronic Devices and Sensors: Presented byDocument25 pagesOptoelectronic Devices and Sensors: Presented byDarrell Justin AbugNo ratings yet

- JZ1009AE SpecificationDocument13 pagesJZ1009AE SpecificationSafeer Ahmed60% (5)

- HC74ADocument7 pagesHC74AAnthony AndreyNo ratings yet

- 1 Lab Work ElectronicsDocument13 pages1 Lab Work ElectronicsFazil SultankulovNo ratings yet

- Railway Crack Detector Robot ReportDocument31 pagesRailway Crack Detector Robot ReportDebashishParidaNo ratings yet

- 4 Axis TB6560 CNC Stepper Motor Driver Board ControllerDocument8 pages4 Axis TB6560 CNC Stepper Motor Driver Board ControllerYilson SierraNo ratings yet

- Applied Physics in The 21Document426 pagesApplied Physics in The 21rasajatiNo ratings yet