Professional Documents

Culture Documents

CDP 1802 Data Sheet 2

Uploaded by

DaveOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CDP 1802 Data Sheet 2

Uploaded by

DaveCopyright:

Available Formats

1

TM

March 1997

CDP1802AC/3

High-Reliability CMOS 8-Bit Microprocessor

Features

For Use In Aerospace, Military, and Critical Industrial

Equipment

Minimum Instruction Fetch-Execute Time of 4.5s

(Maximum Clock Frequency of 3.6MHz) at V

DD

=

5V, T

A

= +25

o

C

Operation Over the Full Military

Temperature Range . . . . . . . . . . . . . . . -55

o

C to +125

o

C

Any Combination of Standard RAM and ROM Up to

65,536 Bytes

8Bit Parallel Organization With Bidirectional Data

Bus and Multiplexed Address Bus

16 x 16 Matrix of Registers for Use as Multiple Pro-

gram Counters, Data Pointers, or Data Registers

On-Chip DMA, Interrupt, and Flag Inputs

High Noise Immunity. . . . . . . . . . . . . . . . . . 30% of V

DD

Description

The CDP1802A/3 High-Reliability LSI CMOS 8-bit register

oriented Central-Processing Unit (CPU) is designed for use

as a general purpose computing or control element in a wide

range of stored-program systems or products.

The CDP1802A/3 includes all of the circuits required for

fetching, interpreting, and executing instructions which have

been stored in standard types of memories. Extensive

input/output (I/O) control features are also provided to facili-

tate system design.

The 1800 Series Architecture is designed with emphasis on

the total microcomputer system as an integral entity so that

systems having maximum flexibility and minimum cost can be

realized. The 1800 Series CPU also provides a synchronous

interface to memories and external controllers for I/O devices,

and minimizes the cost of interface controllers. Further, the I/O

interface is capable of supporting devices operating in polled,

interrupt-driven, or direct memory-access modes.

The CDP1802AC/3 is functionally identical to its predeces-

sor, the CDP1802. The A version includes some perfor-

mance enhancements and can be used as a direct

replacement in systems using the CDP1802.

This type is supplied in 40 lead dual-in-line sidebrazed

ceramic packages (D suffix).

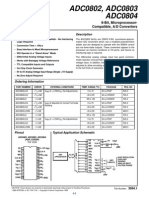

Pinout

CDP1802AC/3 (SBDIP)

TOP VIEW

Ordering Information

PACKAGE

TEMP. RANGE

(

o

C) 5V - 3.2MHz

PKG

NO.

SBDIP -55 to 125 CDP1802ACD3 D40.6

13

1

2

3

4

5

6

7

8

9

10

11

12

14

15

16

17

18

19

20

CLOCK

WAIT

CLEAR

Q

SC1

SC0

MRD

BUS 7

BUS 6

BUS 5

BUS 4

BUS 3

BUS 2

BUS 1

BUS 0

V

CC

N2

N1

N0

V

SS

28

40

39

38

37

36

35

34

33

32

31

30

29

27

26

25

24

23

22

21

V

DD

XTAL

DMA IN

DMA OUT

INTERRUPT

MWR

TPA

TPB

MA7

MA6

MA5

MA4

MA3

MA2

MA1

MA0

EF1

EF2

EF3

EF4

File Number 1441.2

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2002. All Rights Reserved

2

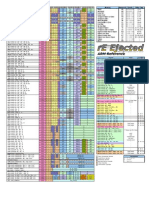

CDP1852

INPUT PORT

DATA CS1

CS2

CDP1852

OUTPUT

PORT

CLOCK

CS1

CS2 MA07

N0

MRD

MWR

N1

TPB DATA TPA

CDP1802

8BIT CPU

MRD

MA04

MWR

CS

CDP1824

32 BYTE RAM

MA07

DATA

CEO

TPA

MRD

8BIT DATA BUS

ADDRESS BUS

CDP1833

1KROM

DATA

FIGURE 1. TYPICAL CDP1802A/3 SMALL MICROPROCESSOR SYSTEM

CDP1802AC/3

3

Absolute Maximum Ratings Thermal Information

DC Supply Voltage Range, (V

DD

)

(All Voltages Referenced to V

SS

Terminal)

CDP1802AC/3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to +7V

Input Voltage Range, All Inputs . . . . . . . . . . . . . -0.5V to V

DD

+0.5V

DC Input Current, any One Input . . . . . . . . . . . . . . . . . . . . . . . . . 10mA

Thermal Resistance (Typical)

JA

(

o

C/W)

JC

(

o

C/W)

SBDIP Package . . . . . . . . . . . . . . . . . . . 55 15

Device Dissipation Per Output Transistor

T

A

= Full Package Temperature Range . . . . . . . . . . . . . . . . 100mW

Operating Temperature Range (T

A

)

Package Type D . . . . . . . . . . . . . . . . . . . . . . . . .-55

o

C to +125

o

C

Storage Temperature Range (T

STG

). . . . . . . . . . . .-65

o

C to +150

o

C

Lead Temperature (During Soldering)

At distance 1/16 1/32 In. (1.59 0.79mm)

from case for 10s max . . . . . . . . . . . . . . . . . . . . . . . . . . . +265

o

C

CAUTION: Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Recommended Operating Conditions T

A

= Full Package Temperature Range. For maximum reliability, operating conditions

should be selected so that operation is always within the following ranges

PARAMETER MIN MAX UNITS

DC Operating Voltage Range 4 6.5 V

Input Voltage Range V

SS

V

DD

V

Maximum Clock Input Rise or Fall Time - 1 s

Performance Specifications

PARAMETER V

DD

(V) -55

o

C TO +25

o

C +125

o

C UNITS

Minimum Instruction Time (Note 1) 5 4.5 5.9 s

Maximum DMA Transfer Rate 5 450 340 Kbytes/s

Maximum Clock Input Frequency,

Load Capacitance (C

L

) = 50pF, f

CL

5 DC-3.6 DC-2.7 MHz

NOTE:

1. Equals 2 machine cycles - one Fetch and one Execute operation for all instructions except Long Branch and Long Skip, which require 3

machine cycles - one Fetch and two Execute operations.

Static Electrical Specifications All Limits are 100% Tested

PARAMETER

CONDITIONS -55

o

C, +25

o

C +125

o

C

UNITS

V

OUT

(V) V

IN,

(V) V

CC,

V

DD

(V) MIN MAX MIN MAX

Quiescent Device Current, I

DD

- - 5 - 100 - 250 A

Output Low Drive (Sink) Current

(Except XTAL), I

OL

0.4 0, 5 5 1.20 - 0.90 - mA

XTAL 0.4 5 5 185 - 140 - A

Output High Drive (Source)

Current (Except XTAL), I

OH

4.6 0, 5 5 - -0.30 - -0.20 mA

XTAL 4.6 0 5 - -135 - -100 A

Output Voltage Low-Level, V

OL

- 0, 5 5 - 0.1 - 0.2 V

Output Voltage High-Level, V

OH

- 0, 5 5 4.9 - 4.8 - V

CDP1802AC/3

4

Input Low Voltage, V

IL

0.5, 4.5 - 5 - 1.5 - 1.5 V

Input High Voltage, V

IH

0.5, 4.5 - 5 3.5 - 3.5 - V

Input Leakage Current, I

IN

Any

Input

0, 5 5 - 1 - 5 A

Three-State Output Leakage

Current, I

OUT

0, 5 0, 5 5 - 1 - 5 A

NOTE:

2. 5V level characteristics apply to Part No. CDP1802AC/3, and 5V and 10V level characteristics apply to part No. CDP1802A/3.

Timing Specifications As a Function of T (T = 1/fCLOCK), C

L

= 50 pF

PARAMETER V

DD

(V)

LIMITS (NOTE 3)

-55

o

C, +25

o

C +125

o

C UNITS

High-Order Memory-Address Byte Setup to TPA Time, t

SU

5 2T-450 2T-580 ns

High-Order Memory-Address Byte Hold After TPA Time, t

H

5 T/2 +0 T/2 +0 ns

Low-Order Memory-Address Byte Hold After WR Time, t

H

5 T-30 T-40 ns

CPU Data to Bus Hold After WR Time, t

H

5 T-170 T-250 ns

Required Memory Access Time Address to Data, t

ACC

5 5T-300 5T-400 ns

NOTE:

3. These limits are not directly tested.

Implicit Specifications (Note 4) T

A

= -55

o

C to +25

o

C

PARAMETER SYMBOL V

DD

(V)

TYPICAL

VALUES UNITS

Typical Total Power Dissipation

Idle 00 at M(0000), C

L

= 50pF

f = 2MHz - 5 4 mW

Effective Input Capacitance any Input - C

IN

- 5 pF

Effective Three-State Terminal Capacitance Data Bus - - 7.5 pF

Minimum Data Retention Voltage - V

DR

- 2.4 V

Data Retention Current - I

DR

2.4 10 A

NOTE:

4. These specifications are not tested. Typical values are provided for guidance only.

Static Electrical Specifications All Limits are 100% Tested (Continued)

PARAMETER

CONDITIONS -55

o

C, +25

o

C +125

o

C

UNITS

V

OUT

(V) V

IN,

(V) V

CC,

V

DD

(V) MIN MAX MIN MAX

CDP1802AC/3

5

Dynamic Electrical Specifications C

L

= 50pF, Timing Measurement at 0.5 V

DD

Point

PARAMETERS V

DD

(V)

-55

o

C TO +25

o

C +125

o

C

UNITS MIN MAX MIN MAX

Progagation Delay Times, t

PLH

, t

PHL

Clock to TPA, TPB 5 - 275 - 370 ns

Clock-to-Memory High Address Byte, t

PLH

, t

PHL

5 - 725 - 950 ns

Clock-to-Memory Low Address Byte Valid, t

PLH

, t

PHL

5 - 340 - 425 ns

Clock to MRD, t

PLH

, t

PHL

5 - 340 - 425 ns

Clock to MWR, t

PLH

, t

PHL

5 - 275 - 370 ns

Clock to (CPU DATA to BUS) Valid, t

PLH

, t

PHL

5 - 430 - 550 ns

Clock to State Code, t

PLH

, t

PHL

5 - 440 - 550 ns

Clock to Q, t

PLH

, t

PHL

5 - 375 - 475 ns

Clock to N (0 - 2), t

PLH

, t

PHL

5 - 400 - 525 ns

Interface Timing Requirements (Note 5)

Data Bus Input Setup, t

SU

5 10 - 10 - ns

Data Bus Input Hold, t

H

5 175 - 230 - ns

DMA Setup, t

SU

5 10 - 10 - ns

DMA Hold, t

H

5 200 - 270 - ns

Interrupt Setup, t

SU

5 10 - 10 - ns

Interrupt Hold, t

H

5 175 - 230 - ns

WAIT Setup, t

SU

5 30 - 30 - ns

EF1-4 Setup, t

SU

5 20 - 20 - ns

EF1-4 Hold, t

H

5 100 - 135 - ns

Required Pulse Width Times

CLEAR Pulse Width, t

WL

5 150 - 200 - ns

CLOCK Pulse Width, t

WL

5 140 - 185 - ns

NOTE:

5. Minimum input setup and hold times required by Part CDP1802AC/3.

CDP1802AC/3

6

Performance Curves

FIGURE 2. TYPICAL MAXIMUM CLOCK FREQUENCY AS A

FUNCTION OF TEMPERATURE

FIGURE 3. TYPICAL MAXIMUM CLOCK FREQUENCY AS A

FUNCTION OF SUPPLY VOLTAGE

FIGURE 4. TYPICAL TRANSITION TIME vs LOAD

CAPACITANCE

FIGURE 5. MINIMUM OUTPUT HIGH (SOURCE) CURRENT

CHARACTERISTICS

FIGURE 6. MINIMUM OUTPUT LOW (SINK) CURRENT

CHARACTERISTICS

NOTES:

6. Idle = 00 at M (0000)

7. Branch = 3707 at M (8107)

FIGURE 7. TYPICAL POWER DISSIPATION AS A FUNCTION

OF CLOCK FREQUENCY FOR BRANCH

INSTRUCTION AND IDLE INSTRUCTION

5

4

3

2

1

0

6

7

8

35 45 55 65 75 85 95 105 115 25 125

S

Y

S

T

E

M

M

A

X

I

M

U

M

C

L

O

C

K

F

R

E

Q

U

E

N

C

Y

(

f

C

L

)

(

M

H

z

)

V

DD

= 5V

LOAD CAPACITANCE (C

L

) = 50pF

AMBIENT TEMPERATURE (T

A

) (

o

C)

3 4 5 6 7 8 9 10 12 2

SUPPLY VOLTAGE (V

DD

) (V)

11

5

4

3

2

1

0

6

7

S

Y

S

T

E

M

M

A

X

I

M

U

M

C

L

O

C

K

F

R

E

Q

U

E

N

C

Y

(

f

C

L

)

(

M

H

z

)

8

LOAD CAPACITANCE (C

L

) = 50pF

T

A

= 25

o

C

T

A

= 125

o

C

E

X

T

R

A

P

O

L

A

T

E

D

50 75 100 125 150 175 200 25

300

250

200

150

100

350

400

0

50

T

R

A

N

S

I

T

I

O

N

T

I

M

E

(

t

T

H

L

,

t

T

L

H

)

(

n

s

)AMBIENT TEMPERATURE (T

A

) = 25

o

C

0

LOAD CAPACITANCE (C

L

) (pF)

t

TLH

t

THL

-9 -8 -7 -6 -5 -4 -3 -10

2

3

4

5

6

1

0 -2 -1

O

U

T

P

U

T

H

I

G

H

(

S

O

U

R

C

E

)

C

U

R

R

E

N

T

(

I

O

H

-

m

A

)

DRAIN TO SOURCE VOLTAGE (V

DS

) (V)

GATE TO SOURCE VOLTAGE (V

GS

) = -5V

AMBIENT TEMPERATURE = -40 TO +85

o

C

0

25

20

15

10

5

30

35

1 2 3 4 5 6 7 0 8 9 10

GATE TO SOURCE VOLTAGE (V

GS

) = 5V

AMBIENT TEMPERATURE = -40

o

C TO +85

o

C

O

U

T

P

U

T

L

O

W

(

S

I

N

K

)

C

U

R

R

E

N

T

(

I

O

L

)

(

m

A

)

0

DRAIN-TO-SOURCE VOLTAGE (V

DS

) (V)

10

1

0.1

100

1000

0.01 0.1 1 10

AMBIENT TEMPERATURE (T

A

) = 25

o

C

CLOCK INPUT FREQUENCY (f

CL

) (MHz)

T

Y

P

I

C

A

L

P

O

W

E

R

D

I

S

S

I

P

A

T

I

O

N

(

P

D

)

(

m

W

)

VC

C

=

VD

D

=

+

5

V

VC

C

=

VD

D

=

5

V

B

R

A

N

C

H

ID

L

E

CDP1802AC/3

7

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporations quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

Burn-In Circuit

NOTE: Any output except XTAL.

FIGURE 8. TYPICAL CHANGE IN PROPAGATION DELAY AS A FUNCTION OF A CHANGE IN LOAD CAPACITANCE

TYPE V

DD

TEMPERATURE TIME

CDP1802AC 7V +125

o

C 160 Hours

FIGURE 9. BIAS/STATIC BURN-IN CIRCUIT

Performance Curves (Continued)

100

75

50

25

0

125

150

P

R

O

P

A

G

A

T

I

O

N

D

E

L

A

Y

T

I

M

E

(

t

P

L

H

,

t

P

H

L

)

(

n

s

)

50 100 150 200 0

LOAD CAPACITANCE ( C

L

) (pF)

AMBIENT TEMPERATURE

(T

A

) = 25

o

C

VC

C

=

VD

D

=

5

V

tP

H

L

t P

L

H

V

C

C

=

V

D

D

=

5

V

V

DD

V

DD

NC

NC

V

DD

V

DD

NC

13

1

2

3

4

5

6

7

8

9

10

11

12

14

15

16

17

18

19

20

28

40

39

38

37

36

35

34

33

32

31

30

29

27

26

25

24

23

22

21

ALL RESISTORS ARE 47k 20%

CDP1802AC/3

You might also like

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- MSDOS 2.11 Advanced Users GuideDocument130 pagesMSDOS 2.11 Advanced Users GuideDaveNo ratings yet

- Dry Hands MinecraftDocument1 pageDry Hands MinecraftBrandon RotzankNo ratings yet

- Introduction To Windows PDFDocument24 pagesIntroduction To Windows PDFRaymoon Twopass DaysNo ratings yet

- RCE Unpacking Ebook (Translated by LithiumLi) - UnprotectedDocument2,342 pagesRCE Unpacking Ebook (Translated by LithiumLi) - Unprotecteddryten7507No ratings yet

- How To Unbrick AT&T Galaxy S5 SM-G900A Soft-Brick Fix & Restore To Stock Firmware Guide - GalaxyS5UpdateDocument21 pagesHow To Unbrick AT&T Galaxy S5 SM-G900A Soft-Brick Fix & Restore To Stock Firmware Guide - GalaxyS5UpdateMarce CJ100% (1)

- CDP1802 DatasheetDocument28 pagesCDP1802 DatasheetDaveNo ratings yet

- cdp1802 CosmacDocument27 pagescdp1802 Cosmacrebirth90No ratings yet

- AD9850Document20 pagesAD9850olopezNo ratings yet

- Programmable Digital QPSK/16-QAM Modulator: Internal Reference Clock MultiplierDocument32 pagesProgrammable Digital QPSK/16-QAM Modulator: Internal Reference Clock MultiplierCristian Villalobos CampañaNo ratings yet

- M U Iti-Character lED Display/lamp Driver Cmos: Motorola Semiconductor Technical DataDocument22 pagesM U Iti-Character lED Display/lamp Driver Cmos: Motorola Semiconductor Technical DataNayeem MamunNo ratings yet

- CAT24C256 256 KB I C CMOS Serial Eeprom: DescriptionDocument18 pagesCAT24C256 256 KB I C CMOS Serial Eeprom: Descriptionjagadees21No ratings yet

- LC Mos High Speed 4-And 8-Channel 8-Bit Adcs Ad7824/Ad7828Document16 pagesLC Mos High Speed 4-And 8-Channel 8-Bit Adcs Ad7824/Ad7828meroka2000No ratings yet

- 32K CMOS SRAMDocument9 pages32K CMOS SRAMroozbehxoxNo ratings yet

- HCF4026B: Decade Counter/Divider With Decoded 7-Segment Display Output and Display EnableDocument11 pagesHCF4026B: Decade Counter/Divider With Decoded 7-Segment Display Output and Display EnableBima Richardo SihombingNo ratings yet

- Document Title: GM76C256CDocument11 pagesDocument Title: GM76C256CFrenk EndyNo ratings yet

- High-Performance Ee PLD ATF16V8C: FeaturesDocument18 pagesHigh-Performance Ee PLD ATF16V8C: FeaturesAmol LandgeNo ratings yet

- 2114 Sram DatasheetDocument8 pages2114 Sram DatasheetntrscribeNo ratings yet

- CA3161EDocument4 pagesCA3161EAlejandro Borrego DominguezNo ratings yet

- MCP3040 DatasheetDocument40 pagesMCP3040 Datasheetjiajun898No ratings yet

- Tle6220gp DatasheetDocument18 pagesTle6220gp Datasheetmaelo99999No ratings yet

- 000 0 Hy628100bllg 70Document9 pages000 0 Hy628100bllg 70Deepa DevarajNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- Green Mode PWM Controller Ap384XgDocument13 pagesGreen Mode PWM Controller Ap384XgbaphometabaddonNo ratings yet

- Dual D-Type Flip-Flop: Integrated CircuitsDocument8 pagesDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DNo ratings yet

- 32kx8bit CMOS SRAM: HY62256B SeriesDocument9 pages32kx8bit CMOS SRAM: HY62256B SeriesShiwam IsrieNo ratings yet

- Stp8Nc50 - Stp8Nc50Fp Stb8Nc50-1: N-Channel 500V - 0.7 - 8A To-220/To-220Fp/I2Pak Powermesh Ii MosfetDocument11 pagesStp8Nc50 - Stp8Nc50Fp Stb8Nc50-1: N-Channel 500V - 0.7 - 8A To-220/To-220Fp/I2Pak Powermesh Ii Mosfetmiguel angel jaramilloNo ratings yet

- ADC0808M: Total Unadjusted Error - . - 0.75 LSB Max Resolution of 8 Bits 100-s Conversion TimeDocument8 pagesADC0808M: Total Unadjusted Error - . - 0.75 LSB Max Resolution of 8 Bits 100-s Conversion TimeSushant MishraNo ratings yet

- ADMC201Document15 pagesADMC201Ariana Ribeiro LameirinhasNo ratings yet

- Isppac 10: Features Functional Block DiagramDocument23 pagesIsppac 10: Features Functional Block DiagramFaiber CalderonNo ratings yet

- CA3140Document20 pagesCA3140Brzata PticaNo ratings yet

- Sega IC7Document10 pagesSega IC7Java BatistaNo ratings yet

- MemoriaDocument7 pagesMemoriaEduardo TaglialavoreNo ratings yet

- Mid Semester 2012 TID203Document17 pagesMid Semester 2012 TID203peas002No ratings yet

- CD4553 Datasheet OKDocument13 pagesCD4553 Datasheet OKCong ThoNo ratings yet

- Uc 3845Document23 pagesUc 3845Bahram RN100% (1)

- Description Power Range: Analog Servo DriveDocument8 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- CB900K e 0203Document73 pagesCB900K e 0203Vuong NguyenNo ratings yet

- 7473Document8 pages7473Merényi OszkárNo ratings yet

- LC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778Document12 pagesLC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778tarpinoNo ratings yet

- Cmos Asynchronous Fifo 256 X 9, 512 X 9 and 1,024 X 9 IDT7200L IDT7201LA IDT7202LADocument14 pagesCmos Asynchronous Fifo 256 X 9, 512 X 9 and 1,024 X 9 IDT7200L IDT7201LA IDT7202LAnevdullNo ratings yet

- CD4047Document9 pagesCD4047Haryadi VjNo ratings yet

- TCM29C23, TCM129C23 Variable-Frequency PCM or DSP Interface: DescriptionDocument21 pagesTCM29C23, TCM129C23 Variable-Frequency PCM or DSP Interface: DescriptionmorlockbrNo ratings yet

- ADP3180Document20 pagesADP3180chrizzcloNo ratings yet

- Synchronous Presettable 4-Bit Counter: M B Order CodesDocument12 pagesSynchronous Presettable 4-Bit Counter: M B Order CodesMarimuthu RajNo ratings yet

- LM75Document12 pagesLM75tebeica2100% (2)

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Document8 pagesMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601No ratings yet

- CD74HC238Document7 pagesCD74HC238roozbehxoxNo ratings yet

- Adc0804 PDFDocument16 pagesAdc0804 PDFbudicw0% (1)

- ADC0802, ADC0803 ADC0804: Features DescriptionDocument17 pagesADC0802, ADC0803 ADC0804: Features DescriptionSuryananda PadmadinataNo ratings yet

- Cy62146dv30 Ram NokiaDocument12 pagesCy62146dv30 Ram NokiaandersonbheringNo ratings yet

- 8-BIT SERIAL SHIFT REGISTERDocument6 pages8-BIT SERIAL SHIFT REGISTERenriquevagoNo ratings yet

- Tle 6220 PDFDocument17 pagesTle 6220 PDFFabio JuniorNo ratings yet

- 6116ASP20Document9 pages6116ASP20BeNz BarrigaNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 1806ac CpuDocument30 pages1806ac CpuDaveNo ratings yet

- ATMEGA To Comp Video OutDocument1 pageATMEGA To Comp Video OutDaveNo ratings yet

- ZRAM Apple IIcDocument76 pagesZRAM Apple IIcDaveNo ratings yet

- CDP 1802Document27 pagesCDP 1802DaveNo ratings yet

- Micro 1st October 1977Document34 pagesMicro 1st October 1977DaveNo ratings yet

- 1806 CpuDocument30 pages1806 CpuDaveNo ratings yet

- Arm RefDocument2 pagesArm RefMichaelNo ratings yet

- W65C22S Versatile Interface Adapter (VIA) : June 1, 2009Document47 pagesW65C22S Versatile Interface Adapter (VIA) : June 1, 2009DaveNo ratings yet

- VGA Signal Generation with the XS Board GuideDocument18 pagesVGA Signal Generation with the XS Board GuideDaveNo ratings yet

- 8 Bit Audio DAC - Commodore Computer Based Sound Effects GeneratorDocument4 pages8 Bit Audio DAC - Commodore Computer Based Sound Effects GeneratorDaveNo ratings yet

- BBC Micro Service Manual 1985Document96 pagesBBC Micro Service Manual 1985Dave100% (1)

- Commodore 128 Basic 8 User ManualDocument242 pagesCommodore 128 Basic 8 User ManualDaveNo ratings yet

- An Inexpensive Operant Chamber Interface For The VIC 20 MicrocomputerDocument3 pagesAn Inexpensive Operant Chamber Interface For The VIC 20 MicrocomputerDaveNo ratings yet

- Commodore Component Catalog 1981Document194 pagesCommodore Component Catalog 1981Dave0% (1)

- CDP 1804Document16 pagesCDP 1804DaveNo ratings yet

- CDP 1802Document27 pagesCDP 1802DaveNo ratings yet

- 4Mb-SRAM 512Kx1BDocument18 pages4Mb-SRAM 512Kx1BserjaniNo ratings yet

- 65GZ032prg v0.11Document77 pages65GZ032prg v0.11DaveNo ratings yet

- SN76489ANDocument9 pagesSN76489ANDaveNo ratings yet

- HD 63 B 45 PDocument38 pagesHD 63 B 45 PDaveNo ratings yet

- Max 232 DatasheetDocument7 pagesMax 232 Datasheetraj_120581No ratings yet

- Synertek An3 6545 CRTCDocument23 pagesSynertek An3 6545 CRTCDaveNo ratings yet

- MC 6847Document26 pagesMC 6847DaveNo ratings yet

- Recommend For New Design: Old Company Name in Catalogs and Other DocumentsDocument21 pagesRecommend For New Design: Old Company Name in Catalogs and Other DocumentsDaveNo ratings yet

- Commodore Vic20 Rom SubroutinesDocument1 pageCommodore Vic20 Rom SubroutinesDaveNo ratings yet

- VIC-20 Interfacing Blue BookDocument52 pagesVIC-20 Interfacing Blue BookDave100% (2)

- Grant Park Platform Bedroom Set Furniture RowDocument1 pageGrant Park Platform Bedroom Set Furniture Rowjyzjz6sr65No ratings yet

- PD 957 AND BP 220 HOUSING DESIGN STANDARDSDocument5 pagesPD 957 AND BP 220 HOUSING DESIGN STANDARDSGeraldine F. CalubNo ratings yet

- GPT 1-15 LineBackerDocument4 pagesGPT 1-15 LineBackerazadeazNo ratings yet

- Protection Systems TransformerDocument14 pagesProtection Systems Transformerrajabharath12No ratings yet

- Sean Dickerson ResumeDocument3 pagesSean Dickerson ResumeSeanNo ratings yet

- Adhokshaj Mishra: Thwarting The Surveillance in Online CommunicationDocument24 pagesAdhokshaj Mishra: Thwarting The Surveillance in Online CommunicationGauravRajNo ratings yet

- Axial Shortening of Column in Tall Structure.Document9 pagesAxial Shortening of Column in Tall Structure.P.K.Mallick100% (1)

- DTOcean - Optimal Design Tools For Ocean Energy ArraysDocument94 pagesDTOcean - Optimal Design Tools For Ocean Energy ArraysWilson NevesNo ratings yet

- Holux M-1000C Bluetooth GPS Logger Manual GuideDocument22 pagesHolux M-1000C Bluetooth GPS Logger Manual Guidenabiloo2003No ratings yet

- Industrial HygieneDocument31 pagesIndustrial HygieneGautam SharmaNo ratings yet

- CV Summary for IT Position Seeking Recent GraduateDocument5 pagesCV Summary for IT Position Seeking Recent Graduateeang barangNo ratings yet

- Numerical Ability - Data Interpretation 3: 25 QuestionsDocument6 pagesNumerical Ability - Data Interpretation 3: 25 QuestionsAvishek01No ratings yet

- HT Series: 73-136Kw I Up To 12 Mppts Three PhaseDocument2 pagesHT Series: 73-136Kw I Up To 12 Mppts Three PhasesyamprasadNo ratings yet

- Environmentally-Friendly LPG Forklift Trucks with Superior Power & PerformanceDocument5 pagesEnvironmentally-Friendly LPG Forklift Trucks with Superior Power & PerformanceCarlos Miguel Apipilhuasco GonzálezNo ratings yet

- UntitledDocument47 pagesUntitledAndy SánchezNo ratings yet

- CNC Meldas 60-60sDocument300 pagesCNC Meldas 60-60schidambaram kasiNo ratings yet

- Plotting in AutoCAD - A Complete GuideDocument30 pagesPlotting in AutoCAD - A Complete GuideAdron LimNo ratings yet

- Zhao PeiDocument153 pagesZhao PeiMuhammad Haris HamayunNo ratings yet

- 38.11 Cum Total Qty of 4 Nos. Culvests 38.11x4 152.43 CumDocument14 pages38.11 Cum Total Qty of 4 Nos. Culvests 38.11x4 152.43 CumMandeep SinghNo ratings yet

- CSE 390 Bash Command ReferenceDocument3 pagesCSE 390 Bash Command Referencesam100% (1)

- RDSO - Specification No.M&C NDT 125 2004 Rev IDocument6 pagesRDSO - Specification No.M&C NDT 125 2004 Rev INiking ThomsanNo ratings yet

- 21st Bomber Command Tactical Mission Report 146, OcrDocument54 pages21st Bomber Command Tactical Mission Report 146, OcrJapanAirRaidsNo ratings yet

- 13-2021مواصفات الفنية لقطع غيار المكيفاتDocument4 pages13-2021مواصفات الفنية لقطع غيار المكيفاتTawfeeq Al-HababbiNo ratings yet

- IEC Certificate 1000V Single Glass 202304Document35 pagesIEC Certificate 1000V Single Glass 202304Marian ProzorianuNo ratings yet

- Chapter-Iv: Profile of The Hindu News PaperDocument5 pagesChapter-Iv: Profile of The Hindu News PaperMurugan SaravananNo ratings yet

- OFFICE 365 PROXY GUIDEDocument4 pagesOFFICE 365 PROXY GUIDErossloveladyNo ratings yet