Professional Documents

Culture Documents

Uploaded by

hariCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Uploaded by

hariCopyright:

Available Formats

Control Word Register: It is selected by Read/Write logic when A1A0=11.

If the CPU does a write operation to the 8253, the data is stored in the control word register

and is used to define the operation of the counter. The control word register can only be

written to, status information is available with the Read—Back command.

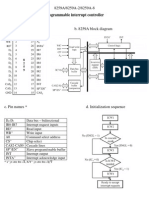

1) Discuss below mentioned terms with the help of INTEL 8259 diagram. [3M]

1) SP / EN b) IRR c) Interrupt Control Logic d)CAS2-CAS0 [6M]

̅̅̅̅/𝐄𝐍

𝑺𝑷 ̅̅̅̅: Slave Program / Enable Buffer. This is a dual function pin.

It is used as an input to determine whether the 8259A is to a master (/ = 1) or as a slave (/ =

0).

It is also used as an output to disable the data bus transceivers when data are being transferred

from the 8259A to the CPU.

When in buffered mode, it can be used as an output and when not in the buffered mode it is

used as an input.

Interrupt request register (IRR): IRR stores all the interrupt inputs that are requesting

service. Basically, it keeps all the interrupt requests in it in order to serve them one by

one on the priority basis.

Interrupt request register (IRR): IRR stores all the interrupt inputs that are requesting

service. Basically, it keeps all the interrupt requests in it in order to serve them one by one

on the priority basis

CAS0-CAS2: Cascade lines: The CAS lines form a private 8259A bus to control a multiple

8259A structure i.e. to identify a particular slave device. These pins are outputs of a master

8259A and inputs for a slave 8259A.

You might also like

- INTEL 8259A Programmable Interrupt ControllerDocument15 pagesINTEL 8259A Programmable Interrupt ControllerSri ShandilyaNo ratings yet

- Lecture 2Document7 pagesLecture 2tejashraj93No ratings yet

- Lecture-51 INTEL 8259A Programmable Interrupt ControllerDocument7 pagesLecture-51 INTEL 8259A Programmable Interrupt ControllerSahil KKNo ratings yet

- Programmable Interrupt Controller: Submitted ToDocument15 pagesProgrammable Interrupt Controller: Submitted ToCSE7 NDUBNo ratings yet

- 8259A ArchitectureDocument33 pages8259A ArchitectureSaksham GargNo ratings yet

- Module III - Stack and InterruptsDocument15 pagesModule III - Stack and InterruptsSNEHA MARIYA TOMNo ratings yet

- An Interrupt Is An Event Which Informs The CPU That Its Service (Action) Is Needed. - Sources of InterruptsDocument20 pagesAn Interrupt Is An Event Which Informs The CPU That Its Service (Action) Is Needed. - Sources of InterruptsMurali KrishnaNo ratings yet

- FALLSEM2022-23 CSE2006 ETH VL2022230103866 Reference Material I 08-09-2022 8259Document42 pagesFALLSEM2022-23 CSE2006 ETH VL2022230103866 Reference Material I 08-09-2022 8259Gaurav Kumar SinghNo ratings yet

- Programmable Interrupt Controller (PIC) - 8259Document23 pagesProgrammable Interrupt Controller (PIC) - 8259Arya ChandranNo ratings yet

- Where & How 8259 PIC Can Be Used To Handle Interrupts. The 8259A Programmable Interrupt ControllerDocument4 pagesWhere & How 8259 PIC Can Be Used To Handle Interrupts. The 8259A Programmable Interrupt ControllerKuberjung ThapaNo ratings yet

- 8259A Pic-Block DiagramDocument16 pages8259A Pic-Block DiagramKarthikeyaNo ratings yet

- Intel: 8259A Programmable Interrupt Controller (8259A/8259A-2)Document26 pagesIntel: 8259A Programmable Interrupt Controller (8259A/8259A-2)Thành Phố BuồnNo ratings yet

- Programmable Interrupt Controller (SUB: Microprocessor and Interfaces)Document7 pagesProgrammable Interrupt Controller (SUB: Microprocessor and Interfaces)mohit mishraNo ratings yet

- 8259 PicDocument14 pages8259 PicRahul AshokNo ratings yet

- 8259a Programmable Interrupt Controller 2Document42 pages8259a Programmable Interrupt Controller 2Tư Tưởng Tồi TànNo ratings yet

- 8259 8237Document13 pages8259 8237Harjot KaurNo ratings yet

- 8259a Programmable Interrupt Controller 2Document42 pages8259a Programmable Interrupt Controller 2annushaNo ratings yet

- 8259 ADocument16 pages8259 Aapi-26113146100% (1)

- 8259 Programmable ControllerDocument44 pages8259 Programmable ControllerShilpa ShettyNo ratings yet

- 8259A Programmable Interrupt Controller: Segment 8BDocument31 pages8259A Programmable Interrupt Controller: Segment 8Bgebretensaymamu11No ratings yet

- Programmable Interrupt ControllerDocument19 pagesProgrammable Interrupt ControllerHimanshi SinghNo ratings yet

- INTEL 8259A Programmable Interrupt ControllerDocument13 pagesINTEL 8259A Programmable Interrupt Controllerkaushikei22No ratings yet

- 8259Document57 pages8259Vats Alok100% (1)

- CH 13 PIC8259Document14 pagesCH 13 PIC8259gokulchandru0% (1)

- 8250 Programmable Interrupt ControllerDocument20 pages8250 Programmable Interrupt Controllerrobern ndoloNo ratings yet

- 8259 Programmable Interrupt Controller T.Srikrishna, M.SC, M.Tech, GVPDocument4 pages8259 Programmable Interrupt Controller T.Srikrishna, M.SC, M.Tech, GVPAbhayNo ratings yet

- 8259 A FinalDocument52 pages8259 A FinalAnitha Joseph100% (1)

- 8259 Programmable Interrupt ControllerDocument15 pages8259 Programmable Interrupt ControllerramkumarrajaNo ratings yet

- Unit 3 Interfacing: InterfaceDocument21 pagesUnit 3 Interfacing: Interfacechirag khandelwalNo ratings yet

- Memory InterfacingDocument16 pagesMemory InterfacingTharshninipriya RajasekarNo ratings yet

- 8259 - FinalDocument14 pages8259 - FinalkadaNo ratings yet

- Dma ControllerDocument28 pagesDma ControllerVEL TECHNo ratings yet

- Microprocessor - 8257 DMA Controller TutorialspointDocument5 pagesMicroprocessor - 8257 DMA Controller Tutorialspointpreethiu19phd036No ratings yet

- V Dinesh Ap/Ece SCE, TrichyDocument15 pagesV Dinesh Ap/Ece SCE, TrichykadaNo ratings yet

- 8259 Programmable Interrupt Controller for 8086 MicroprocessorDocument5 pages8259 Programmable Interrupt Controller for 8086 MicroprocessorMuthu KumarNo ratings yet

- Internal Test-Unit-3 AnswersDocument32 pagesInternal Test-Unit-3 AnswersDr.R.RAMANNo ratings yet

- PIC 8259 Interrupt Controller Block Diagram and DescriptionDocument15 pagesPIC 8259 Interrupt Controller Block Diagram and DescriptionSuyash Sanjay SrivastavaNo ratings yet

- 8259 Microprocessor: Some Features of This MicroprocessorDocument6 pages8259 Microprocessor: Some Features of This Microprocessorabu sayedNo ratings yet

- 8259 PIC: Intel's Prog. Interrupt ControllerDocument22 pages8259 PIC: Intel's Prog. Interrupt ControllerAsawari DudwadkarNo ratings yet

- DMA Controller - DMA Controller 8257: Internal Architecture of 8257Document8 pagesDMA Controller - DMA Controller 8257: Internal Architecture of 8257LAVANYA DURAISAMYNo ratings yet

- Lecture 7Document26 pagesLecture 7ShazidNo ratings yet

- MD Shabbir Hasan: Made byDocument15 pagesMD Shabbir Hasan: Made byShiva prasadNo ratings yet

- DatasheetDocument16 pagesDatasheetAmmu PuniNo ratings yet

- 8259 PIC Programmable Interrupt ControllerDocument6 pages8259 PIC Programmable Interrupt ControllerAyush DusejaNo ratings yet

- Microprocessor - 8257 DMA ControllerDocument5 pagesMicroprocessor - 8257 DMA ControllerFraud PriyanNo ratings yet

- 8259_PIC_RNMDocument43 pages8259_PIC_RNMRajNo ratings yet

- Dma 8257Document12 pagesDma 8257Ishmeet KaurNo ratings yet

- The Dma Controller 8257 and 8237 .Document78 pagesThe Dma Controller 8257 and 8237 .BETHWEL KIPROTICHNo ratings yet

- 8257 DmaDocument6 pages8257 DmaAdarsh AmzeNo ratings yet

- Microprocessor System: Session # 7Document13 pagesMicroprocessor System: Session # 7Aamir BhuttoNo ratings yet

- 8251Document24 pages8251Aravind IyerNo ratings yet

- 8257 - Microprocessors and Microcontrollers NotesDocument25 pages8257 - Microprocessors and Microcontrollers NotesFathima HeeraNo ratings yet

- 8259 Programmable Interrupt Controller (PIC) GuideDocument57 pages8259 Programmable Interrupt Controller (PIC) GuideSugunaNo ratings yet

- 8259A Programmable Interrupt ControllerDocument18 pages8259A Programmable Interrupt ControllerBasheer V.PNo ratings yet

- 8-bit Parallel I/O Device 8255 Programmable InterfaceDocument32 pages8-bit Parallel I/O Device 8255 Programmable Interfacesulekha saxenaNo ratings yet

- Programmable Interrupt Controller: X Jeistoštoix ̅, X/Y Je Isto Što I X/Y ̅Document4 pagesProgrammable Interrupt Controller: X Jeistoštoix ̅, X/Y Je Isto Što I X/Y ̅Pera DetlicNo ratings yet

- MicroprocessorDocument7 pagesMicroprocessorSanoxNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- AssignmentDocument7 pagesAssignmenthari100% (1)

- Eigen Value Detection For Spectrum Sensing inDocument5 pagesEigen Value Detection For Spectrum Sensing inhariNo ratings yet

- Intercom System Services RFQ Final PDFDocument65 pagesIntercom System Services RFQ Final PDFhariNo ratings yet

- 04 BasisDocument8 pages04 BasishariNo ratings yet

- How To Interface LED With 8086 Lab Trainer KitDocument1 pageHow To Interface LED With 8086 Lab Trainer KithariNo ratings yet

- EmfDocument5 pagesEmfhariNo ratings yet

- SS IiDocument53 pagesSS IihariNo ratings yet

- RL 2Document2 pagesRL 2hariNo ratings yet

- MITRES 6 007S11 hw10 SolDocument11 pagesMITRES 6 007S11 hw10 SolhariNo ratings yet

- Ordinance 1Document7 pagesOrdinance 1hariNo ratings yet

- Mci Quiz 2016Document2 pagesMci Quiz 2016hariNo ratings yet

- Digital Signal Processing Lab ManualDocument171 pagesDigital Signal Processing Lab ManualRaj Kumar ChowdaryNo ratings yet

- ECS 50 8086 Instruction Set Opcodes Operation Operands OpcodeDocument2 pagesECS 50 8086 Instruction Set Opcodes Operation Operands OpcodehariNo ratings yet

- 8086 MICROPROCESSOR LAB MANUALDocument14 pages8086 MICROPROCESSOR LAB MANUALhariNo ratings yet

- NotesDocument37 pagesNoteshariNo ratings yet

- MCI Chapter 1Document6 pagesMCI Chapter 1hariNo ratings yet

- Mosfet Small SignalDocument7 pagesMosfet Small SignalTabraizShahNo ratings yet

- Lecture1 PDFDocument4 pagesLecture1 PDFhariNo ratings yet

- Mci Chapter 2Document10 pagesMci Chapter 2hariNo ratings yet

- M Hari - Paper On ImageDocument6 pagesM Hari - Paper On ImagehariNo ratings yet

- Key Words: Arduino Uno, Induction MotorDocument49 pagesKey Words: Arduino Uno, Induction Motorhari100% (1)

- Chapter 3Document19 pagesChapter 3hariNo ratings yet

- MPMC ManualDocument93 pagesMPMC ManualsravyaNo ratings yet

- NotesDocument37 pagesNoteshariNo ratings yet

- Chapter 1Document6 pagesChapter 1hariNo ratings yet

- Errors in Measurement Theory and Statistical AnalysisDocument19 pagesErrors in Measurement Theory and Statistical AnalysishariNo ratings yet

- MCI Course OutlineDocument9 pagesMCI Course OutlinehariNo ratings yet

- Measurements and Sources of Errors1Document32 pagesMeasurements and Sources of Errors1hariNo ratings yet

- EE101 Measurement Guide to OhmmetersDocument5 pagesEE101 Measurement Guide to OhmmetersIqmal Shah PutraNo ratings yet