Professional Documents

Culture Documents

DOST-ASTI Electric Manual PDF

DOST-ASTI Electric Manual PDF

Uploaded by

roxy8marie8chanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DOST-ASTI Electric Manual PDF

DOST-ASTI Electric Manual PDF

Uploaded by

roxy8marie8chanCopyright:

Available Formats

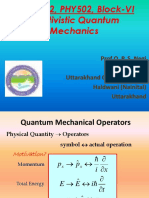

Electric VLSI Design

System

Training Manual

(Version 6.03)

Advanced Science and Technology Institute

Department of Science and Technology

ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

Loading Electric

Load Electric by either clicking the Electric icon on the desktop or by clicking on

Start → Programs → Electric.

The Electric Display

Shown below is a typical Electric display with some of its essential features.

Components Menu Pulldown Menu

Editing Window

Messages Window

Status Area

The editing window or design window is the largest window that initially says “No

facet in this window” (this indicates that no circuit is being displayed in that window).

The messages window is a text window that is typically found at the bottom of the

screen. This is used for all textual communication.

The pulldown menu contains a list of command options.

The components menu shows a list of nodes or components (in black outline) and

arcs or wires (in red outline) that can be used in the design. The selected arc is highlighted

with a bolder red outline.

The status area provides useful information about the design state.

2 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

SCHEMATIC

Setting the Schematic Technology

1. Click on Technology → Change Current Technology… from the pulldown menu.

2. Select schematic, analog as the technology (you will have to scroll down to find it).

3. Click OK. Notice that the symbols in the components menu will change to a

schematic set.

4. Click on the 4 – Port box in the components menu. This will convert all the

transistors in the components menu to 4-port transistors.

Changing the Lambda Size

1. Click on Technology → Change Units….

2. Change Lambda Size to 2000.

3. Change Display Units to Microns.

4. Change Internal Units to Half-Millimicrons.

5. Click OK.

Creating a New Library

1. Click on File → New Library… on the pulldown menu.

2. Type the library name that you want to create.

3. Click OK.

4. To save the new library, click on File → Save Library… on the pulldown menu.

5. On the Library File Creation window, browse through the file folders and select the

folder where you want to save the library.

6. Click OK. A message confirming that the new library has been saved will be

displayed in the message window.

Creating a New Schematic Facet

1. Click on Facets → Edit Facet.

2. Select the appropriate library.

3. Click New Facet.

4. Type the facet name that you want to create. Set the facet view to schematic.

5. Click OK.

Adding Components

1. Select the desired device in the components menu by using the left mouse button. A

white outline will appear around the chosen component.

2. Click on the design window to drop the component.

Selecting Components and Ports

1. To select a component, left click on the node or component in the

design window. A box that highlights the component appears, which

indicates that it has been selected.

In the second and third figure on the right, DC voltage sources are

shown with highlights indicating that these components were selected.

2. Ports are the connection sites on nodes where the wires connect. A

single node could have several ports. To select a port, click inside the

figure of the node near the location of the desired port.

The second and third figures on the right are voltage sources with the

positive and negative terminals selected, respectively.

3 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

Changing Components Properties

1. Highlight the device property label by clicking it. A white X mark should appear on

this label.

2. Double click the property label to access the device Information window.

3. Modify the properties that you want to change.

4. Click OK.

For the voltage sources in the previous page, the device property label is DC.

Adding Export Pins

Table 1

1. Select the node in the components

Export

menu. Export Pin

Characteristic

2. Click on the design window to drop the export

Vdd Power

pin.

3. Type the export name and indicate the Gnd Ground

appropriate export characteristic. Table 1 lists Input Input

the most commonly used export pins and their Output Output

corresponding export characteristics.

4. Click OK.

Adding Wires

1. In the components menu, check if the wire arc (blue line) is highlighted (with a bold

red outline). If it is not highlighted, click on the wire arc to select it.

2. Select the wire starting point by left clicking the component near the desired port.

Make sure that the desired port is highlighted, as discussed in Selecting Components

and Ports, before proceeding to the next step.

3. To create the wire, right click on another device port (to connect two device ports) or

anywhere on the design window (to create a wire segment). Once a wire has been

created, the other end is highlighted.

Adding Voltage/Current Sources

1. In the components menu, click the Spice node to access the Spice list.

2. Choose Voltage/Current Source from the Spice list.

3. Click on the design window to drop the voltage/current source.

4. Type the appropriate SPICE card parameters in the SPICE Card window. Table 2 is

a list of SPICE card formats for the different types of sources.

5. Click OK.

Adding Voltage/Current Meters

1. In the components menu, click the Spice node to access the Spice list.

2. Choose Voltage/Current Meter from the Spice list.

3. Click on the design window to drop the voltage/current meter.

4. To plot the voltage across a device, connect the voltage meter in parallel to that

device. To plot the current through a device connect the current meter in series to

that device.

Choosing the Circuit Analysis

1. In the components menu, click the Spice node to access the Spice list.

2. Three options (transient, DC and AC) are available for the circuit analysis. Choose

the appropriate analysis from the Spice list.

3. Click on the design window to drop the chosen analysis.

4 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

4. Type the appropriate SPICE card parameters in the SPICE Card window. Table 3 is

a list of SPICE card formats for the different analyses.

5. Click OK.

Table 2

Source Type Syntax Parameters

DC DC Value Value – the value of the source

V1 – initial value

V2 – peak value

PULSE(V1 V2 TD Tr Tf PW Pd) TD – initial delay time

Pulse

Tr – rise time

Tf – fall time

PW – pulse width

Pd – period

Piecewise (Ti Vi) – the value Vi of the source at

PWL(T1 V1 T2 V2 T3 V3…)

linear (PWL) time Ti

VO – offset value

VA – amplitude

FREQ – frequency in Hz

Sinusoid SIN(VO VA FREQ TD THETA PHASE)

TD – delay in seconds

THETA – damping factor per second

PHASE – phase in degrees

Table 3

Analysis Syntax Parameters

TSTEP – printing increment

TSTOP – final time

TSTART – starting time (if omitted,

TSTART is assumed to be zero)

TMAX – maximum step size

Transient TSTEP TSTOP <TSTART> <TMAX> <UIC>

UIC (Use Initial Condition) instructs

SPICE to use the specified initial

condition instead of the quiescent

operating point before beginning

the transient analysis.

START – starting value

DC START STOP STEP STOP – ending value

STEP – size of the increment

AC

With linear NP – number of points

frequency LIN NP FSTART FSTOP FSTART – start frequency in Hz

variation FSTOP – stop frequency in Hz

ND – number of frequency points

With decade per decade

DEC ND FSTART FSTOP

variation FSTART – start frequency in Hz

FSTOP – stop frequency in Hz

NO - number of frequency points

With octave per octave

OCT NO FSTART FSTOP

variation FSTART – start frequency in Hz

FSTOP – stop frequency in Hz

5 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

Saving the Schematic

To save the schematic design that you created, click on File → Save All Libraries from

the pulldown menu. (Using the shortcut control key Ctrl-S will also save the circuit.) A

message confirming that all facets of the library has been saved will be displayed in the

message window.

Creating an Icon for the Schematic

1. To create the icon facet of a schematic, open first its schematic facet. An icon is a

symbol facet associated to the schematic facet. Make sure that you have created all

the relevant exports before creating the icon.

2. To configure the appearance of the icon, Table 4

click on View → Icon Options…. Inputs on Left side

a. Make sure that the options have Outputs on Right side

the settings as listed in Table 4. Bidir. on Top side

b. Check the Draw leads option. Power on Top side

c. Check the Draw body option. Ground on Bottom side

d. Click OK. Clock on Left side

3. Click on View → Make Icon from the Export location Lead end

pulldown menu to create the icon facet. Export style Outward

A new design window will appear Export technology Schematic

containing the icon.

4. Edit the icon facet if you want to make further changes on its appearance.

Creating a Schematic SPICE Netlist

1. Click on Tools → Simulation Interface → SPICE Options….

a. Set the File format to SPICE3 and the SPICE level to 3.

b. Check the Use Node Names option.

c. Click on Use Header Cards From File. In the SPICE Model File Selection

window set the file type to All Files (*.*).

d. Browse through the folder list to locate the model file

(\\Electric\models\BSIM3v31.txt). Select the model file.

e. Click OK.

2. Before creating the SPICE netlist, make sure that all connections are checked. Refer

to Checking for Connectivity on the Tips section of this manual.

3. Click on Tools → Simulation Interface →Write SPICE Deck from the pulldown

menu to create a SPICE netlist of your schematic design.

4. Add a .cir extension to the file name.

5. Click Save.

6 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

LAYOUT

Setting the Layout Technology

1. Click on Technology → Change Current Technology… from the pulldown menu.

2. Select mocmossub as the technology (you will have to scroll down to find it).

3. Click OK. The symbols in the schematic menu will change to a mocmos subset.

Changing the Lambda Size

1. Click on Technology → Change Units.

2. Change Lambda Size to 350.

3. Change Display Units to Microns.

4. Change Internal Units to Half-Millimicrons.

5. Click OK.

Creating a New Layout Facet

1. Click on Facets → Edit Facet.

2. Select the appropriate library.

3. Click New Facet.

4. Type the facet name that you want to create. Set the facet view to layout.

5. Click OK.

Adding Nodes

1. Select a node from the components menu by using the left mouse button.

2. Click on the design window.

Note: Nodes in the mocmossub components menu are the ones in blue outlines.

Adding Arcs

1. Select an arc in the components menu.

2. Choose the arc starting point by left clicking the node near the desired port. Make

sure that the desired port is highlighted before proceeding to the next step.

3. To create the arc, right click on another node port (to connect two node ports) or

anywhere on the design window (to create an arc segment). Once an arc has been

created, the other end is highlighted.

Note: Arcs in the mocmossub components menu are the ones in red outlines.

Adding Export Pins

1. Select the node or arc to be exported.

2. Click on Export → Create Export….

3. Type the export name and indicate the appropriate export characteristic.

Checking the Layout for Design Rule Errors

Before proceeding to the simulation, check for any layout violations by running a Design

Rule Check (DRC). Design rules are the set of rules that must be followed when a given

design is laid out. To run a DRC, click on Tools → DRC → Hierarchical Check.

Saving the Layout

To save the layout that you created click on File → Save All Libraries from the

pulldown menu. (Using the shortcut control key Ctrl-S will also save the layout.) A

message confirming that all facets of the library has been saved will be displayed in the

message window.

7 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

Creating a SPICE Netlist Using the Layout Instance

1. Create a new schematic facet by following the instructions in the Schematic section

of this manual.

2. Click on Edit → New Facet Instance…. Click the name of the layout that you want

to instantiate.

3. Click OK and click on the design window. An instance box of the circuit layout now

appears on the design window.

4. Click on Export → Re-Export Everything.

5. Add necessary components for simulation such as voltage/current sources, ground,

voltage/current meters and load capacitances.

6. Save the circuit.

7. Change the current technology to mocmossub. Notice that the symbols in the

components menu will change from a schematic set to a layout set.

8. Click on Tools → Simulation Interface → SPICE Options….

a. Set the File format to SPICE3 and the SPICE level to 3.

b. Check the Use Node Names option.

c. Check the Use Parasitics option.

d. Click on Use Header Cards From File. In the SPICE Model File Selection

window set the file type to All Files (*.*).

e. Browse through the folder list to locate the model file

(\\Electric\models\BSIM3v31.txt). Select the model file.

f. Click OK.

9. Before creating the SPICE netlist, make sure that all connections are checked. Refer

to Transistor Layout on the Tips section of this manual.

10. Click on Tools → Simulation Interface →Write SPICE Deck from the pulldown

menu to create a SPICE netlist of your circuit design.

11. Add a .cir extension to the file name.

12. Click Save.

Determining the Area of the Layout

1. Click on Info → Measure Distance from the pulldown menu.

2. Press X on the keyboard. This key tells Electric that you are ready to specify the

starting point of your measurement.

3. Left click on the starting point of your measurement.

4. Left click on the end point of your measurement. A line appears and the value of the

length is shown.

5. Press the Enter key when done.

8 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

SIMULATION

Simulating the Circuit Behavior Using WinSpice

1. Run WinSpice by clicking on Start → Programs → WinSpice.

2. Open the *.cir file in WinSpice.

3. Wait until WinSpice starts displaying the simulation data. Press Esc to skip the

viewing of data points. WinSpice will automatically plot in a single window all

voltages and currents that were specified in the schematic.

Plotting Waveforms in Separate Windows

There are 2 ways to plot the parameters in separate windows.

Through the cir file:

1. Open the *.cir file using Notepad or any other text editor program.

2. Add the following line for each parameter to be plotted in a separate window:

.PRINT <analysis type> <parameter> <node name in parenthesis>

3. Run the simulation in WinSpice.

Example:

Plotting several parameters in one window,

.PRINT TRAN V(Va) V(Vb) V(Vout)

The above picture shows the transient response of Va, Vb and Vout superimposed in

one plot. To plot each parameter in separate windows, delete the above code and

rewrite it as:

.PRINT TRAN V(Va)

.PRINT TRAN V(Vb)

.PRINT TRAN V(Vout)

Through the WinSpice command prompt:

If the simulation has been run already, simply type the following on the WinSpice command

prompt:

plot <parameter><node name in parenthesis>

Example: Winspice 1 -> plot v(va)

Winspice 2 -> plot v(vb)

Winspice 3 -> plot v(vout)

9 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

SHORTCUT CONTROL KEYS

Open Library Ctrl-O

Save All Libraries Ctrl-S

Quit Ctrl-Q

Cut Ctrl-X

Copy Ctrl-C

Paste Ctrl-V

Duplicate Ctrl-M

Undo Ctrl-Z

Redo Ctrl-R

Rotate 90 Degrees Counterclockwise Ctrl-J

Select All Ctrl-A

Edit Facet Ctrl-N

Down Hierarchy Ctrl-D

Up Hierarchy Ctrl-U

Look Inside Highlighted Ctrl-P

Create Export Ctrl-E

Fill Window Ctrl-9

Zoom Out Ctrl-0

Zoom In Ctrl-7

Fit to Screen Ctrl-9

Focus on Highlighted Ctrl-F

Left Ctrl-4

Right Ctrl-6

Up Ctrl-8

Down Ctrl-2

Toggle Grid Ctrl-G

Delete Window Ctrl-W

Get Info Ctrl-I

10 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

ELECTRIC AND WINSPICE ERROR/ WARNING MESSAGES

Listed here are some of the most common errors encountered and their corresponding

solutions.

Electric Warning Messages

Warning: there may be inconsistent ground networks in <facet name>

Warning: there may be inconsistent power networks in <facet name>

Warning: top of source [nodex]/DC 3.3 in facet <facet name> not connected to

an export

This means that the ground and power in the circuit is not connected to the DC source.

Refer to Checking forCconnectivity in the Tips section of this manual.

WinSpice Error Messages

Illegal Characters in the SPICE Netlist

Error in ‘x.cir’ on line x : _nodex xxx x

=> unknown device type - error

To remove this type of error, follow these steps.

1. Open the *.cir file using Notepad or any other text editor program.

2. Scroll down and look for the illegal character ‘ ’. Substitute all occurrences of this

character with the letter ‘v’.

3. Save the text file.

Example:

** Sources and special nodes:

node11 Vout_1 Vout DC 0

Vnode9 Vout_1 0 sin(1.65 1m 1k 0 0 0)

Inode6 VDD Ibias DC 100u

Vnode2 VDD 0 DC 3.3

.PRINT TRAN I( node11) V(Vout_1)

.TRAN 10u 10m 10u

.END

Corrected Example:

Notice that all occurrences of ‘ ’ are now substituted with ‘v’.

** Sources and special nodes:

vnode11 Vout_1 Vout DC 0

Vnode9 Vout_1 0 sin(1.65 1m 1k 0 0 0)

Inode6 VDD Ibias DC 100u

Vnode2 VDD 0 DC 3.3

.PRINT TRAN I(vnode11) V(Vout_1)

.TRAN 10u 10m 10u

.END

Note: Text characters in a SPICE netlist are not case-sensitive.

11 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

Unconnected Nodes

Error in ‘x.cir’ on line x : mnodex Vout Vin 0 * N L=0.35U W=0.80U

Error in ‘x.cir’ on line x : mnodex Vdd Vin Vout * P L=0.35U W=3.20U

Only level 9 B3S0I can have 5 nodes

Note: * in the beginning of a line denotes it is a comment in the program and is therefore not an error, while an *

within a command denotes a missing node in the program

To remove this type of error, follow these steps.

1. Open the *.cir file using Notepad or any other text editor program.

2. Scroll down and look for the line mentioned in the error message.

Example: Mnode5 Vout Vin 0 * N L=0.35U W=0.80U

Mnode6 Vdd Vin Vout * P L=0.35U W=3.20U

3. Check the schematic for unconnected nodes in the transistors. For this example, the

bulk nodes are unconnected. Connect the bulk correspondingly (to ground for NMOS

and to Vdd for PMOS).

4. Save the schematic and recreate the SPICE netlist. Check if the line is correctly

modified by opening the *.cir file again.

Corrected Example: Mnode5 Vout Vin 0 0 N L=0.35U W=0.80U

Mnode6 Vdd Vin Vout Vdd P L=0.35U W=3.20U

Missing Model Files

Unable to find definition of model 1 – default assumed

Error: no unlabeled parameter permitted on mosfet

Error: unresolved model or device references: -p n

To remove this type of error, follow these steps.

1. Open the *.cir file using Notepad or any other text editor program.

2. Check if the model files for NMOS and PMOS are at the top most part of the file.

Example: .model P PMOS

+…

+…

.model N NMOS

+…

+…

3. If the model files are not found, go to the schematic window.

4. Check the spice options by clicking on Tools -> Simulation Interface -> SPICE

Options.

5. Make sure that all the settings are as specified in the Schematic section of this

manual.

6. Re-create the SPICE netlist by clicking on Tools -> Simulation Interface -> Write

SPICE Deck.

7. The model file should already be included in the *.cir file.

12 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

TIPS

Checking for Connectivity

Click on a component. All connections to the component should appear highlighted.

Example:

Notice that all the nodes connected to ground are highlighted. An example of an

unconnected wire is shown below:

The ground in black circle is not connected to the rest of the nodes connected to ground. If

this is the case, do the following:

1. Save the library (Ctrl-S).

2. Open the same library without closing the current facet.

3. Check for connectivity. The nodes concerned should now all be highlighted.

13 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

Transistor Layout

1. Overlapping two nodes does not automatically connect them. This will only generate

spacing errors. Make sure to connect them first using an arc and then move them closer

as in the example below:

a. Unconnected b. Connected c. Compress further

2. Try to move the node closer one step at a time while checking the message window

to see if a DRC error is generated. Or you can perform the DRC independently as

specified in the Layout section of this manual.

3. Checking their connectivity is the same as with the schematic. Clicking a node should

highlight all that is connected to it as in the figures below.

Connected Unconnected

All nodes connected are highlighted

4. If nodes are well connected, and there are still spacing errors, double click on the arc

connecting the nodes with the spacing error.

14 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

5. Uncheck “ends extend” (This option sizes the node / arc in proportion to the node

width).

6. Another cause of spacing errors is multiple components that are overlapping. One can

easily identify this by moving the component concerned and checking if there is an

extra component under it as in the example below.

Two coinciding nodes Extra component under the node

In this case, the extra component is not connected to the other nodes and so it

generates the other spacing errors. Simply delete the extra component and run a

DRC again.

7. If there is still a spacing error, then the two nodes must be really too close. One of

the nodes should therefore be moved until the error disappears.

15 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

DESIGN RULES FOR MOCMOSSUB TECHNOLOGY

Arc widths (minimum sizes):

metal1: 3

metal2: 3

metal3: 5

metal3: 3

metal4: 6

poly1: 2

poly2: 3

p/n active (active&select&well):

active: 3, select extends by 2, well extends by 6

active: 3

Pin/Node sizes (minimum sizes):

metal1: 3

metal2: 3

metal3: 5

metal3: 3

metal4: 6

poly1: 2

poly2: 3

active: 3

select: 2

well: 12

Special nodes:

p/n active-to-metal1 contact:

cuts 2x2, separated 3

metal1 extends around cut by 1 (4x4)

active extends around cut by 1.5 (5x5)

select extends around active by 2 (8x8)

well extends around active by 6 (17x17)

poly1-to-metal1 contact:

cuts 2x2, separated 3

metal1 extends around cut by 1 (4x4)

poly1 extends around cut by 1.5 (5x5)

poly2-to-metal1 contact:

cuts 2x2 , separated 3

metal1 extends around cut by 1 (4x4)

poly2 size: 3 (3x3)

poly1-to-poly2 (capacitor) contact:

cuts 2x2 [5.1], separated 3

poly2 size: 3 (3x3)

poly1 extends around poly2 by 2 (7x7)

Transistors:

active is 3 wide and sticks out by 3 (3x8)

poly1 is 2 wide and sticks out by 2 (7x2)

transistor area is 3x2

select surrounds active by 2 (7x12)

well surrounds active by 6 (15x20)

Via1:

cuts 2x2, separated 3

16 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

Advanced Science and Technology Institute

Department of Science and Technology

metal1 extends around cut by 1 (4x4)

metal2 extends around cut by 1 (4x4)

Via2:

cuts 2x2, separated 3

metal2 extends around cut by 1 (4x4)

metal3 extends around cut by: 2 (6x6) (if 3-metal process)

metal3 extends around cut by: 1 (4x4) (if 4-metal process)

Via3:

cuts 2x2, separated 4

metal3 extends around cut by: 1 (4x4)

metal4 extends around cut by: 2 (6x6)

Substrate/well contact:

select extends around active by 2

well extends around active by 6

DRC:

metal1-to-metal1: 3

metal2-to-metal2: 4

metal3-to-metal3: 3

metal4-to-metal4: 6

poly1-to-poly1: 3

poly1-to-active: 1

poly2-to-poly2: 3

poly2-to-active: 1

poly2-to-polyCut: 3

active-to-active: 3

select-to-trans: 3

polyCut/actCut-to-polyCut/actCut: 3

polyCut/actCut-to-via1: 2

polyCut-to-active: 2

actCut-to-poly: 2

via1-to-via1: 3

via1-to-via2: 2

via2-to-via2: 2

via3-to-via3: 4

Metals: Metal-1 Metal-2 Metal-3 Metal-4 Metal-5 Metal-6

2-metals: 3 wide 3 wide

3 apart 4 apart

1 over via1 1 over via1

3-metals: 3 wide 3 wide 5 wide

3 apart 3 apart 3 apart

1 over via1 1 over via1/2 2 over via2

4-metals: 3 wide 3 wide 3 wide 3 wide

3 apart 3 apart 3 apart 3 apart

1 over via1 1 over via1/2 1 over via2/3 1 over via3

5-metals: 3 wide 3 wide 3 wide 3 wide 4 wide

3 apart 3 apart 3 apart 3 apart 4 apart

1 over via1 1 over via1/2 1 over via2/3 1 over via3/4 1 over via4

6-metals: 3 wide 3 wide 3 wide 3 wide 3 wide 4 wide

3 apart 3 apart 3 apart 3 apart 3 apart 4 apart

1 over via1 1 over via1/2 1 over via2/3 1 over via3/4 1 over via4/5 1 over via5

Note: All dimensions are given in lambda.

17 ASTI-VCTI OpenLab Training Series

Introduction to Full-Custom Digital IC Design Flow

You might also like

- Scenario (Business Area) : Business Process: : Functional SpecificationDocument21 pagesScenario (Business Area) : Business Process: : Functional SpecificationsapeinsNo ratings yet

- Unit 1 - Semiconductor Devices and Technology & VLSI OverviewDocument60 pagesUnit 1 - Semiconductor Devices and Technology & VLSI Overviewphillip100% (1)

- Ec8353electronicdevicesandcircuitsunit2 180711152109Document126 pagesEc8353electronicdevicesandcircuitsunit2 180711152109dhivyaNo ratings yet

- Chapter 7. Switched-Inductor Regulators With Design Insight and Intuition (Power IC Design)Document119 pagesChapter 7. Switched-Inductor Regulators With Design Insight and Intuition (Power IC Design)Minh Hai RungNo ratings yet

- EC2 Exp2 F09Document17 pagesEC2 Exp2 F09Nurul Hanim HashimNo ratings yet

- Fabrication Stick-DiagramDocument68 pagesFabrication Stick-DiagramNikita ChawlaNo ratings yet

- Design of 12-Bit DAC Using CMOS TechnologyDocument5 pagesDesign of 12-Bit DAC Using CMOS TechnologysanthoshNo ratings yet

- Digital Logic: Tutorial CPSC 401Document18 pagesDigital Logic: Tutorial CPSC 401Shikha NayyarNo ratings yet

- I Had A Farm in Africa PDFDocument4 pagesI Had A Farm in Africa PDFAlberto de la FuenteNo ratings yet

- Design ProjectDocument19 pagesDesign Projectcard2717No ratings yet

- Nand, Nor Gates, Circuit Minimization and Karnaugh Maps: Prof. Sin-Min Lee Department of Computer ScienceDocument62 pagesNand, Nor Gates, Circuit Minimization and Karnaugh Maps: Prof. Sin-Min Lee Department of Computer ScienceYONIWO EDWARD TSEMINo ratings yet

- Chapter SixDocument5 pagesChapter Sixyunus memonNo ratings yet

- Logical Effort Designing Fast Cmos CircuitsDocument17 pagesLogical Effort Designing Fast Cmos CircuitsNishant MittalNo ratings yet

- 3M Busbar InsulationDocument8 pages3M Busbar Insulationbtd2011No ratings yet

- Decoder TocciDocument25 pagesDecoder ToccimohitNo ratings yet

- Cmos LayoutDocument13 pagesCmos LayoutshastryNo ratings yet

- Why VLSI? - Moore's Law. - The VLSI Design ProcessDocument28 pagesWhy VLSI? - Moore's Law. - The VLSI Design Processlim hyNo ratings yet

- Ecen 607 CMFB-2011Document44 pagesEcen 607 CMFB-2011Girish K NathNo ratings yet

- Design of A Single Ended Two Stage Opamp Using 90Nm Cmos GPDK TechnologyDocument8 pagesDesign of A Single Ended Two Stage Opamp Using 90Nm Cmos GPDK Technologygill6335No ratings yet

- C3.0 Operational Amplifiers II: Jeng-Han TsaiDocument12 pagesC3.0 Operational Amplifiers II: Jeng-Han Tsailinux14No ratings yet

- Digital Design of A Digital Combination LockDocument6 pagesDigital Design of A Digital Combination LockIJERAS-International Journal of Engineering Research and Applied Science (ISSN: 2349-4522)No ratings yet

- British AirwaysDocument16 pagesBritish AirwaysRahat Ali100% (7)

- Handbook of Spectrum Monitoring 2011Document678 pagesHandbook of Spectrum Monitoring 2011haripost100% (1)

- Drawing Stick Diagrams: Mask Layout and Stick Diagram For A CMOS InverterDocument3 pagesDrawing Stick Diagrams: Mask Layout and Stick Diagram For A CMOS InverterMuhammad JehangirNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument113 pagesDigital Integrated Circuits: A Design Perspectiveapi-127299018No ratings yet

- Basic VLSI SlidesDocument91 pagesBasic VLSI SlidesDivya AhujaNo ratings yet

- 3 - CMOS InverterDocument32 pages3 - CMOS Inverterroxy8marie8chanNo ratings yet

- Differential Voltage Current Conveyor (DVCC)Document81 pagesDifferential Voltage Current Conveyor (DVCC)raam0006100% (1)

- 01 Experiment 1 - Familiarization of Components and InstrumentsDocument5 pages01 Experiment 1 - Familiarization of Components and InstrumentsNikita Mayee sahooNo ratings yet

- LCDF4 Chap 03 P1Document33 pagesLCDF4 Chap 03 P1Parikshit KadamNo ratings yet

- Introduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)Document27 pagesIntroduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)TygerYashanshuNo ratings yet

- Solid State Device Modeling 1Document199 pagesSolid State Device Modeling 1DarwinNo ratings yet

- Microprocessor All Experiment IT PDFDocument22 pagesMicroprocessor All Experiment IT PDFSuraj KumarNo ratings yet

- Microprocessors & Interfacing Lab ManualDocument30 pagesMicroprocessors & Interfacing Lab Manualjeravi84100% (1)

- D 01Document209 pagesD 01Raj Boda0% (1)

- MPMC Lab Manual 15-11-2016Document139 pagesMPMC Lab Manual 15-11-2016k padmavathiNo ratings yet

- Ecl 203 MCQDocument3 pagesEcl 203 MCQresham k vNo ratings yet

- Optimal Design of A Reversible Full AdderDocument17 pagesOptimal Design of A Reversible Full AdderMohamedNo ratings yet

- PMOS, NMOS and CMOS Transmission Gate Characteristics.Document13 pagesPMOS, NMOS and CMOS Transmission Gate Characteristics.Prajwal KhairnarNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument84 pagesDigital Integrated Circuits: A Design PerspectivedurraizaliNo ratings yet

- Layout & Design RulesDocument17 pagesLayout & Design RulesSubir MaityNo ratings yet

- DLD Lab Manual 7 FlipFlopsDocument6 pagesDLD Lab Manual 7 FlipFlopsHanzala NasirNo ratings yet

- LIC FLEXI Lab Manual Second Experiment Student Copy-3Document5 pagesLIC FLEXI Lab Manual Second Experiment Student Copy-3Vignesh RamakrishnanNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument29 pagesDigital Integrated Circuits: A Design PerspectiveEMADNo ratings yet

- Labmanual Ecen474 PDFDocument81 pagesLabmanual Ecen474 PDFSURAJ GUPTANo ratings yet

- VLSI I - V CharacteristicsDocument46 pagesVLSI I - V CharacteristicsMALATHI .LNo ratings yet

- SCIM DesignDocument9 pagesSCIM DesignRafael BulaonNo ratings yet

- VLSI Notes 1 PDFDocument305 pagesVLSI Notes 1 PDFKishore KumarNo ratings yet

- Realtivistic Quantum Mechanics PPT SlidesDocument72 pagesRealtivistic Quantum Mechanics PPT SlidesSUNANDAN PANDANo ratings yet

- 8.4 A Case Study: Using LCD Module On DE2 BoardDocument19 pages8.4 A Case Study: Using LCD Module On DE2 BoardMas Shari0% (1)

- Cmos ReportDocument25 pagesCmos ReportNaveen KumarNo ratings yet

- Abdullah Khurram - Coal Lab 12Document9 pagesAbdullah Khurram - Coal Lab 12muhammad saadNo ratings yet

- 2 Bit Comparator PDFDocument12 pages2 Bit Comparator PDFSunith CkNo ratings yet

- 2 To 1 MuxDocument19 pages2 To 1 MuxTelmoDiez100% (1)

- MSDFFDocument20 pagesMSDFFShweta KumariNo ratings yet

- VLSI Design: 2 To 4 DecoderDocument1 pageVLSI Design: 2 To 4 DecoderohgiggitygooNo ratings yet

- Small Signal Model MOSFETDocument8 pagesSmall Signal Model MOSFETRAHUL100% (1)

- PDC Lab ManualDocument33 pagesPDC Lab ManualBhanu SriNo ratings yet

- Buchepalli Venkayamma Subbareddy Engineering College: Microwave & Optical Communication Lab ManualDocument31 pagesBuchepalli Venkayamma Subbareddy Engineering College: Microwave & Optical Communication Lab ManualMalakonda Reddy0% (1)

- Network Selected QuestionsDocument13 pagesNetwork Selected Questionsmisho_16100% (1)

- De Practical FileDocument140 pagesDe Practical FileSahil BharalNo ratings yet

- Lecture - Slides - 2.8 The Three-Terminal MOS Structure - Part 1Document6 pagesLecture - Slides - 2.8 The Three-Terminal MOS Structure - Part 1Cesar Santiago Bolaño SalazarNo ratings yet

- Eca Lab ManualDocument78 pagesEca Lab ManualNageswariah.MNo ratings yet

- Measure of Central TendencyDocument13 pagesMeasure of Central TendencyJB NavarroNo ratings yet

- Counting Techinques and Expected ValueDocument4 pagesCounting Techinques and Expected ValueJB NavarroNo ratings yet

- Counting Techniques and Expected Value ProblemsDocument13 pagesCounting Techniques and Expected Value ProblemsJB NavarroNo ratings yet

- 00 ELE 5 Orientation PDFDocument10 pages00 ELE 5 Orientation PDFJB NavarroNo ratings yet

- Procedure: Setting Up The BackgroundDocument10 pagesProcedure: Setting Up The BackgroundJB NavarroNo ratings yet

- = cos 4 = cos π 2 − 2sin π 3 − sin π 4 = sin 2t = 2e: a. x (n) n t t t c. x (t) d. x (n)Document2 pages= cos 4 = cos π 2 − 2sin π 3 − sin π 4 = sin 2t = 2e: a. x (n) n t t t c. x (t) d. x (n)JB NavarroNo ratings yet

- 01-Econ Common TermsDocument4 pages01-Econ Common TermsJB NavarroNo ratings yet

- CMOS Inverter LayoutDocument2 pagesCMOS Inverter LayoutRen ValerosoNo ratings yet

- Vector AlgebraDocument22 pagesVector AlgebraJB NavarroNo ratings yet

- Microstructure and Mechanical Properties of Resistance Upset Butt Welded 304Document11 pagesMicrostructure and Mechanical Properties of Resistance Upset Butt Welded 304Ashkaan OzlatiNo ratings yet

- CM 801 A Process Piping Design Dec 2020Document2 pagesCM 801 A Process Piping Design Dec 2020RAHUL MATHURNo ratings yet

- 20th Century Arch'ReDocument6 pages20th Century Arch'ReRachelleGomezLatrasNo ratings yet

- Your E-Vouchers: Order No.261267Document2 pagesYour E-Vouchers: Order No.261267João ReisNo ratings yet

- Instruction Manual: VHF Marine TransceiverDocument20 pagesInstruction Manual: VHF Marine TransceiverFRANK NIELE DE OLIVEIRANo ratings yet

- Types of Extrusion and Extrusion Equipment: NPTEL - Mechanical Engineering - FormingDocument8 pagesTypes of Extrusion and Extrusion Equipment: NPTEL - Mechanical Engineering - FormingtechopelessNo ratings yet

- Chapter 1: The Basics of Qualitative ResearchDocument9 pagesChapter 1: The Basics of Qualitative ResearchEijmert van der MeijNo ratings yet

- 3 Domain and Range Wsh3Document24 pages3 Domain and Range Wsh3Vishwas JainNo ratings yet

- R & D English GeneralBook 2009Document40 pagesR & D English GeneralBook 2009Suman Kakkirala100% (1)

- Kelas 8 Present Continous - 083001Document3 pagesKelas 8 Present Continous - 083001RachiyopaaNo ratings yet

- Present Value, Annuity, and PerpetuityDocument42 pagesPresent Value, Annuity, and PerpetuityEdwin OctorizaNo ratings yet

- Gcse Pe Coursework 6 Week Training ProgrammeDocument7 pagesGcse Pe Coursework 6 Week Training Programmeirugqgajd100% (2)

- How To Use Radiofacsimile Weather MapsDocument29 pagesHow To Use Radiofacsimile Weather MapsJerry HigdonNo ratings yet

- Radiodermatitis India TransDocument14 pagesRadiodermatitis India TransNaufal Fadhil Mufid LazuardiNo ratings yet

- Social Media and Youth Wellbeing ReportDocument33 pagesSocial Media and Youth Wellbeing ReportRayleen WangNo ratings yet

- Payment Process For Contribution UpdatedDocument4 pagesPayment Process For Contribution Updatedojo ayodeji johnsonNo ratings yet

- Febe Lynne Eclarin's ResumeDocument3 pagesFebe Lynne Eclarin's ResumeLeo Angelo SalinelNo ratings yet

- IELTS - Model Answer SpeakingDocument11 pagesIELTS - Model Answer SpeakingpimNo ratings yet

- Event Management Notes - Semester 5 - BA (JMC) - IP UniversityDocument109 pagesEvent Management Notes - Semester 5 - BA (JMC) - IP UniversityAadarsh Pandey0% (1)

- Ken 19M - DDX - APP - FWupdate - enDocument1 pageKen 19M - DDX - APP - FWupdate - enORARI CiamisNo ratings yet

- "Student Record Management System": A Project Report ONDocument11 pages"Student Record Management System": A Project Report ONGaurisankar DuttaNo ratings yet

- A Contingency View of Porter's "Generic Strategies"Document12 pagesA Contingency View of Porter's "Generic Strategies"Onos Bunny BenjaminNo ratings yet

- Refrigeration Systems & Comparative Study of VCRSDocument12 pagesRefrigeration Systems & Comparative Study of VCRSShashi Bhushan KumarNo ratings yet

- The Seventh Spark Knights of The TrinityDocument57 pagesThe Seventh Spark Knights of The TrinityNetNo ratings yet

- Final Draft Whitepaper With Track Changes Accepted SharksDocument10 pagesFinal Draft Whitepaper With Track Changes Accepted Sharksapi-676366041No ratings yet