Professional Documents

Culture Documents

TS-3-Combinational Circuits-II PDF

Uploaded by

Udai Kumar0 ratings0% found this document useful (0 votes)

3 views1 pageOriginal Title

TS-3-Combinational Circuits-II.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

3 views1 pageTS-3-Combinational Circuits-II PDF

Uploaded by

Udai KumarCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 1

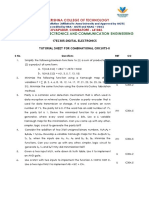

SRI KRISHNA COLLEGE OF TECHNOLOGY

(An Autonomous Institution |Affiliated to Anna University and Approved by AICTE|

Accredited by NBA - AICTE and NAAC – UGC)

KOVAIPUDUR, COIMBATORE - 641042.

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

17EC305-DIGITAL ELECTRONICS

TUTORIAL SHEET FOR COMBINATIONAL CIRCUITS-II

S No. Questions RBT CO

1. Simplify the following Boolean functions to (1) a sum of products form

(2) a product of sums form:

U C304.2

a. f1(A,B,C,D) = ABC’ + AB’D + BCD

b. f2(A,B,C,D) = π(1, 3, 5, 7, 13, 15)

2. Minimize the following function using a Karnaugh map of five

variables: f = ∑ (0, 2, 4, 6, 8, 10, 12, 14, 17, 19, 21, 23, 24, 25, 26, 27, 29,

U C304.2

31). Minimize the same function using the Quine-McCuskey tabulation

method.

3. Parity is a common error detection mechanism that is often used in

data reception or retrieval systems. Consider a parity encoder that is

used for data transmission or storage. If a word contains an even

number of 1’s, the parity bit is 0. If the word has an odd number of 1’s,

AN C304.5

the parity bit is 1. Derive the minimized function for a parity bit

generator, where every word contains 6 bits. Use a 6 variable

Karnaugh map for the minimization. Can you come up with any other,

simpler, logic circuit to generate the parity bit?

4. Consider the addition of two 3-bit unsigned binary numbers, A2A1A0 +

B2B1B0 = S2S1S0. Develop 6-variable Karnaugh maps for the outputs S2,

S1, S0, when the inputs are A2, A1, A0 and B2, B1, B0. Minimize the AN C304.5

functions. Can you come up with any other, simpler, logic circuit to

generate S2, S1 and S0? Why did minimization fail?

5. Given a two input MUX, write down its truth table. Use it to implement

U C304.2

an AND gate.

6. Use a MUX with two inputs to implement the function A XOR B XOR C.

U C304.5

Use a two input MUX to implement AB + BC + CA.

You might also like

- 17EC305-Digital Electronics-Detailed Lecture PlanDocument3 pages17EC305-Digital Electronics-Detailed Lecture PlanUdai KumarNo ratings yet

- TS-2-Combinational Circuits-I PDFDocument1 pageTS-2-Combinational Circuits-I PDFUdai KumarNo ratings yet

- TS 1 A Logic MinimizationDocument1 pageTS 1 A Logic MinimizationUdai KumarNo ratings yet

- TS-1-Number Systems PDFDocument2 pagesTS-1-Number Systems PDFUdai Kumar33% (3)

- TS-3-Combinational Circuits-II PDFDocument1 pageTS-3-Combinational Circuits-II PDFUdai KumarNo ratings yet

- Boolean Algebra and Logic GatesDocument50 pagesBoolean Algebra and Logic GatesUdai KumarNo ratings yet

- Accreditation by Nba JntuDocument31 pagesAccreditation by Nba JntuUdai KumarNo ratings yet

- Down Meba MathDocument101 pagesDown Meba MathUdai KumarNo ratings yet

- 01 ReviewofNumberSystems PDFDocument17 pages01 ReviewofNumberSystems PDFUdai KumarNo ratings yet

- Blooms TaxonomyDocument1 pageBlooms TaxonomysivaeeinfoNo ratings yet

- Basic CalculusDocument292 pagesBasic Calculuslouis_kwan_10% (1)

- 4th Sem.-Cs1252 QBDocument6 pages4th Sem.-Cs1252 QBSuba BaluNo ratings yet

- COADocument137 pagesCOAThonta DariNo ratings yet

- Applications DSPDocument85 pagesApplications DSPUdai KumarNo ratings yet

- Ejsr 72 2 05Document11 pagesEjsr 72 2 05Udai KumarNo ratings yet

- Asynchronous Sequential NetworkDocument20 pagesAsynchronous Sequential NetworkGulzar Ahamd100% (1)

- 01 DrakeDocument5 pages01 DrakeNithin ShivashankarNo ratings yet

- Paper C54Document5 pagesPaper C54Udai KumarNo ratings yet

- CSE243: Introduction To Computer Architecture and Hardware/Software InterfaceDocument25 pagesCSE243: Introduction To Computer Architecture and Hardware/Software InterfaceUdai KumarNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Adc Lab Manual - Cycle 2Document28 pagesAdc Lab Manual - Cycle 2Karthik KarthiksNo ratings yet

- RT 21053112017Document1 pageRT 21053112017RaunaqNo ratings yet

- Chapter 1 - Understand Numbering SystemDocument30 pagesChapter 1 - Understand Numbering SystemF1001 NUR SHUHADA AHMADNo ratings yet

- Wallace Tree Multiplier Part1Document5 pagesWallace Tree Multiplier Part1vineeth_vs_4No ratings yet

- CSA Unit 1 NotesDocument46 pagesCSA Unit 1 Notes6747 mohammedjeelaniNo ratings yet

- Logic GatesDocument14 pagesLogic GatesMuhammad wali JanNo ratings yet

- 6 Logic Gates and Boolean Algebra 3Document18 pages6 Logic Gates and Boolean Algebra 3shahnawazuddinNo ratings yet

- Graphic Organizer - Venn Diagram ActivityDocument2 pagesGraphic Organizer - Venn Diagram ActivityDevina BranzuelaNo ratings yet

- Answer:: Name: Yohanes Pratama Naibaho Student ID: 001201900101Document3 pagesAnswer:: Name: Yohanes Pratama Naibaho Student ID: 001201900101Kelvin Putra UtamaNo ratings yet

- Number System in DeldDocument283 pagesNumber System in DeldAnand Gharu100% (1)

- CHAPTER 3 - 4-Flags and Data Processing Instructions - 3Document85 pagesCHAPTER 3 - 4-Flags and Data Processing Instructions - 3Weehao SiowNo ratings yet

- Class 7 Worksheet 25th June - ComputerDocument16 pagesClass 7 Worksheet 25th June - ComputervmhsphysicsNo ratings yet

- Department of Computer Science, CUI Lahore Campus: CSC102 - Discrete Structures by Mahwish WaqasDocument41 pagesDepartment of Computer Science, CUI Lahore Campus: CSC102 - Discrete Structures by Mahwish WaqasSubhan ShahzadNo ratings yet

- 2.3 - DE Unit 2 - 4variable - KMAP, Don't Care Conditions, QuineMc-Clusky MethodDocument34 pages2.3 - DE Unit 2 - 4variable - KMAP, Don't Care Conditions, QuineMc-Clusky Methodnaman shahNo ratings yet

- Number Systems TopicDocument9 pagesNumber Systems TopicHeybaejuliaNo ratings yet

- Bitwise OperatorsDocument15 pagesBitwise OperatorsArya BhattNo ratings yet

- Arithmetic and Logic Unit (ALU) PDFDocument13 pagesArithmetic and Logic Unit (ALU) PDFnathulalusaNo ratings yet

- Dr. Praveen Kumar: School of Electronics Engineering (SENSE) VIT-AP University E-MailDocument25 pagesDr. Praveen Kumar: School of Electronics Engineering (SENSE) VIT-AP University E-MailrerereNo ratings yet

- Qs-1) What Are Redundant Bits? Suppose The Number of Data Bits Is 7, Then Calculate The Redundant Bits. AnswerDocument6 pagesQs-1) What Are Redundant Bits? Suppose The Number of Data Bits Is 7, Then Calculate The Redundant Bits. AnswerMd. Azizul Haque 180235No ratings yet

- vb6 crc32Document3 pagesvb6 crc32Jhon ThomasNo ratings yet

- L4 Slides - Representations - From Clay To Silicon - Y8Document51 pagesL4 Slides - Representations - From Clay To Silicon - Y8Sage PaclibarNo ratings yet

- Slide 2 - Computer Number SystemDocument104 pagesSlide 2 - Computer Number SystemSanskriti LamichhaneNo ratings yet

- Ch.2 Number Systems and CodesDocument82 pagesCh.2 Number Systems and CodesDiane GutierrezNo ratings yet

- BOOLEAN Notes Assignment 1Document14 pagesBOOLEAN Notes Assignment 1Sasuke ItachiNo ratings yet

- LAB 3 Binary-Hexadecimal NotesDocument5 pagesLAB 3 Binary-Hexadecimal NotesJohnNo ratings yet

- Verilog EXPERIMENT 2Document11 pagesVerilog EXPERIMENT 2udayNo ratings yet

- 03 OSCA Logic Gate Exercise Solutions: Section ADocument8 pages03 OSCA Logic Gate Exercise Solutions: Section ASadiqu ZzamanNo ratings yet

- Lesson 2 - Number Systems and Data RepresentationDocument3 pagesLesson 2 - Number Systems and Data RepresentationNoel S. De Juan Jr.No ratings yet

- (P Q) (P Q) : Truth Table For EXCLUSIVE OR Exclusive orDocument4 pages(P Q) (P Q) : Truth Table For EXCLUSIVE OR Exclusive orJunaid AkramNo ratings yet

- Functions of Combinational Logic NotesDocument21 pagesFunctions of Combinational Logic NotesAbdullah AftabNo ratings yet