Professional Documents

Culture Documents

06aug201707082204 Munmee Borah 2 358-362

Uploaded by

Munmee BorahOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

06aug201707082204 Munmee Borah 2 358-362

Uploaded by

Munmee BorahCopyright:

Available Formats

Advanced Research in Electrical and Electronic Engineering

p-ISSN: 2349-5804; e-ISSN: 2349-5812 Volume 3, Issue 5, October-December, 2016, pp. 358-362

© Krishi Sanskriti Publications

http://www.krishisanskriti.org/Publication.html

A Comparative Analysis on All Digital Phase

Locked–Loops

Munmee Borah1 and Tulshi Bezboruah2

1,2

Department of Electronics & Communication Technology Gauhati University Guwahati, India

E-mail: 1munmeeborah01@gmail.com, 2zbt_gu@yahoo.co.in

Abstract—In this paper we have designed and implemented two all- In this work we have designed two ADPLL models with

digital phase – locked loop models one with an XOR gate as phase EXOR gate as PD and with edge triggered JK FF as PD and

detector and the other with edge triggered JK flip flop as Phase compare their results after simulation by using Very High

Detector. The proposed models are implemented by using Very High Speed Integrated Circuit Hardware Description Language

Speed Integrated Circuit Hardware Description Language. The

simulation has been performed in ISE Xilinx 14.2 software platform

(VHDL).

to study the power consumptions and synthesis characteristics of the

models. The power consumptions of the models are evaluated from

2. REVIEW OF RELATED WORKS

Xilinx Power Estimator. It is observed that the power consumption of

the model with XOR gate and with edge triggered JK FF phase In 1999, Nam Guk Kim et al. have proposed ADPLL to

detector are recorded to be 15 mW and 21 mW respectively at provide both large locking frequency range and good tracking

ambient temperature of 25° C. performance. They observed that the model does not suffer

from phase jitter due to the quantization effect of the

Keywords: ADPLL, EXOR, phase detector, VHDL. numerically controlled oscillator [7].

1. INTRODUCTION In 2003, R. Stefo, J. Schreiter, J. U. Schlussler and R.

Schuffny have designed a high resolution ADPLL frequency

The phase locked loop (PLL) is a self - control closed loop synthesizer model for FPGA- and ASIC-based applications.

system for tracking signal phase. It has a wide range of They implemented their model in 4OOBG432VIRTEX FPGA.

applications including analog and digital communications, and They described the whole model using synthesizable VHDL

other electronic fields. The first PLL was introduced in 1923 [8].

by Edward Appleton that introduced Automatic

In 2003, T. Olsson and P. Nilsson designed and fabricated a

Synchronization of triode oscillators which were basic

prototype all-digital PLL clock multiplier using a 0. 3 5 ~

elements of radio communications [1, 2]. In 1940s, the PLL

CMOS process [9].

was widely used in synchronization of horizontal and vertical

sweep oscillators in television receivers for transmission of In 2006 C. H. Shan, Z. Chen and Wang, Y proposed an

synchronized pulses [3]. In 1960, the single chip PLL ADPLL model with double edge triggered D-FF. The model

integrated circuit (IC) was developed and it was used in designed using VHDL and implemented on a prototype based

various electrical engineering fields as well as in radio on a chip of VIRTEX FPGA VCU400Bg432 [10].

communication. In 1970, the design and implementation of

In 2009 C. H. Shan, Z. Chen and J. Jiang designed an ADPLL

digital PLL’s (DPLL’s) started because of the popularity of

system with high performance on wideband frequency

large-scale integrations (LSI’s) [4]. The first All digital phase

tracking and also proposed a balance mechanism for

locked loop (ADPLL) was started in 1980 [5]. The advantages

improving system performance on noise. The system is

of digital PLL’s over analog PLL’s are (i) less sensitivity to dc

designed by using VHDL and implemented on a FPGA chip

drifts and component aging, (ii) ease in building higher order

[11].

loops, (iii) no need for adjustment, (iv) ability to perform

sophisticated signal processing on the IC chips, (v) more In 2012 M. H. Shabaany and M. Saneei presented ADPLL

flexible and versatile. The classical DPLL’s are still semi – with a new phase frequency detector and controlled oscillator

analog circuit, therefore the ADPLL and the software with body-biasing for 0.1 – 1.1 GHz frequency range [12].

controlled PLL (SCPLL) has gained increased attention [4].

In 2014, A. Patil and R. Saini proposed a method of

The ADPLL’s is implemented only by using digital blocks.

implementing a linear ADPLL based on FPGA to obtain high

ADPLL’s have become lucrative due to its scalability, faster

frequency resolution & short locking time. They designed the

lock in time and easy redesign with process changes [6, 14].

A Comparative Analysis on All Digital Phase Locked–Loops 359

ADPLL model using ISE Xilinx 9.2. They observed the centre (i) EXOR PD

frequency of the model is 100 kHz [13].

EXOR gate PD simply a two input EXOR gate that utilizes the

In 2016 N. Tripathi and S. N. Pradhan presented a power property of EXOR gate. Since the EXOR gate produces output

efficient design of ADPLL using digital loop filter instead of with logic high only when both the inputs are not equal and

the conventional one. They implemented their model using that can be seen as the phase difference between two inputs

Verilog HDL and is synthesized using Cadence RTL complier [15].

[6].

3. THE OBJECTIVE AND METHODOLOGY

The main objective of the proposed work is to design and

implementation of ADPLL models with EXOR gate as PD and

with edge triggered JK FF as PD. The simulation of the model

has been performed in Xilinx 14.2 platform by using VHDL to

study power consumption and synthesis details of the designed

ADPLL model.

The methodologies towards implementation of the proposed

work are: (i) each block of the model is design and simulated Fig. 1: Block diagram of ADPLL

by using Xilinx 14.2., (ii) behavioral simulation of the overall

model by integrating individual blocks is done to study

various aspects of the model and (iii) XPE power estimator is

used to calculate power consumption of the model.

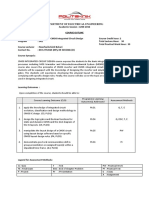

4. PROPOSED ADPLL MODEL

In ADPLL, all components used are digital in nature. ADPLL

consists of digital phase detector (PD), digital loop filter (LF)

and digital controlled oscillator (DCO) which are connected to

form a closed – loop feedback path as shown in Fig.1. The

advancements of very - large scale integration circuits

(VLSI’s), APLL’s have abilities to achieve the requirements

of communication applications. The ADPLL is most widely

used since FPGA is an exclusively a digital device where

ADPLL is to be implement. The proposed ADPLL models

with EXOR gate as PD and edge triggered JK FF as PD is

shown in Fig.2 (a) and (b) [6, 16, 17]. Here K counter is used

as digital LF and DCO is formed by combination of increment

decrement counter (ID counter) and divide by N counter.

5. THE ANALYSIS OF INDIVIDUAL BLOCKS

Details of each individual blocks of the corresponding circuit

Fig. 2 (a). ADPLL circuit diagram with EXOR PD

of ADPLL model depicted in Fig.2 (a) and (b) are given

below:

A. Digital PD

In this ADPLL design we have implemented two types of PD

namely EXOR gate PD and edge triggered JK FF PD. It

compares the phase of the input reference signal with the

phase of the produced ADPLL output signal. It generates an

error signal which is proportional to the phase difference

between these two signals.

Advanced Research in Electrical and Electronic Engineering

p-ISSN: 2349-5804; e-ISSN: 2349-5812 Volume 3, Issue 5, October-December, 2016

360 Munmee Borah and Tulshi Bezboruah

6. THE SIMULATIONS

Simulation of the proposed model is done by using VHDL

code in Xilinx 14.2 software. The schematic diagram of

synthesized ADPLL models with EXOR gate as PD and with

JK FF as PD are shown in Fig.3 (a) and (b) respectively. The

behavioural simulation results for both cases are shown in Fig.

4 (a) and (b). From the simulation results it is observed that

ADPLL model with EXOR gate as PD, locked after ten clock

cycles and ADPLL with edge triggered JK FF as PD model

locked after six clock cycles.

Fig.2 (b). ADPLL circuit diagram with JKFF PD

(ii) Edge triggered JK FF PD

Fig. 3 (a). Schematic representation of ADPLL with

EXOR gate as PD

It contains a JK FF with a clock input. JK FF is used as PD

because it is a sequentially based circuit.

B. Digital LF

K counter is used as digital LF in this ADPLL design. K

counter LF consists of two independent counters namely up

counter and down counter that counts always upward. The

content of both counters ranges from 0 to (K-1) where K is

controlled by K modulus control input and always power of

two [6]. When UP/DN signal is high, the down counter is

active and the contents of the up counter stay frozen.

Similarly, when UP/DN signal is low, the up counter is active

and the contents of the down counter stay frozen. The up and Fig. 3 (b). Schematic representation of ADPLL with

down counter produces carry and borrow output respectively JK FF as PD model

which are the MSB bits of the both counter. Both counter reset

to zero when the counter contents exceeds the maximum count

(K-1) [5, 6].

C. DCO

ID counter and divide by N counter is used as DCO in this

implementation. The ID counter consists of three inputs: a

clock input, increment and decrement. The carry of the K

counter LF is assigned to increment (INCR) input and borrow

is assigned to decrement (DECR) input. When carry pulse

appears at the INCR input then the next ID output pulse is

advanced in time by one ID clock period and when borrow

pulse appears at the DECR input then the next ID output pulse Fig. 4 (a). Simulation result for ADPLL with

is delayed in time by one ID clock period [5]. ID counter EXOR gate as PD model

output is fed to the divide by N counter.

Advanced Research in Electrical and Electronic Engineering

p-ISSN: 2349-5804; e-ISSN: 2349-5812 Volume 3, Issue 5, October-December, 2016

A Comparative Analysis on All Digital Phase Locked–Loops 361

4 Number 4 102 3% 5 232 2%

of bonded

IOBs

Table 3. Comparison of the ADPLL models with the

previous work

SL Parameters Proposed Proposed Previous Traditio

NO. model model work nal

with with JK ADPLL

EXOR FF PD

PD

Fig. 4 (b). Simulation result for ADPLL with JK FF as PD model 1 Power 0.015 0.021 0.485 [Ref 0.561

consumption 16]

7. RESULTS AND DISCUSSION (Watt)

2 IO 4/102 5/232 6/600 [Ref 4/480

The result obtained from the synthesis are given in Table 1 Utilization 16]

and Table 2 for ADPLL model with EXOR gate as PD and (bonded

model with edge triggered JK FF as PD. A comparison with IOB)

3 Number of 17/2,400 18/9112 135/297600 26/2880

obtained result and the previous work is given in Table 3.

Slice LUTs [Ref 16] 0

From the simulation results it is observed that JK FF ADPLL 4 Number of 22/4,800 23/18224 45/9,312 -

model has faster locking time than the EXOR PD model. The Slice flip [Ref 17]

total power consumption for ADPLL with EXOR gate PD flops

model is 15 mW. Dynamic as well as quiescent power 5 Number of 8/600 9/2,278 71/4,656 -

consumption is recorded as 1 mw and 14 mW for EXOR gate occupied [Ref 17]

PD model. The total power consumption for JK FF as PD Slices

model is 21 mW as Dynamic and quiescent power

consumption are recorded 1 mw and 20 mW respectively. 8. CONCLUSION

Table 1: Power consumption of ADPLL models From the present study model it can be concluded that the

locking speed of edge triggered JK FF ADPLL model is faster

SL Model Total Power Temp. Device than the ADPLL model with EXOR gate as PD. As such, edge

NO. /Parameters consumption (° C) Family triggered JK FF ADPLL can be used for high speed

(mW) communication with the expense of higher power

1 EXOR gate PD 15 25 Spartan6

consumption than ADPLL with EXOR gate as PD.

2 Edge triggered 21 25 Spartan6

JK FF PD

9. ACKNOWLEDGEMENT

Table 2: Synthesis details of ADPLL models The authors are thankful to the Head, Department of

Electronics & Communication Technology (ECT), Gauhati

SL Logic ADPLL Model with ADPLL Model with University, for necessary infrastructure facility and

NO Utilizatio EXOR as PD edge triggered JK FF

encouragement towards the present work. Also, authors would

. n as PD

Us Availab Logic Use Availab Logic

like to thank Mr. Manash Pratim Sarma, Assistant Professor,

ed le Utilizati d le Utilizat Department of Electronics & Communication Engineering,

on ion IST, Gauhati University, for his valuable suggestion during

1 Number 22 4,800 1% 23 18,244 1% the VHDL simulation.

of Slice

used as REFERENCES

Flip flops

2 Number 17 2,400 1% 18 9,112 1% [1] Gardner, F. M., “Phase Locked Loop Techniques,” 2nd ed., New

of Slice York; Wiley, 1979.

LUTs [2] Prasad, V. and Sharma, C., “A Review of Phase Locked Loop,”

3 Number 8 600 1% 9 2,278 1% International Journal of Emerging Technology and Advanced

of Engineering, vol 2, no.6, pp.98-104, June 2012.

occupied

Slices

Advanced Research in Electrical and Electronic Engineering

p-ISSN: 2349-5804; e-ISSN: 2349-5812 Volume 3, Issue 5, October-December, 2016

362 Munmee Borah and Tulshi Bezboruah

[3] Kalita, K., Maitra, A. and Bezboruah, T., “Modeling and [11] Shan, C. H., Chen, Z. and Jiang, J., “An All Digital Phase-

behavioral simulation of a wide band phase - locked loop for Locked Loop System with High Performance on Wideband

wireless communication receivers”, IJCTA, vol. 7, no.1, pp.27- Frequency Tracking”, Ninth International Conference on Hybrid

39, Jan-June 2014. Intelligent Systems, vol. 3, pp. 460 – 463, 2009.

[4] Lai, M. F. and Nakano, M., “Special Section on Phase-Locked [12] Shabaany, M. H. and Saneei, M., “A 0.7-to-1.1-GHz all-digital

LoopTechniques”, Guest Editorial, IEEE Transactions on phase-locked loop with a new phase frequency detector and

Industrial Electronics, vol.43, no.6, pp.607-608, December controlled oscillator with body biasing”, The 16th CSI

1996. International Symposium on Computer Architecture and Digital

[5] Best, R. E., “Phase locked Loops Design Simulation and Systems, pp. 54 – 59, 2012.

Applications”, McGraw – Hill Professional, ch. 6, pp. 205 – [13] Patil, A. and Saini, R., “Design and Implementation of FPGA

246, 5th edition, 2003. based linear all digital phase locked loop”, International

[6] Tripathi, N. and Pradhan, S. N., “Design of Power Efficient All Conference on Green Computing Communication and Electrical

Digital Phase Locked Loop (ADPLL)”, International conference Engineering (ICGCCEE), pp. 1 – 1, 2014.

on Wireless communications, Signal Processing and Networking [14] Kratyuk, V., Hanumolu P. K., Moon, U.K. and Mayaram K., “A

(IEEE), pp. 778 – 782, 2016. Design procedure for All – Digital Phase - Locked Loops Based

[7] Kim, N. G. and Ha, I. J., “Design of ADPLL for Both Large on a Charge Pump Phase- Locked – Loop analogy”, IEEE

Lock-In Range and Good Tracking Performance”, IEEE Transactions On Circuit And Systems – II: Express Briefs, vol.

Transactions on Circuits and Systems-II: Analog and Digital 54, no. 3, March 2007.

Signal Processing, vol. 46, no. 9, pp. 1192-1204, sept 1999. [15] Patel, P., Nemade, S. and Rathi, A., “A Non Linear Loop Filter

[8] Stefo, R., Schreiter, J., Schlussler, J. U. and Schuffny, R, “ High Approach for Fast Locking Digital PLL VHDL AMS

Resolution ADPLL frequency Synthesizer for FPGA - and ASIC Simulation”, International Journal of Engineering Innovation &

– based applications”, IEEE International Conference on Field- Research, vol. 1, no. 6, 2012.

Programmable Technology (FPT), pp. 28 – 34, 2003. [16] Rao, S., and Kumar K. V. G., “VHDL Implementation of

[9] Olsson, T. and Nilsson, P., “A Digitally Controlled PLL for optimized ADPLL and TMDS encoder for serial

Digital SOCs”, Circuits and systems, vol. 5, pp. V-437- V-440, communication”, International Journal of Engineering

2003. Innovation & Research in Technology, vol. 2, no. 1, 2015.

[10] Shan, C. H., Chen, Z. and Wang, Y., “An All Digital Phase [17] Vydehi, N. and Rao, A. S. S., “A Low Power VLSI Design of an

Locked loop based on Double Edge triggered Flip – flop”,8th All Digital Phase Locked Loop”, International Journal of

International conference on Solid-State and Integrated Circuit Engineering Trends & Technology, vol. 16, no. 6, Oct 2014.

Technology Proceedings, pp. 1990 – 1992, 2006.

Advanced Research in Electrical and Electronic Engineering

p-ISSN: 2349-5804; e-ISSN: 2349-5812 Volume 3, Issue 5, October-December, 2016

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Chap 06Document41 pagesChap 06Hidayah HadiNo ratings yet

- Differential Amplifiers Problems of MOS - 1Document5 pagesDifferential Amplifiers Problems of MOS - 1lokeshwarrvrjcNo ratings yet

- Icom IC-2200H Service ManualDocument54 pagesIcom IC-2200H Service ManualErick CoNo ratings yet

- Digital Signal Processing - An IntroductionDocument35 pagesDigital Signal Processing - An Introductionmeseret sisayNo ratings yet

- A 1-V 1-GSs 6-Bit Low-Power Flash ADC in 90nm CMOSDocument4 pagesA 1-V 1-GSs 6-Bit Low-Power Flash ADC in 90nm CMOSThanos van RamNo ratings yet

- Logic SynthesisDocument2 pagesLogic SynthesisSoumyarshi DasNo ratings yet

- Research Task GraphDocument1 pageResearch Task Graphapi-419834532No ratings yet

- For The Following Network and I8.: A. Find The Currents I2, I6, B. Find The Voltages V4 andDocument2 pagesFor The Following Network and I8.: A. Find The Currents I2, I6, B. Find The Voltages V4 andعبدالله عبدالحكيم عامرNo ratings yet

- Unisonic Technologies Co., LTD: High Performance Current Mode PWM ControllersDocument7 pagesUnisonic Technologies Co., LTD: High Performance Current Mode PWM ControllersCesra HMNo ratings yet

- Kec 302 Digital System DesignDocument2 pagesKec 302 Digital System DesignAditya KasaudhanNo ratings yet

- Engr228 Chapter 7, RL and RC Circuits' Transient ResponseDocument27 pagesEngr228 Chapter 7, RL and RC Circuits' Transient ResponsejoelduparNo ratings yet

- 3 Band Parameq Full V1.01Document4 pages3 Band Parameq Full V1.01crackintheshatNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument3 pages3 Hours / 70 Marks: Seat NoFack AccountNo ratings yet

- Deld - Online - MCQ - DELD Online Questions Unit IVDocument5 pagesDeld - Online - MCQ - DELD Online Questions Unit IVShanti GuruNo ratings yet

- ECEN689: Special Topics in High-Speed Links Circuits and Systems Spring 2010Document23 pagesECEN689: Special Topics in High-Speed Links Circuits and Systems Spring 2010Phoebe MensahNo ratings yet

- Perez Et Al - 2019 - Distributed Network of LDO Microregulators Providing Submicrosecond DVFS and IRDocument4 pagesPerez Et Al - 2019 - Distributed Network of LDO Microregulators Providing Submicrosecond DVFS and IR马晓飞No ratings yet

- Binary AdderDocument5 pagesBinary Adderstatusking8056No ratings yet

- Notes PDFDocument24 pagesNotes PDFkalyanNo ratings yet

- DEE6113 Course Outline Jun2016Document4 pagesDEE6113 Course Outline Jun2016FonzBahariNo ratings yet

- Colpitts Oscillator Circuit Design and Working PrincipleDocument3 pagesColpitts Oscillator Circuit Design and Working PrincipleVishal BasugadeNo ratings yet

- Switched Capacitor CircuitsDocument6 pagesSwitched Capacitor CircuitsEduardo ReynaNo ratings yet

- UM3481Document4 pagesUM3481mungos967No ratings yet

- RF Balun Transformers m565 PDFDocument4 pagesRF Balun Transformers m565 PDFtinears02No ratings yet

- AC Thevenin's Theorem LabDocument5 pagesAC Thevenin's Theorem Labyasir aliNo ratings yet

- The Design of A SRAM-Based Field-Programmable Gate Array-Part II: Circuit Design and LayoutDocument10 pagesThe Design of A SRAM-Based Field-Programmable Gate Array-Part II: Circuit Design and LayoutNiqabi NextdoorNo ratings yet

- 04 LCD Key IntrptDocument32 pages04 LCD Key IntrptahmetakdoganNo ratings yet

- NTE107 Silicon NPN Transistor UHF Oscillator For Tuner TO 92 Type PackageDocument2 pagesNTE107 Silicon NPN Transistor UHF Oscillator For Tuner TO 92 Type PackagekarlNo ratings yet

- 1 Transient ResponseDocument17 pages1 Transient ResponseJayvee ColiaoNo ratings yet

- VHDL Programs for Comparator, Decoder, Mux and ALUDocument6 pagesVHDL Programs for Comparator, Decoder, Mux and ALUVidhya DsNo ratings yet

- SWR Meters Make You StupidDocument38 pagesSWR Meters Make You StupidnosajseveerNo ratings yet