Professional Documents

Culture Documents

IT3L3 Digital System Design Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks Objectives

Uploaded by

Vyshnavi ThottempudiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IT3L3 Digital System Design Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks Objectives

Uploaded by

Vyshnavi ThottempudiCopyright:

Available Formats

PRASAD V.

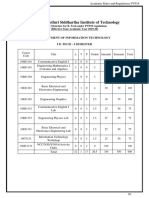

POTLURI SIDDHARTHA INSTITUTE OF TECHNOLOGY

2/4 B.Tech - FIRST SEMESTER

IT3L3 DIGITAL SYSTEM DESIGN LAB Credits: 2

Internal assessment: 25 marks

Lab: 3 Periods/week Semester end examination: 50 marks

Objectives:

To verify basic logic gates.

To verify half-adder and full-adder and its truth tables.

To implement and verify Encoder\Decoder and Multiplexer\De-Multiplexer using logic gates.

To verify state tables of RS, JK, T and D flip-flops using NAND & NOR gates.

To verify Basic Shift Registers.

Outcomes:

Students will be able to

Get practical knowledge on number systems.

Get familiar with half-adder and full-adder logic circuits.

Get familiar with Decoder, Encoder, Multiplexer and De-multiplexer circuits.

Get familiar with Flip-Flops and its circuitry.

Get familiar with basic shift registers and its circuitry.

Exercise 1

Boolean algebra: Theorems and logical guides, verification of truth tables

Exercise 2

Realization of Boolean expressions; Using (i) AND – OR-NOT Gates (ii) NAND Gates (iii) NOR

Gates

Exercise 3

Code Converters: Binary – to- Gray, Gray- to -Binary

Exercise 4

Simplification of Boolean Functions

Exercise 5

Adders / Sub tractors: Half Adder, Full Adder,

Exercise 6

Multiplexers/ Data Selector: 2- input and 8- input, De-multiplexers, Logic Function Generator

Exercise 7

Decoders and Encoders.

Exercise 8

Comparators

Exercise 9

Latches Flip – Flops: RS, JK, T, D Flip – Flops.

DEPARTMENT OF INFORMATION TECHNOLOGY

PRASAD V. POTLURI SIDDHARTHA INSTITUTE OF TECHNOLOGY

Exercise 10

Counters: Binary Counter, Ripple Counter, Up/Down Counter

Exercise 11

Registers: Basic Shift Register (SR), SI/SO SR, SI/PO SR, PI/SO SR, PI/PO SR.

Exercise 12

Parity Generators/Checkers.

Reference Book:

1. Digital Design by M. Morris Mano, Michael D.Ciletti Pearson 4th Edition.

DEPARTMENT OF INFORMATION TECHNOLOGY

You might also like

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationFrom EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo ratings yet

- EE204 Digital Electrncs N Logic DesignDocument3 pagesEE204 Digital Electrncs N Logic DesignsaniljayamohanNo ratings yet

- IT5L2 Microprocessors and Microcontrollers Lab Credits:2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 MarksDocument1 pageIT5L2 Microprocessors and Microcontrollers Lab Credits:2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 MarksVyshnavi ThottempudiNo ratings yet

- IT3T1Document2 pagesIT3T1Vyshnavi ThottempudiNo ratings yet

- Syllabus - DigitalElectronics and MicroprocessorDocument2 pagesSyllabus - DigitalElectronics and Microprocessorrockin_ravi_vitNo ratings yet

- Course File Final Heena A DigitalDocument23 pagesCourse File Final Heena A DigitalraghuippiliNo ratings yet

- Digital Electronics Circuits Course FileDocument23 pagesDigital Electronics Circuits Course FileraghuippiliNo ratings yet

- De Course File 2013-14Document75 pagesDe Course File 2013-14ragvshahNo ratings yet

- Bti 402 Digital ElectronicsDocument1 pageBti 402 Digital ElectronicsSanjay Kr SinghNo ratings yet

- Deca ChoDocument9 pagesDeca ChoTARANGITNo ratings yet

- Attachment Circular 2023081115025923 Ic 001Document9 pagesAttachment Circular 2023081115025923 Ic 001shivam.cs667No ratings yet

- Obe Curriculum For The Course: RGPV (Diploma Wing) BhopalDocument22 pagesObe Curriculum For The Course: RGPV (Diploma Wing) BhopalHarshit Sahu CS-26No ratings yet

- NU (DIGITTAL ELECTRONICS AND INSTRUMENTS) LatestDocument2 pagesNU (DIGITTAL ELECTRONICS AND INSTRUMENTS) Latestkhushalee.chavadaNo ratings yet

- Digital Electronics Laboratory Manual 17ECL38: Avalahalli, Doddaballapur Road Yelahanka, Bengaluru-560064Document51 pagesDigital Electronics Laboratory Manual 17ECL38: Avalahalli, Doddaballapur Road Yelahanka, Bengaluru-560064SANTOSH KUMAR SNo ratings yet

- Course Information Sheet: Syllabus: Unit Details HoursDocument47 pagesCourse Information Sheet: Syllabus: Unit Details HoursHarshith BejjamNo ratings yet

- Logic Gates ExercisesDocument6 pagesLogic Gates ExercisesSachidananda SwarNo ratings yet

- Birla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionDocument4 pagesBirla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionTrideeb BhattacharyaNo ratings yet

- M Tech DigitalSystemsComputerElectronicsDocument56 pagesM Tech DigitalSystemsComputerElectronicsShikhar AgarwalNo ratings yet

- DDE 1313 Digital Electronics 1 LODocument6 pagesDDE 1313 Digital Electronics 1 LOAhmad FadzlyNo ratings yet

- EE405 - Digital ElectronicsDocument3 pagesEE405 - Digital ElectronicsTakudzwa MNo ratings yet

- GTU Digital Electronics Course OverviewDocument3 pagesGTU Digital Electronics Course OverviewBhargavsinh ParmarNo ratings yet

- Demulti Plexer and MultiolexerDocument7 pagesDemulti Plexer and Multiolexerkaran007_mNo ratings yet

- 12-307 DatasheetDocument2 pages12-307 DatasheetLara WilliamsNo ratings yet

- Coa Lab Manual Aimt (Cse) PDFDocument24 pagesCoa Lab Manual Aimt (Cse) PDFRajesh kumarNo ratings yet

- B.tech Cse VTR Uge2021 de SyllabusDocument4 pagesB.tech Cse VTR Uge2021 de SyllabusBOLLIGARLA MOHAN SAI AKASH,CSE2021 Vel Tech, ChennaiNo ratings yet

- PDFDocument4 pagesPDFArpit PatelNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document4 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24f20220264No ratings yet

- DD HandoutDocument3 pagesDD HandoutAsdgjkNo ratings yet

- Gujarat Technological University: W.E.F. AY 2018-19Document4 pagesGujarat Technological University: W.E.F. AY 2018-19useless9925No ratings yet

- VLSI Lab ManualDocument117 pagesVLSI Lab ManualSusmitha BollimunthaNo ratings yet

- Gujarat Technological University: W.E.F. AY 2018-19Document3 pagesGujarat Technological University: W.E.F. AY 2018-19Alok MauryaNo ratings yet

- DSD Syll - Merged DSD GtuDocument8 pagesDSD Syll - Merged DSD GtuSandeep kumarNo ratings yet

- Digital Design Using HDL PDFDocument2 pagesDigital Design Using HDL PDFMarvin MayormenteNo ratings yet

- CS8382 DS Lab Manual Cse PDFDocument65 pagesCS8382 DS Lab Manual Cse PDFvlsiprabhu0% (1)

- Course Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentDocument6 pagesCourse Information Sheet: Sir Syed University of Engineering & Technology Electronic Engineering DepartmentAbdullah SohailNo ratings yet

- Digital Electronics Laboratory Manual (ECE 2002L) : For 4 Semester B.TechDocument62 pagesDigital Electronics Laboratory Manual (ECE 2002L) : For 4 Semester B.TechTushar PatelNo ratings yet

- CSE Modified PDFDocument40 pagesCSE Modified PDFbuddunaNo ratings yet

- Electronics 4Document4 pagesElectronics 4drkhamuruddeenNo ratings yet

- Dr. MPS Memorial College of Business Studies, Agra (Department of IT)Document528 pagesDr. MPS Memorial College of Business Studies, Agra (Department of IT)Anupma MalhotraNo ratings yet

- NUST Syllabus For DLDDocument2 pagesNUST Syllabus For DLDwistfulmemory100% (1)

- B.SC ITDocument34 pagesB.SC ITKhaled PatelNo ratings yet

- Open 16f8 ECDocument62 pagesOpen 16f8 ECRitik TiwariNo ratings yet

- HDL Manual 3 June 2022Document83 pagesHDL Manual 3 June 2022Ram Kumar SinghNo ratings yet

- BEEE206L - DIGITAL-ELECTRONICS - TH - 1.0 - 67 - Digital ElectronicsDocument3 pagesBEEE206L - DIGITAL-ELECTRONICS - TH - 1.0 - 67 - Digital ElectronicsNithish kumar RajendranNo ratings yet

- Ece103 Digital-logic-Design Eth 1.10 Ac29Document2 pagesEce103 Digital-logic-Design Eth 1.10 Ac29netgalaxy2010No ratings yet

- Digital Electronics Course HandoutDocument3 pagesDigital Electronics Course HandoutKanav Preet SinghNo ratings yet

- DSP Lab Manual - FinalDocument72 pagesDSP Lab Manual - FinalSwetNo ratings yet

- EE309 Microprocessors and Embedded SystemsDocument2 pagesEE309 Microprocessors and Embedded SystemsSarin C. R EeeNo ratings yet

- Amity, Digital Electronics-1 (B.tech Ece-4th Sem0Document1 pageAmity, Digital Electronics-1 (B.tech Ece-4th Sem0deepak173No ratings yet

- Laboratory Manual: ELE-203 Digital Logic DesignDocument73 pagesLaboratory Manual: ELE-203 Digital Logic DesignMoiz MazharNo ratings yet

- EEE241-DLD Course OutlineDocument2 pagesEEE241-DLD Course OutlineZeeshan TahirNo ratings yet

- Lecture Plan Digital ElectronicsDocument3 pagesLecture Plan Digital Electronicsprerak guptaNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document3 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Deepti MishraNo ratings yet

- 2131004Document3 pages2131004Parthiv Oza MasterMindNo ratings yet

- Revised Syllabus of B.C.A. (Science), With Credit Based System. W.e.f.: 2009-10Document32 pagesRevised Syllabus of B.C.A. (Science), With Credit Based System. W.e.f.: 2009-10Sudip BiswasNo ratings yet

- Gujarat Technological University: 1 of 3 W.E.F. AY 2018-19Document3 pagesGujarat Technological University: 1 of 3 W.E.F. AY 2018-19gecg ICNo ratings yet

- List of Lab and Its DetailsDocument16 pagesList of Lab and Its DetailsKnow HowNo ratings yet

- DLD Lab 1Document5 pagesDLD Lab 1Sardar SubhanNo ratings yet

- Getting Started with Tiva ARM Cortex M4 Microcontrollers: A Lab Manual for Tiva LaunchPad Evaluation KitFrom EverandGetting Started with Tiva ARM Cortex M4 Microcontrollers: A Lab Manual for Tiva LaunchPad Evaluation KitNo ratings yet

- Topic - Unit 5 - Team Problem Solving Activity - Unit 5 Group 3Document13 pagesTopic - Unit 5 - Team Problem Solving Activity - Unit 5 Group 3Vyshnavi ThottempudiNo ratings yet

- Mobility 3Document3 pagesMobility 3Vyshnavi ThottempudiNo ratings yet

- Biometrics SecurityDocument2 pagesBiometrics SecurityVyshnavi ThottempudiNo ratings yet

- IT6L5 Seminar Credits: 1 Lab: 2 Periods/week Internal Assessment: 50 MarksDocument1 pageIT6L5 Seminar Credits: 1 Lab: 2 Periods/week Internal Assessment: 50 MarksVyshnavi ThottempudiNo ratings yet

- Website Metrics Gap - Ford Beats NissanDocument7 pagesWebsite Metrics Gap - Ford Beats NissanVyshnavi ThottempudiNo ratings yet

- Computer Graphics Lab TechniquesDocument1 pageComputer Graphics Lab TechniquesVyshnavi ThottempudiNo ratings yet

- How To Make A Single CashNet PaymentDocument4 pagesHow To Make A Single CashNet PaymentVyshnavi ThottempudiNo ratings yet

- Newyork Crime Data AnalysisDocument15 pagesNewyork Crime Data AnalysisVyshnavi ThottempudiNo ratings yet

- Assignment1 622Document3 pagesAssignment1 622Vyshnavi ThottempudiNo ratings yet

- Newyork Crime Data Analysis-VyshnaviDocument12 pagesNewyork Crime Data Analysis-VyshnaviVyshnavi ThottempudiNo ratings yet

- IT7T1Document2 pagesIT7T1Vyshnavi ThottempudiNo ratings yet

- PVP19 Course StructureDocument6 pagesPVP19 Course StructureVyshnavi ThottempudiNo ratings yet

- IT6L2 DM Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks ObjectivesDocument1 pageIT6L2 DM Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks ObjectivesVyshnavi ThottempudiNo ratings yet

- Personality Development Course Lab SyllabusDocument2 pagesPersonality Development Course Lab SyllabusVyshnavi ThottempudiNo ratings yet

- IT6T3Document2 pagesIT6T3Vyshnavi ThottempudiNo ratings yet

- IT6T4Document2 pagesIT6T4Vyshnavi ThottempudiNo ratings yet

- IT6T2Document2 pagesIT6T2Vyshnavi ThottempudiNo ratings yet

- IT6L1 Ooad Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 MarksDocument1 pageIT6L1 Ooad Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 MarksVyshnavi ThottempudiNo ratings yet

- IT6T1Document2 pagesIT6T1Vyshnavi ThottempudiNo ratings yet

- IT5L4Document1 pageIT5L4Vyshnavi ThottempudiNo ratings yet

- IT5T5Document2 pagesIT5T5Vyshnavi ThottempudiNo ratings yet

- IT5L3 Web Technologies Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 MarksDocument6 pagesIT5L3 Web Technologies Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 MarksVyshnavi ThottempudiNo ratings yet

- It5t3 PDFDocument2 pagesIt5t3 PDFVyshnavi ThottempudiNo ratings yet

- IT5T5Document2 pagesIT5T5Vyshnavi ThottempudiNo ratings yet

- It5t2 PDFDocument2 pagesIt5t2 PDFVyshnavi ThottempudiNo ratings yet

- IT5L1 Unix Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks ObjectivesDocument3 pagesIT5L1 Unix Lab Credits: 2 Internal Assessment: 25 Marks Lab: 3 Periods/week Semester End Examination: 50 Marks ObjectivesVyshnavi ThottempudiNo ratings yet

- ItDocument2 pagesItVyshnavi Thottempudi100% (1)

- ItDocument2 pagesItVyshnavi ThottempudiNo ratings yet

- It5t2 PDFDocument2 pagesIt5t2 PDFVyshnavi ThottempudiNo ratings yet