Professional Documents

Culture Documents

Reset signals and clock oscillators on a laptop motherboard

Uploaded by

Delwar Hossain0 ratings0% found this document useful (0 votes)

440 views2 pagesOriginal Title

FIRST_RESET_SIGNAL_ON_LAPTOP_MOTHERBOARD.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

440 views2 pagesReset signals and clock oscillators on a laptop motherboard

Uploaded by

Delwar HossainCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 2

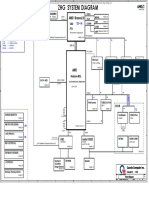

FIRST RESET SIGNAL ON LAPTOP MOTHERBOARD

By Adie Dkhaz on Sunday, March 8, 2015 at 8:00pm

RSMRST#

When the Power,Bios,Ec are OK, the RSMRST# will go Hi. In the other word,this pin go Low

only when the systemreset.If BIOSdata is error,RSMRST# won’t go HI.

When SIO(EC) get +V_RTC

thecrystal will work.

1. RTC have to be oscillating(32.768KHz).

2. RTCRST# have to be high.

3. RSMRST# have to be inactive (high).

4. PWRBTN# have a trigger.

5. LOW_BAT# have to be inactive (high).

If true, thenEC will recieve SLP_S3# / SLP_S5 from ICH/PCH, in the old ICH or some deferent

circuirity SLP_S3 and SLP_S5 will generate directly from ICH,or both EC and PCH having

this signal also.

When All+V?S/+V? powers are ready, PWR_GOOD will tie to high to turn on CPU

powers(+VCCP and +VCC_CORE).

SB/PCH Power good--->SB/PCH pwr_btn--->PCH RUN

SUSB## from PCH toSIO pullup the signal SLP_S3# The signal is usedto shut power off /on

through logic gate transistor or IC

SUSC# from PCH toSIO pullup the signal SLP_S5# The signal is usedto shut power off /on

through logic gate transistor or IC

ICH/SB,MCH & CPU

IMVP_PWRGD => CLK_ENABLE# => RESET_OUT#=> ICH_PWRGD => PLTRST# =>

PCI_RST=> H_PWRGOOD

CPU generate the first cycle to read the BIOS code

CPU bus DMI LPC SPI

CPU ===> GMCH===> ICH===>SIO ===> BIOS

CPU MASTER POWER

VR_ON Enable--->+VCCORE 08VS to 1,5VS

Memory +VTT and +V1.5VS (DDR3) is ok, the PGOOD VTT_PWRGD pull high to CPU

First nd ICH will tie H_PWRGD to high ,then NB will tieCPURST# to reset CPU.

Crystal clock Oscilator CLOCK SUMMARY

(1) 32.768KHz to SIO Required +V_RTC and to ICH(chipset) also Required +V_RTC

(2) 49.152MHz to (audio controller) Required +V3S

(3) 27MHz : to Graphicchip (video controller)Required +V3S

(4) 14.318MHz : X1 to (clock Generator) Required +V3S

Make sure crystal is oscillating for EC(SIO),SB/ICH/PCH and VGA or it will no post

Clock Generator

Elementary required

1) Power : +V3S

(2) Crystal : 14.318MHz

(3) Control : PCISTOP# , CPUSTOP#_ is HI

When +VCC_CORE is ready, CLKEN#will go high to enable clock-Generator and turn all

clock.

PCI_STOP# and CPU_STOP# must beat high otherwise some clocks will be turned off.

Clock out -->SIO(EC)-->PCH/SB-->NB-->CPU

LPC_Frame-->SB output signal is high

Note High signal can be identified by measuring 3.3V available

copyrigh_adiedkhaz

You might also like

- Laptop Power SequenceDocument16 pagesLaptop Power SequenceDelwar Hossain90% (10)

- Preview-Laptop Chip Level Repair Guide PDFDocument34 pagesPreview-Laptop Chip Level Repair Guide PDFIbrahim Alsaidi67% (12)

- Laptop Training Shri Ram SyllbusDocument4 pagesLaptop Training Shri Ram SyllbusAnthony Lobo100% (2)

- English Menu (Laptop Repair Books)Document12 pagesEnglish Menu (Laptop Repair Books)Paulo Mariano100% (1)

- Laptop Signal SequencesDocument52 pagesLaptop Signal SequencesMohammad Azwan86% (7)

- Advance Laptop Chip Level Repair Engineering Training CourseDocument15 pagesAdvance Laptop Chip Level Repair Engineering Training CourseSanjeewa Silva50% (4)

- Inventec A10 PCB design and specificationsDocument72 pagesInventec A10 PCB design and specificationsDelwar HossainNo ratings yet

- Desktop Power SequenceDocument1 pageDesktop Power SequenceBivek Basnet100% (4)

- Laptop Power Sequence Training 100pdf PDFDocument52 pagesLaptop Power Sequence Training 100pdf PDFPc Laptop Care Mukesh67% (3)

- Laptop Power SequencingDocument14 pagesLaptop Power SequencingOlivier Ouina100% (2)

- Chip Level Motherboard Repair Guide PDFDocument5 pagesChip Level Motherboard Repair Guide PDFKalyan DhupatiNo ratings yet

- Laptop Motherboard Repair DetailsDocument7 pagesLaptop Motherboard Repair Detailssshku7750% (2)

- BOOK Laptop Motherboard Fault FinderDocument85 pagesBOOK Laptop Motherboard Fault FinderServis Accu80% (5)

- Desktop - Power Sequence PDFDocument8 pagesDesktop - Power Sequence PDFআশিক সরকার100% (1)

- Laptop Power SquenceDocument52 pagesLaptop Power Squencedjonsen100% (2)

- Motherboard Power On SequenceDocument17 pagesMotherboard Power On SequenceSreeraj Sekharan80% (25)

- Power On Detail Step With TimingDocument15 pagesPower On Detail Step With Timingz4rm4r100% (4)

- Basic IO/KBC/EC requirements and triggering process in laptopsDocument4 pagesBasic IO/KBC/EC requirements and triggering process in laptopsMohamed B Ali100% (2)

- Laptop Chip Level Repairing Course SyllabusDocument4 pagesLaptop Chip Level Repairing Course SyllabusLciit LaptopCareNo ratings yet

- T - Con Module Fault - Google SearchDocument2 pagesT - Con Module Fault - Google SearchRaja Pathamuthu.G100% (1)

- 5th Gen Power SeqDocument1 page5th Gen Power SeqBivek Basnet0% (1)

- Laptop Voltage Requirement and Power Supply DiagramDocument5 pagesLaptop Voltage Requirement and Power Supply Diagrambong bernalbongNo ratings yet

- Acer Aspire V5-121 - Da0zhgmb6d0 Rev DDocument28 pagesAcer Aspire V5-121 - Da0zhgmb6d0 Rev Ddigantamilon75% (4)

- First Reset Signal On Laptop MotherboardDocument2 pagesFirst Reset Signal On Laptop Motherboardangelito alarasNo ratings yet

- Motherboard Repair InformationDocument33 pagesMotherboard Repair Informationabhilashvaman5542100% (1)

- Components Code and Abbreviation On Laptop MotherbDocument7 pagesComponents Code and Abbreviation On Laptop MotherbDelwar HossainNo ratings yet

- Power On SequenceDocument3 pagesPower On SequenceNsb El-kathiri100% (2)

- Wistron Power ON - SequenceDocument1 pageWistron Power ON - SequenceCarlos Gomes100% (1)

- LAPTOP POWER SequenceDocument1 pageLAPTOP POWER SequenceIshwer Rao100% (1)

- How To Check 3v1Document12 pagesHow To Check 3v1jonas consina100% (2)

- Laptop Power Sequence - Shriram InfotechDocument52 pagesLaptop Power Sequence - Shriram InfotechRod Palma100% (1)

- Check the 3V and 5V Power System on a Laptop Motherboard Using the RT8206B ICDocument2 pagesCheck the 3V and 5V Power System on a Laptop Motherboard Using the RT8206B ICLeth ComputerRepair67% (3)

- Laptop Power Sequence ExplainedDocument3 pagesLaptop Power Sequence ExplainedYenco Barliza Diaz100% (4)

- Laptop Power SequenceDocument2 pagesLaptop Power SequenceGabriel Meneses100% (1)

- Laptop Troubleshoot Service LogDocument27 pagesLaptop Troubleshoot Service Logangelito alaras100% (1)

- How To Clear Me PDFDocument7 pagesHow To Clear Me PDFChandrasekharan NairNo ratings yet

- Laptop Power2Document52 pagesLaptop Power2Nsb El-kathiri100% (12)

- Free Lapto Mother Board Fault FinderDocument112 pagesFree Lapto Mother Board Fault FinderAdjarko PhilipNo ratings yet

- Dead Phone Testing1Document12 pagesDead Phone Testing1HEM SHRESTHANo ratings yet

- System Power Laptop MotherboardDocument5 pagesSystem Power Laptop MotherboardLeth ComputerRepairNo ratings yet

- All Rights ReservedDocument22 pagesAll Rights ReservedLisandro Martinez DominguezNo ratings yet

- Desktop Power Sequence 4 PDF FreeDocument8 pagesDesktop Power Sequence 4 PDF FreeAhmad Syafii LeongNo ratings yet

- Component Level Motherboard Repair EDITEDDocument17 pagesComponent Level Motherboard Repair EDITEDB Sukma SyarifudinNo ratings yet

- DESKTOP CHIP NOTES Modify 0511 PDFDocument65 pagesDESKTOP CHIP NOTES Modify 0511 PDFNsb El-kathiriNo ratings yet

- 1 Month Laptop Repairing CourseDocument10 pages1 Month Laptop Repairing CourseChiptroniksInst0% (1)

- Course Structure of Laptop Chip Level TrainingDocument10 pagesCourse Structure of Laptop Chip Level TrainingBivek BasnetNo ratings yet

- v2000 Power On Sequence Step Wise Final NotesDocument10 pagesv2000 Power On Sequence Step Wise Final NotesEduardo AramburuNo ratings yet

- Motherboard RepairDocument22 pagesMotherboard Repairz4rm4rNo ratings yet

- HOW TO CHECK 3V AND 5V POWER SYSTEMS ON A LAPTOP MOTHERBOARDDocument7 pagesHOW TO CHECK 3V AND 5V POWER SYSTEMS ON A LAPTOP MOTHERBOARDأحمد الأمينNo ratings yet

- 40 Pin Led Screen Panel Datasheet PDFDocument30 pages40 Pin Led Screen Panel Datasheet PDFDelwar Hossain100% (3)

- Motherboard Repairing MethodDocument18 pagesMotherboard Repairing MethodRamdas KambleNo ratings yet

- Laptop Repair Guide - Basic Troubleshooting StepsDocument111 pagesLaptop Repair Guide - Basic Troubleshooting StepsJan Alam100% (21)

- First Reset Signal On Computer CircuitDocument2 pagesFirst Reset Signal On Computer CircuitLeth ComputerRepairNo ratings yet

- Reset SignalDocument1 pageReset SignalSomendra SinghNo ratings yet

- General Laptop Power Supply Diagram (VALW Section of ADP+,+3V,+5V)Document3 pagesGeneral Laptop Power Supply Diagram (VALW Section of ADP+,+3V,+5V)Leth ComputerRepair100% (2)

- Learn about the Intel laptop boot process and chipset signalsDocument3 pagesLearn about the Intel laptop boot process and chipset signalsmadumadawa rajapakshaNo ratings yet

- Motherboard Power Timing Knowledge AnalysisDocument5 pagesMotherboard Power Timing Knowledge Analysisabhilashvaman5542No ratings yet

- Synchronize Communication Interface: 清华 Freescale MCU/DSP 应用开发研究中心Document35 pagesSynchronize Communication Interface: 清华 Freescale MCU/DSP 应用开发研究中心mataleao.zNo ratings yet

- Using Serial Peripheral InterfaceDocument21 pagesUsing Serial Peripheral InterfaceArton TonoNo ratings yet

- Energy Check 3000 - 93lc46Document10 pagesEnergy Check 3000 - 93lc46Zoltán SzikszaiNo ratings yet

- 340S8 Service ManualDocument83 pages340S8 Service ManualPeter MugohNo ratings yet

- Arduino Based Digital Clock With AlarmDocument17 pagesArduino Based Digital Clock With AlarmAsdfghjklNo ratings yet

- Pic18 Hardware InterfacingDocument9 pagesPic18 Hardware Interfacingadamwaiz100% (2)

- Pertemuan 7 Organisasi Input / OutputDocument29 pagesPertemuan 7 Organisasi Input / OutputYason Timothy HamdaniNo ratings yet

- File list for embedded system hardware diagramsDocument54 pagesFile list for embedded system hardware diagramscahemlNo ratings yet

- Dell XPS 17 Schematics VersionDocument55 pagesDell XPS 17 Schematics VersionDevender kumarNo ratings yet

- 1 4916103022511128890Document20 pages1 4916103022511128890Delwar HossainNo ratings yet

- HCC eMMC Management Driver User Guide v1 - 10Document28 pagesHCC eMMC Management Driver User Guide v1 - 10Delwar HossainNo ratings yet

- Lvds Circuit Testing On DsoDocument1 pageLvds Circuit Testing On DsoDelwar HossainNo ratings yet

- Sky13491-31: 0.7 To 2.7 GHZ Sp14T Mipi Antenna Switch: Data SheetDocument23 pagesSky13491-31: 0.7 To 2.7 GHZ Sp14T Mipi Antenna Switch: Data SheetDelwar HossainNo ratings yet

- CPU Stability Test: Rev.011: ProcedureDocument10 pagesCPU Stability Test: Rev.011: ProcedureDelwar HossainNo ratings yet

- Up 7704Document13 pagesUp 7704Delwar HossainNo ratings yet

- EmmcflashDocument32 pagesEmmcflashDelwar HossainNo ratings yet

- Improving Android Bootup Time: Tim Bird Sony Network Entertainment, IncDocument40 pagesImproving Android Bootup Time: Tim Bird Sony Network Entertainment, IncDelwar Hossain100% (1)

- 823c2 Compal LA-7912PDocument63 pages823c2 Compal LA-7912Pwotanel100% (1)

- Asus P8Z77-V LX Component TrainingDocument48 pagesAsus P8Z77-V LX Component TrainingDelwar Hossain100% (1)

- HDDS Hard Drive Repair WorkbenchDocument5 pagesHDDS Hard Drive Repair WorkbenchDelwar HossainNo ratings yet

- Dell Inspiron 3542 7 Beep Sound Solutions - IndiarefixDocument3 pagesDell Inspiron 3542 7 Beep Sound Solutions - IndiarefixDelwar HossainNo ratings yet

- 40 Pin Led Screen Panel Datasheet PDFDocument30 pages40 Pin Led Screen Panel Datasheet PDFDelwar Hossain100% (3)

- Gateway - Arima W350DI PDFDocument44 pagesGateway - Arima W350DI PDFJose BenavidesNo ratings yet

- Compal Confidential: P1VE6 LA7071P Schematics DocumentDocument37 pagesCompal Confidential: P1VE6 LA7071P Schematics DocumentChristiam OrtegaNo ratings yet

- 6th Gen Core PCH U y Io Datasheet Vol 1Document278 pages6th Gen Core PCH U y Io Datasheet Vol 1Dion OntosenoNo ratings yet

- Ecs H 61 H 2 M 12 Rev 1 0 452539720 PDFDocument29 pagesEcs H 61 H 2 M 12 Rev 1 0 452539720 PDFFlavianoSilva100% (1)

- General Power and Swicthing System On Laptop Motherboard PDFDocument6 pagesGeneral Power and Swicthing System On Laptop Motherboard PDFDelwar Hossain100% (1)

- PCI Schematic Block DiagramDocument51 pagesPCI Schematic Block DiagramDelwar Hossain100% (1)

- Ecs H 61 H 2 M 12 Rev 1 0 452539720 PDFDocument29 pagesEcs H 61 H 2 M 12 Rev 1 0 452539720 PDFFlavianoSilva100% (1)

- Analyses Procedure No Post Problem On Laptop Motherboard Circuit PDFDocument3 pagesAnalyses Procedure No Post Problem On Laptop Motherboard Circuit PDFDelwar HossainNo ratings yet