Professional Documents

Culture Documents

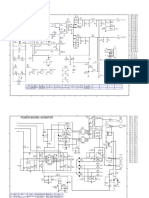

Y511电路图

Uploaded by

nomomk hiomioCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Y511电路图

Uploaded by

nomomk hiomioCopyright:

Available Formats

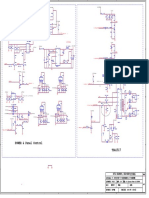

cap Close to BB IC

100nF

C108

U101-H

cap Close to BB IC

VIO18_PMU VIO18_PMU T25 DVDD18_MIPIRX AVDD28_DAC F1 VTCXO_PMU VTCXO_PMU

U25 DVSS18_MIPIRX

AVDD18_AP E5

R25 DVDD18_MIPITX DVDD18_PLLGP U9 VIO18_PMU VIO18_PMU

P25 DVSS18_MIPITX

AVDD18_MD D3 VIO18_PMU

VIO18_PMU VIO18_PMU H23 AVDD18_USB AVSS18_MD A1

VUSB_PMU VUSB_PMU G24 AVDD33_USB AVSS18_MD A4

0.1uF

100nF

C128

G23 C3

100nF

AVSS33_USB AVSS18_MD

C112

AVSS18_MD E2

C122

C113

100nF

1uF

C104

100nF

100nF

C101

C107

REFP F6 BG

REFP

C109

G6

1uF

REFN

BGA428-10.7X10.7-0.4E0.25B(MT6572)

dedicate VSS ball, must return to cap then to main GND:

1. REFN(G6) => C109

2. DVSS18_MIPIRX(U25) => C107

3. DVSS18_MIPITX(P25) => C101

VIO_EMI

U101-B

W9

1.8V IO for DDR1

VCC VCCIO_EMI

VCCIO_EMI W12 1.2V IO for DDR2

Memory W14

VCCIO_EMI

AC21 W16

100nF

100nF

GND VCCIO_EMI

C405

C406

AD11 GND VCCIO_EMI W19

AF13 GND If double-sided SMT, put C405 & C406 below BB.

100nF

C124

AB11 GND

AC8 If single-sided SMT, put C405 & C406 around memory.

GND DVDD

AB5 GND

AB14 Peripheral

GND

W26 GND DVDD18_MC0 AA1 VIO18_PMU VIO18_PMU

T15 GND DVDD18_CAM K20 VIO18_PMU

W23 GND DVDD18_VIO_1 L3 VIO18_PMU

T14 GND DVDD18_VIO_2 J19 VIO18_PMU

AF26 GND DVDD18_VIO_3 H13 VIO18_PMU 0

G3 GND DVDD18_LCD AB24 DVDD18_LCD

K21 GND

L11 R119

GND

L12 GND

L14 GND DVDD3_MC1 K24 VMC_PMU VMC_PMU

C126

1uF

L15 GND

L16 GND DVDD3_LCD W24 DVDD18_LCD

M5 GND

M11 GND DVDD28_BPI C10 VIO28_PMU VIO28_PMU

M12

C117

1uF

GND

1uF_NF

C121

M13 GND

M14 GND VCC

M15 GND

M16 CPU P6

GND VCCK_CPU

N10 GND VCCK_CPU T7

N8 GND VCCK_CPU P7

N9 GND VCCK_CPU P8 Close to BB IC, recommand < 150mil

N11 GND VCCK_CPU P9

N12 GND VCCK_CPU R6

N13 GND VCCK_CPU R7

N14 GND VCCK_CPU R8

N15 GND VCCK_CPU R9

N16 GND VCCK_CPU T6 Based on your system level

P10 GND VCCK_CPU U6 design , if better FM performance

N22 GND VCCK_CPU T9

P11 GND VCCK_CPU T8 is needed on your system ,

P12 GND VCCK_CPU U7

P13 GND

please refer to FM desense

P14 GND performance enhance proposal

P15

P16

GND

GND

120mil VPROC_PMU

VCC VPROC_PMU [1,3][3]

R10 GND

R11 Core J9

GND VCCK

R12 GND VCCK J15

R13 GND VCCK M9

R14 GND VCCK K6

R15 GND VCCK K7

100nF

100nF

100nF

100nF

R16 K8

10uF

2.2uF

2.2uF

C111

10uF

10uF

GND VCCK

1uF

1uF

1uF

1uF

T10 GND VCCK K9

T11 GND VCCK K11

T12 GND VCCK K14

4.7uF

C103

C106

C102

T13 K15

C114

C135

C137

C118

C116

C120

C134

C119

C136

GND VCCK

C115

AF1 VSS VCCK M10

VCCK K16

U10 VSS VCCK K17

U11 VSS VCCK U17

V13 VSS VCCK M17

W11 VSS VCCK L7 Vproc remote sense :

Y21 VSS VCCK L8

L9 HT1 differential 4mil with good shielding, from the BB to PMIC

VCCK

VCCK L17 GND_VPROC_FB [3] [3]

M6 GND

VCCK 4mil - defferential - GND shielding HT2

VCCK M7

M8 VPROC_FB [3] [3]

VCCK

VCCK J17

VCCK J16

VCCK R17

VCCK T16

VCCK L6

VCCK K12

VCCK T17

VCCK J10

VCCK J11

VCCK U12

VCCK U13

VCCK U14

VCCK U15

VCCK U16

VCCK J8

VCCK J14

A26 DUMMY

BGA428-10.7X10.7-0.4E0.25B(MT6572)

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 01_MT6572_POWER SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 1 OF 15

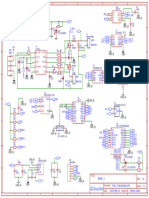

U101-A

U101-D

[6] RX_I_P [6] D2 DL_I_P BPI_BUS0 B12 BPI_0 [6,7]

[6]

[6] RX_I_N [6] C2 DL_I_N BPI_BUS1 B11 BPI_1 [6,7]

[6]

[6] RX_Q_P [6] B1 DL_Q_P BPI_BUS2 C12 BPI_2 [6,7]

[6] [3] AUD_MISO [3] J1 AUD_DAT_MISO

[6] RX_Q_N [6] C1 DL_Q_N BPI_BUS3 A11 BPI_3 [6,7]

[6] [3] AUD_CLK [3] K5 AUD_CLK_MOSI

[3] AUD_MOSI [3] K1 AUD_DAT_MOSI

BPI_BUS4 D11

[6] TX_I_P [6] A2 UL_I_P BPI_BUS5 C11 EINT_HP [5] [5] [3] PMIC_SPI_MOSI [3] L2 PMIC_SPI_MOSI

[6] TX_I_N [6] B2 UL_I_N BPI_BUS6 A13 GPIO_GPS_LNA_EN[11] [3] PMIC_SPI_MISO [3] L5 PMIC_SPI_MISO

[6] TX_Q_P [6] B4 UL_Q_P [3] PMIC_SPI_SCK [3] L4 PMIC_SPI_SCK

[6] TX_Q_N [6] B3 UL_Q_N BPI_BUS7 A10 W_PA_B1_EN [7] [3,4]PMIC_SPI_CS [3] K2 PMIC_SPI_CSN

BPI_BUS8 B10

D10 W_PA_B2_EN [7] [3] WATCHDOG [3,4] G2

BPI_BUS9 WATCHDOG

BPI_BUS10 E9 W_PA_B8_EN[7] [3,6]SRCLKENA [3,6] H4 SRCLKENA

BPI_BUS11 E8 [3] EINT_PMIC [3] J2 EINTX

BPI_BUS12 B9 EINT_MAG [80]

A8 VM0 BPI_BUS13 B8 EINT_ALPXS [15][21]

[7] VM0

A7 VM1 BPI_BUS14 E7 EINT_ACC [15][21] [3] SIM1_SCLK [2,3] H5 SIM1_SCLK

[7] VM1 D7 M3

BPI_BUS15 EINT8_ACC1[15] [3] SIM1_SIO [3] SIM1_SIO

reserve for JTAG debug

[6] TXBPI [6] D5 TXBPI BSI_DATA2 D6 BSI-A_DAT2 [6] [6]

BSI_DATA1 C7 BSI-A_DAT1 [6] [6] [3] SIM2_SCLK [3] J5 SIM2_SCLK

[6] VAPC1[7] F2 APC BSI_DATA0 F9 BSI-A_DAT0 [6] [6] [3] SIM2_SIO [3] M1 SIM2_SIO

BSI_EN F11 BSI-A_EN [6] [6]

F3 VBIAS BSI_CLK G11 BSI-A_CK [6] [6] VIO18_PMU

R210

SIM1_SCLK [2,3]

20K_NF

BGA428-10.7X10.7-0.4E0.25B(MT6572)

Normal : NC

BGA428-10.7X10.7-0.4E0.25B(MT6572)

JTAG : 20K

Reserve R footprint

for JTAG debugging

Based on your system level design , if better

desense performance is needed on your

system , please refer to desense

performance enhance proposal

U101-G

MIPI_2nd_CAM

[13] GPIO_CMPDN2 [10] L25 CMPDN2 U101-E

[13] GPIO_CMRST2 [10] K25 Parallel 8-bit

CMRST2

[13] GPIO_CMPDN [10] H22 CMPDN

[13] GPIO_CMRST [10] J22 CMRST

CMMCLK Y22 CMMCLK [10][13]

[13] MIPI_RDN0 [10] R24 RDN0

R23 MIPI_CAM Y23 [6] CLK1_BB [6] E1 CLK26M PWM_A D12 GPIO_FLASH_EN [80]

[13] MIPI_RDP0 [10] RDP0 CMPCLK CMPCLK [10][13] SYSTEM PWM E12

R22 PWM_B EINT_CTP [9] [12]

[13] MIPI_RDN1 [10] RDN1 H2

100-ohm differential [13] MIPI_RDP1 [10] R21 RDP1 RCN_A V25 CMVSYNC [10][13]

[3] CLK32K_BB [3] CLK32K_IN

[13] MIPI_RCN [10] R26 RCN RCP_A W25 CMHSYNC [10][13] LCD

T26 V24 [3] RESETB [3] M2 SYSRSTB LPD17 N1

[13] MIPI_RCP [10] RCP RDN1_A CMDAT7 [10]

[13] Parallel N2

RDP1_A V23 CMDAT6 [10]

[13] LPD16 LCD_BL_CTL[9]

P19 U22 G4 TESTMODE LPD15 N3

[12] MIPI_TDN0 [9] TDN0 RDN0_A CMDAT5 [10]

[13]

P20 MIPI_LCD U21 LPD14 P2

[12] MIPI_TDP0 [9] TDP0 RDP0_A CMDAT4 [10]

[13]

N25 AC24 FSOURCE LPD13 N4 EINT_CMMB [80]

100-ohm differential [12] MIPI_TDN1 [9] TDN1

N26 Y26 LPD12 R2

[12] MIPI_TDP1 [9] TDP1 CMDAT3 CMDAT3 [10]

[13]

P23 Y25 LPD11 N5

MIPI_TDN2 TDN2 CMDAT2 CMDAT2 [10]

[13] J26 R1

P24 AA25 [3] CHD_DP [3] CHD_DP LPD10 MC1_INS [13][18]

MIPI_TDP2 TDP2 CMDAT1 CMDAT1 [10]

[13] J25 BC 1.1 P5

[12] MIPI_TCN [9] N20 AB25 [3] CHD_DM [3] CHD_DM LPD9

TCN CMDAT0 CMDAT0 [10]

[13] T1

[12] MIPI_TCP [9] N19 TCP LPD8

LPD7 R5

[14] USB_DM [8] 90-ohm differential G26 USB_DM LPD6 T2

[14] USB_DP [8] R203 G25 USB 2.0 T5

R202 USB_DP LPD5

MIPI_VRT P26 USB_VRT H25 USB_VRT LPD4 U2

VRT T3

5.1K LPD3

1.5k LPD2 U5

[13] SCL_0[2,10] C25 i2C T4

SCL_0 LPD1

close to BB close to BB [13] SDA_0[2,10]

[12,21]SCL_1[2,9,15]

C26

B24

SDA_0

SCL_1

LPD0 V2

[12,21]SDA_1[2,9,15] B23 SDA_1

BGA428-10.7X10.7-0.4E0.25B(MT6572)

LPCE0B AD25 EINT_GY [80]

[80] SPI_MISO F24 SPI_MISO LPTE AB26 LPTE [9][12]

[80] SPI_MOSI F25 SPI AC26 GPIO_LRSTB [9] [12]

SPI_MOSI LRSTB

[80] SPI_SCK F23 SPI_SCK LPRDB AA22 GPIO_FLASH_SEL [80]

[80] SPI_CSB E23 SPI_CS LPA0 AB23 GPIO_TV_RST [80]

LPWRB AC25 GPIO_CTP_RSTB [9] [12]

MT6572 support JTAG from below :

[18] MC1CMD [13] K23 MC1_CMD T-flash KP KROW0 B25 KROW0 [14][20] KROW2 1. KP (recommand)

[18] MC1CK [13] L21 MC1_CK KROW1 A24 KROW1 [20]

[18] MC1DAT0 [13] K22 MC1_DAT0 KROW2 B26 2. MC1 KROW2

[18] MC1DAT1 [13] M22 MC1_DAT1 KCOL0 C24 KCOL0 [8,14]

[20] KCOL2 TP205

[18] MC1DAT2 [13] M25 MC1_DAT2 KCOL1 D24 KCOL1 [14] 3. CAM

[18] MC1DAT3 [13] L26 MC1_DAT3 KCOL2 A25

for JTAG pin out from MC1/CAM, refer

KCOL2

LCD_ID_ADC [9] B7 AUX_IN0 ADC UART UTXD1 E25 UTXD1 to HW design notice TP206

B6 AUX_IN1 URXD1 D25 TP201

[3] BAT_ID_ADC TP202

C5 AUX_IN2_XP UTXD2 E26 URXD1

B5 AUX_IN3_YP URXD2 F26

C4 AUX_IN4_XM

A5 AUX_IN5_YM

BGA428-10.7X10.7-0.4E0.25B(MT6572)

VCAMD_IO_PMU

2.2K

2.2K

R204

R205

[13] Power by CAM_IO

[13] SCL_0[2,10]

SDA_0[2,10]

VIO18_PMU

2.2K

2.2K

R207

R206

[12,21]

[12,21] Power by CTP, MEMS sensor

SCL_1[2,9,15]

SDA_1[2,9,15]

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 02_MT6572_BASEBAND SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 2 OF 15

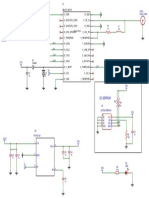

Before you select BJT , please take power dissipation into consideration.

Refer to MT6323 design notice

Charger

VBUS

U301

1. Close to Battery Connector.

(Rsense (R328) <10mm) BGA145-5.8X5.8-0.4E0.25B(MT6323)

R329

2. Main path should be 40mil. VCDT [3]

SPK_P K1 AU_SPKP [8] [5]

(VBUS -> U303's E, -> U303's C -> R328 -> VBAT) 330K VCDT rating: 1.268V SPK_N L1 AU_SPKN [8] [5]

R324 VBAT C313 P1

3. Star connection from R328 to BAT Connector VBAT VBAT_SPK

C329

1uF

cap rating depends on 39K L2 GND_SPK AU_HSP H1 AU_HSP [5] [5]

2.2uF AU_HSN G1 AU_HSN [5] [5]

Phone OVP spec.

40mils AU_HPL H4 AU_HPL [5] [5]

MICBIAS0 F2 AU_MICBIAS0 AU_HPR J4 AU_HPR [5] [5]

MICBIAS1 G2 AU_MICBIAS1

R331

C312

1uF

CHR_LDO [3] [5] AU_VIN0_P [5] E4 E9 ISINK0 [12]

AU_VIN0_P AUDIO DRIVER ISINK0

3.3K [5] AU_VIN0_N [5] F4 AU_VIN0_N ISINK1 C9 ISINK1 [12]

E10 ISINK2 [12]

6

ISINK2

C C E [5] AU_VIN1_P [5] G3 AU_VIN1_P ISINK3 C10 ISINK3 [14][12]

U303

[5] AU_VIN1_N [5] G4 AU_VIN1_N

40mils

VA_PMU VA_PMU D2

1

AU_VIN2_P

C C B D1 AU_VIN2_N

G

U305

1uF

D:PMICZTE ULC2LINEAR CHARGER EVBMT6326_ATE_EVB V1_BGA_20080331.DSN

TRIODE-PNP-CJ10P20

1

J2

D3

AVDD28_ABB Please use inductor recommand by MTK

3 AVDD28_AUXADC

D H2 Refer to MT6323 design notice

C314

2 VDRV[3] GND_ABB

S

40mils

FET-N-2SK3541T2L

40mils 4mil [5] ACCDET [5] E2 ACCDET BUCK OUTPUT C14

HT303 VPROC L301 0.68UH

ISENSE [3]

SR0805

[6] CLK4_AUDIO[6] E1 CLK26M VPROC D14 VPROC_PMU

R328

0.2

Rsense Differential BATSNS [3][6] VPROC E14 [1]

HT304 2 1 VPROC_PMU [1,3]

D301 C A NF

4mil VPROC_FB B12 VPROC_FB [1] [1]

ISENSE/BSTSNS 4mil CHARGER C12

TP-1.0MM

40mils

TP-1.0MM AUXADC_REF

GND_VPROC_FB GND_VPROC_FB [1] ¿¿½üL305

[6] BATSNS [3] BATSNS P13 BATSNS

TP310 TP312 differential to Rsense L305 2.2UH

ISENSE [3] ISENSE P12 ISENSE VPA A14

TP-1.0MM AUXADC_REF [3,6][6] BAT_ON [3] BAT_ON K3 B14 VBAT

BATON VPA VPA_PMU [1]

TP311 VCDT [3] VCDT A12 VCDT

2

VDRV[3] VDRV M13 VDRV VPA_FB D12

R334

2.2uF

C337

16.9K

BATTERY VPA_PMU

1

2

CHR_LDO [3] CHR_LDO N13 CHRLDO

SOD-323

CONNECTOR

CON301

D306

1

L303 0.68UH

1 40mils 40mils VSYS H14 VSYS_SW VSYS_PMU

2

C316

VBAT

1uF

CONTROL SIGNAL

1

3 R317 VBAT [3,7,9,14]

[6] R316 1K 2 1

4 [20] PWRKEY [14] M2 PWRKEY A NF

BAT_ON [3] [2] WATCHDOG [2,4] A1 D303 C VPA_SW

SYSRSTB

5 1K [2] RESETB [2] K4 RESETB

A9 ALDO OUTPUT M3 VA_PMU

FSOURCE VA

2

6

[2] EINT_PMIC [2] A7 INT

Close to PMIC

R335

SOD-323

N12 N3 VCN_2V8_PMU

27K

EXT_PMIC_EN VCN28

D305

0.1uF

C345

L4

VR301

VR302

VTCXO VTCXO_PMU

BBATTCON-BAC3290400 R334,R335 must to be close to N2

VEMC_3V3_PMU

PMU_TESTMODE

PMIC AUXADC_REF pin VCAMA P3 VCAMA_PMU

1

[2] AUD_MOSI [2] E7 AUD_MOSI VCN33 M6 VCN_3V3_PMU

[2] AUD_CLK [2] E8 AUD_CLK AVDD33_RTC C3 VRTC

[2] AUD_MISO [2] B6 AUD_MISO C331

C355 1uF

[2,6]SRCLKENA [2,6] A2

0.1uF

SRCLKEN 100nF

C354

TP301

M1 DLDO OUTPUT

FCHR_ENB [3] FCHR_ENB [3] FCHR_ENB

VM J13 VM_PMU

Based on your system level design , if [2] PMIC_SPI_SCK [2] D9 SPI_CLK VRF18 H11 VRF18_PMU

if battery NTC is 10kohm, R334=16.9K, R335=27K [2,4]PMIC_SPI_CS [2] B7 SPI_CSN VIO18 L12 VIO18_PMU

better ESD performance is needed on [2] PMIC_SPI_MOSI [2] D8 M4 VIO28_PMU

if battery NTC is 47kohm, R334=61.9K, R335=100K SPI_MOSI VIO28

your system, please refer to ESD [2] PMIC_SPI_MISO [2] B8 SPI_MISO VCN18 J12 VCN_1V8_PMU

Refer to MT6323 HW design notice

VIO18_PMU [1,2,3,4,6,9,13,15] VBAT

VCAMD K14 VCAMD_PMU

performance enhance proposal VCAM_IO L13 VCAMD_IO_PMU

F13 VBAT INPUT

VBAT_VPROC

TP-1.0MM

R361

80mil 40mil F14 VBAT_VPROC

20K

G13 P7

TP9

VBAT_VPROC VEMC_3V3 VEMC_3V3_PMU

1 4mil (VPA no use) VBAT A13 L6 VMC_PMU

VBAT_VPA VMC

VMCH P4 VMCH_PMU

R360 15mil VBAT H13 VBAT_VSYS VUSB N6 VUSB_PMU

P8 VBAT_LDOS3 VSIM1 P9 VSIM1_PMU

BAT_ID_ADC [2] Add Zenar Diode500mW 20mil VBAT P6 N9 VSIM2_PMU

VBAT_LDOS3 VSIM2

10uF

C310

1K

10uF_NF

Place on the path 20mil VBAT P5 VBAT_LDOS2 VGP1 L8 VGP1_PMU

C330

20mil VBAT P2 VBAT_LDOS1

from VBAT to IC

1

D302 VIBR M7 VIBR_PMU

VSYS_PMU 20mil J14 AVDD22_BUCK VGP2 N8

(Battery connector M14 L14 VGP3_PMU

AVDD22_BUCK VGP3

VR310

or test point or IO DVDD18_DIG_PMIC VCAM_AF N7 VCAM_AF_PMU

2

connector) A8 DVDD18_DIG

VF : 4.85V~5.36V

VIO18_PMU VIO18_PMU A5 DVDD18_IO

Between IC and IO port AUXADC_REF C2 AUXADC VREF

[6] AUXADC_REF [3,6] AUXADC_VREF18

[6] AUXADC_TSX [6] AUXADC_TSX B1 AUXADC_AUXIN_GPS VREF P14

[6] GND_AUXADC [6] GND_AUXADC B2 AVSS28_AUXADC

100nF

C320

Refer to MT6323 design C323

dedicate VSS ball, must return to cap then to main GND:

C322

1uF

BC 1.1

1. GND_VREF(N14) => C320

notice for Zener selection 100nF

[2] CHD_DM [2] A10 CHG_DM GND_VREF N14

[2] CHD_DP [2] A11 CHG_DP

10uF

C322 must to be close

10uF

Based on your system level design , if

better EOS performance is needed on your to PMIC AUXADC_TSX pin

RTC_32K1V8 D5 CLK32K_BB [2] [2]

X301 RTC

HT301

SIM LVS RTC C4

system, please refer to EOS performance RTC_32K2V8 RTC 32K : X301+C324+C319=> mount, R333=> NC

C303

C301

[2] SIM1_SCLK [2] B5 SIM1_AP_SCLK XIN A3 32K_IN

enhance proposal [2] SIM1_SIO [2] M11 SIMLS1_AP_SIO XOUT A4 32K_OUT 32K-less: X301+C324=> remove, C319+R333=> 0R

E6 1 2

SIM1_AP_SRST

1uF

18PF

18PF

10uF

10uF

1uF

C5 B10

1uF

[2] SIM2_SCLK [2] SIM2_AP_SCLK GND_ISINK

[2] SIM2_SIO [2] K11 SIMLS2_AP_SIO GND_VSYS G11

4.7uF

C350

D6 SIM2_AP_SRST GND_VPA E13

C304

Connect TSX/XTAL GND E11 XTAL-32.768K-KYOCERA

C306

C324

C319

GND_VPROC

C307

C308

C309

[19] SCLK[12] M9 SIMLS1_SCLK GND_VPROC F11

to AUXADC_GND first [19] SIO [12] N11 SIMLS1_SIO GND_VPROC F10

than connect to main GND [19] SRST [12] M10 SIMLS1_SRST

GND_LDO K6

[19] SCLK2[12] K9 SIMLS2_SCLK GND_LDO K8

[19] SIO2 [12] L11 SIMLS2_SIO

[19] SRST2 [12] K10 SIMLS2_SRST GND_LDO F5 Close to chip

GND_LDO F6 R333

GND_LDO F7 DCXO_32K

[6] [6]

F8

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

GND_LDO

refer to system analog LDO GND_LDO F9 0_NF

GND_LDO G5

performance improve proposal GND_LDO G6

VIBR_PMU

J10

J9

J8

J7

J6

H10

H9

H8

H7

H6

H5

G9

G8

G7

Vibra Refer to MT6323 design notice

for Buck GND layout rule

CON3

1

VRTC

C311

1uF

AUDIO-CON_SPK(MIC-RE-MOT)

R312

CON4

1K

AUDIO-CON_SPK(MIC-RE-MOT)

Refer to GPS co-clock layout rule GB301

1

22uF

C325

3V_NF

2

==> for longer RTC time sustain after battery remove,

please refer to RTC design notice

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 03_MT6323 SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 3 OF 15

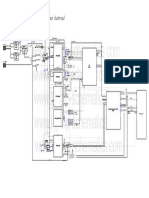

0

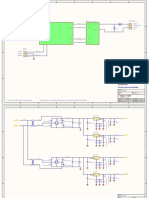

Memory MCP

VM_PMU VIO_EMI

R401

VIO18_PMU

C421

1 2

4.7uF

C422

1 2

U101-F U402

DRAM DRAM U3 E6 100nF

EA0[4] CA0 VDD1

AF6 Data Ctrl EA1[4] T3 F1

[4] ED12 ED31 CA1 VDD1 VIO_EMI

AE6 ED30 ECS0_B AF22 EA2[4] R3 CA2 VDD1 V1

[4] ED8

AF8 ED29 ECS1_B AF19 EA3[4] R2 CA3 VDD1 W6

[4] ED10 4.7uF

AE7 ED28 EA4[4] R1 CA4

[4] ED14 2 1

AE8 ED27 EWR_B AF21 EA3 [4] EA5[4] K2 CA5 VDD2 E5

[4] ED9

[4] ED13 AC9 ED26 ERAS_B AD21 EA6[4] J2 CA6 VDD2 G2

EA7 [4]

[4] ED15 AC7 ED25 ECAS_B AB20 EA7[4] J3 CA7 VDD2 K1 C401

EA5 [4] H3 M7

[4] ED11 AB9 ED24 ECKE AD24 EA8[4] CA8 VDD2 Put C402 & C403 between BB & memory.

[4] ED26 AF5 ED23 EA9[4] H2 CA9 VDD2 U2 100nF

[4] ED25 AE5 ED22 EDQM0 AB13 EDQM2 [4] VDD2 W5 2 1

AD5 AD12 ED0[4] T8

[4] ED28 ED21 EDQM1 EDQM0 [4] ED1[4] DQ0

[4] ED30 AC5 ED20 EDQM2 AD8 R8 DQ1 VDDQ F7

EDQM3 [4] ED2[4] C402

[4] ED29 AE4 ED19 EDQM3 AE12 R7 DQ2 VDDQ F10

EDQM1 [4] ED3[4]

[4] ED27 AF3 ED18 R9 DQ3 VDDQ G5 1 2

[4] ED31 AF2 ED17 EDQS0 AA14 EDQS2 [4]

ED4[4] R6 DQ4 Power VDDQ H9

AB6 Y13 ED5[4] P7 J10

[4] ED24 ED16 EDQS1 EDQS0 [4] ED6[4] DQ5 VDDQ C403 100nF

AE11 ED15 EDQS2 Y8 P8 DQ6 VDDQ L6

[4] ED7 EDQS3 [4] ED7[4] 1uF

AD15 ED14 EDQS3 AA9 P9 DQ7 VDDQ M6

[4] ED0 EDQS1 [4] ED8[4] 1 2

[4] ED1 AE10 ED13 K9 DQ8 VDDQ N6

AE9 Y14 ED9[4] K8 R10

[4] ED6 ED12 EDQS0_B EDQS2_B [4] ED10[4] DQ9 VDDQ

AF12 ED11 EDQS1_B AA13 K7 DQ10 VDDQ T9 C129

[4] ED2 EDQS0_B [4] ED11[4]

AF11 ED10 EDQS2_B AA8 J6 DQ11 VDDQ U5 1 2

[4] ED3 EDQS3_B [4] ED12[4]

AF9 ED9 EDQS3_B Y9 J9 DQ12 VDDQ V7

[4] ED5 EDQS1_B [4] ED13[4] 4.7uF

AC13 ED8 J7 DQ13 VDDQ V10

[4] ED4 ED14[4] C110

AE16 ED7 EDCLK0_B Y18 J8 DQ14

[4] ED17 ED15[4]

AE13 ED6 EDCLK0 AA18 H8 DQ15 VDDCA J1

[4] ED22 ED16[4]

AE15 ED5 W7 DQ16 VDDCA L1

[4] ED18 ED17[4]

AE14 AA19 U6 DQ17 VDDCA T2 VEMC_3V3_PMU

[4] ED21 ED4 EDCLK1_B EDCLK_B [4] ED18[4] VIO18_PMU

AF15 ED3 EDCLK1 Y19 W8 DQ18

[4] ED16 EDCLK [4] ED19[4]

AF16 ED2 T5 DQ19 VCC A8

[4] ED19 ED20[4]

AC15 ED1 U7 DQ20 VCC B2

[4] ED20 ED21[4]

AB16 ED0 ND0 AA2 W9 DQ21 VCCQ B8

[4] ED23 NAND I/F NLD1 ED22[4]

ND1 Y2 NLD8 V8 DQ22 VDDI A5 EMMC_VDDI

ED23[4]

2

T6

2

AB17 W1

2

VREF1 ND2 NLD3 ED24[4] DQ23

4.7uF

H6 B5

C412

100nF

AC11 W3

C404

DQ24 CLKM NREB [4]

C410

[4] EVREF VREF0 ND3

1uF

NLD13 ED25[4]

ND4 AB1 F8 DQ25 RST C1 NLD10 [4]

DRAM NLD10 [4] ED26[4] E9 C5

ND5 AD2 DQ26 CMD NRNB [4]

NLD5 [4] ED27[4] eMMC

1

Address

1

G7

1

AB18 EA18 ND6 W4 NLD12 DQ27

AE18 AE1 ED28[4] H5 B4

EA17 ND7 NLD14 [4] DQ28 DAT7 NALE [4]

AE17 W2 ED29[4] E8 A4

EA16 ND8 NLD9 DQ29 DAT6 NCLE [4]

AE21 Y3 ED30[4] G6 A6

EA15 ND9 NLD6 DQ30 DAT5 NLD4 [4]

AB19 AC2 ED31[4] E7 B6

[4] ECKE EA14 ND10 NLD4 [4] DQ31 DAT4 NLD5 [4]

AE22 EA13 ND11 AC1 R454 DAT3 A7 NLD7 [4]

[4] EA4 NREB [4] 2

AC23 EA12 ND12 Y4 R455 1 G3 ZQ0 DAT2 B7 NLD14 [4]

NLD0 1 2

AD22 EA11 ND13 V5 F3 ZQ1/NC DAT1 B3 NLD11 [4]

[4] EA6 NLD2 240

AD18 EA10 ND14 AE2 DAT0 A3 NWPB [4]

[4] ECS1_B NLD7 [4] 240

[4] EA8 AE25 EA9 ND15 V1 NLD15

BA[1:0] AE23 F6 P1

[4] = EA2 EA8 VSSQ CS0# ECS0_B[4]

[4]

EA[15:14] ECS0_B AF25 EA7 F9 VSSQ CS1#/NC P2 ECS1_B[4]

AE24 EA6 G10 VSSQ

(LPDDR1) AF24 W5 H10 N1 ECKE[4]

EA5 NCEB NCEB VSSQ CKE0

AE26 EA4 NWRB Y5 J5 VSSQ CKE1/NC N2

[4] EA9 NWRB

AC18 EA3 NREB AB2 [4] K10 VSSQ

GPIO46

AE19 EA2 NCLE AC3 M5 VSSQ CLK M3 EDCLK[4]

NCLE [4]

[4] EA0 AE20 EA1 NALE AD3 P10 VSSQ CLK# L3 EDCLK_B[4]

NALE [4]

AF18 EA0 NRNB AE3 R5 VSSQ

[4] EA1 NRNB [4]

GPIO47 AB3 T10 VSSQ DQS0 P6 EDQS0 [4]

NLD11 [4]

U10 VSSQ DQS0# P5 EDQS0_B [4]

AC22 ERESET V6 VSSQ DQS1 K6 EDQS1 [4]

V9 VSSQ DQS1# K5 EDQS1_B [4]

DQS2 U8 EDQS2 [4]

T1 VSSCA DQS2# U9 EDQS2_B [4]

M1 VSSCA DQS3 G8 EDQS3 [4]

BGA428-10.7X10.7-0.4E0.25B(MT6572) H1 VSSCA DQS3# G9 EDQS3_B [4] VIO_EMI

B9 VSSM DM0 N5 EDQM0 [4]

E1 VSSM DM1 L5 EDQM1 [4]

F2 LP-DDR2 T7

1

VSS DM2 EDQM2 [4]

F5 VSS DM3 H7 EDQM3 [4]

10K

R452

G1 VSS

L2 VSS VREFCA K3 EVREF [4]

M8 VSS VREFDQ M9

U1

2

VSS

Please make sure the ball map is V2

V5

VSS NC C2

C4

EVREF [4]

2

VSS NC

C3 C6

100nF

match to the MCP type you selected VSSQM NC

C453

NC D1

10K

R453

A1 DNU NC D2

A2 D3

1

DNU NC

A9 DNU NC D4

A10 D5

2

DNU NC

B1 DNU NC D6

B10 DNU NC E2

E10 DNU NC E3

W1 DNU NC M2

W10 DNU NC N3

Y1 DNU NC P3

Y2 DNU NC V3

Y9 DNU NC W2

Y10 DNU NC W3

Hynix H9TP32A4GDMCPR;H9TP32A8JDMCPR-KGM;Micron MT29PZZZ4D4TKETF-25

R412 0_NF

1 2 WATCHDOG [2,3]

NWPB [4]

1 2 GPIO46

R413

0

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 04_MEMORY_EMMC_LPDDR2 SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 4 OF 15

Earphone Audio close to IC

same power domain

close to connector

R505 470K

VIO28_PMU

R506 47K

[2] EINT_HP

Reserve bead+C footprint for FM

performance tuning

NF

NF

Based on your system level design , if better BEAD501 1800ohm

C530

C529

[5] HP_MIC HP_MIC-1 [5]

desense performance is needed on your

system , please refer to desense BEAD503 1800ohm 10uF R507 33 HP_MP3L BEAD502 1800ohm

[3] AU_HPL [3] C519 HP_MP3L-1 [5]

performance enhance proposal

Receiver [3] AU_HPR [3]

BEAD504 1800ohm C520 10uF R508 33

HP_MP3R

BEAD505 1800ohm EAR_DET [5]

HP_MP3R-1 [5] [5] HP_MIC-1 1

2

J501

[5] FM_ANT-1 3

33PF

33PF

close to IC close to connector J502

VR502

[5] HP_MP3R-1

FM_ANT-1 [5]

1 4

[5]HP_MP3L-1

C506

33PF

2 EAR_DET 5

[5]

C522

C521

6

1

R520 REC-NOG-93045-WQM2000000

VR501

[3] AU_HSP

[3]

AUDIO-EAR-PH8-5B05F35A

0

2

100PF

C505

470

470

R521 R501 [10]

[3] AU_HSN

[3] J503 1 2 FM_ANT [11]

0 1 0

R509

R510

2

C504

33PF

100NH

VR503

L502

REC-NOG-93045-WQM2000000

Based on your system level design , if better ESD

performance is needed on your system, please

VR505

VR504

VR506

refer to ESD performance enhance proposal R502

1 2 FM_RX_N_6572 [11][10]

0

Single via to GND plane

Handset Microphone 1 MICBIAS0

R514

1K

VR508

Close to

Close to

MIC

BB

MICBIAS1

1.5K

R515

Analog MIC Earphone MICPHONE

C511 0.1uF CON502

1K

[3] AU_VIN0_P

R522

C513 1

Close to BB Close to MIC GND of C(4.7uF) and headset

100PF

R523

C508

R511

2 should tie together and single

4.7uF 0

0.1uF 4.7uF via to GND

GND plane

C512 C523 100nF AU_VIN1_N1 C531

[3] AU_VIN0_N [3] AU_VIN1_N

AUDIO-MIC-OB-F15PD44-26-C10C33EP

33PF

33PF

C526 R512

Close to EarJack

1.5K

33PF

R516

C509

C510

100PF

1.5K

VR509

C525

C527

if you use digital MIC, C524 100nF

33PF

[3] AU_VIN1_P HP_MIC [5]

please change cap

R517

1K

(C511,C512) to 1.0uF

R513

together then single

1K

[3] ACCDET

via to main GND

together then single via to main GND

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 05_AUDIO SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 5 OF 15

7

RF9810 control logic table

L604

Enable VctC VctB VctA 1 2

W_PA_OUT_B8

TRXB2 [7]

LB_GMSK_TX H L H L 0 ohm

TRXB8 7

HB_GMSK_TX H L H H

C606

2.2nH

NF

L638

L607

1 2

LB_EDGE_TX H L L L TRXB1 [7]

1

0 ohm [7] [7]

HB_EDGE_TX H L L H

2

7

C652

2.2nH

NF

C608

RX1 L H L L GND GND

RX2 L L H L

1

RX3 L L H H 7 W_PA_OUT_B2 [7]

GND GND 27nH

RX4 L L L H 1 2

GND

3

ANT 6

1

L612

SAYFP1G95CA0B00

C639

TX

1.1nH

W_PA_OUT_B1 [7] G 9

G 7

G 5

2

7 G 4

3

ANT 6

G 9.1nH

SAYFP1G95CA0B00

1 2

U602

2

RX

RX

TX

G GND

GND

9

G 7

G C641

1

8

5

7 G 4

G

U616

2

6

RX

RX

SAYRJ897MCA0F00

GND 4.3nH L603

ANT

G 9

1 2 G

1

8

7

G

GND

5

GND G 4

1

G

U607

4.3nH L653 2

TX

RX

RX

1

1

C601

4.7pF

1 2

C602

C603

4.7pF

NF

3

1

8

L601 L602

2

GND

1 2 1 2

2

1

1

C616

4.7pF

NF NF

C609

C645

4.7pF

33nH

NF

L621 L634 1 2

2

1 2 1 2

2

L613

2

NF NF

1.8nH

1.8nH

C617

C626

1

1

NF

1 2

L614

L600

GGE_PA_LB_IN

GGE_PA_HB_IN

[7] [7]

[7]

W_PA_B1_IN

LB_RX_P [6]

W_PA_LB_IN

W_PA_B2_IN

12nH

L616

39nH

C600

NF

L618

L615

10

2G_LB [7]

Z600

BPI0~4 and 10~11 are 2G+3G mode both 2.2nH L619

GND

22PF

VRF18-1 [6]

C665

1 9 LB_RX_N [6]

NF

BPI5~9 and 12~14 are 3G mode only LBIN LBOUT

2 1.8nH

2.2nH

2 8 12nH

(suggest BPI5~9 = 1.8V) GND LBOUT C669 0.47UF

3 7 VRF18-1

GND HBOUT

GGE_PA_HB_IN

C667

GGE_PA_LB_IN

[2] [2,6,7]BPI_0 BPI_0 [2,6,7] [2] L622 L623

[2] [2,6,7]BPI_1 BPI_1 [2,6,7] [2][2] 2G_HB [7] 4 6 HB_RX_P [6]

GND

[2] BPI_2 [2] HBIN HBOUT

[2,6,7]BPI_2 [2,6,7]

6.2nH PDET [7]

C19 1

3.3nH

L2

22PF

C668

[2] [2,6,7]BPI_3 BPI_3 [2,6,7]

NF

L625

7.5nH

NF

L624

L626

D11

C10

A10

A11

B11

B10

D3

C3

C2

C7

C8

C9

E3

A2

A3

B3

B4

A5

B5

A6

B6

B8

A8

A9

J2

J7

J8

HB_RX_N [6] U600

6.2nH

GND

GND

GND

GND

GND

3GB1_RXP

3GB1_RXN

3GB5_RXP

3GB5_RXN

3GB2_RXP

3GB2_RXN

3GB8_RXP

3GB8_RXN

2GHB_TX

3GH1_TX

3GH2_TX

3GL5_TX

2GLB_TX

VTXHF

DET

GND

GND

GND

GND

GND

GND

GND

F3 GND GND D9

G3 GND GND E9

H3 GND GND F9

J3 GND GND G9

C4 FDD RX TXO H9

GND GND

D4 GND GND J9

[2] [6] WG_GGE_PA_VRAMP

WG_GGE_PA_VRAMP [6] [2]

Two Application Circuit Conditions, A1 B40_RXP DETGND D10

B1 C11 TMEAS

1.TSX Circuit : X600=TSX, R653=R656=NC, R654=100K+-1%, R655=R657=0ohm B40_RXN TMEAS

LB_RX_P [6] LB_RX_P C1 LB_RXP V28 E10 VTCXO28-1 VTCXO28-1 [6]

2.XTAL Circuit :X600=Mobile XTAL, R653=R656=0ohm, R654=R655=R657=NC TDD RX R639

0

LB_RX_N [6] LB_RX_N D1 LB_RXN 3GTX_IP G10 TX_I_P TX_I_P [2,6]

DCXO_32K [3,6] connect to main GND

0.47UF

[3] [3,6] DCXO_32K [3]

C674

HB_RX_P [6] HB_RX_P E1 HB_RXP 3GTX_IN G11 TX_I_N TX_I_N [2,6]

R633 [3] AUXADC_REF [3] Route AUXADC_REF with 4mil trace width TX(I/Q)

0 VTCXO28-1 [6]

VTCXO_PMU HB_RX_N [6] HB_RX_N F1 HB_RXN 3GTX_QP F10 TX_Q_P TX_Q_P [2,6] 1

C675

NF

VRF18-1 [6]

R634 0 X600

VRF18_PMU VRF18-1 [6] VRF18-1 F2

MT6166 F11 TX_Q_N R645

C685

0 VRXHF 3GTX_QN TX_Q_N [2,6]

1uF

XTAL-CRYSTAL-26M-7M26

R656

R654

0.47UF G2 RFVCO_MON TXVCO_MON L11 VRF18-1 [6]

VIO18_PMU VIO18_PMU C676 100K

R657 BGA104-4.7X4.7-0.4E0.25B(MT6166)

[3] AUXADC_TSX [3] Route AUXADC_TSX with 4mil trace width 4

GND IN/OUT

3 J1 XTAL1 VTXLF J11 VRF18-1

2 R610 close to 3G PA

[2] BSI-A_EN [2,6] BSI-A_EN [2,6]

[2]

[2] BSI-A_CK BSI-A_CK [2,6]

[2] H2 XTAL2 TXBPI H10 TXBPI TXBPI [2,6] 0.47UF [2]

[2,6]

NF

XO

[2] BSI-A_DAT0 [2,6] BSI-A_DAT0 [2,6]

[2] 1 2

[2] BSI-A_DAT1 BSI-A_DAT1 [2,6]

[2] IN/OUT GND VTCXO28-1 K1 VTCXO28 RCAL J10 RCAL

[2,6] Test pin

[2] BSI-A_DAT2 [2,6] BSI-A_DAT2 [2,6]

[2] Route AUXADC_GND with 24mil trace width R655 R600

[3] GND_AUXADC [3] DCXO_32K_EN G1 32K_EN TST2 K11

[2] TXBPI [2,6] TXBPI [2,6] [2]

under AUXADC_REF/AUXADC_TSX trace SRCLKENA L1 L10

EN_BB TST1 1K

NF

SRCLKENA[2,3,6] [2,3] VTCXO28-1 [6] BSI

0

[2,3]SRCLKENA [2,3,6] SRCLKENA [2,3,6] [2,3] SRCLKENA K2 G8 BSI-A_DAT2 BSI-A_DAT2 [2,6]

[2]

R653

Close to each other C677 CLK_SEL BSI_DATA2

26M output

[2] CLK1_BB [2,6] CLK1_BB [2,6] [2]

[10] SYSCLK_WCN [6,11] and nearby X600 CLK3_CMMB L2 XO3 BSI_DATA1 H8 BSI-A_DAT1 BSI-A_DAT1 [2,6]

[2]

SYSCLK_WCN [6,11] [10] Connect TSX/XTAL GND

CLK3_CMMB [6] CLK3_CMMB [6] 0.47UF

[3] CLK4_AUDIO[3,6] to GND_AUXADC first E4 GND GND B7

CLK4_AUDIO [3,6] [3]

AVDD_VIO18

F4 GND GND J6

BSI_DATA0

than connect to main GND connect to main GND G4 RX(I/Q) D8

GND GND

BSI_CLK

OUT32K

VXODIG

RX_Q_P [2,6] H4 E8

XMODE

[2] RX_Q_P [2,6]

BSI_EN

RX_QP

RX_QN

GND GND

VRXLF

[2,3]SRCLKENA

[2,3,6]

RX_IP

RX_IN

[2] RX_Q_N [2,6] RX_Q_N [2,6]

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

XO4

XO2

XO1

[2] RX_I_N [2,6] RX_I_N [2,6]

[2] RX_I_P [2,6] RX_I_P [2,6] Route AUXADC_REF/AUXADC_TSX as differential trace with well GND shielding [2,3]SRCLKENA

[2,3,6]

J4

C5

D5

E5

F5

D7

K4

K3

L4

K5

L5

K6

K7

L7

L8

K8

K10

K9

G6

H6

F8

E7

J5

C6

D6

E6

F6

CLK3_CMMB [6]

[2] TX_Q_P [2,6] TX_Q_P [2,6]

and route AUXADC_GND with 24mil trace width under

[2] TX_Q_N [2,6] TX_Q_N [2,6] NF

AUXADC_TSX/AUXADC_REF trace to provide return current path. R616

RX_Q_P

RX_Q_N

[2] TX_I_N [2,6] TX_I_N [2,6] [6] VTCXO28-1

RX_I_P

RX_I_N

1 2 [3] CLK4_AUDIO [3,6] CLK4_AUDIO BSI-A_DAT0 BSI-A_DAT0 [2,6]

[2]

[2] TX_I_P [2,6] TX_I_P [2,6] R647 0 DCXO_32K_EN [6]

[10] SYSCLK_WCN [6,11] SYSCLK_WCN

1 2 [2] CLK1_BB [2,6] CLK1_BB BSI-A_CK BSI-A_CK [2,6]

[2]

[3] DCXO_32K [3,6] DCXO_32K

VRF18-1

BSI-A_EN

RX_Q_P

BSI-A_EN [2,6]

RX_I_P

[2]

RX_Q_N

RX_I_N

VIO18_VGPIO

Logic 2 1R1

MODE XMODE VXODIG NF [6] XMODE

DCXO_ 0

R649

[6] VIO18_VGPIO

32K_EN 1 2

R618 NF XMODE [6] VRF18-1 [6]

[6] VTCXO28-1 VIO18_PMU L630

1 2 0 C682 C684

[1,2,3,4,6,9,13,15]

DCXO + 32K XO 0(GND) 1(VIO18) 1(VIO18)

1uF 0.47UF

DCXO + 32K-Less 1(VTXCO28) 1(VTXCO28) 1(VTXCO28)

R648 0

[6] VIO18_VGPIO

1 2

[6] VXODIG Reserved LC filter

R617 NF VXODIG [6]

[6] VTCXO28-1 1 2

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 06_RF_TD_MT6166 SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 6 OF 15

R715

BPI_2 [2,6]

1K 2

R716

R3

BPI_3 [2,6]

1K 2

VAPC1 [2] 1 2

22PF

22PF

C18

C17

10k

2

1

220PF

C11

24K

R717

SKY77590 control logic table

1

2

GND VctA VctB VctC TxEn

GND

6 2G_HB [6] SKY77590 ¼æÈÝSKY77584Éè¼Æ BS2 BS1 mode ebable

2

VBAT

(TRX1)G_DCS L L H L

[6]

6 2G_LB SKY77590 pin22 pin24¿É½ÓÆäËûTRX¶Ë¿Ú£¬¿ÕÔØʱÐèÒª51Å·Ä·½ÓµØ

(TRX2)W_Band8 L H H L

2

2

(TRX3)W_Band1 H L H L

2

TRXB1 [6]

10uF

22PF

C13

100PF

6

C14

C707

10uF

C650

[6]

SKY77584 pin22 pin24½ÓµØ (TRX4)W_Band5 H H H L

TRXB2

1

6

1

(TRX5)W_Band2 L H L L

1

GND GND

6

(TRX6) NA H L L L

¶àÓàµÄ¶Ë¿Ú£¬ÓÃ50Å·Ä·½ÓµØ

EDGETX_L H L H H

EDGETX_H H H H H

R714

GMSKTX_L H L L H

BPI_1 [2,6] GMSKTX_H H H L H

1K TRXB8 [6]

2 GND

R713

[2,6] BPI_0

15

16

17

18

19

20

21

22

1K 2 TDD_B40_TX

1

GND

MODE

TXEN

VRAMP

TRX1

TRX2

TRX3

TRX4

R730

51

U1

22PF

22PF

C15

C16

R729

R726 1 2

14 1 2 ANT701 ANT702 ANT703

VCC 0723 50ohm terminated

GND

23 NF

2

13 TRX5

1

1

VBATT 0

24

RF-PA-SKY77590

12 TRX6

BS1 C708 J701

25 GND R725 J700 C756

C12 11 GND 1 2 R724

BS2 2 1 1 IN OUT 4 1 IN 2 1

10 ANT

26 OUT 4 1 2

GGE_PA_LB_IN [6] 6 2 1 TX_LB_IN

27 39pF 0

9 GND N161788340 RF-MM8430-2600 RF-MM8430-2600 39pF 0

TX_HB_IN

1

56PF

1

1

28

GND

C764

C768

C748

C757

C755

NF

NF

NF

NF

NF

C751

NF

GND

R712

NF

R705

NF

2

GND

GND

GND

GND

GND

GND

GND

GND

2

8

7

6

5

4

3

2

1

2

GND GND GND GND

18PF GND

2 1

GGE_PA_HB_IN

[6] EDGE TXM

C712

1

1

R711

NF

R710

NF

2

GND GND

W_PA_VBAT [7] W_PA_VBAT [7]

W_PA_VCC W_PA_VCC [7]

[7]

2

2 2

2

2

2

2 2

82pF

0.1uF

VM1[2,7] VM1 [2,7]

C719

C720

BPI0~6 are 2G+3G mode both

0.1uF

0.1uF

0.1uF

82pF

C746

C736

C737

C733

VM0[2,7] VM0 [2,7]

BPI7~13 are 3G mode only

1

1

1

6 6 GND

GND GND GND GND

GND

10

10

4

3

4

3

1

VMODE_0

VMODE_1

VBAT

VCC

VMODE_0

VMODE_1

VBAT

VCC

C725

C728 C745 R719 C726

R720 2 1 1 2

6 2 1 1 2 2 9 2 1 W_PA_B1_IN

6 2 9 1 2

[6] W_PA_LB_IN RF_IN RF_OUT 6

W_PA_OUT_B8 [6] RF_IN RF_OUT W_PA_OUT_B16 [6]

[6] 18PF 0

18PF 0 56PF R723 51 1.1nH

2

2

U708 U713

2

8 6 GND 8 6

1

C750

C732

CPL_IN CPL_OUT CPL_IN CPL_OUT

NF

NF

1

C749

sky77768 SKY77761

C754

NF

NF

R728

NF

R727

NF

1

2 5 2 5

GND

GND

GND

GND

W_PA_B8_EN VEN W_PA_B1_EN VEN

1

1

[2] GND GND [2]

GND GND

2

2

7

11

7

11

GND

1

3G_PA_CPL_OUT [7] GND

GND

R752

0

R758

0

GND

2

2

3G_B2_CPL_OUT [7] 3G_B1_CPL_OUT

[7]

R622

1 2

VPA_PMU W_PA_VCC

[7]

0

2

2.2uF

C735

VBAT

1

GND

R619

1 2

VBAT W_PA_VBAT [7]

0 W_PA_VBAT [7]

W_PA_VCC [7]

2

2

2

2

2

82pF

0.1uF

VM1 [2,7]

C610

C611

0.1uF

C607

VM0 [2,7]

1

1

GND

GND GND

10

4

3

1

VMODE_0

VMODE_1

VBAT

VCC

C624

R625 C621

2 1 1 2 1 2

W_PA_B2_IN 2 9

[6] RF_IN RF_OUT W_PA_OUT_B26 [6]

18PF 0

1.1nH

2

3G_B1_CPL_OUT [7] 8 U606 6

C622

C623

CPL_IN CPL_OUT

NF

NF

1

SKY77762

R623

²Î¿¼Éè¼ÆÊÇ26Å·Ä· ²Î¿¼Éè¼ÆÊÇ26Å·Ä·

NF

1

near-IC 2 5

GND

GND

W_PA_B2_EN VEN

R733 R737 [2]

1 2 1 2 GND GND

PDET 3G_PA_CPL_OUT [7]

2

6

7

11

[6]

24 24

2

GND

R746

GND

R620

36

²Î¿¼Éè¼ÆÊÇ35Å·Ä·

1

3G_B2_CPL_OUT

GND [7]

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 16.TD_WCDMA SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 7 OF 15

USB HS IF

TP-1.0MM

TP701

TP-1.0MM TP-1.0MM TP-1.0MM

TP1 TP-1.0MM

TP703 TP704

TP702

1

1

1

1

1

CON6401

CON701

1

1

VBUS

90 ohm differential R703 0 2

AUDIO-CON_SPK(MIC-RE-MOT) [2] USB_DM

CON1

R702 0 3

1 [2] USB_DP

4

KCOL0

[2,14] 1K R701 5

AUDIO-CON_SPK(MIC-RE-MOT)

USB-UAF95-05164-S115-A-CUS

220ohm GND

[3] AU_SPKP

2.2uF_NF

SPK_N

C710

VR701

BEAD701

VR702

TVS701

TVS702

100PF

C702

À®°È

220ohm

AU_SPKN GND GND

[3] GND GND

SPK_P

BEAD702

GND

C703

C704

33pF

33pF

VR703

VR704

FIDUCIAL-MARK-1MM

FIDUCIAL-MARK-1MM

FIDUCIAL-MARK-1MM

FIDUCIAL-MARK-1MM

TP2 S701 TP5 TP6 TP7 TP8

HOLE-3.2MM

TP3

1

1 TP4 TP23 TP24

HOLE-1.8MM HOLE-1.8MMHOLE-1.6MM

HOLE-2.4MM

1

SN-23X5

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 07_USB SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 8 OF 15

VBAT

TP-1.0MM

TP-1.0MM TP-1.0MM TP-1.0MM TP-1.0MM TP-1.0MM

TP907

TP905 TP904 TP903 TP902 TP901

CTP FB901 L901 D901

R905 30ohm 10UH

1

1

1

1 2 C933 FB902

GND

10K LEDA [9]

VIO18_PMU VIO18_PMU 2.2uF U901

R823 1K 600ohm

[2] GPIO_CTP_RSTB CTP_GPIO_CTP_RSTB

[9] 6 1

VIN SW

[2] EINT_CTP

R822 1K

CTP_EINT_CTP

[9]

GND C938 50V C939

GND 2 GND NC/OVP/VOUT

5

R923 1uF 47PF

[1,3,5,9,15] VIO28_PMU VIO28_PMU [1,3,5,9,15] 4 3

R821 1K LCD_BL_CTL EN FB

[2,15] SDA_1 CTP_SDA_1

[9] [2] 0 GND GND

R820 1K LED-DRIVER-ET5119A

R912

[2,15] SCL_1 CTP_SCL_1

[9]

C922

NF

R810

NF

LEDK [9]

100K

J902

1 GND R903

[9] CTP_GPIO_CTP_RSTB C924

47PF

2

[9] CTP_EINT_CTP [9] LCD_CABC 15

3

[1,3,5,9,15] VIO28_PMU

C915

0.1uF

4

2

[9] CTP_SCL_1

C913

100nF

GND GND

100nF(NF)

5

VR910

2

100nF(NF)

[9] CTP_SDA_1

VR908

2

100nF(NF)

VR907

6

VR909

VR906

GND

1

C914

C907

1

1

C912

1

1

ZIF-04-6298-006-000-883+

GND GND GND GND GND

Backlight LED Driver

Main LCM

GND

C909

47PF

ZIF-FH26-25S-0.3SHW

LEDA [9]

27

26

1 2 25

[2] LCD_ID_ADC

1K R907 24

[9] LEDK

23

[9] LEDA

22

R916

2 1 2 21

VIO28_PMU R915 0

2 1 20

VIO18_PMU 0

2

19

0.1uF

C905

2

33

18

C906

[2] LPTE

1

R920 17

0.1uF

GND

1

[2] GPIO_LRSTB

GND 16

15

[9] LCD_CABC

2

C908

14

100nF

EMI906 13

1

[2] 1 4 12

MIPI_TCN GND

[2] 11

MIPI_TCP 2 3

10

EMI908

9

[2] 1 4 8

MIPI_TDN1

[2] 2 3 7

MIPI_TDP1

6

5

EMI907

4

[2] 1 4

MIPI_TDN0

3

[2] 2 3

MIPI_TDP0 2

J6401

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 08_LCD_CTP SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 9 OF 15

[2,10] [2,10]

GPIO_CMRST2

GPIO_CMRST2

[2,10] [2,10]

VCAMD_IO_PMU VCAMA_PMU CMVSYNC

[2,10] [2,10] CMVSYNC

VCAMD_PMU

CMHSYNC

CMHSYNC

[2,10] [2,10]

VCAM_IO CMDAT7

CMDAT7

C940 33PF_NF

C941 33PF_NF

C942 33PF_NF

C943 33PF_NF

C930

R922

R909

0

0

R921

0

1uF

[2,10] [2,10]

CMDAT2

CMDAT2 [2,10] [2,10]

AVDD_SUB [10] CMDAT1

CMDAT1 [2,10] [2,10]

CMDAT3

[10] CMDAT3 [2,10] [2,10]

DVDD_SUB

DOVDD_SUB [10] CMDAT0

CMDAT0

C944 33PF_NF

C945 33PF_NF

C946 33PF_NF

C947 33PF_NF

0.01uF

1uF

C927

1uF [2,10] GND [2,10]

C926

C925

CMDAT4

CMDAT4 [2,10] [2,10]

CMPCLK

CMPCLK [2,10] [2,10]

GND CMDAT5

GND CMDAT5 [2,10] [2,10]

CMDAT6

CMDAT6

C948 33PF_NF

C949 33PF_NF

C950 33PF_NF

C951 33PF_NF

GND

AVDD_SUB

DVDD_SUB

DOVDD_SUB

J5101

1 24

AGND Y2 CMDAT0 [2,10]

2 23

[2,10] SDA_0 SIO_D Y3 CMDAT1 [2,10]

3 22

AVDD(2.8V) Y4 CMDAT2 [2,10]

[2,10] 4 21

SCL_0 SIO_C Y5 CMDAT3 [2,10]

5 20 CMDAT4 [2,10]

DGND Y6

6 19 CMDAT5 [2,10]

[2,10] CMVSYNC VSYNC Y7

7 18

DGND Y8 CMDAT6 [2,10]

8 17

[2,10] CMHSYNC HREF Y9 CMDAT7 [2,10]

9 16

DVDD(1.5V) Y1

[2,10] CMMCLK 10 15

XCLK1 RESET GPIO_CMRST2 [2,10]

11 14

[2] GPIO_CMPDN2 PWDN Y0

12 13 CMPCLK[2,10]

DOVDD(2.8V) PCLK

BTB-AXK724147G(DL200)13040

CAP-0201-NF

2

C960

NF

1

GND

1 TP-1.0MM

TP45

FRONT_camera

light sensor 0x90 Write(STK3171)

light sensor 0x46 Write (LTR-558ALS)

Main Camera / Sub Camera share power domain design

should double check the voltage level is compatible

[2] MIPI_RCN 2 3

[2] MIPI_RCP 1 4

J0003

24 1

NC NC

EMI901 23 2

NC AGND CMMCLK [2,10]

22 3 R906 0

Y2 SIO_D

21 4 1 2

Y1 AVDD R911 VCAMA_PMU VCAMA

2 3 20 5 0

[2] MIPI_RDN0 Y3 SIO_C 1 2

19 6 VCAMD_PMU VCAMD

Y0 RESET

18 7 1 2

1 4 Y4 VSYNC VCAMD_IO_PMU VCAM_IO

[2] MIPI_RDP0 17 8 R910 0

PCLK PWDN

16 9

Y5 HREF

15 10 SDA_0 [2,10]

EMI902 DGND DVDD

14 11

VCAM_AF' Y6 DOVDD SCL_0 [2,10]

13 12

XCLK Y7 GPIO_CMRST [2]

2 3

[2] MIPI_RDN1 [2] GPIO_CMPDN

C961

BTB-AXK724147G

1uF

1uF

2

1 4

C9182.2uF

[2] MIPI_RDP1

NF_0.01uF

C902

C904

1

EMI903

GND GND GND

MAIN_camera TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 09_CAMERA SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 10 OF 15

XTAL-TCXO-26M-DSB321SCL

4

OUTPUT

VCC

U1006

R1013 0

VCN_2V8_PMU

GND

GND

U101-C

C1022

[11] GPS_RX_IN B16 GPS_RXIN GND_WBG A14

[11] CONN_XO_IN

1uF

A16 GPS_RXIP GND_WBG D18

[11] GPS_RX_IP

GND_WBG B22

GND_WBG C16

B14 GPS_RXQN GND_WBG C17

[11] GPS_RX_QN

B15 GPS_RXQP GND_WBG C18

R1001 NF [11] GPS_RX_QP

SYSCLK_WCN [6] [6] GND_WBG C19

GND_WBG C20

[11] WB_TXIN A19 WB_TXIN GND_WBG C15

[11] WB_TXIP B19 WB_TXIP GND_WBG D16

GND_WBG D17

[11] WB_TXQN B18 WB_TXQN GND_WBG D19

[11] WB_TXQP A18 WB_TXQP GND_WBG D20

50 Ohm

WIFI/BT/GPS Single ANT Ref. [11] WB_RXIN A21

A22

WB_RXIN

WB_RXIP

GND_WBG C21

POGO-P03-AB001F140

[11] WB_RXIP

POGO-P03-AB001F140

CONN_WB_CTRL0 E20 WB_CTRL0 [11]

[11] WB_RXQN B20 WB_RXQN CONN_WB_CTRL1 F20 WB_CTRL1 [11]

B21 WB_RXQP CONN_WB_CTRL2 D22 WB_CTRL2 [11]

[11] WB_RXQP

ANT0901

ANT0001

CONN_WB_CTRL3 E22 WB_CTRL3 [11]

CONN_WB_CTRL4 C22 WB_CTRL4 [11]

CONN_WB_CTRL5 C23 WB_CTRL5 [11]

2

R1007 NF R1008 NF

1

[11] AVDD18_WBG F18 AVDD18_WBG CONN_RSTB C14 WB_RSTB [11]

1 2 1 2 CONN_SEN E15 WB_SEN [11]

NF

WB_CTRL3 [11] E14

CONN_SDATA WB_SDATA [11]

C1018

CONN_SCLK G12 WB_SCLK [11]

WB_CTRL2 [11]

1

CONN_F2W_DAT E13 FM_DATA [11]

[11] WB_CTRL4 CONN_F2W_CLK F12 FM_CLK [11]

WB_CTRL1 [11] F14

CONN_XO_IN CONN_XO_IN [11]

[11] WB_CTRL5

Close to MT6572

NF

L1

RF-SAW-DP1608-V1524CAT U1007

WB_CTRL0 [11]

6 GND WIFI 1

50 Ohm C1050 15PF [11] AVDD18_WB

R1030 0 50 Ohm HT1004 BGA428-10.7X10.7-0.4E0.25B(MT6572)

R1006 0 1 2 WB_RXIP [11]

50 Ohm 5 2 [11] AVDD18_WBG VCN_1V8_PMU

50 Ohm ANT GND

1 2

C1026

NF

50 Ohm WB_RXIN [11]

C1042

4 3 2 1

NF

100nF

C1001

GND GPS

U1000

L1004

18PF

30

29

28

27

26

25

24

23

22

21

W_LNA_EXT

AVDD18_WBT

WB_CTRL5

WB_CTRL4

WB_CTRL3

WB_CTRL2

WB_CTRL1

WB_CTRL0

WB_RX_IP

WB_RX_IN

GND

50 Ohm 31 WB_GPS_RF_IN WB_RX_QP 20 WB_RXQP [11]

[11] AVDD18_WB

HT1002

VCN_1V8_PMU

50 Ohm 32 GPS_DPX_RFOUT WB_RX_QN 19 WB_RXQN [11]

[11] AVDD18_GPS HT1003

VCN_1V8_PMU

Based on your system level design , if

better WiFi TX performance is needed on AVDD33_WB 33 AVDD33_WBT WB_TX_IP 18 WB_TXIP [11]

[11]

your system, please refer to WiFi Star Conn

100nF

C1007

performance enhance proposal 34 17 for WB/GPS/WBG 1V8

NC WB_TX_IN WB_TXIN [11]

50 Ohm

C1008

4700PF

C1005

C1006

35 16

1uF

NC WB_TX_QP WB_TXQP [11]

VCN_2V8_PMU_FM 36 AVDD28_FM

¸ÖÍø×öÆÁ±Î´¦Àí MQFN40-5X5-0.4E(MT6627) WB_TX_QN 15 WB_TXQN [11]

100PF

[11]

37 FM_LANT_N GPS_RX_IP 14 GPS_RX_IP [11]

FM [5] FM_RX_N_6572 [5]

[5] FM_ANT [5]

L1011

FM_RX_N_6572

FM_LANT_P

38 FM_LANT_P GPS_RX_IN 13 GPS_RX_IN [11]

82nH 91NH NF

82nH_NF

L1012

R1031

50 Ohm 39 GPS_RFIN GPS_RX_QP 12 GPS_RX_QP [11]

1 2

91NH

40 11

refer to FM desense performance

AVDD18_GPS AVDD18_GPS GPS_RX_QN GPS_RX_QN [11]

[11] enhance FB1010

proposal

AVDD28_FSOURCE

VCN_2V8_PMU_FM VCN_2V8_PMU

41 DVSS

R1009 0 600ohm

0.01uF

F2W_DATA

C1002

F2W_CLK

FM_DBG

U1002

HRST_B

SDATA

XO_IN

SCLK

CEXT

SEN

U1004 1 6

GND RFOUT

R1032 0 MT6627 SMD QFN40

2 5

1

10

C1013 L1001 GND EN GPIO_GPS_LNA_EN [2]

1 4 2 1 1 2 3 4

IN OUT RFIN VDD

Close to MT6627

GND

GND

GND

33pF 9.1nH

2

GPS-LNA-RDALN16

0.1uF

C1023

HT1001

NF

2

2 1 VCN_3V3_PMU

[11]AVDD33_WB

100PF

WB_RSTB

2.2uF

1

100PF

0.22uF

C1015

2.2uF

[11] CONN_XO_IN

1uF

0 R1012 [11]

C1004

C1003

VCN_2V8_PMU

C1011

C1010

C1012

C1009

[3,11] [11] FM_DATA

[11] FM_CLK

Based on your system level design , if

better GPS performance is needed on

[11] WB_SCLK

your system, please refer to GPS

performance enhance proposal [11]WB_SDATA

[11] WB_SEN

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 10_BT_FM_GPS_WIFI_MT6627 SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 11 OF 15

[3,12]

VSIM1_PMU

TP-1.0MM

TP-1.0MM

TP1101

TP-1.0MM TP-1.0MM

TP1102 TP1103 SIM1 TP1104

R1120

NF

1

1

1

J1101

0 0

[3] SCLK 2 1 6 1 2 1 SIO [3]

CLK IO

[3] R1107 5 2 R1101

SRST RST VPP

VSIM1_PMU 4 3

VCC GND

[3,12]

SIM-CAF99-06300-1504

2

GND

VR1106

VR1107

C1101

VR1109

1uF

1

VR1110

GND GND GND

GND

GND

[3,12]

VSIM2_PMU

TP-1.0MM TP-1.0MM TP-1.0MM

TP1105 TP1106 TP1107

TP-1.0MM

TP1108

R1121

SIM2

NF

1

1

0_NF

1

2 1

R1106 0

2 1 SIO2 [3]

J1102

R1105

[3] SCLK2 2 1 6 1

CLK IO

R1108 0 5 2

[3] SRST2 RST VPP

VSIM2_PMU 4 3

VCC GND

VR1103

SIM-CAF99-06300-1504

1uF

2

VR1101

VR1102

GND

VR1104

C1102

1

GND GND GND GND

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 11_DUAL_SIM SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 12 OF 15

SD CARD VMCH_PMU

TP-0.8MM TP-0.8MM

TP1208 TP1206

TP-0.8MM TP-0.8MM

TP-0.8MM

TP1204

TP-0.8MM

TP1202

TP-0.8MM TP-0.8MM

TP1207 TP1205 TP1203 TP1201

2

R1201

1

1

0

1

1

1

1

Shielding connect to ground

CON2 VIO18_PMU

TP-0.8MM

R1205 0

1 TP25

[2] MC1DAT2 R1206 0 DAT_2

[2] MC1DAT3 R1207 0

2

[2] MC1CMD CD/DAT_3

R1208 0

47K_NF

3

R1212

[2] MC1CK CMD

1

R1209 0

R1210 0 4 9

[2] MC1DAT0 VDD

10

[2] MC1DAT1 5

CLK

11 MC1_INS [2]

GND 6 VSS 12

2

7

C1201

4.7uF

DAT0

VR1202

VR1203

VR1204

VR1205

VR1206

VR1208

VR1207

8

DAT1

1

GND

VR1201

GND

GND TFLASH-CAF11-08373-SF07

T¿¨clkÐèÒª±£»¤

T-card ESD protection is optional depends on

T-card's type and position

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 12_MEMORY_CARD SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 13 OF 15

Power Key

DO NOT put pull-up resistor on PWRKEY

TP-1.0MM

TP1302

1

[3] PWRKEY

VR1301

C1301

0.1uF

GND

GND

Volume Up(kcol1 krow0) 1

FPC1

R1301 1K

[2] KCOL1 2

R1302 1K 3

[2] KROW0

[2,8] KCOL0 R1303 1K 4

MAIN-BTB-5P-0.7P

GND

VR1302

VR1303

VR1304

GND GND

Volume Down(kcol0 krow0) For USB download

D1301

R1304

1 2

33 DIODE-LED-WHITE-0603

D1302

R1305

VBAT 1 2

ISINK3 [3]

33 DIODE-LED-WHITE-0603

D1303

R1306

1 2

MLV701

33 DIODE-LED-WHITE-0603

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 13_KEYPAD SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 14 OF 15

VIO18_PMU

AUX_I2C_SDA

AUX_I2C_SCL

R1407

10K_NF

VIO28_PMU

VIO18_PMU

U702

R1405

U1401 [2,9,15]

1 8

3 1 VDD SDA SDA_1

VDDIO SDO 2 7

GND

0 [2,9,15] SCL_1 SCL INT EINT_ALPXS [2]

4 2 R1403

VDDD SDX SDA_1 [2,9,15] 0 3 6

7 12 R1406 GND LDR

1uF

R1401 VDDA SCK 0 R1404

SCL_1 [2,9,15] 4 5

C1402

C1403

9 10 LEDA LEDC

GND CSB 0

0

8 11

LED power

C1401

GND PS SENSOR-ALS+PS+IR-AP3216C

0_NF

R1402

6 VIO18_PMU

0.1uF

1uF

CAP0 5

INT EINT_ACC [2,15]

SENSOR-ACCELER-BMA220

47K_NFR1415

GND

47K_NF

GND GND

R1416

KXTJ2-1009 VIO18_PMU

EINT8_ACC1[2,15] R14180_NF 0x1B Write EINT_ACC [2,15]

EINT8_ACC1 [2,15]

ALS+PS+IR

TITLE: <TITLE> REV: <REV>

DOCUMENT NO.: 14_SENSORS SIZED: A1

DEPARTMENT:

Hardware DEPT.

COMPANY:

DESIGNER: <DESIGNER> Last Saved Date: 2013-6-26 SHEET: 15 OF 15

You might also like

- K-Touch Confidential: Id MarkDocument14 pagesK-Touch Confidential: Id MarkncirNo ratings yet

- w706 v3.1 lpddr2 Mipilcm 2015030Document14 pagesw706 v3.1 lpddr2 Mipilcm 2015030Jhon Fredy Diaz CorreaNo ratings yet

- B6000 B8000 Blade MB H302 20130815-3Document10 pagesB6000 B8000 Blade MB H302 20130815-3stryker strykerNo ratings yet

- QHV5160 V1.0 SCHDocument1 pageQHV5160 V1.0 SCHToàn LeNo ratings yet

- 2BU001 V2.01 DL S56 DualDocument20 pages2BU001 V2.01 DL S56 DualRiza VirsadaNo ratings yet

- 2BT061 - V1 03 - DL (150121)Document22 pages2BT061 - V1 03 - DL (150121)Riza VirsadaNo ratings yet

- Schematic - F722 FC 20x20 ELRS - 2021-09-16Document1 pageSchematic - F722 FC 20x20 ELRS - 2021-09-16He is LegendNo ratings yet

- P1ma40 SchematicsDocument21 pagesP1ma40 Schematicsaris coolNo ratings yet

- TS100 V2.46 Schematics V1.0 PDFDocument1 pageTS100 V2.46 Schematics V1.0 PDFzoki100% (2)

- TS100 V2.46 Schematic Diagram V1.0 PDFDocument1 pageTS100 V2.46 Schematic Diagram V1.0 PDFnitroboozter100% (1)

- TS100 V2.46 Schematic Diagram V1.0 PDFDocument1 pageTS100 V2.46 Schematic Diagram V1.0 PDFAlexandre Correa100% (1)

- TS100 V2.46 Schematics V1.0Document1 pageTS100 V2.46 Schematics V1.0dnn38hdNo ratings yet

- Iprog Mainboard SCHDocument1 pageIprog Mainboard SCHnelson lince100% (1)

- Skyworth 5M67BDocument19 pagesSkyworth 5M67BAlb TvledNo ratings yet

- YT8511 DemoDocument3 pagesYT8511 Demo周勇100% (1)

- Pluse Charger BB Power: 25V RatingDocument12 pagesPluse Charger BB Power: 25V RatingROSELA LABSNo ratings yet

- BNT 400a500a600aDocument1 pageBNT 400a500a600aEmilio Kowalski100% (1)

- Sección 303-06F Sistema de Arranque - 2.2L Duratorq-Tdci (DW) DieselDocument5 pagesSección 303-06F Sistema de Arranque - 2.2L Duratorq-Tdci (DW) DieselAdolfo BelloNo ratings yet

- Samsung+DTV 981A+LE32 450+ (BN41-00982B) PDFDocument11 pagesSamsung+DTV 981A+LE32 450+ (BN41-00982B) PDFEveraldoNo ratings yet

- Half-Bridge Analog ControllerDocument1 pageHalf-Bridge Analog Controllersami karadağNo ratings yet

- 206-09B-Anti-Lock Control - Stability Assist 206-09BDocument6 pages206-09B-Anti-Lock Control - Stability Assist 206-09BCARLOS BELTRÁNNo ratings yet

- Polytron 1415n7 t15n7r bm6 HBM 00 07 SCHDocument2 pagesPolytron 1415n7 t15n7r bm6 HBM 00 07 SCHIrwantoirwanNo ratings yet

- SECCIÓN 303-06B Sistema de Arranque - 2.5L Duratec-ST (VI5) : Página ContenidoDocument3 pagesSECCIÓN 303-06B Sistema de Arranque - 2.5L Duratec-ST (VI5) : Página ContenidoAdolfo BelloNo ratings yet

- Cat - 797 Truck and Starting Aid Electrical CircuitsDocument2 pagesCat - 797 Truck and Starting Aid Electrical CircuitsneftalicastroNo ratings yet

- Schematic Ktc-Cbu 24 VCMDocument4 pagesSchematic Ktc-Cbu 24 VCMMarco Kersul100% (1)

- CNC-satshakit CNC 20mhz BRDDocument1 pageCNC-satshakit CNC 20mhz BRDTomi OzzyNo ratings yet

- Engine Data Sensors - Oxygen Sensors, Throttle Actuator Controls, and Ignition SystemDocument1 pageEngine Data Sensors - Oxygen Sensors, Throttle Actuator Controls, and Ignition SystemDavid MVNo ratings yet

- Sección 303-06D Sistema de Arranque - 2.0L Duratorq-Tdci (DW) DieselDocument5 pagesSección 303-06D Sistema de Arranque - 2.0L Duratorq-Tdci (DW) DieselAdolfo BelloNo ratings yet

- FoglampsDocument2 pagesFoglampscontato mecanicadalazemNo ratings yet

- Schematic - S-60-12 - 12 5ADocument1 pageSchematic - S-60-12 - 12 5Avolovin.vNo ratings yet

- Schematic FL5150 Wifi Dimmer 2022-01-04Document1 pageSchematic FL5150 Wifi Dimmer 2022-01-04Naveen.R - SonetonixNo ratings yet

- Schematic GPS Module 2022-12-14Document1 pageSchematic GPS Module 2022-12-14samsularief03No ratings yet

- Philips 715g5821 m01 000 004i Meridian 5 Chassis SCHDocument8 pagesPhilips 715g5821 m01 000 004i Meridian 5 Chassis SCHRamkiNo ratings yet

- PCB DiagramDocument1 pagePCB Diagramtaz1mx0% (1)

- Ford Galaxy SMAXDocument14 pagesFord Galaxy SMAXAdolfo BelloNo ratings yet

- Planta de Oxido de EtilenoDocument1 pagePlanta de Oxido de EtilenoValve Anton V RNo ratings yet

- LE49F1461 Esquema - Placa-MainDocument18 pagesLE49F1461 Esquema - Placa-MainstkzNo ratings yet

- 206-09A-Anti-Lock Control 206-09ADocument8 pages206-09A-Anti-Lock Control 206-09ACARLOS BELTRÁNNo ratings yet

- Figure 1: Schematic - Power Section (1/2)Document6 pagesFigure 1: Schematic - Power Section (1/2)MARIA ALEXANDRA STOICANo ratings yet

- Schematics 622679Document2 pagesSchematics 622679sahim d'algerNo ratings yet

- Place Decoupling Capacitors Close To VDD Pins:: CC2541 Postage Stamp CC2541 Postage Stamp CC2541 Postage StampDocument2 pagesPlace Decoupling Capacitors Close To VDD Pins:: CC2541 Postage Stamp CC2541 Postage Stamp CC2541 Postage Stampraduseica100% (1)

- Mostly Harmless: Deklein DekleinDocument1 pageMostly Harmless: Deklein DekleinAlekShmitNo ratings yet

- Volterra Slave Options 2480087300G - VT242 - 10A RATED 2480087200G - VT243 - 15A RATEDDocument1 pageVolterra Slave Options 2480087300G - VT242 - 10A RATED 2480087200G - VT243 - 15A RATEDKrasimir MalamovNo ratings yet

- Fuel Controls - Fuel Injectors and EVAP ControlsDocument1 pageFuel Controls - Fuel Injectors and EVAP ControlsDavid MVNo ratings yet

- Schematic - TA2022 Class T - Sheet - 1 - 20200208194238Document1 pageSchematic - TA2022 Class T - Sheet - 1 - 20200208194238Mateusz MalecNo ratings yet

- LilyGo SIM800L IP5306 20200811Document3 pagesLilyGo SIM800L IP5306 20200811Bill Ordoñez EgoavilNo ratings yet

- Uart LDO 3.3VDocument2 pagesUart LDO 3.3VMas SamNo ratings yet

- USB LDO: Rst/En U0Txd U0Rxd U0Txd U0Rxd IO0Document3 pagesUSB LDO: Rst/En U0Txd U0Rxd U0Txd U0Rxd IO0Diego YabburNo ratings yet

- RP2040 ZeroDocument1 pageRP2040 ZeroLeonardo AnguloNo ratings yet

- BA115 SchematicDocument9 pagesBA115 SchematicAlan ShoreNo ratings yet

- Cat 980 Cat - Dcs.sis - ControllerDocument4 pagesCat 980 Cat - Dcs.sis - ControllerlubisNo ratings yet

- Tractor D3GDocument12 pagesTractor D3GCuba Juan CarlosNo ratings yet

- (Before Press Power Button) : Power Sequence and Architecture DiagramDocument1 page(Before Press Power Button) : Power Sequence and Architecture DiagramYoho Y.No ratings yet

- Pid303 Pid303: Piy101 Piy102 Piy102 Piy101Document2 pagesPid303 Pid303: Piy101 Piy102 Piy102 Piy101Thomas Yandex100% (2)

- Philips 8204 100 14014 (SCH)Document3 pagesPhilips 8204 100 14014 (SCH)scartthoNo ratings yet

- Schematic Pilomar Tiny2040 2023-02-03Document1 pageSchematic Pilomar Tiny2040 2023-02-03Ian ApplebyNo ratings yet

- qrv09 SchematicDocument12 pagesqrv09 SchematicTravis EstepNo ratings yet

- SECCIÓN 206-09A Control Antibloqueo: Página ContenidoDocument8 pagesSECCIÓN 206-09A Control Antibloqueo: Página ContenidoAdolfo BelloNo ratings yet

- PDFDocument34 pagesPDFDental LabNo ratings yet

- Main Types of ThinFlex Materials For Flex BoardDocument4 pagesMain Types of ThinFlex Materials For Flex BoardjackNo ratings yet

- 2011 - Powering Autonomous Sensors - PenellaDocument155 pages2011 - Powering Autonomous Sensors - PenellafergusoniseNo ratings yet

- York VRF Odu - Jvor (080-540) - Service Manual - 1778 201604Document231 pagesYork VRF Odu - Jvor (080-540) - Service Manual - 1778 201604SIDNEY DA CUNHA NEVES88% (8)

- Interfacing DEIF Equipment, Application Notes 4189340670 UK - 2013.10.04Document49 pagesInterfacing DEIF Equipment, Application Notes 4189340670 UK - 2013.10.04Luis Jesus50% (2)

- 144-Cell: Framed 144 Half-Cell ModuleDocument2 pages144-Cell: Framed 144 Half-Cell ModuleJuan CamargoNo ratings yet

- Keysight - First Steps in 5G PDFDocument9 pagesKeysight - First Steps in 5G PDFpravin.netalkar2353No ratings yet

- Power Supplies TutorialDocument9 pagesPower Supplies TutorialBarry Bj ShaideNo ratings yet

- Emu4 Modbus MapaDocument81 pagesEmu4 Modbus MapaAlberto Suazo BasaezNo ratings yet

- Service Manual: TV-FT2588Document21 pagesService Manual: TV-FT2588André LeftNo ratings yet

- ClincherDocument5 pagesClinchersoegi_1983No ratings yet

- MCQ-MW PlanningDocument2 pagesMCQ-MW PlanningMohamed Saber MokdafNo ratings yet

- FM 357-2 Positioning Module: FunctionDocument7 pagesFM 357-2 Positioning Module: FunctionAli AbdullahNo ratings yet

- Consolidated DataDocument28 pagesConsolidated Datavenkatesh_1829No ratings yet

- You Can DIY! The F5 Power Amplifier: First WattDocument19 pagesYou Can DIY! The F5 Power Amplifier: First WattagmNo ratings yet

- Viking RAD 1ADocument8 pagesViking RAD 1Abestbest07No ratings yet

- Fundamentals of Physics, 8th Edition Halliday, Resnick, WalkerDocument5 pagesFundamentals of Physics, 8th Edition Halliday, Resnick, Walkerabhishekkumar1996No ratings yet

- Neca200 10 PDocument30 pagesNeca200 10 Pcharlesc5746No ratings yet

- DV06PUB4 Study GuideDocument5 pagesDV06PUB4 Study GuideSavio FernandesNo ratings yet

- Data and Computer Communication Exam IDocument5 pagesData and Computer Communication Exam ISuper RageNo ratings yet

- AC Motor Single PhaseDocument14 pagesAC Motor Single PhaseMohamed HAMDYNo ratings yet

- LS800 eDocument124 pagesLS800 eNguyễn Bá ThịnhNo ratings yet

- Section - : Exit To Main MenuDocument180 pagesSection - : Exit To Main Menuadi100% (2)

- HovermaniaDocument4 pagesHovermaniamecharena2k13No ratings yet

- SWM VHF PDFDocument6 pagesSWM VHF PDFshubhraenergyNo ratings yet

- Spu 1253Document1 pageSpu 1253Josemir MarquesNo ratings yet

- MEC-1 Earth Continuity RelayDocument2 pagesMEC-1 Earth Continuity RelayAkashNo ratings yet

- Wj15edgkm-3 53 81Document3 pagesWj15edgkm-3 53 81Bahman Tamandehroo AkhalghiNo ratings yet

- Re - 1982-11Document140 pagesRe - 1982-11Anonymous kdqf49qbNo ratings yet

- Cisco TelePresence PrecisionHD 1080p-720p Camera GuideDocument1 pageCisco TelePresence PrecisionHD 1080p-720p Camera GuideGonzalo DiazNo ratings yet