0% found this document useful (0 votes)

157 views4 pagesCMOS NAND Gate Design

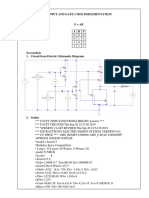

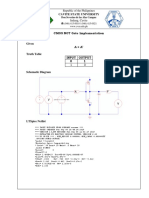

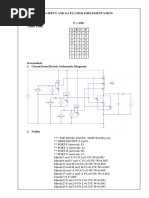

The document describes a 2-input NAND gate implemented in CMOS technology. It provides the truth table and shows that the output is low when both inputs are high and high for all other input combinations. It includes the circuit schematic from Electric and the SPICE netlist describing the NMOS and PMOS transistor models and connections to implement the 2-input NAND function.

Uploaded by

Kevin SimonsCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

157 views4 pagesCMOS NAND Gate Design

The document describes a 2-input NAND gate implemented in CMOS technology. It provides the truth table and shows that the output is low when both inputs are high and high for all other input combinations. It includes the circuit schematic from Electric and the SPICE netlist describing the NMOS and PMOS transistor models and connections to implement the 2-input NAND function.

Uploaded by

Kevin SimonsCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as DOCX, PDF, TXT or read online on Scribd