Professional Documents

Culture Documents

Cmos Inverter Best Short PDF

Cmos Inverter Best Short PDF

Uploaded by

naviOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cmos Inverter Best Short PDF

Cmos Inverter Best Short PDF

Uploaded by

naviCopyright:

Available Formats

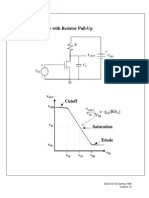

CMOS Inverter: DC Analysis

• Analyze DC Characteristics of CMOS Gates

by studying an Inverter

• DC Analysis

– DC value of a signal in static conditions

• DC Analysis of CMOS Inverter

– Vin, input voltage

– Vout, output voltage

– single power supply, VDD

– Ground reference

– find Vout = f(Vin)

• Voltage Transfer Characteristic (VTC)

– plot of Vout as a function of Vin

– vary Vin from 0 to VDD

– find Vout at each value of Vin

ECE 410, Prof. A. Mason Lecture Notes 7.1

Inverter Voltage Transfer Characteristics

• Output High Voltage, VOH

– maximum output voltage

• occurs when input is low (Vin = 0V)

• pMOS is ON, nMOS is OFF

• pMOS pulls Vout to VDD

– VOH = VDD

• Output Low Voltage, VOL

– minimum output voltage

• occurs when input is high (Vin = VDD)

• pMOS is OFF, nMOS is ON

• nMOS pulls Vout to Ground

– VOL = 0 V

• Logic Swing

– Max swing of output signal

• VL = VOH - VOL

• VL = VDD

ECE 410, Prof. A. Mason Lecture Notes 7.2

Inverter Voltage Transfer Characteristics

• Gate Voltage, f(Vin) •Drain Voltage, f(Vout)

– VGSn=Vin, VSGp=VDD-Vin –VDSn=Vout, VSDp=VDD-Vout

+

• Transition Region (between VOH and VOL) VSGp

– Vin low -

• Vin < Vtn +

– Mn in Cutoff, OFF VGSn

– Mp in Triode, Vout pulled to VDD

-

• Vin > Vtn < ~Vout

– Mn in Saturation, strong current

– Mp in Triode, VSG & current reducing

– Vout decreases via current through Mn

– Vin = Vout (mid point) ≈ ½ VDD

– Mn and Mp both in Saturation

– maximum current at Vin = Vout Vin < VIL

– Vin high input logic LOW

• Vin > ~Vout, Vin < VDD - |Vtp|

– Mn in Triode, Mp in Saturation Vin > VIH

• Vin > VDD - |Vtp|

input logic HIGH

– Mn in Triode, Mp in Cutoff

ECE 410, Prof. A. Mason Lecture Notes 7.3

Noise Margin

• Input Low Voltage, VIL

– Vin such that Vin < VIL = logic 0

– point ‘a’ on the plot

• where slope, ∂Vin

= −1

∂Vout

• Input High Voltage, VIH

– Vin such that Vin > VIH = logic 1

– point ‘b’ on the plot

• where slope =-1

• Voltage Noise Margins

– measure of how stable inputs are with respect to signal interference

– VNMH = VOH - VIH = VDD - VIH

– VNML = VIL - VOL = VIL

– desire large VNMH and VNML for best noise immunity

ECE 410, Prof. A. Mason Lecture Notes 7.4

Switching Threshold

• Switching threshold = point on VTC where Vout = Vin

– also called midpoint voltage, VM

– here, Vin = Vout = VM

• Calculating VM

– at VM, both nMOS and pMOS in Saturation

– in an inverter, IDn = IDp, always!

– solve equation for VM

μ nCOX W βn βp

I Dn = (VGSn − Vtn ) 2 = (VGSn − Vtn ) 2 = (VSGp − Vtp ) 2 = I Dp

2 L 2 2

– express in terms of VM

βn βp βn

(V − Vtn ) = VDD − VM − Vtp

2

(VM − Vtn ) 2 =

2

(VDD − VM − Vtp ) 2 ⇒ βp M

– solve for VM VDD − Vtp + Vtn

βn

βp

VM =

βn

1+

βp

ECE 410, Prof. A. Mason Lecture Notes 7.5

Effect of Transistor Size on VTC

• Recall ⎛W ⎞

k 'n ⎜ ⎟ VDD − Vtp + Vtn

βn

βn ⎝ L ⎠n βp

β n = k 'n

W = VM =

βp ⎛W ⎞ βn

L k'p ⎜ ⎟ 1+

⎝ L ⎠p βp

• If nMOS and pMOS are same size

– (W/L)n = (W/L)p ⎛W ⎞

μ nCoxn ⎜ ⎟

βn ⎝ L ⎠n μ n

– Coxn = Coxp (always) βp

=

⎛W ⎞

=

μp

≅ 2or 3

⎛W ⎞ μ pCoxp ⎜ ⎟

⎜ ⎟ ⎝ L ⎠p

μn ⎝ L ⎠ p β

• If =

μp ⎛W ⎞

, then n = 1

βp

since L normally min. size for all tx,

⎜ ⎟ can get betas equal by making Wp larger than Wn

⎝ L ⎠n

• Effect on switching threshold

– if βn ≈ βp and Vtn = |Vtp|, VM = VDD/2, exactly in the middle

• Effect on noise margin

– if βn ≈ βp, VIH and VIL both close to VM and noise margin is good

ECE 410, Prof. A. Mason Lecture Notes 7.6

Example

• Given

– k’n = 140uA/V2, Vtn = 0.7V, VDD = 3V

– k’p = 60uA/V2, Vtp = -0.7V

• Find

– a) tx size ratio so that VM= 1.5V

– b) VM if tx are same size

transition pushed lower

as beta ratio increases

ECE 410, Prof. A. Mason Lecture Notes 7.7

CMOS Inverter: Transient Analysis

• Analyze Transient Characteristics of

CMOS Gates by studying an Inverter

• Transient Analysis

– signal value as a function of time

• Transient Analysis of CMOS Inverter

– Vin(t), input voltage, function of time

– Vout(t), output voltage, function of time

– VDD and Ground, DC (not function of time)

– find Vout(t) = f(Vin(t))

• Transient Parameters

– output signal rise and fall time

– propagation delay

ECE 410, Prof. A. Mason Lecture Notes 7.8

Transient Response

• Response to step change in input

– delays in output due to parasitic R & C

• Inverter RC Model

– Resistances

– Rn = 1/[βn(VDD-Vtn)] +

– Rp = 1/[βn(VDD-|Vtp|)] Vout

– Output Cap. (only output is important) CL -

• CDn (nMOS drain capacitance)

– CDn = ½ Cox Wn L + Cj ADnbot + Cjsw PDnsw

• CDp (pMOS drain capacitance)

– CDp = ½ Cox Wp L + Cj ADpbot + Cjsw PDpsw

• Load capacitance, due to gates attached at the output

– CL = 3 Cin = 3 (CGn + CGp), 3 is a “typical” load

• Total Output Capacitance

– Cout = CDn + CDp + CL term “fan-out” describes

# gates attached at output

ECE 410, Prof. A. Mason Lecture Notes 7.9

Fall Time

• Fall Time, tf

– time for output to fall from ‘1’ to ‘0’

– derivation: ∂V V

i = −Cout out = out

∂t Rn

• initial condition, Vout(0) = VDD

• solution time constant

t −

Vout (t ) = VDD e τn

τn = RnCout

⎛V ⎞

t = τ n ln⎜ DD ⎟

⎝ Vout ⎠

– definition

• tf is time to fall from

90% value [V1,tx] to 10% value [V0,ty]

⎡ ⎛ V ⎞ ⎛ V ⎞⎤

t = τ n ⎢ln⎜⎜ DD ⎟⎟ − ln⎜⎜ DD ⎟⎟⎥

⎣ ⎝ 0.1VDD ⎠ ⎝ 0.9VDD ⎠⎦

• tf = 2.2 τn

ECE 410, Prof. A. Mason Lecture Notes 7.10

Rise Time

• Rise Time, tr

– time for output to rise from ‘0’ to ‘1’

– derivation: ∂Vout VDD − Vout

i = Cout =

∂t Rp

• initial condition, Vout(0) = 0V

• solution time constant

⎡ − t

τ ⎤

Vout (t ) = VDD ⎢1 − e p ⎥ τp = RpCout

⎣ ⎦

– definition

• tf is time to rise from

10% value [V0,tu] to 90% value [V1,tv]

• tr = 2.2 τp

• Maximum Signal Frequency

– fmax = 1/(tr + tf)

• faster than this and the output can’t settle

ECE 410, Prof. A. Mason Lecture Notes 7.11

Propagation Delay

• Propagation Delay, tp

– measures speed of output reaction to input change

– tp =½ (tpf + tpr)

• Fall propagation delay, tpf

– time for output to fall by 50%

• reference to input change by 50%

• Rise propagation delay, tpr

– time for output to rise by 50%

• reference to input change by 50%

• Ideal expression (if input is step change)

– tpf = ln(2) τn

Propagation delay measurement:

– tpr = ln(2) τp

- from time input reaches 50% value

• Total Propagation Delay - to time output reaches 50% value

– tp = 0.35(τn + τp)

Add rise and fall propagation delays for total value

ECE 410, Prof. A. Mason Lecture Notes 7.12

Switching Speed -Resistance

• Rise & Fall Time τn = RnCout τp = RpCout

– tf = 2.2 τn, tr = 2.2 τp,

• Propagation Delay Rn = 1/[βn(VDD-Vtn)] β= μCox (W/L)

– tp = 0.35(τn + τp) Rp = 1/[βp(VDD-|Vtp|)]

• In General

Cout = CDn + CDp + CL

– delay ∝ τn + τp

– τn + τp = Cout (Rn+Rp)

• Define delay in terms of Beta Matched if βn=βp=β,

design parameters Rn+Rp = 2 = 2L

– Rn+Rp = (VDD-Vt)(βn +βp) β (VDD-Vt) μCox W (VDD-Vt)

βn βp(VDD-Vt)2 Width Matched if Wn=Wp=W, and L=Ln=Lp

– Rn+Rp = βn + βp Rn+Rp = L (μn+ μp)

βn βp(VDD-Vt) (μn μp) Cox W (VDD-Vt)

• if Vt = Vtn = |Vtp| To decrease R’s, ⇓L, ⇑W, ⇑VDD, ( ⇑μp, ⇑Cox )

ECE 410, Prof. A. Mason Lecture Notes 7.13

Switching Speed -Capacitance

• From Resistance we have Cout = CDn + CDp + CL

– ⇓L, ⇑W, ⇑VDD, ( ⇑μp, ⇑Cox ) if L=Ln=Lp estimate

– but ⇑ VDD increases power CL = 3 (CGn + CGp) = 3 Cox (WnL+WpL)

– ⇑ W increases Cout CDn = ½ Cox Wn L + Cj ADnbot + Cjsw PDnsw

• Cout CDp = ½ Cox Wp L + Cj ADpbot + Cjsw PDpsw

– Cout = ½ Cox L (Wn+Wp) + Cj 2L

(Wn+Wp) + 3 Cox L (Wn+Wp) ~2L

• assuming junction area ~W•2L W

• neglecting sidewall capacitance

– Cout ≈ L (Wn+Wp) [3½ Cox +2 Cj] L

– Cout ∝ L (Wn+Wp)

To decrease Cout, ⇓L, ⇓W, (⇓Cj, ⇓Cox )

• Delay ∝ Cout(Rn+Rp) ∝ L W L = L2

W VDD VDD

Decreasing L (reducing feature size) is best way to improve speed!

ECE 410, Prof. A. Mason Lecture Notes 7.14

Switching Speed -Local Modification

• Previous analysis applies to the overall design

– shows that reducing feature size is critical for higher speed

– general result useful for creating cell libraries

• How do you improve speed within a specific gate?

– increasing W in one gate will not increase CG of the load gates

• Cout = CDn + CDp + CL

• increasing W in one logic gate will increase CDn/p but not CL

– CL depends on the size of the tx gates at the output

– as long as they keep minimum W, CL will be constant

– thus, increasing W is a good way to improve the speed within a

local point

– But, increasing W increases chip area needed, which is bad

• fast circuits need more chip area (chip “real estate”)

• Increasing VDD is not a good choice because it increases

power consumption

ECE 410, Prof. A. Mason Lecture Notes 7.15

CMOS Power Consumption

• P = PDC + Pdyn

– PDC: DC (static) term

– Pdyn: dynamic (signal changing) term

• PDC

– P = IDD VDD

• IDD DC current from power supply

• ideally, IDD = 0 in CMOS: ideally only current during switching action

• leakage currents cause IDD > 0, define quiescent leakage current,

IDDQ (due largely to leakage at substrate junctions)

– PDC = IDDQ VDD

• Pdyn, power required to switch the state of a gate

– charge transferred during transition, Qe = Cout VDD

– assume each gate must transfer this charge 1x/clock cycle

– Paverage = VDD Qe f = Cout VDD2 f, f = frequency of signal change

Power increases with Cout and

• Total Power, P = IDDQ VDD + Cout VDD2 f frequency, and strongly with

VDD (second order).

ECE 410, Prof. A. Mason Lecture Notes 7.16

Multi-Input Gate Signal Transitions

• In multi-input gates multiple signal transitions produce

output changes

• What signal transitions need to be analyzed?

– for a general N-input gate with M0 low output states and M1 high

output states

• # high-to-low output transitions = M0⋅M1

• # low-to-high output transitions = M1⋅M0

• total transitions to be characterized = 2⋅M0⋅M1

• example: NAND has M0 = 1, M1 = 3

– don’t test/characterize cases without output transitions

• Worst-case delay is the slowest of all possible cases

– worst-case high-to-low

– worst-case low-to-high

– often different input transitions for each of these cases

ECE 410, Prof. A. Mason Lecture Notes 7.17

Series/Parallel Equivalent Circuits

• Scale both W and L

– no effective change in W/L

– increases gate capacitance

β = μCox (W/L)

inputs must be at same value/voltage

• Series Transistors

– increases effective L

effective

β⇒½β

• Parallel Transistors

– increases effective W

effective

β ⇒ 2β

ECE 410, Prof. A. Mason Lecture Notes 7.18

NAND: DC Analysis

• Multiple Inputs

• Multiple Transitions

• Multiple VTCs

– VTC varies with transition

• transition from 0,0 to 1,1 pushed right of others

• why?

– VM varies with transition

• assume all tx have same L

• VM = VA = VB = Vout

– can merge transistors at this point

• if WpA=WpB and WnA=WnB

– series nMOS, βN ⇒ ½ βn

– parallel pMOS, βP ⇒ 2 βp

– can now calculate the NAND VM

ECE 410, Prof. A. Mason Lecture Notes 7.19

NAND Switching Point

• Calculate VM for NAND

– 0,0 to 1,1 transition

• all tx change states (on, off)

• in other transitions, only 2 change

– VM = VA = VB = Vout

– set IDn = IDp, solve for VM

series nMOS means

1 βn

VDD − Vtp + Vtn more resistance to

2 βp

VM = output falling,

1 βn

1+

2 βp shifts VTC to right

– denominator reduced more

• VTC shifts right to balance this effect

and set VM to VDD/2,

• For NAND with N inputs can increase β by

1 βn increasing Wn

VDD − Vtp + Vtn

N βp

VM = but, since μn>μp, VM≈VDD/2

1 βn

1+ when Wn = Wp

N βp

ECE 410, Prof. A. Mason Lecture Notes 7.20

NOR: DC Analysis

• Similar Analysis to NAND

• Critical Transition

– 0,0 to 1,1

– when all transistors change

• VM for NOR2 critical transition

– if WpA=WpB and WnA=WnB

• parallel nMOS, βn ⇒ 2 βn

• series pMOS, βp ⇒ ½ βp

βn βn

VDD − Vtp + 2Vtn VDD − Vtp + NVtn

βp βp

VM = VM =

β βn

1+ 2 n 1+ N

βp βp

for NOR2 for NOR-N

– series pMOS resistance means slower rise

– VTC shifted to the left

– to set VM to VDD/2, increase Wp

• this will increase βp

ECE 410, Prof. A. Mason Lecture Notes 7.21

NAND: Transient Analysis

• NAND RC Circuit

– R: standard channel resistance

– C: Cout = CL + CDn + 2CDp

• Rise Time, tr

– Worst case charge circuit

• 1 pMOS ON

– tr = 2.2 τp

• τp = Rp Cout

– best case charge circuit

• 2 pMOS ON, Rp ⇒ Rp/2

• Fall Time, tf

– Discharge Circuit

• 2 series nMOS, Rn ⇒ 2Rn

• must account for internal cap, Cx

– tf = 2.2 τn

Cx = CSn + CDn

• τn = Cout (2 Rn ) + Cx Rn

ECE 410, Prof. A. Mason Lecture Notes 7.22

NOR: Transient Analysis

• NOR RC Circuit

– R: standard channel resistance

– C: Cout = CL + 2CDn + CDp

• Fall Time, tf

– Worst case discharge circuit

• 1 nMOS ON

– tf = 2.2 τn

• τn = Rn Cout

– best case discharge circuit

• 2 nMOS ON, Rn ⇒ Rn/2

• Rise Time, tr

– Charge Circuit

• 2 series pMOS, Rp ⇒ 2Rp Cy = CSp + CDp

• must account for internal cap, Cy

– tr = 2.2 τp

• τp = Cout (2 Rp ) + Cy Rp

ECE 410, Prof. A. Mason Lecture Notes 7.23

NAND/NOR Performance

• Inverter: symmetry (VM=VDD/2), βn = βp

– (W/L)p = μn/μp (W/L)n

• Match INV performance with NAND

β is adjusted by

– pMOS, βP = βp, same as inverter changing transistor

– nMOS, βN = 2βn, to balance for 2 series nMOS size (width)

• Match INV performance with NOR

– pMOS, βP = 2 βp, to balance for 2 series pMOS

– nMOS, βN = βn, same as inverter

• NAND and NOR will still

be slower due to larger Cout

• This can be extended to

3, 4, … N input NAND/NOR

gates

ECE 410, Prof. A. Mason Lecture Notes 7.24

NAND/NOR Transient Summary

• Critical Delay Path

– paths through series transistors will be slower

– more series transistors means worse delays

• Tx Sizing Considerations

– increase W in series transistors

– balance βn/βp for each cell

• Worst Case Transition

– when all series transistor go from OFF to ON

– and all internal caps have to be

• charged (NOR)

• discharged (NAND)

ECE 410, Prof. A. Mason Lecture Notes 7.25

Performance Considerations

• Speed based on βn, βp and parasitic caps

• DC performance (VM, noise) based on βn/βp

• Design for speed not necessarily provide good DC

performance

• Generally set tx size to optimize speed and then test DC

characteristics to ensure adequate noise immunity

• Review Inverter: Our performance reference point

– for symmetry (VM=VDD/2), βn = βp

• which requires (W/L)p = μn/μp (W/L)n

• Use inverter as reference point for more complex gates

• Apply slowest arriving inputs to series node closest to

output slower

output

– let faster signals begin to charge/discharge signal

nodes closer to VDD and Ground faster

signal power supply

ECE 410, Prof. A. Mason Lecture Notes 7.26

Timing in Complex Logic Gates

• Critical delay path is due to series-connected transistors

• Example: f = x (y+z)

– assume all tx are same size

• Fall time critical delay

– worst case, x ON, and y or z ON

– tf = 2.2 τn

• τn = Rn Cn + 2 Rn Cout

– Cout = 2CDp + CDn + CL

– Cn = 2CDn + CSn

• Rise time critical delay

size vs. tx speed considerations

– worst case, y and z ON, x OFF

⇑Wnx ⇒ ⇓Rn but ⇑Cout and ⇑Cn

– tr = 2.2 τp ⇓Wny ⇒ ⇓Cn but ⇑Rn

• τp = Rp Cp + 2 Rp Cout

– Cout = 2CDp + CDn + CL ⇑Wpz ⇒ ⇓Rp but ⇑Cout and ⇑Cp

– Cp = CDp + CSp ⇓Wpx ⇒ no effect on critical path

ECE 410, Prof. A. Mason Lecture Notes 7.27

Sizing in Complex Logic Gates

• Improving speed within a single logic gate

• An Example: f=(a b+c d) x

• nMOS

– discharge through 3 series nMOS

– set βN = 3βn

• pMOS

– charge through 2 series pMOS

– set βP = 2βp

– but, Mp-x is alone so βP1 = βp

• but setting βP1 = 2βp might make layout easier

• These large transistors will increase capacitance and

layout area and may only give a small increase in speed

• Advanced logic structures are best way to improve speed

ECE 410, Prof. A. Mason Lecture Notes 7.28

Timing in Multi-Gate Circuits

• What is the worst-case delay in multi-gate circuits?

A AB CD F

B F

C↑

0 0 0 0 0

C

D

0 0 0 1 0 C ↑D ↓

0 0 1 0 1

– too many transitions to test manually 1 0 0 0 0 B↑

• Critical Path 1 1 0 0 1

– longest delay through a circuit block 1 1 1 1 1

– largest sum of delays, from input to output

– intuitive analysis: signal that passes through most gates

• not always true. can be slower path through fewer gates

A

B F path through most gates

C

D critical path if delay due to

D input is very slow

ECE 410, Prof. A. Mason Lecture Notes 7.29

Power in Multi-Input Logic Gates

• Inverter Power Consumption

– P = PDC + Pdyn = VDDIDDQ + CoutV2DDf

• assumes gates switches output state once per clock cycle, f

• Multi-Input Gates

– same DC component as inverter, PDC = VDDIDDQ

– for dynamic power, need to estimate “activity” of the

gate, how often will the output be switching

– Pdyn = aCoutV2DDf, a = activity coefficient NOR NAND

– estimate activity from truth table

• a = p0p1

– p0 = prob. output is at 0

– p1 = prob. of transition to 1 p0=0.75 p0=0.25

p1=0.25 p1=0.75

a=3/16 a=3/16

ECE 410, Prof. A. Mason Lecture Notes 7.30

Timing Analysis of Transmission Gates

• TG = parallel nMOS and pMOS

• RC Model

– in general, only one tx active at same time

• nMOS pulls output low

• pMOS pushes output high

– RTG = max (Rn, Rp)

– Cin = CSn + CDp

• if output at higher voltage than input

– larger W will decrease R but increase Cin

• Note: no connections to VDD-Ground. Input signal, Vin,

must drive TG output; TG just adds extra delay

ECE 410, Prof. A. Mason Lecture Notes 7.31

Pass Transistor

• Single nMOS or pMOS tx

• Often used in place of TGs

– less area and wiring

– can’t pull to both VDD and Ground

– typically use nMOS for better speed

• Rise and Fall Times Φ=1

y ID

– τn = Rn Cout time x=0 y=1 ⇒ 0

– tf = 2.94 τn Φ=1

y ID

– tr = 18 τn time

• much slower than fall time x=1 y=0 ⇒ 1

• nMOS can’t pull output to VDD

– rise time suffers from threshold loss in nMOS

ECE 410, Prof. A. Mason Lecture Notes 7.32

You might also like

- Current Mirror CadenceDocument80 pagesCurrent Mirror Cadencejuni khisha100% (2)

- Digital Transistor and Logic Gates IoT - Attempt ReviewDocument6 pagesDigital Transistor and Logic Gates IoT - Attempt ReviewaurelliaNo ratings yet

- Lecture 12 SRAMDocument37 pagesLecture 12 SRAMSachin MalikNo ratings yet

- Cmos Inverter CharacteristicsDocument5 pagesCmos Inverter CharacteristicsRichu Jose CyriacNo ratings yet

- Science of InformationDocument362 pagesScience of InformationChristian Chagas100% (3)

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- CMOS InverterDocument97 pagesCMOS Invertercnt2ssk100% (8)

- CMOS BasicsDocument41 pagesCMOS BasicsYeshoda MallikarjunaNo ratings yet

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Document34 pagesDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaNo ratings yet

- PROJECT1 S 2013 v2 PDFDocument4 pagesPROJECT1 S 2013 v2 PDFHarshal SinghNo ratings yet

- Bandgap 2009Document27 pagesBandgap 2009jjloksNo ratings yet

- 2016 Ch2-MOS TransistorsDocument47 pages2016 Ch2-MOS Transistorsជើងកាង ភូមិ100% (1)

- Bias Circuits For RF DevicesDocument20 pagesBias Circuits For RF Devicesmaheshsamanapally100% (1)

- Full-Wave RectifierDocument7 pagesFull-Wave Rectifiermohdshujaat100% (2)

- VLSI I - V CharacteristicsDocument46 pagesVLSI I - V CharacteristicsMALATHI .LNo ratings yet

- Cadence - Virtuoso: Amity UniversityDocument27 pagesCadence - Virtuoso: Amity UniversityAkhil Aggarwal100% (1)

- IC Design 3 - Basic MOS Device PhysicsDocument59 pagesIC Design 3 - Basic MOS Device PhysicsNana Sarkodie KwakyeNo ratings yet

- D Mosfet PDFDocument39 pagesD Mosfet PDFvanithapremkumarNo ratings yet

- Z TansformDocument65 pagesZ TansformThe Aviator00No ratings yet

- Two Stage CMOS Op Amp - Seid PDFDocument79 pagesTwo Stage CMOS Op Amp - Seid PDFTayachew BerhanNo ratings yet

- Unit 2 - CMOS Logic, Fabrication and LayoutDocument34 pagesUnit 2 - CMOS Logic, Fabrication and LayoutphillipNo ratings yet

- Digital To Analog Converter PDFDocument20 pagesDigital To Analog Converter PDFoman13905No ratings yet

- SEL 4283 Analog CMOS IC Design Single Stage Amplifiers: Small Signal Model 1Document52 pagesSEL 4283 Analog CMOS IC Design Single Stage Amplifiers: Small Signal Model 1jitendraNo ratings yet

- Lecture 3 Single Stage AmplifiersDocument76 pagesLecture 3 Single Stage Amplifierstranhieu_hcmutNo ratings yet

- Cmos Design Rules Layout PDFDocument33 pagesCmos Design Rules Layout PDFkrishnaavNo ratings yet

- Analog-To-Digital Conversion Btech IIIDocument50 pagesAnalog-To-Digital Conversion Btech IIILisa BhagatNo ratings yet

- Lec3 Single StageDocument24 pagesLec3 Single Stagerajeevjain09No ratings yet

- Two-Stage CMOS Op-Amp Circuit Design - Jianfeng SunDocument17 pagesTwo-Stage CMOS Op-Amp Circuit Design - Jianfeng Sunjianfeng sun100% (2)

- Analog Mosfet - Large Signal and Small Signal AnalysisDocument26 pagesAnalog Mosfet - Large Signal and Small Signal AnalysisAnil Kumar YernintiNo ratings yet

- Mos Transistor TheoryDocument144 pagesMos Transistor TheorymailtolokiNo ratings yet

- Digital To Analog ConvertersDocument39 pagesDigital To Analog ConvertersMANOJ MNo ratings yet

- MOSFETDocument13 pagesMOSFETMarkCabalunaNo ratings yet

- Cmos Inverter CharacteristicsDocument8 pagesCmos Inverter CharacteristicsShambhavi SonuNo ratings yet

- Ec8353electronicdevicesandcircuitsunit2 180711152109Document126 pagesEc8353electronicdevicesandcircuitsunit2 180711152109dhivyaNo ratings yet

- Two Stage Op-AmpDocument4 pagesTwo Stage Op-AmpShreerama Samartha G BhattaNo ratings yet

- Analog To Digital ConverterDocument41 pagesAnalog To Digital Converterkhushbubansal100% (1)

- Why VLSI? - Moore's Law. - The VLSI Design ProcessDocument28 pagesWhy VLSI? - Moore's Law. - The VLSI Design Processlim hyNo ratings yet

- Lecture4 Partition2Document51 pagesLecture4 Partition2api-3834272No ratings yet

- Dcs Lab ManualDocument33 pagesDcs Lab ManualKumaran SgNo ratings yet

- VLSI Ch4 DelayDocument27 pagesVLSI Ch4 Delayជើងកាង ភូមិNo ratings yet

- Tutorial On Layout of Mixed-Signal CircuitsDocument29 pagesTutorial On Layout of Mixed-Signal CircuitsPetru NistorNo ratings yet

- 9085 CMOS Analog Design Chapter 5Document25 pages9085 CMOS Analog Design Chapter 5istlyyNo ratings yet

- MosfetDocument15 pagesMosfetAnkita BanerjeeNo ratings yet

- Enee359a Sizing PDFDocument47 pagesEnee359a Sizing PDFRakesh SahuNo ratings yet

- Common Source AmplifierDocument4 pagesCommon Source AmplifierShoumik DeyNo ratings yet

- CMOS Inverter Design Using CadenceDocument3 pagesCMOS Inverter Design Using CadenceVikas YerramNo ratings yet

- Band Gap ReferencesDocument115 pagesBand Gap ReferencesNam Luu Nguyen NhatNo ratings yet

- CMOS CM & Biasing CircuitsDocument50 pagesCMOS CM & Biasing Circuitsabhi_jNo ratings yet

- Switch CapacitorDocument90 pagesSwitch CapacitorVaibhav Khurana100% (1)

- Folded Cascode ChopperDocument4 pagesFolded Cascode ChoppergirishknathNo ratings yet

- Analog Layout UTLDocument3 pagesAnalog Layout UTLDr. Sampatrao L PinjareNo ratings yet

- PMOS, NMOS and CMOS Transmission Gate Characteristics.Document13 pagesPMOS, NMOS and CMOS Transmission Gate Characteristics.Prajwal KhairnarNo ratings yet

- Design Procedure For Fully Differential Folded Cascode OTADocument4 pagesDesign Procedure For Fully Differential Folded Cascode OTAwleaderheeNo ratings yet

- CMOS IntroDocument45 pagesCMOS IntroNishanth Nish0% (1)

- Digital Signal Processing NotesDocument12 pagesDigital Signal Processing NotesDanial ZamanNo ratings yet

- OTA DesignDocument18 pagesOTA DesignAnandNo ratings yet

- Lecture 7 - CMOS DC - Transient ResponseDocument40 pagesLecture 7 - CMOS DC - Transient Responsesadia santaNo ratings yet

- S98 Lecture12Document11 pagesS98 Lecture12manohar487No ratings yet

- Inverter DynamicsDocument86 pagesInverter DynamicsRajesh MahadevNo ratings yet

- Simplified CMOS Voltage Transfer Curve Step 1. Finding V: M M IN MDocument6 pagesSimplified CMOS Voltage Transfer Curve Step 1. Finding V: M M IN MSeizalal SingsonNo ratings yet

- Chapter5 Industrial InverterDocument54 pagesChapter5 Industrial InverterTruong NguyenNo ratings yet

- Dynamic Logic CircuitsDocument38 pagesDynamic Logic Circuitssreekanthreddy peramNo ratings yet

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Document34 pagesDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaNo ratings yet

- Dynamic Logic Circuits: A. MarzukiDocument25 pagesDynamic Logic Circuits: A. Marzukisreekanthreddy peramNo ratings yet

- Electronics Ch14Document22 pagesElectronics Ch14Denise NelsonNo ratings yet

- Dynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)Document29 pagesDynamic Combinational Circuits: - Dynamic Circuits - Domino Logic - np-CMOS (Zipper CMOS)vardhanNo ratings yet

- Cmos InverterDocument92 pagesCmos Invertersreekanthreddy peramNo ratings yet

- CMOS InverterDocument16 pagesCMOS Invertersreekanthreddy peramNo ratings yet

- Digital Logic CircuitsDocument20 pagesDigital Logic Circuitssreekanthreddy peramNo ratings yet

- 9 YeungDocument19 pages9 YeungNathan PittmanNo ratings yet

- Dimensional Analysis A A SoninDocument57 pagesDimensional Analysis A A SoninJeff WebbNo ratings yet

- Std11 Bot EM 1Document236 pagesStd11 Bot EM 1Irshad Ali100% (1)

- Grazers and Browsers: How Digestive Morphology Affects Diet Selection Lisa A. ShipleyDocument8 pagesGrazers and Browsers: How Digestive Morphology Affects Diet Selection Lisa A. Shipleysreekanthreddy peramNo ratings yet

- Morphology of The Pteridophytes SporneDocument200 pagesMorphology of The Pteridophytes Spornesreekanthreddy peram100% (1)

- Physical Quantities Handout.........Document5 pagesPhysical Quantities Handout.........sreekanthreddy peramNo ratings yet

- Behaviour of OFDM System Using MATLAB SimulationDocument5 pagesBehaviour of OFDM System Using MATLAB Simulationsreekanthreddy peramNo ratings yet

- OFDM SIMULATION in MATLAB PDFDocument59 pagesOFDM SIMULATION in MATLAB PDFaasmabaka100% (2)

- All About Fundamental Physical QuantitiesDocument18 pagesAll About Fundamental Physical Quantitiessreekanthreddy peramNo ratings yet

- A Survey On Digital Modulation Techniques For Software Defined Radio ApplicationsDocument8 pagesA Survey On Digital Modulation Techniques For Software Defined Radio Applicationssreekanthreddy peramNo ratings yet

- FPGA Implementation of MIMO System Using Xilinx System Generator For Efficient Hardware/ Software Co-DesignDocument9 pagesFPGA Implementation of MIMO System Using Xilinx System Generator For Efficient Hardware/ Software Co-Designsreekanthreddy peramNo ratings yet

- Alstom Differential Protection RelayDocument8 pagesAlstom Differential Protection RelayNirmal KumarNo ratings yet

- DTSC-200: Automatic Transfer Switch ControllerDocument4 pagesDTSC-200: Automatic Transfer Switch ControllerJoemark YangagNo ratings yet

- SN74LVC2G14 Dual Schmitt-Trigger InverterDocument25 pagesSN74LVC2G14 Dual Schmitt-Trigger InverterhogaoftNo ratings yet

- VLSI Design Module - 5Document30 pagesVLSI Design Module - 5PavitraNo ratings yet

- Digital System DesignDocument2 pagesDigital System DesignMiguel Angel Tambo MoralesNo ratings yet

- Priti Kadam CGR ProjectDocument16 pagesPriti Kadam CGR Projectakash thoratNo ratings yet

- Intro To Digital Logic Labs v02 PDFDocument35 pagesIntro To Digital Logic Labs v02 PDFairbuk doeingNo ratings yet

- Phsical Design Automation of FpgasDocument18 pagesPhsical Design Automation of FpgasNitesh YadavNo ratings yet

- A Survey On Fault Injection Methods of Digital Integrated Circuits 2020Document10 pagesA Survey On Fault Injection Methods of Digital Integrated Circuits 2020Yohannes B. BekeleNo ratings yet

- PLC Question Level #1Document7 pagesPLC Question Level #1TinhNguyenNo ratings yet

- E1 - Digital Logic GatesDocument5 pagesE1 - Digital Logic GatesNEIL NADANo ratings yet

- 1MRK504019-BEN A en Transformer Protection Terminal RET 521-C2 2.3Document23 pages1MRK504019-BEN A en Transformer Protection Terminal RET 521-C2 2.3Robert MihayoNo ratings yet

- Women'S Polytechnic College-Karaikalmedu-Karaikal-609 605 Department of Electronics and Communication EngineeringDocument16 pagesWomen'S Polytechnic College-Karaikalmedu-Karaikal-609 605 Department of Electronics and Communication EngineeringRaja BalanNo ratings yet

- Digital Logic Design NotesDocument58 pagesDigital Logic Design NotesPrem VinodhNo ratings yet

- S7-300 PLC in RTGDocument72 pagesS7-300 PLC in RTGmunawar munawarNo ratings yet

- FpgaDocument99 pagesFpgaBABU MNo ratings yet

- Pilz Pnoz - User ManualDocument26 pagesPilz Pnoz - User ManualWellington MatosNo ratings yet

- Activity 3: The or Gate Objective:: A B (A) Y A+BDocument3 pagesActivity 3: The or Gate Objective:: A B (A) Y A+BChristian Allan LumakinNo ratings yet

- Delay Calculation (IMP)Document28 pagesDelay Calculation (IMP)Amarnath Reddy100% (1)

- 6N137 OptocouplerDocument14 pages6N137 OptocouplerAhmad SubkhanNo ratings yet

- Megger Relay Test System: SMRT410Document12 pagesMegger Relay Test System: SMRT410Aemco Persada NusantaraNo ratings yet

- Combinational Logic CircuitsDocument32 pagesCombinational Logic CircuitsShaikh Arham AyazNo ratings yet

- Computer System Architecture: (Third Edition)Document40 pagesComputer System Architecture: (Third Edition)Saravanan KumarNo ratings yet

- Digital Electronics Lab-3Document150 pagesDigital Electronics Lab-3hajera.mubeen2006No ratings yet

- CS203 Switching Theory and Logic Design PDFDocument3 pagesCS203 Switching Theory and Logic Design PDFsivaramkumarNo ratings yet

- W 2019 DSD GtuDocument2 pagesW 2019 DSD GtuSandeep kumarNo ratings yet

- Dual Power MOSFET Driver Features: File Number Data Sheet April 1999Document8 pagesDual Power MOSFET Driver Features: File Number Data Sheet April 1999tommyhghNo ratings yet

- BSC Computer Science PDFDocument56 pagesBSC Computer Science PDFB.ArulNo ratings yet