Professional Documents

Culture Documents

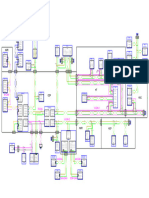

Neso HDMI VGA Framebuffer Block Diagram Rotated

Neso HDMI VGA Framebuffer Block Diagram Rotated

Uploaded by

Jesus SalvadorOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Neso HDMI VGA Framebuffer Block Diagram Rotated

Neso HDMI VGA Framebuffer Block Diagram Rotated

Uploaded by

Jesus SalvadorCopyright:

Available Formats

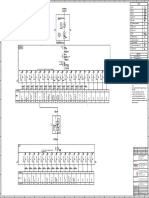

microblaze_subsystem

microblaze_0_axi_periph

S00_AXI

S01_AXI

S01_AXI

ACLK

ARESETN

S00_ACLK

S00_ARESETN

M00_ACLK M00_AXI mig_7series_0

M00_ARESETN M01_AXI ddr3_sdram

DDR3 ddr3_sdram

M01_ACLK M02_AXI S_AXI

ui_clk_sync_rst

M01_ARESETN M03_AXI sys_rst

ui_clk

M02_ACLK sys_clk_i

mmcm_locked

rst_mig_7series_0_100M M02_ARESETN aresetn

init_calib_complete

M03_ACLK

slowest_sync_clk mb_reset

M03_ARESETN Memory Interface Generator (MIG 7 Series)

ext_reset_in bus_struct_reset[0:0] usb_uart

S01_ACLK usb_uart

aux_reset_in peripheral_reset[0:0] M03_AXI

S01_ARESETN

mb_debug_sys_rst interconnect_aresetn[0:0]

axi_uartlite_0

dcm_locked peripheral_aresetn[0:0]

AXI Interconnect

S_AXI

Processor System Reset UART

s_axi_aclk

interrupt

s_axi_aresetn

microblaze_0 microblaze_0_local_memory AXI Uartlite

mdm_1 s_axi_aresetn[0:0]

INTERRUPT

DLMB DLMB

rst_clk_wiz_0_100M MBDEBUG_0 DEBUG

ILMB ILMB

Debug_SYS_Rst Clk

slowest_sync_clk mb_reset M_AXI_DP LMB_Clk

reset Reset

ext_reset_in bus_struct_reset[0:0] MicroBlaze Debug Module (MDM) SYS_Rst

sys_clk_i MicroBlaze

aux_reset_in peripheral_reset[0:0]

Clk

mb_debug_sys_rst interconnect_aresetn[0:0]

dcm_locked

dcm_locked peripheral_aresetn[0:0]

Processor System Reset

microblaze_0_axi_intc

s_axi

microblaze_0_xlconcat s_axi_aclk

In0[0:0] s_axi_aresetn

In0[0:0] interrupt

dout[1:0] intr[1:0]

reset In1[0:0]

processor_clk

clk_wiz_0 Concat processor_rst

clk100

AXI Interrupt Controller

clk200

resetn clk40

sys_clock clk_in1 clk_pix_5x

clk_pix_5x_180

locked vsync

video_subsystem

Clocking Wizard vga_decimate_0

axi_vdma_0

red[2:0] red[2:0]

S_AXI_LITE active

S_AXI_LITE M_AXI_MM2S green[2:0] green[2:0]

M_AXI_MM2S din[23:0]

s_axi_lite_aclk blue[1:0] blue[1:0]

M_AXIS_MM2S

m_axi_mm2s_aclk

clk mm2s_frame_ptr_out[5:0] vga_decimate_v1_0

m_axis_mm2s_aclk

mm2s_introut hsync

axi_resetn

hdmi_subsystem

AXI Video Direct Memory Access

dvi_top_0

proc_sys_reset_0 clk_pix_1x

clk_pix_1x

clk_pix_5x

slowest_sync_clk mb_reset clk_pix_5x

reset clk_pix_5x_180

ext_reset_in bus_struct_reset[0:0] clk_pix_5x_180

aux_reset_in peripheral_reset[0:0] rst

util_vector_logic_0

mb_debug_sys_rst interconnect_aresetn[0:0] red[7:0] tmds[3:0]

dcm_locked tmds[3:0] tmds[3:0]

dcm_locked peripheral_aresetn[0:0] de[0:0] blue[7:0] tmdsb[3:0]

m_axi_mm2s_aclk Op1[0:0] Res[0:0] tmdsb[3:0] tmdsb[3:0]

green[7:0]

axi_resetn

Processor System Reset v_axi4s_vid_out_0 vid_active_video

de

Utility Vector Logic

vsync

v_tc_0 vid_io_out blank

hsync hsync

vid_active_video hsync

clk video_in vid_data[23:0] vsync

vid_data[23:0] vsync

clken vtiming_out vtiming_in mm2s_introut

vid_hsync blue8

gen_clken fsync_out[0:0] aclk peripheral_reset[0:0]

dvi_top_v1_0

vid_vsync din[23:0]

resetn aclken Din[23:0] Dout[7:0]

vtg_ce

aresetn

Video Timing Controller locked Slice

fid

overflow

vid_io_out_ce red8

underflow

constant_1 status[31:0] Din[23:0] Dout[7:0]

dout[0:0] AXI4-Stream to Video Out Slice

Constant green8

Din[23:0] Dout[7:0]

Slice

rst

You might also like

- G2 MG Z1B.190RDocument13 pagesG2 MG Z1B.190RTavi DumitrescuNo ratings yet

- P-0004-Ph01-D01-01e001-Mrc-Sdr-Str-100011 - 4-6Document1 pageP-0004-Ph01-D01-01e001-Mrc-Sdr-Str-100011 - 4-6yasirjurabaNo ratings yet

- Sony - 1 879 646 11 - A 1708 948 A - Ip1f Board - PsuDocument4 pagesSony - 1 879 646 11 - A 1708 948 A - Ip1f Board - PsuMarko MatićNo ratings yet

- MNM SLD Wesm I170 ModelDocument2 pagesMNM SLD Wesm I170 ModelKiko MariazetaNo ratings yet

- Proje ToDocument1 pageProje ToFábio SalatielNo ratings yet

- 20-08-06 Batuan Native Chicken 8-5-2020Document15 pages20-08-06 Batuan Native Chicken 8-5-2020julzNo ratings yet

- SSP X Ssps Stp1 Dads Arc Lap 031223 x00cDocument1 pageSSP X Ssps Stp1 Dads Arc Lap 031223 x00cbadeNo ratings yet

- VFD Display VFD DisplayDocument5 pagesVFD Display VFD Displayapi-3703813No ratings yet

- Plano de ChiclayoDocument1 pagePlano de ChiclayoPaola Novoa OlivaresNo ratings yet

- Plano Topografico ESCALA 1:1000: C: Mid: TDocument1 pagePlano Topografico ESCALA 1:1000: C: Mid: Tluis leonardo flores olivasNo ratings yet

- 2010 CENSUS - CENSUS BLOCK MAP (INDEX) : Choctaw County, AL: MILFORD 47500 Davis 18100Document1 page2010 CENSUS - CENSUS BLOCK MAP (INDEX) : Choctaw County, AL: MILFORD 47500 Davis 18100Igor SemenovNo ratings yet

- Gate 4Document1 pageGate 4AMARNo ratings yet

- Haier D32fa9akm - Ka5q1265rf, Stv9379fa, Tda8947j - TV D SCHDocument1 pageHaier D32fa9akm - Ka5q1265rf, Stv9379fa, Tda8947j - TV D SCHAlberto CamarenaNo ratings yet

- NEW PWB24915 19 Nov 2019 New-Pages-10Document1 pageNEW PWB24915 19 Nov 2019 New-Pages-10danilsanjaya33No ratings yet

- Boon Mixer Guarding-ModelDocument1 pageBoon Mixer Guarding-Modelpatrick pacayraNo ratings yet

- 320DLRR YDS ELE SchematicDocument2 pages320DLRR YDS ELE Schematicthaw3tar3minNo ratings yet

- TroubleshootingDocument75 pagesTroubleshootingAlfonso Josue CastilloNo ratings yet

- XT2149-x (Saipan) MB Component Location L3 RepairDocument2 pagesXT2149-x (Saipan) MB Component Location L3 RepairCanguro GuigueNo ratings yet

- Layout Plan of Jolshiri AbashonDocument1 pageLayout Plan of Jolshiri Abashonkutubulalam723No ratings yet

- New Pos Technology Limited: VER Description Date ApprovedDocument13 pagesNew Pos Technology Limited: VER Description Date ApprovedValeriyNo ratings yet

- Layout Amb-0-Ocb-ge-pla-003 Rev.2 Ambon General Layout DRM IspDocument1 pageLayout Amb-0-Ocb-ge-pla-003 Rev.2 Ambon General Layout DRM IspAhmad IbrahimiNo ratings yet

- 1199 S Panigale WiringDocument1 page1199 S Panigale WiringLucas GonzalezNo ratings yet

- Motoniveladora Hyd Plano HydDocument4 pagesMotoniveladora Hyd Plano HydAlejandro ReyesNo ratings yet

- M3 DJV Edr Eme00 D70 Dep 1161920Document1 pageM3 DJV Edr Eme00 D70 Dep 1161920Mario FeghaliNo ratings yet

- Sheet 05 - Grading Plan-GradingDocument1 pageSheet 05 - Grading Plan-GradingnoelNo ratings yet

- General NotesDocument1 pageGeneral Notesmustafa1989ocNo ratings yet

- RRPR-OPR-PRB-BR1-SB85 - Rev 1Document1 pageRRPR-OPR-PRB-BR1-SB85 - Rev 1sanjeev sharmaNo ratings yet

- ID-001 GROUND FLOOR FURNITURE LAYOUT-ModelDocument1 pageID-001 GROUND FLOOR FURNITURE LAYOUT-ModelAamerNo ratings yet

- Haier D32fa11akm - fscq1265rf, Stv9379fa, Tda8947j - TV D SCHDocument1 pageHaier D32fa11akm - fscq1265rf, Stv9379fa, Tda8947j - TV D SCHAlberto CamarenaNo ratings yet

- G-102-01 (790DBBC) Al-Shahaniya: Qatar Armed ForcesDocument1 pageG-102-01 (790DBBC) Al-Shahaniya: Qatar Armed ForcesAslamNo ratings yet

- Nivel Acceso A-4Document1 pageNivel Acceso A-4Jesus Rafael Quijada AndradeNo ratings yet

- Sector Pedregal Sector Pedregal: Cisterna 4 (480 MSNM)Document1 pageSector Pedregal Sector Pedregal: Cisterna 4 (480 MSNM)Giancarlos Villalobos RomeroNo ratings yet

- 8.PLANO CANTERA-Presentación1Document1 page8.PLANO CANTERA-Presentación1manuel gonzalesNo ratings yet

- Hot BitDocument1 pageHot BitLaercio Marques100% (1)

- Cable Track Sizing and Locations PDFDocument1 pageCable Track Sizing and Locations PDFiqbal husseinNo ratings yet

- RRPR-OPR-PRB-BR1-SB32 - Rev 1Document1 pageRRPR-OPR-PRB-BR1-SB32 - Rev 1sanjeev sharmaNo ratings yet

- STP Plan & SectionDocument1 pageSTP Plan & SectionanishmetaNo ratings yet

- 20105-AR-HOT-07-105-01 Rev 0Document1 page20105-AR-HOT-07-105-01 Rev 0Bahaa MohamedNo ratings yet

- Canlayout HybridDocument1 pageCanlayout HybridLuis MuñozNo ratings yet

- SS-0150-TJR-DWG-ELE-004 - Auxiliary Single Line Diagram (Along With UPS) - PV2-MCRDocument1 pageSS-0150-TJR-DWG-ELE-004 - Auxiliary Single Line Diagram (Along With UPS) - PV2-MCRtukaram.pawarNo ratings yet

- LOTE D-6-2-Layout1Document1 pageLOTE D-6-2-Layout1JENRRI VILLALOBOS LIMACHINo ratings yet

- CH 52 PennsylvaniaDocument1 pageCH 52 PennsylvaniaTonyNo ratings yet

- SE01 SE04 SE03 SE02 E14 E13: As BuiltDocument1 pageSE01 SE04 SE03 SE02 E14 E13: As BuiltgenricNo ratings yet

- RRPR-OPR-PRB-BR1-SB8 - Rev 1Document1 pageRRPR-OPR-PRB-BR1-SB8 - Rev 1sanjeev sharmaNo ratings yet

- Shop Drawings Project Name: Toilet Type 1 Kitchen G003Document7 pagesShop Drawings Project Name: Toilet Type 1 Kitchen G003Wael MohamedNo ratings yet

- 20MU-416200 Rev 0 IFTDocument4 pages20MU-416200 Rev 0 IFTmansoj777No ratings yet

- Deslinde Final 13042021-PlanoDocument1 pageDeslinde Final 13042021-PlanoAlejandra MurciaNo ratings yet

- RRPR-OPR-PRB-BR1-SB52 - Rev 1Document1 pageRRPR-OPR-PRB-BR1-SB52 - Rev 1sanjeev sharmaNo ratings yet

- Lote 05b Sayas Alvares RicardoDocument1 pageLote 05b Sayas Alvares RicardoDEMETRIO POMASONCCO TAYANo ratings yet

- TP 56 PDFDocument1 pageTP 56 PDFViral VegadNo ratings yet

- AllebDocument1 pageAllebstephenc144No ratings yet

- Eep 000097 0102148005 3 ST Det 0702 R02Document1 pageEep 000097 0102148005 3 ST Det 0702 R02Vikram DalalNo ratings yet

- Plano en Planta: Gobierno Regional de PunoDocument1 pagePlano en Planta: Gobierno Regional de PunoHenry Ligue MonzonNo ratings yet

- (Schematic) Ceaza Mega v1.6Document1 page(Schematic) Ceaza Mega v1.6Diego YabburNo ratings yet

- H. T. McCabe Story in The Staunton SpectatorDocument1 pageH. T. McCabe Story in The Staunton Spectatorrflores8810No ratings yet

- ZONA - 1: FabricacionDocument1 pageZONA - 1: FabricacionFreddy flavio Sucuytana cosiNo ratings yet

- Urbanizacion PDFDocument1 pageUrbanizacion PDFRamiro GarcíaNo ratings yet

- Ing Mco009 Pro DFP 005Document1 pageIng Mco009 Pro DFP 005Edward CadavidNo ratings yet

- Jcss Probabilistic Modelcode Part 3: Resistance ModelsDocument4 pagesJcss Probabilistic Modelcode Part 3: Resistance Modelsdimitrios25No ratings yet

- What Is Database?Document17 pagesWhat Is Database?AsadNo ratings yet

- Distortion NPTELDocument58 pagesDistortion NPTELkijiji userNo ratings yet

- AP7760 FAT To H3C FIT Code ConversionDocument21 pagesAP7760 FAT To H3C FIT Code ConversionJake MillsNo ratings yet

- Root Cause Analysis: Motivation, Process, Tools, and PerspectivesDocument15 pagesRoot Cause Analysis: Motivation, Process, Tools, and Perspectives3320021100% (2)

- Schwenk - Katalog 2016 ENDocument36 pagesSchwenk - Katalog 2016 END.T.No ratings yet

- Yeka Subcity Chemistry Model ExamDocument4 pagesYeka Subcity Chemistry Model ExamKerod Mohamed100% (2)

- BLDG. 366 - Light/Sound in Buildings Week 4 - Sound TransmissionDocument33 pagesBLDG. 366 - Light/Sound in Buildings Week 4 - Sound TransmissionSimu LinkNo ratings yet

- Algebra ManipulationsDocument8 pagesAlgebra ManipulationsRobin Kosasih100% (1)

- The in Uence Weekly Resistance Training Frequency On Strength and Body CompositionDocument7 pagesThe in Uence Weekly Resistance Training Frequency On Strength and Body CompositionGabriel AvelinoNo ratings yet

- Renoam: A Grammar Sequencing Tool For Renoise 2.8Document6 pagesRenoam: A Grammar Sequencing Tool For Renoise 2.8WolfNo ratings yet

- FNIRSI-DC6006L English ManualDocument10 pagesFNIRSI-DC6006L English ManualmafmonteNo ratings yet

- ST MQP-3 PDFDocument2 pagesST MQP-3 PDFRaghuram CoorgNo ratings yet

- Quemar UsrpDocument2 pagesQuemar UsrpJoshua Nessus Aragonès SalazarNo ratings yet

- A Privacy-Preserving Authentication in An Edge-Fog EnvironmentDocument7 pagesA Privacy-Preserving Authentication in An Edge-Fog EnvironmentBushra MohsinNo ratings yet

- Operation Guide EL-531V R S PDFDocument30 pagesOperation Guide EL-531V R S PDFlotannaNo ratings yet

- Chapter 2. Signals and SpectraDocument105 pagesChapter 2. Signals and SpectraYoussef GamesNo ratings yet

- 2.EN - Goldwind GW155-4.0-OS Wind Turbine SpecificationsDocument50 pages2.EN - Goldwind GW155-4.0-OS Wind Turbine SpecificationsNguyen BunNo ratings yet

- 19089-LZN7080141 - 4uen - Aradiorelee Marconi8rDocument414 pages19089-LZN7080141 - 4uen - Aradiorelee Marconi8rdigit_ro2051No ratings yet

- Sampling DistributionsDocument25 pagesSampling DistributionsJawad SandhuNo ratings yet

- At 05415 WP Acid Gas Cleaning Using Amine Solvents 2019 1125Document63 pagesAt 05415 WP Acid Gas Cleaning Using Amine Solvents 2019 1125Muhammad NaeemNo ratings yet

- Xerox Phaser 3121 Service M2Document61 pagesXerox Phaser 3121 Service M2Prisăcaru Ionel ViorelNo ratings yet

- A Detailed Lesson Plan in Kindergarten MathematicsDocument12 pagesA Detailed Lesson Plan in Kindergarten MathematicsLoida LiponNo ratings yet

- OR2 4 QueuingModelsDocument5 pagesOR2 4 QueuingModelsCarl Harold AranaydoNo ratings yet

- Rotary Bored Piles: Technique SheetDocument2 pagesRotary Bored Piles: Technique SheetValentVeeNo ratings yet

- A Neural Network Evaluation Model For Individual Thermal ComfortDocument8 pagesA Neural Network Evaluation Model For Individual Thermal Comforthassna ait aliNo ratings yet

- SAP MM Course Sap MM: How To Create SAP RFQ?Document9 pagesSAP MM Course Sap MM: How To Create SAP RFQ?MohammadNo ratings yet

- Yumizen H500 Brochure enDocument4 pagesYumizen H500 Brochure enPopovNo ratings yet

- Minimess EnglishDocument39 pagesMinimess EnglishMoreno Salamanca HelmyNo ratings yet