Professional Documents

Culture Documents

Stp5N105K5: N-Channel 1050 V, 2.9 Ω Typ., 3 A Mdmesh™ K5 Power Mosfet In A To-220 Package

Uploaded by

Jorman Cristopher Amaya AvilezOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Stp5N105K5: N-Channel 1050 V, 2.9 Ω Typ., 3 A Mdmesh™ K5 Power Mosfet In A To-220 Package

Uploaded by

Jorman Cristopher Amaya AvilezCopyright:

Available Formats

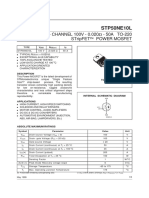

STP5N105K5

N-channel 1050 V, 2.9 Ω typ., 3 A MDmesh™ K5

Power MOSFET in a TO-220 package

Datasheet - production data

Features

Order code VDS RDS(on) max. ID PTOT

STP5N105K5 1050 V 3.5 Ω 3A 85 W

Worldwide best FOM (figure of merit)

Ultra low gate charge

100% avalanche tested

Zener-protected

Applications

Switching applications

Figure 1: Internal schematic diagram

Description

D(2, TAB)

This N-channel Zener-protected Power MOSFET

is designed using ST’s revolutionary avalanche-

rugged very high voltage MDmesh™ K5

technology, based on an innovative proprietary

vertical structure. The result is a dramatic

G(1) reduction in on-resistance, and ultra-low gate

charge for applications which require superior

power density and high efficiency.

Table 1: Device summary

Order code Marking Package Packaging

STP5N105K5 5N105K5 TO-220 Tube

S(3)

AM01476v1

October 2014 DocID026703 Rev 3 1/14

This is information on a product in full production. www.st.com

Contents STP5N105K5

Contents

1 Electrical ratings ............................................................................. 3

2 Electrical characteristics ................................................................ 4

2.1 Electrical characteristics (curves) ...................................................... 6

3 Test circuits ..................................................................................... 9

4 Package mechanical data ............................................................. 10

4.1 TO-220 package mechanical data .................................................. 11

5 Revision history ............................................................................ 13

2/14 DocID026703 Rev 3

STP5N105K5 Electrical ratings

1 Electrical ratings

Table 2: Absolute maximum ratings

Symbol Parameter Value Unit

VGS Gate- source voltage ± 30 V

ID Drain current (continuous) at TC = 25 °C 3 A

ID Drain current (continuous) at TC = 100 °C 2 A

IDM(1) Drain current (pulsed) 12 A

PTOT Total dissipation at TC = 25 °C 85 W

IAR Max current during repetitive or single pulse avalanche 1 A

Single pulse avalanche energy

EAS 85 mJ

(starting TJ = 25 °C, ID=IAS, VDD= 50 V)

dv/dt (2) Peak diode recovery voltage slope 4.5 V/ns

dv/dt (3) MOSFET dv/dt ruggedness 50 V/ns

Tj Operating junction temperature

- 55 to 150 °C

Tstg Storage temperature

Notes:

(1)Pulse width limited by safe operating area

(2)I

SD ≤ 3 A, di/dt ≤ 100 A/µs, VDS(peak) ≤ V(BR)DSS

(3)V

DS ≤ 840 V

Table 3: Thermal data

Symbol Parameter Value Unit

Rthj-case Thermal resistance junction-case max 1.47 °C/W

Rthj-amb Thermal resistance junction-amb max 62.5 °C/W

DocID026703 Rev 3 3/14

Electrical characteristics STP5N105K5

2 Electrical characteristics

(TCASE = 25 °C unless otherwise specified).

Table 4: On/off states

Symbol Parameter Test conditions Min. Typ. Max. Unit

Drain-source breakdown

V(BR)DSS VGS= 0, ID = 1 mA 1050 V

voltage

VGS = 0, VDS = 1050 V 1 µA

Zero gate voltage drain

IDSS VGS = 0, VDS = 1050 V,

current 50 µA

Tc=125 °C

IGSS Gate body leakage current VDS = 0, VGS = ± 20 V ±10 µA

VGS(th) Gate threshold voltage VDS = VGS, ID = 100 µA 3 4 5 V

Static drain-source on-

RDS(on) VGS = 10 V, ID= 1.5 A 2.9 3.5 Ω

resistance

Table 5: Dynamic

Symbol Parameter Test conditions Min. Typ. Max. Unit

Ciss Input capacitance - 210 - pF

VDS =100 V, f=1 MHz,

Coss Output capacitance - 16 - pF

VGS=0

Crss Reverse transfer capacitance - 0.5 - pF

Equivalent capacitance time

Co(tr)(1) - 26 - pF

related

VGS = 0, VDS = 0 to 840 V

Equivalent capacitance

Co(er)(2) - 10 - pF

energy related

RG Intrinsic gate resistance f = 1MHz open drain - 9 - Ω

Qg Total gate charge VDD = 840 V, ID = 3 A - 12.5 - nC

Qgs Gate-source charge VGS =10 V - 2 - nC

Figure 16: "Gate charge

Qgd Gate-drain charge test circuit" - 9.5 - nC

Notes:

(1)Timerelated is defined as a constant equivalent capacitance giving the same charging time as C oss when VDS

increases from 0 to 80% VDSS

(2)Energyrelated is defined as a constant equivalent capacitance giving the same stored energy as Coss when VDS

increases from 0 to 80% VDSS

Table 6: Switching times

Symbol Parameter Test conditions Min. Typ. Max. Unit

Turn-on delay

td(on) - 15.5 - ns

time

VDD = 525V, ID = 1.5 A, RG=4.7 Ω,

tr Rise time VGS=10 V - 8.5 - ns

Turn-off delay Figure 18: " Unclamped inductive load

td(off) test circuit" - 31 - ns

time

tf Fall time - 24 - ns

4/14 DocID026703 Rev 3

STP5N105K5 Electrical characteristics

Table 7: Source drain diode

Symbol Parameter Test conditions Min. Typ. Max. Unit

Source-drain

ISD - 3 A

current

Source-drain

ISDM 12 A

current (pulsed)

Forward on

VSD(1) ISD= 3 A, VGS=0 - 1.5 V

voltage

Reverse recovery

trr ISD= 3 A, VDD= 60 V - 400 ns

time

di/dt = 100 A/µs,

Reverse recovery

Qrr Figure 17: " Test circuit for inductive - 2.3 µC

charge

load switching and diode recovery

Reverse recovery times"

IRRM - 12 A

current

Reverse recovery ISD= 3 A,VDD= 60 V

trr - 560 ns

time di/dt=100 A/µs,

Reverse recovery Tj=150 °C

Qrr - 3.1 µC

charge Figure 17: " Test circuit for inductive

Reverse recovery load switching and diode recovery

IRRM times" - 11 A

current

Notes:

(1)Pulsed: pulse duration = 300µs, duty cycle 1.5%

Table 8: Gate-source Zener diode

Symbol Parameter Test conditions Min Typ. Max. Unit

V(BR)GSO Gate-source breakdown voltage IGS = ± 1mA, ID=0 30 - - V

The built-in back-to-back Zener diodes have specifically been designed to enhance the

device's ESD capability. In this respect the Zener voltage is appropriate to achieve an

efficient and cost-effective intervention to protect the device's integrity. These integrated

Zener diodes thus avoid the usage of external components.

DocID026703 Rev 3 5/14

Electrical characteristics STP5N105K5

2.1 Electrical characteristics (curves)

Figure 3: Thermal impedance

Figure 2: Safe operating area

GIPD030920141136FSR

ID

(A)

10

is

RD rea

n)

ax a

(o

m his

S

by in t 100µs

1

ite tion

1ms

Lim era

d

p

O

10ms

0.1

Tj=150°C

Tc=25°C

Single pulse

0.01

0.1 1 10 100 1000 V DS(V)

Figure 4: Output characteristics Figure 5: Transfer characteristics

GIPG290820141204FSR GIPG290820141334FSR

ID

ID(A)

(A)

V DS=20V

6

5

V GS=10, 11V

5

4

9V

4

3

3

8V

2

2

1 7V 1

6V

0 0

0 5 10 15 20 V DS(V) 5 6 7 8 9 10 V GS(V)

Figure 6: Gate charge vs gate-source voltage Figure 7: Static drain-source on-resistance

V GS GIPG290820141348FSR

V DS GIPG290820141400FSR

(V) R DS(on)

(V) (Ω)

V DS=840V V GS=10V

10 ID=3A 1200 4

V DS

8 800 3.5

3

6 600

2.5

4 400

2

2 200

1.5

0 0

0 2 4 6 8 10 12 Q g(nC) 1

0 1 2 3 4 ID(A)

6/14 DocID026703 Rev 3

STP5N105K5 Electrical characteristics

Figure 8: Capacitance variations Figure 9: Source-drain diode forward

C

GIPG290820141409FSR characteristics

(pF) GIPG290820141432FSR

V SD (V)

1000

1

T J=-50°C

Ciss

100 0.9

0.8 T J=25°C

10

Coss

Crss 0.7

1

T J=150°C

0.6

0.1

0.1 1 10 100 V DS(V)

0.5

0 0.5 1 1.5 2 2.5 3 ISD(A)

Figure 10: Normalized gate threshold Figure 11: Normalized on-resistance vs

voltage vs temperature temperature

V GS(th) AM18082v1

(norm)

1.2 ID=100 µ A

1.1

0.9

0.8

0.7

0.6

0.5

0.4

-100 -50 0 50 100 150 T J(°C)

Figure 12: Normalized V(BR)DSS vs

Figure 13: Maximum avalanche energy

temperature GIPG290820141445FSR

AM18083v1 E AS

V (BR)DSS (mJ)

(norm)

80

ID=1m A

1.1

70

60

1.05

50

1 40

30

0.95

20

0.9 10

0

0.85 0 20 40 60 80 100 120 140 T J(°C)

-100 -50 0 50 100 T J(°C)

DocID026703 Rev 3 7/14

Electrical characteristics STP5N105K5

Figure 14: Output capacitance stored energy vs temperature

GIPG290820141419FSR

E oss

(µJ)

0

0 200 400 600 800 V DS(V)

8/14 DocID026703 Rev 3

STP5N105K5 Test circuits

3 Test circuits

Figure 15: Switching times test circuit for

resistive load Figure 16: Gate charge test circuit

Figure 17: Test circuit for inductive load

switching and diode recovery times Figure 18: Unclamped inductive load test

circuit

Figure 19: Unclamped inductive waveform Figure 20: Switching time waveform

DocID026703 Rev 3 9/14

Package mechanical data STP5N105K5

4 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK® packages, depending on their level of environmental compliance. ECOPACK ®

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK® is an ST trademark.

10/14 DocID026703 Rev 3

STP5N105K5 Package mechanical data

4.1 TO-220 package mechanical data

Figure 21: TO-220 type A package outline

DocID026703 Rev 3 11/14

Package mechanical data STP5N105K5

Table 9: TO-220 type A mechanical data

mm

Dim.

Min. Typ. Max.

A 4.40 4.60

b 0.61 0.88

b1 1.14 1.70

c 0.48 0.70

D 15.25 15.75

D1 1.27

E 10 10.40

e 2.40 2.70

e1 4.95 5.15

F 1.23 1.32

H1 6.20 6.60

J1 2.40 2.72

L 13 14

L1 3.50 3.93

L20 16.40

L30 28.90

ÆP 3.75 3.85

Q 2.65 2.95

12/14 DocID026703 Rev 3

STP5N105K5 Revision history

5 Revision history

Table 10: Document revision history

Date Revision Changes

17-Jul-2014 1 First release.

Document status promoted from preliminary to production data.

03-Sep-2014 2 Added Section 3.1: "Electrical characteristics (curves)"

Minor text changes.

Updated Figure 6: "Gate charge vs gate-source voltage"and Figure

15-Oct-2014 3

8: "Capacitance variations"

DocID026703 Rev 3 13/14

STP5N105K5

IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and

improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST

products before placing orders. ST products are sold pursuant to ST’s terms and conditions of sale in place at the time of order

acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the

design of Purchasers’ products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2014 STMicroelectronics – All rights reserved

14/14 DocID026703 Rev 3

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- STP50N06 STP50N06FI: N - Channel Enhancement Mode Power Mos TransistorDocument11 pagesSTP50N06 STP50N06FI: N - Channel Enhancement Mode Power Mos TransistorJorman Cristopher Amaya AvilezNo ratings yet

- STP5NA80 Stp5Na80Fi: N - Channel Enhancement Mode Fast Power Mos TransistorDocument11 pagesSTP5NA80 Stp5Na80Fi: N - Channel Enhancement Mode Fast Power Mos TransistorJorman Cristopher Amaya AvilezNo ratings yet

- STB57N65M5, STF57N65M5, Sti57n65m5, STP57N65M5Document23 pagesSTB57N65M5, STF57N65M5, Sti57n65m5, STP57N65M5Jorman Cristopher Amaya AvilezNo ratings yet

- Stb50Nf25 Stp50Nf25: N-Channel 250V - 0.055 - 45A - D Pak - To-220 Low Gate Charge Stripfet™ Power MosfetDocument15 pagesStb50Nf25 Stp50Nf25: N-Channel 250V - 0.055 - 45A - D Pak - To-220 Low Gate Charge Stripfet™ Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- STP53N08: N - Channel Enhancement Mode Power Mos TransistorDocument6 pagesSTP53N08: N - Channel Enhancement Mode Power Mos TransistorJorman Cristopher Amaya AvilezNo ratings yet

- Stp4Nc60 - Stp4Nc60Fp Stb4Nc60-1: N-Channel 600V - 1.8 - 4.2A To-220/To-220Fp/I Pak Powermesh™Ii MosfetDocument11 pagesStp4Nc60 - Stp4Nc60Fp Stb4Nc60-1: N-Channel 600V - 1.8 - 4.2A To-220/To-220Fp/I Pak Powermesh™Ii MosfetJorman Cristopher Amaya AvilezNo ratings yet

- DSDocument8 pagesDSJorman Cristopher Amaya AvilezNo ratings yet

- Stp50Ne10: N - Channel 100V - 0.021 - 50A To-220 Stripfet Power MosfetDocument9 pagesStp50Ne10: N - Channel 100V - 0.021 - 50A To-220 Stripfet Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- 4NK60ZFP DatasheetDocument16 pages4NK60ZFP DatasheetrpaqrvNo ratings yet

- Stp50Ne10L: N - Channel 100V - 0.020 - 50A To-220 Stripfet Power MosfetDocument9 pagesStp50Ne10L: N - Channel 100V - 0.020 - 50A To-220 Stripfet Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- Stp4Nm60 Std3Nm60 - Std3Nm60-1: N-Channel 600V - 1.3 - 3A To-220/Dpak/Ipak Zener-Protected Mdmesh™Power MosfetDocument13 pagesStp4Nm60 Std3Nm60 - Std3Nm60-1: N-Channel 600V - 1.3 - 3A To-220/Dpak/Ipak Zener-Protected Mdmesh™Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- STD4N52K3, STF4N52K3, STP4N52K3, Stu4n52k3Document22 pagesSTD4N52K3, STF4N52K3, STP4N52K3, Stu4n52k3Jorman Cristopher Amaya AvilezNo ratings yet

- STP2N80 STP2N80FI: N - Channel Enhancement Mode Power Mos TransistorDocument10 pagesSTP2N80 STP2N80FI: N - Channel Enhancement Mode Power Mos TransistorscribdsteNo ratings yet

- Stp52N25M5: N-Channel 250 V, 0.055, 28 A, To-220 Mdmesh V Power MosfetDocument13 pagesStp52N25M5: N-Channel 250 V, 0.055, 28 A, To-220 Mdmesh V Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- Stb50Nf25 Stp50Nf25: N-Channel 250V - 0.055 - 45A - D Pak - To-220 Low Gate Charge Stripfet™ Power MosfetDocument15 pagesStb50Nf25 Stp50Nf25: N-Channel 250V - 0.055 - 45A - D Pak - To-220 Low Gate Charge Stripfet™ Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- Stp50Ne10: N - Channel 100V - 0.021 - 50A To-220 Stripfet Power MosfetDocument9 pagesStp50Ne10: N - Channel 100V - 0.021 - 50A To-220 Stripfet Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- STP2N80 STP2N80FI: N - Channel Enhancement Mode Power Mos TransistorDocument10 pagesSTP2N80 STP2N80FI: N - Channel Enhancement Mode Power Mos TransistorscribdsteNo ratings yet

- 1Document6 pages1Jorman Cristopher Amaya AvilezNo ratings yet

- Stp4Nb50 Stp4Nb50Fp: N - Channel Enhancement Mode Powermesh MosfetDocument8 pagesStp4Nb50 Stp4Nb50Fp: N - Channel Enhancement Mode Powermesh MosfetJorman Cristopher Amaya AvilezNo ratings yet

- Stp4Nc50 Stp4Nc50Fp: N-Channel 500V - 2.2 - 3.5A To-220/To-220Fp Powermesh Ii MosfetDocument10 pagesStp4Nc50 Stp4Nc50Fp: N-Channel 500V - 2.2 - 3.5A To-220/To-220Fp Powermesh Ii MosfetJorman Cristopher Amaya AvilezNo ratings yet

- C 32725Document4 pagesC 32725Hannibal Zeugon ZǝnƃouNo ratings yet

- STP3N100 STP3N100FI: N - Channel Enhancement Mode Power Mos TransistorDocument11 pagesSTP3N100 STP3N100FI: N - Channel Enhancement Mode Power Mos TransistorJorman Cristopher Amaya AvilezNo ratings yet

- Stp4Nc60A - Stp4Nc60Afp Stb4Nc60A-1: N-Channel 600V - 1.8 - 4.2A To-220/To-220Fp/I Pak Powermesh Ii MosfetDocument11 pagesStp4Nc60A - Stp4Nc60Afp Stb4Nc60A-1: N-Channel 600V - 1.8 - 4.2A To-220/To-220Fp/I Pak Powermesh Ii MosfetJorman Cristopher Amaya AvilezNo ratings yet

- Stp50Ne10L: N - Channel 100V - 0.020 - 50A To-220 Stripfet Power MosfetDocument9 pagesStp50Ne10L: N - Channel 100V - 0.020 - 50A To-220 Stripfet Power MosfetJorman Cristopher Amaya AvilezNo ratings yet

- STP36N06L STP36N06LFI: N - Channel Enhancement Mode Power Mos TransistorDocument11 pagesSTP36N06L STP36N06LFI: N - Channel Enhancement Mode Power Mos TransistorJorman Cristopher Amaya AvilezNo ratings yet

- Darlington Transistors BC517: NPN SiliconDocument9 pagesDarlington Transistors BC517: NPN SiliconJhonny Mamani LópezNo ratings yet

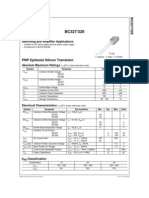

- PNP Silicon Planar Medium Power Transistor: Absolute Maximum RatingsDocument2 pagesPNP Silicon Planar Medium Power Transistor: Absolute Maximum RatingsJorman Cristopher Amaya AvilezNo ratings yet

- Continental Device India Limited: Silicon Planar Epitaxial Transistors BC337 BC337A BC338 TO-92 Plastic PackageDocument5 pagesContinental Device India Limited: Silicon Planar Epitaxial Transistors BC337 BC337A BC338 TO-92 Plastic PackageJorman Cristopher Amaya AvilezNo ratings yet

- BC548 Hoja de Datos PDFDocument5 pagesBC548 Hoja de Datos PDFJuan FiNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Fronius Eco enDocument2 pagesFronius Eco enPatrice NdondaNo ratings yet

- Capacitor Metallized Polyester Film 250V 155J 4pc FL US - EbayDocument1 pageCapacitor Metallized Polyester Film 250V 155J 4pc FL US - EbayoscarNo ratings yet

- Mitsubishi UPS - Owners Manual 98AB SMS V20Document67 pagesMitsubishi UPS - Owners Manual 98AB SMS V20Marcelo BenacchioNo ratings yet

- Schaefer VVD Flyer Arkel Arcode enDocument2 pagesSchaefer VVD Flyer Arkel Arcode enadda chariNo ratings yet

- PCB Layout Rules for Signal IntegrityDocument31 pagesPCB Layout Rules for Signal Integrityessen999No ratings yet

- Eet 521 Lecture NoteDocument6 pagesEet 521 Lecture NoteEmmanuel AtinsolaNo ratings yet

- Harga TintaDocument1 pageHarga TintaFerrarians1981No ratings yet

- HSC Physics NotesDocument13 pagesHSC Physics NotesAditya VermaNo ratings yet

- Micro Drives pdc1000 Manual en-US en-USDocument36 pagesMicro Drives pdc1000 Manual en-US en-USPezhmandmNo ratings yet

- Nnse 284 SDocument31 pagesNnse 284 SPatrice PaulNo ratings yet

- Calculus Based Physics Midterm Exam FlavianoDocument27 pagesCalculus Based Physics Midterm Exam FlavianoDhmi yassinNo ratings yet

- Balance Model FA-2204B: Instructions ManualDocument22 pagesBalance Model FA-2204B: Instructions ManualAntonio G. B. da CruzNo ratings yet

- Ihm Carel NovoDocument4 pagesIhm Carel NovoLeonardo SantosNo ratings yet

- Mxn13 NMB MatDocument1 pageMxn13 NMB MatAndriuw Jetzer GualNo ratings yet

- Low Voltage Control CircuitsDocument17 pagesLow Voltage Control CircuitsmersiumNo ratings yet

- 1788-14 ECM Smart Whisperflow Fan Filter Units ManualDocument5 pages1788-14 ECM Smart Whisperflow Fan Filter Units Manualzivkovic brankoNo ratings yet

- 20 VMC100 AdvDocument1 page20 VMC100 AdvLuc PhamNo ratings yet

- Aer Conditionat Multisplit LG Unitati Interne Ceiling Concealed Duct Type Pliant Date TehniceDocument6 pagesAer Conditionat Multisplit LG Unitati Interne Ceiling Concealed Duct Type Pliant Date TehniceKyaw San OoNo ratings yet

- Canon Ir7105 - 7095 - 7086 Series Service ManualDocument588 pagesCanon Ir7105 - 7095 - 7086 Series Service ManualCOLOR50No ratings yet

- Acoustic Box 2 ManualDocument17 pagesAcoustic Box 2 ManualAdedejinfoNo ratings yet

- De Sulfat or PCBDocument1 pageDe Sulfat or PCBrachmatNo ratings yet

- Diodo Soplador de Aire 1N4007Document2 pagesDiodo Soplador de Aire 1N4007AlexferminNo ratings yet

- CHB InverterDocument6 pagesCHB InverterSateesh KumarNo ratings yet

- Diesel Engine Fire Pump Controllers (Firetrol)Document4 pagesDiesel Engine Fire Pump Controllers (Firetrol)Shibu ThomasNo ratings yet

- Tps 40200Document51 pagesTps 40200qwertyNo ratings yet

- Quick reference to hand pumps and accessoriesDocument20 pagesQuick reference to hand pumps and accessoriesFederico TomiNo ratings yet

- Placa SolarDocument2 pagesPlaca Solarromulo bragaNo ratings yet

- Data - Sheet - Fine Film - IG030BK28VBDocument2 pagesData - Sheet - Fine Film - IG030BK28VBLiliana ZamoraNo ratings yet

- ATL Starter Motor Protection System Instruction Manual MVRSM Series Manual-4 - 217900Document108 pagesATL Starter Motor Protection System Instruction Manual MVRSM Series Manual-4 - 217900Steven Varon RodriguezNo ratings yet

- 7734 15 T6734R6Document26 pages7734 15 T6734R6Alexandre MorelNo ratings yet