Professional Documents

Culture Documents

Digital Electronics Exercises

Uploaded by

Vito LOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Electronics Exercises

Uploaded by

Vito LCopyright:

Available Formats

Esercizi di

Elettronica

Digitale

A.C. Neve – Esercizi Digitali 1

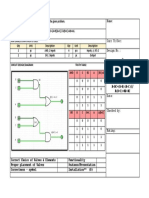

Porte logiche Elementari

A B AND OR NAND NOR EXOR EXNOR

0 0 0 0 1 1 0 1

0 1 0 1 1 0 1 0

1 0 0 1 1 0 1 0

1 1 1 1 0 0 0 1

* + ⊕ ⊗

Reti logiche con interruttori

Vcc

OR Out

R

Vcc Out

AND R

Vcc Out

R

NOT

Vcc Out

R

NOR

Vcc Out

R

NAND

Insiemi di operatori Universale

AND-OR-NOT

NAND-NAND

NOR-NOR

A.C. Neve – Esercizi Digitali 2

Reti combinatorie con uscita singola

CD

AB 00 01 11 10

00 0 0 1 0

Z ( A, B, C , D) = AB + CD + BC

01 0 0 1 1

11 1 1 1 1

10 0 0 1 0

CD

AB 00 01 11 10

00 0 0 0 0

Z ( A, B, C , D) = AC + A BD + BCD

01 0 1 1 1

11 1 1 0 1

10 1 1 0 0

CD

AB 00 01 11 10

00 0 0 1 0

01 1 1 1 0 Z ( A, B, C , D) = A BC + A CD + ABC + AC D

11 0 1 1 1

10 0 1 0 0

CD

AB 00 01 11 10

00 0 0 1 1

01 0 1 1 0 Z ( A, B, C , D) = AC D + BC D + A CD + B CD

11 1 1 0 0

10 1 0 0 1

A.C. Neve – Esercizi Digitali 3

CD

AB 00 01 11 10

00 0 0 1 1

01 1 0 0 1

Z ( A, B, C , D) = A BC + ABC + ABD + AB D

11 0 0 1 1

10 1 0 0 1

CD

AB 00 01 11 10

00 1 0 1 0 Z ( A, B, C , D) = AB + BC + BD + A C D + A CD + AB C D

01 1 1 1 1

11 1 0 1 1

10 0 1 0 0

CD

AB 00 01 11 10

00 1 1 0 1

01 0 1 1 1 Z ( A, B, C , D) = BD + A B C + A CD + AC D + AB C

11 1 1 1 0

10 1 0 1 1

CD

AB 00 01 11 10

00 0 1 1 0

01 0 0 0 1

Z ( A, B, C , D) = AD + B D + ABC + A BCD

11 1 1 1 0

10 0 1 1 0

A.C. Neve – Esercizi Digitali 4

CD

AB 00 01 11 10

00 1 0 0 1

01 1 1 1 1

Z ( A, B, C , D) = BD + A B + B D

11 0 1 1 0

10 1 0 0 1

CD

AB 00 01 11 10

00 0 0 1 1

01 0 1 1 1 Z ( A, B, C , D) = AC + BD + A C

11 1 1 1 0

10 1 1 0 0

CD

AB 00 01 11 10

00 1 0 0 1

01 1 1 0 1

11 1 0 1 0 Z ( A, B, C , D) = C D + A D + A BC + ABCD

10 1 0 0 0

CD

AB 00 01 11 10

00 0 1 0 1

01 1 0 1 0

Z ( A, B, C , D) = ( A ⊗ B ) ⊗ (C ⊗ D)

11 0 1 0 1

10 1 0 1 0

A.C. Neve – Esercizi Digitali 5

Reti combinatorie non completamente specificate

CD

AB 00 01 11 10

00 0 0 0 x

01 1 1 0 0 Z ( A, B, C , D) = BC + AD + AB C

11 1 x 0 x

10 1 0 1 x

CD

AB 00 01 11 10

00 1 0 x 1

01 0 1 x 0 Z ( A, B, C , D) = AD + B D + A BD

11 1 0 x x

10 1 0 x x

CD

AB 00 01 11 10

00 1 1 1 0

01 0 x 1 0 Z ( A, B, C , D) = A D + B C + AC D

11 1 0 0 0

10 x x 0 x

CD

AB 00 01 11 10

00 1 1 0 1

01 0 0 1 0 Z ( A, B, C , D) = B C + B D + BCD

11 x x x x

10 x x 0 1

A.C. Neve – Esercizi Digitali 6

CD

AB 00 01 11 10

00 x 0 x 0

01 0 1 1 1 Z ( A, B, C , D) = AC + AD + A BD + A BC

11 1 1 0 1

10 1 1 0 x

CD

AB 00 01 11 10

00 1 1 1 0

01 0 x 0 x Z ( A, B, C , D) = B C + B D + AC D

11 1 0 0 0

10 x x x x

CD

AB 00 01 11 10

00 1 1 1 0

01 0 x 1 x

Z ( A, B, C , D) = B C + A D + AC D

11 1 0 0 0

10 x x x x

CD

AB 00 01 11 10

00 0 1 x 0

01 0 x 1 0 Z ( A, B, C , D) = A D + AD + AB C

11 1 0 x x

10 1 1 0 x

A.C. Neve – Esercizi Digitali 7

Analisi di reti combinatorie

f ( A, B, C ) = C ⋅ ( B ⋅ ( A + B + C ) ⋅ C ) = C ⋅ ( B ⋅ ( A + B + C ) ⋅ C = C ⋅ ( B + ( A + B + C ) + C ) =

C ⋅ ( B + A B C + C ) = C B + A B C C + CC = C B ⋅ (1 + A ) = C B = C B = C + B

f ( A, B, C , D) = A B + D ⋅ ( B + C ) = A + B + B D + CD = A + B ⋅ (1 + D) + CD = A + B + CD

A.C. Neve – Esercizi Digitali 8

f ( A, B, C ) = ( A + B + C ) ⋅ ( AB + A B + A BC ) = ( A + B + C ) + ( AB + A B + A BC ) =

= A B C + ( AB ⋅ A B ⋅ A BC ) = A B C + ( A + B ) ⋅ ( A + B) ⋅ A BC = A B C + ( A A + A B + AB + B B) ⋅ A B C =

A B C + A BA B C + AB A B C = A B C

[ ]

f ( A, B, C ) = ( A + B) ⋅ AB ⋅ B + C = ( A + B) + AB ⋅ B + C = ( AB + AB) ⋅ B + C =

AB B + ( A + B ) ⋅ B + C = AB + A B + B + C = ( A + A ) ⋅ B + B + C = B + B + C = B + C = BC

A.C. Neve – Esercizi Digitali 9

Circuiti combinatori con uscita multipla

Sommatore:

La funzione espletata da un sommatore a due bit è descritta dalla seguente tabella:

A B S C

S = somma 0 0 0 0

C = riporto 0 1 1 0

1 0 1 0

1 1 0 1

S = A B + AB = A ⊕ B

C = AB

Il circuito proposto è detto sommatore semplice (Half Adder) in quanto non tiene conto di eventuali

riporti precedenti.

La tabella di verità di un sommatore completo (Full Adder) è invece la seguente:

A B Ci S Co

0 0 0 0 0

0 0 1 1 0 Ci = riporto precedente

0 1 0 1 0 S = somma

0 1 1 0 1 Co = riporto successivo

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

S = A B Ci + A BCi + AB C i + ABCi = Ci ⋅ ( A B + AB) + C i ⋅ ( A B + AB ) =

= Ci ⋅ ( A ⊕ B) + C ⋅ ( A ⊕ B) = C ⊕ ( A ⊕ B)

Co = A BCi + AB Ci + ABC i + ABC = ( A B + AB ) ⋅ Ci + AB ⋅ (Ci + C i ) = AB + Ci ⋅ ( A ⊕ B)

Nella figura seguente è proposto il circuito di un Full Adder.

A.C. Neve – Esercizi Digitali 10

Sottrattore:

La funzione espletata da un sottratore a due bit è descritta dalla seguente tabella:

A B S P

S = differenza 0 0 0 0

P = prestito 0 1 1 1

1 0 1 0

1 1 0 0

S = A B + AB = A ⊕ B

P = AB

Il circuito proposto è detto sottrattore semplice (Half Subtractor) in quanto non tiene conto di

eventuali prestiti precedenti.

La tabella di verità di un sottrattore completo (Full Subtractor) è invece la seguente:

A.C. Neve – Esercizi Digitali 11

A B Pi S Po

0 0 0 0 0

0 0 1 1 1 Pi = prestito precedente

0 1 0 1 1 S = differenza

0 1 1 0 1 Po = prestito successivo

1 0 0 1 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

S = A B Pi + A BP i + AB P i + ABPi = Po = A B Pi + A BP i + A BPi + ABPi =

= Pi ⋅ ( A B + AB) + P i ⋅ ( A B + AB ) = = A B ⋅ ( Pi + P i ) + Pi ⋅ ( A B + AB) =

= Pi ⊕ ( A ⊕ B ) = A B + Pi ⋅ ( A ⊗ B)

Nella figura seguente è proposto il circuito di un Full Subtractor.

A.C. Neve – Esercizi Digitali 12

Esercizio: Descrivere la funzione espletata dal seguente circuito

Il circuito proposto si comporta come una piccola ALU a due bit in grado di espletare le quattro

funzioni logiche elementari AND, OR, NAND e NOR. Gli ingressi sono A e B. I segnali di

selezione sono S1 ed S2.

S1 S2 Z1 Z2 Z3 Z4

0 0 A nand B 1 0 0

0 1 1 A nor B 0 0

1 0 1 1 A and B 0

1 0 1 1 0 A or B

Esercizio: Utilizzando un decodificatore, realizzare un generatore di parità a tre bit:

A.C. Neve – Esercizi Digitali 13

Esercizio: Realizzare, con porte logiche, un codificatore a priorità con quattro ingressi

I3 I2 I1 I0 A1 A0 I1I0

0 0 0 0 0 0 I3I2 00 01 11 10

0 0 0 1 0 0 00 0 0 1 1

0 0 1 0 0 1

0 0 1 1 0 1 01 0 0 0 0 A0

0 1 0 0 1 0

0 1 0 1 1 0

11 1 1 1 1

0 1 1 0 1 0 10 1 1 1 1

0 1 1 1 1 0

1 0 0 0 1 1 I1I0

1 0 0 1 1 1 I3I2 00 01 11 10

1 0 1 0 1 1 00 0 0 0 0

1 0 1 1 1 1

A1

1 1 0 0 1 1 01 1 1 1 1

1 1 0 1 1 1

1 1 1 0 1 1

11 1 1 1 1

1 1 1 1 1 0 10 1 1 1 1

A0 = I 3 + I1I 2

A1 = I 2 + I 3

A.C. Neve – Esercizi Digitali 14

Esercizio: Realizzare un circuito che accetti in ingresso una parola in codice BCD8421 con codifica

Hamming, ne effettui il controllo d’errore ed eventualmente anche la correzione ed emetta in uscita

la parola corretta.

k1 1

k2 2

1 n0

n0 3

2 n1

k3 4

3 n2

n1 5

4 n3

n2 6

n3 7

Circuito per la rilevazione e correzione di errore

per codici BCD 8421 in codifica Hamming

HAMMING CODE INPUT

n3 n2 n1 k3 n0 k2 k1

P3

P2 3 --> 8

DECODER

7 6 5 4 3 2 1 0

P1

BCD 8421 CORRECT OUTPUT

n0

n1

n2

n3

A.C. Neve – Esercizi Digitali 15

Esercizio: Realizzare un convertitore di codice da BCD 8421 in BCD Eccesso-3.

N B3 B2 B1 B0 E3 E2 E1 E0

0 0 0 0 0 0 0 1 1

1 0 0 0 1 0 1 0 0

2 0 0 1 0 0 1 0 1 La tabella descrive una macchina combinatoria

3 0 0 1 1 0 1 1 0 avente quattro ingressi per il codice BCD 8421 e

4 0 1 0 0 0 1 1 1 quattro uscite per il corrispondente codice BCD

5 0 1 0 1 1 0 0 0 Eccesso-3.

6 0 1 1 0 1 0 0 1

7 0 1 1 1 1 0 1 0

8 1 0 0 0 1 0 1 1

9 1 0 0 1 1 1 0 0

- 1 0 1 0 x x x x

- 1 0 1 1 x x x x

- 1 1 0 0 x x x x

- 1 1 0 1 x x x x

- 1 1 1 0 x x x x

- 1 1 1 1 x x x x

B1B0 B1B0

B3B2 00 01 11 10 B3B2 00 01 11 10

00 0 0 0 0 00 0 1 1 1

01 0 1 1 1 01 1 0 0 0

11 x x x x 11 x x x x

10 1 1 x x 10 0 1 x x

E 3 = B3 + B0 B 2 + B1B 2 E 2 = B0 B 2 + B1B 2 + B 0 B1B 2

B1B0 B1B0

B3B2 00 01 11 10 B3B2 00 01 11 10

00 1 0 1 0 00 1 0 0 1

01 1 0 1 0 01 1 0 0 1

11 x x x x 11 x x x x

10 1 0 x x 10 1 0 x x

E1 = B0 B1 + B 0 B1 E0 = B 0

A.C. Neve – Esercizi Digitali 16

Esercizio: Realizzare un convertitore di codice da BCD Eccesso-3 in BCD 8421.

N E3 E2 E1 E0 B3 B2 B1 B0

- 0 0 0 0 x x x x

- 0 0 0 1 x x x x

- 0 0 1 0 x x x x La tabella descrive una macchina combinatoria

0 0 0 1 1 0 0 0 0 avente quattro ingressi per il codice BCD Eccesso-3

1 0 1 0 0 0 0 0 1 e quattro uscite per il corrispondente codice BCD

2 0 1 0 1 0 0 1 0 8421.

3 0 1 1 0 0 0 1 1

4 0 1 1 1 0 1 0 0

5 1 0 0 0 0 1 0 1

6 1 0 0 1 0 1 1 0

7 1 0 1 0 0 1 1 1

8 1 0 1 1 1 0 0 0

9 1 1 0 0 1 0 0 1

- 1 1 0 1 x x x x

- 1 1 1 0 x x x x

- 1 1 1 1 x x x x

E1E0 E1E0

E3E2 00 01 11 10 E3E2 00 01 11 10

00 x x 0 x 00 x x 0 x

01 0 0 0 0 01 0 0 1 0

11 1 x x x 11 0 x x x

10 0 0 1 0 10 1 1 0 1

B3 = E 0 E1E 3 + E 2 E 3 B 2 = E 0 E1E 2 + E 0 E 2 + E 1E 2

E1E0 E1E0

E3E2 00 01 11 10 E3E2 00 01 11 10

00 x x 0 x 00 x x 0 x

01 0 1 0 1 01 1 0 0 1

11 0 x x x 11 1 x x x

10 0 1 0 1 10 1 0 0 1

B1 = E 0 E1E 3 + E 2 E 3 B0 = E 0

A.C. Neve – Esercizi Digitali 17

Esercizio: Realizzare un convertitore di codice da BCD 8421 in BCD GRAY.

N B3 B2 B1 B0 G3 G2 G1 G0

0 0 0 0 0 0 0 0 0

1 0 0 0 1 0 0 0 1

2 0 0 1 0 0 0 1 1 La tabella descrive una macchina combinatoria

3 0 0 1 1 0 0 1 0 avente quattro ingressi per il codice BCD 8421 e

4 0 1 0 0 0 1 1 0 quattro uscite per il corrispondente codice BCD

5 0 1 0 1 1 1 1 0 GRAY.

6 0 1 1 0 1 0 1 0

7 0 1 1 1 1 0 1 1

8 1 0 0 0 1 0 0 1

9 1 0 0 1 1 0 0 0

- 1 0 1 0 x x x x

- 1 0 1 1 x x x x

- 1 1 0 0 x x x x

- 1 1 0 1 x x x x

- 1 1 1 0 x x x x

- 1 1 1 1 x x x x

B1B0 B1B0

B3B2 00 01 11 10 B3B2 00 01 11 10

00 0 0 0 0 00 0 0 0 0

01 0 1 1 1 01 1 1 0 0

11 x x x x 11 x x x x

10 1 1 x x 10 0 0 x x

G3 = B3 + B0 B 2 + B1B 2 G 2 = B1B 2

B1B0 B1B0

B3B2 00 01 11 10 B3B2 00 01 11 10

00 0 0 1 1 00 0 1 0 1

01 1 1 1 1 01 0 0 1 0

11 x x x x 11 x x x x

10 0 0 x x 10 1 0 x x

G1 = B1 + B 2 G 0 = B 0 B3 + B 0 B1B 2 + B 0 B1B 2 + B0 B1B 2 B 3

A.C. Neve – Esercizi Digitali 18

Esercizio: Realizzare un convertitore di codice da BCD GRAY in BCD 8421.

N G3 G2 G1 G0 B3 B2 B1 B0

0 0 0 0 0 0 0 0 0

1 0 0 0 1 0 0 0 1

3 0 0 1 0 0 0 1 1 La tabella descrive una macchina combinatoria

2 0 0 1 1 0 0 1 0 avente quattro ingressi per il codice BCD GRAY e

- 0 1 0 0 x x x x quattro uscite per il corrispondente codice BCD

- 0 1 0 1 x x x x 8421.

4 0 1 1 0 0 1 0 0

- 0 1 1 1 x x x x

9 1 0 0 0 1 0 0 1

8 1 0 0 1 1 0 0 0

6 1 0 1 0 0 1 1 0

7 1 0 1 1 0 1 1 1

- 1 1 0 0 x x x x

- 1 1 0 1 x x x x

5 1 1 1 0 0 1 0 1

- 1 1 1 1 x x x x

G1G0 G1G0

G3G2 00 01 11 10 G3G2 00 01 11 10

00 0 0 0 0 00 0 0 0 0

01 x x x 0 01 x x x 1

11 x x x 0 11 x x x 1

10 1 1 0 0 10 0 0 1 1

B3 = G 1G3 B 2 = G 2 + G1G3

G1G0 G1G0

G3G2 00 01 11 10 G3G2 00 01 11 10

00 0 0 1 1 00 0 1 0 1

01 x x x 0 01 x x x 0

11 x x x 0 11 x x x 1

10 0 0 1 1 10 1 0 1 0

B1 = G1G 2 B 0 = G 2G3 + G 0G1G3 + G 0G 1G3 + G 0G1G 2G 3 + G 0G1G3

A.C. Neve – Esercizi Digitali 19

Esercizio:

Realizzare un convertitore da CODICE GRAY in BINARIO LINEARE

Realizzare un convertitore da BINARIO LINEARE in CODICE GRAY

A.C. Neve – Esercizi Digitali 20

Reti sequenziali

Esercizio: Realizzare un contatore binario sincrono in avanti con modulo 5 e privo di protezione

antiblocco.

Un contatore modulo 5 richiede l’utilizzo di tre flip-flop in quanto 23>5.

Vengono utilizzati del flip-flop JK la cui tabella di transizione inversa è la seguente.

Qn → Qn+1 J K

0 0 0 x

0 1 1 x

1 0 x 1

1 1 x 0

L’evoluzione degli stati è descritta dalla seguente tabella :

Stato presente Stato futuro

Clock Q2 Q1 Q0 Q’2 Q’1 Q’0 J2 K2 J1 K1 J0 K0

0 0 0 0 0 0 1 0 x 0 x 1 x

1 0 0 1 0 1 0 0 x 1 x x 1

2 0 1 0 0 1 1 0 x x 0 1 x

3 0 1 1 1 0 0 1 x x 1 x 1

4 1 0 0 0 0 0 x 1 0 x 0 x

- 1 0 1 x x x x x x x x x

- 1 1 0 x x x x x x x x x

- 1 1 1 x x x x x x x x x

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 0 0 1 0 0 x x x x

1 x x x x 1 1 x x x

J 2 = Q0Q1 K2 =1

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 0 1 x x 0 x x 1 0

1 0 x x x 1 x x x x

J1 = Q0 K1 = Q0

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 1 x x 1 0 x 1 1 x

1 0 x x x 1 x x x x

J0 = Q2 K0 =1

A.C. Neve – Esercizi Digitali 21

Il relativo circuito risulta il seguente:

Il grafo che descrive l’evoluzione degli stati è invece il seguente:

111

000

Come si può notare, la scelta pur casuale delle

condizioni non specificate, è stata tale da non

generare alcun anello di conteggio secondario e

quindi il contatore è antiblocco.

100 001

011 010

110 101

Si evidenzia che, con una scelta sfortunata dei sottocubi sulle mappe di Karnaugh il risultato finale

sarebbe risultato fallimentare come si può notare in seguito:

A.C. Neve – Esercizi Digitali 22

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 0 0 1 0 0 x x x x

1 x x x x 1 1 x x x

J 2 = Q0Q1 K 2 = Q 0Q 1

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 0 1 x x 0 x x 1 0

1 0 x x x 1 x x x x

J1 = Q0 K1 = Q0

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 1 x x 1 0 x 1 1 x

1 0 x x x 1 x x x x

J 0 = Q1 + Q 2 K 0 = Q1 + Q 2

Con queste scelte si ottiene ancora il contatore richiesto che ha però il seguente grafo degli stati:

000

110

100 001

101 111

011 010

Il contatore così ottenuto presenta però un pericoloso anello di conteggio secondario.

Una tecnica più affidabile per impostare il progetto di un contatore sincrono consiste nell’assegnare,

fin dall’inizio, le transizioni degli stati non utilizzati in modo da confluire rapidamente nell’anello

di conteggio principale come si può notare nella tabella successiva.

In questo caso, gli stati non utilizzati vengono fatti confluire tutti nello stato iniziale 000.

A.C. Neve – Esercizi Digitali 23

Stato presente Stato futuro

Clock Q2 Q1 Q0 Q’2 Q’1 Q’0 J2 K2 J1 K1 J0 K0

0 0 0 0 0 0 1 0 x 0 x 1 x

1 0 0 1 0 1 0 0 x 1 x x 1

2 0 1 0 0 1 1 0 x x 0 1 x

3 0 1 1 1 0 0 1 x x 1 x 1

4 1 0 0 0 0 0 x 1 0 x 0 x

- 1 0 1 0 0 0 x 1 0 x x 1

- 1 1 0 0 0 0 x 1 x 1 0 x

- 1 1 1 0 0 0 x 1 x 1 x 1

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 0 0 1 0 0 x x x x

1 x x x x 1 1 1 1 1

J 2 = Q0Q1 K2 =1

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 0 1 x x 0 x x 1 0

1 0 0 x x 1 x x 1 1

J 1 = Q0Q 2 K1 = Q0 + Q 2

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 1 x x 1 0 x 1 1 x

1 0 x x 0 1 x 1 1 x

J0 = Q2 K0 =1

A.C. Neve – Esercizi Digitali 24

Il relativo diagramma degli stati è il seguente:

101 111 110

000

100 001

011 010

A.C. Neve – Esercizi Digitali 25

Esercizio: Realizzare un contatore sincrono modulo 6 i cui stati si evolvano in codice Gray.

Sono necessari tre flip-flop.

Risultando di tipo Gray, il codice di uscita dovrà essere monoprogressivo e ciclico per cui sarà

necessaria una particolare attenzione nella scelta degli stati da scartare.

Una possibile scelta è visibile è proposta nella seguente tabella di transizione degli stati:

Stato presente Stato futuro

Clock Q2 Q1 Q0 Q’2 Q’1 Q’0 J2 K2 J1 K1 J0 K0

0 0 0 0 0 0 1 0 x 0 x 1 x

1 0 0 1 0 1 1 0 x 1 x x 0

2 0 1 1 1 1 1 1 x x 0 x 0

3 1 1 1 1 0 1 x 0 x 1 x 0

4 1 0 1 1 0 0 x 0 0 x x 1

5 1 0 0 0 0 0 x 1 0 x 0 x

- 0 1 0 0 0 0 0 x x 1 0 x

- 1 1 0 1 0 0 x 0 x 1 0 x

ATTENZIONE AL RIEMPIMENTO DELLE MAPPE

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 0 0 1 0 0 x x x x

1 x x x x 1 1 0 0 0

J 2 = Q0Q1 K 2 = Q 0Q 1

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 0 1 x x 0 x x 0 1

1 0 0 x x 1 x x 1 1

J 1 = Q0Q 2 K1 = Q 0 + Q 2

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 1 x x 0 0 x 0 0 x

1 0 x x 0 1 x 1 0 x

J 0 = Q 1Q 2 K 0 = Q 1Q 2

A.C. Neve – Esercizi Digitali 26

Il grafo degli stati è il seguente:

101

110

111 100

011 000

010

001

A.C. Neve – Esercizi Digitali 27

Esercizio: Realizzare un contatore binario sincrono all’indietro con modulo 7

Sono necessari tre flip-flop.

In questo esempio, lo stato non utilizzato è quello 000.

La tabella di transizione degli stati risulta la seguente:

Stato presente Stato futuro

Clock Q2 Q1 Q0 Q’2 Q’1 Q’0 J2 K2 J1 K1 J0 K0

0 1 1 1 1 1 0 x 0 x 0 x 1

1 1 1 0 1 0 1 x 0 x 1 1 x

2 1 0 1 1 0 0 x 0 0 x x 1

3 1 0 0 0 1 1 x 1 1 x 1 x

4 0 1 1 0 1 0 0 x x 0 x 1

5 0 1 0 0 0 1 0 x x 1 1 x

6 0 0 1 1 1 1 1 x 1 x x 0

- 0 0 0 x x x x x x x x x

ATTENZIONE AL RIEMPIMENTO DELLE MAPPE

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 x 1 0 0 0 x x x x

1 x x x x 1 1 0 0 0

J 2 = Q1 K 2 = Q 0Q 1

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 x 1 x x 0 x x 0 1

1 1 0 x x 1 x x 0 1

J1 = Q 0 + Q 2 K1 = Q 0

Q1Q0 Q1Q0

Q2 00 01 11 10 Q2 00 01 11 10

0 x x x 1 0 x 0 1 x

1 1 x x 1 1 x 1 1 x

J0 =1 K 0 = Q1 + Q 2

A.C. Neve – Esercizi Digitali 28

Il relativo grafo degli stati è il seguente:

100 101 110

011 111 000

010 001

A.C. Neve – Esercizi Digitali 29

Esercizio: Realizzare un contatore binario sincrono in avanti con modulo 10 e privo di anelli

secondari di conteggio.

Sono necessari quattro flip-flop.

Una conveniente assegnazione degli stati esclusi risulta essere la seguente:

0110 0111 1000 1001

1100 0101 0000 1111

1101 0100 0011 0010 0001 1110

1011 1010

Stato presente Stato futuro

Clock Q3 Q2 Q1 Q0 Q’3 Q’2 Q’1 Q’0 J3 K3 J2 K2 J1 K1 J0 K0

0 0 0 0 0 0 0 0 1 0 x 0 x 0 x 1 x

1 0 0 0 1 0 0 1 0 0 x 0 x 1 x x 1

2 0 0 1 0 0 0 1 1 0 x 0 x x 0 1 x

3 0 0 1 1 0 1 0 0 0 x 1 x x 1 x 1

4 0 1 0 0 0 1 0 1 0 x x 0 0 x 1 x

5 0 1 0 1 0 1 1 0 0 x x 0 1 x x 1

6 0 1 1 0 0 1 1 1 0 x x 0 x 0 1 x

7 0 1 1 1 1 0 0 0 1 x x 1 x 1 x 1

8 1 0 0 0 1 0 0 1 x 1 0 x 0 x 1 x

9 1 0 0 1 0 0 0 0 x 1 0 x 0 x x 1

- 1 0 1 0 1 0 1 1 x 0 0 x x 0 1 x

- 1 0 1 1 0 1 0 0 x 1 1 x x 1 x 1

- 1 1 0 0 1 1 0 1 x 0 x 0 0 x 1 x

- 1 1 0 1 0 1 0 0 x 1 x 0 0 x x 1

- 1 1 1 0 1 1 1 1 x 0 x 0 x 0 1 x

- 1 1 1 1 0 0 0 0 x 1 x 1 x 1 x 1

A.C. Neve – Esercizi Digitali 30

Q1Q0 Q1Q0

Q3Q2 00 01 11 10 Q3Q2 00 01 11 10

00 0 0 0 0 00 x x x x

01 0 0 1 0 01 x x x x

11 x x x x 11 0 1 1 0

10 x x x x 10 0 1 1 0

J 3 = Q0Q1Q 2 K 3 = Q0

Q1Q0 Q1Q0

Q3Q2 00 01 11 10 Q3Q2 00 01 11 10

00 0 0 1 0 00 x x x x

01 x x x x 01 0 0 1 0

11 x x x x 11 0 0 1 0

10 0 0 1 0 10 x x x x

J 2 = Q0Q1 K 2 = Q0Q1

Q1Q0 Q1Q0

Q3Q2 00 01 11 10 Q3Q2 00 01 11 10

00 0 1 x x 00 x x 1 0

01 0 1 x x 01 x x 1 0

11 0 0 x x 11 x x 1 0

10 0 0 x x 10 x x 1 0

J 1 = Q0Q 3 K1 = Q0

Q1Q0 Q1Q0

Q3Q2 00 01 11 10 Q3Q2 00 01 11 10

00 1 x x 1 00 x 1 1 x

01 1 x x 1 01 x 1 1 x

11 1 x x 1 11 x 1 1 x

10 1 x x 1 10 x 1 1 x

J0 =1 K0 =1

A.C. Neve – Esercizi Digitali 31

Come si può notare, il circuito finale è dotato di una uscita ausiliaria di riporto per il collegamento

in cascata di più contatori (decadi di conteggio), di un ingresso di reset generale e di un ingresso di

abilitazione al conteggio.

Si evidenzia la particolare semplicità del circuito grazie alla opportuna scelta delle transizioni

assegnate agli stati non utilizzati.

A.C. Neve – Esercizi Digitali 32

Esercizio: Progettare un sistema che sia in grado di gestire tre pulsanti per tre concorrenti di un

telequiz e funzioni nel seguente modo:

Quando un concorrente schiaccia il suo pulsante prima degli altri due, si accende su un display il

numero ad esso associato (1,2,3) e contemporaneamente viene inibito il funzionamento degli altri

due pulsanti. Il sistema deve essere poi dotato di un quarto pulsante per il presentatore il cui

azionamento faccia spegnere totalmente il display e riabiliti il funzionamento dei tre pulsanti.

In linea di principio, il sistema dovrebbe utilizzare un numero di flip-flop almeno uguale al numero

di concorrenti. Le uscite dei flip-flop, adeguatamente codificate dovrebbero pilotare un driver BCD-

7segmenti e, contemporaneamente, inibire il funzionamento degli altri due pulsanti ad eccezione di

quello per il reset generale.

Una possibile soluzione è proposta nel circuito seguente.

Il sistema può essere resettato attivando il pulsante di RESET il quale genera uno zero logico sigli

ingressi di clear dei tre flip-flop.

In queste condizioni, le tre uscite Q 1, Q 2, Q 3 sono all’1 logico abilitando cos’ le tre porte AND a

lasciar passare gli impulsi provenienti dai tre pulsanti.

L’attivazione di uno qualsiasi dei tre pulsanti manderà all’1 logico l’uscita Q del flip-flop associato

ed a zero quella negata la quale, a sua volta, adrà a bloccare le uscite delle tre porte AND e quindi la

funzionalità dei restanti pulsanti.

A.C. Neve – Esercizi Digitali 33

Esercizio: Generatore digitale di numeri peudo casuali.

La generazione di numeri pseudo casuali si ottiene facendo uso di registri a scorrimento (shift

register) retroazionati riportando cioè in ingresso un segnale proveniente dalla combinazione dei bit

di uscita.

Un registro a scorrimento di M bit viene pilotato con un clock a frequenza fo.

L’ingresso del registro a scorrimento viene pilotato dall’uscita di una porta ex-OR i cui ingressi

sono collegati alle uscite del registro a scorrimento (N e M) una delle quali è sempre l’ultimo bit M.

La lunghezza massima della sequenza di numeri così ottenibile è pari a 2M-1 poiché lo stato formato

da tutti zero bloccherebbe la generazione dei numeri.

Questo valore della lunghezza della sequenza può essere ottenuto solo con una opportuna scelta dei

valori di N ed M.

Una volta generata l’intera sequenza, questa tornerà a ripetersi in modo periodico.

La tabella seguente descrive i valori di M ed N e le relative lunghezze delle sequenze ottenibili.

M N Lunghezza

4 3 15

5 3 31

6 5 63

7 6 127

9 5 511 1 2 3 N M

10 7 1023

11 9 2047

15 14 32767

20 17 1048575

25 22 33554431

31 28 2147483647

35 33 34359738367

39 35 549755813887

Nel caso in cui si volessero utilizzare dei registri di dimensione multipla di 8 bit, si dovranno

utilizzare più di due linee di retroazione come descritto dalla seguente tabella.

M N1 N2 N3 Lunghezza

8 4 5 6 255

16 4 13 15 65535

24 17 22 23 16777215

Nelle figure seguenti sono proposti i circuiti di due generatori di numeri pseudo casuali

rispettivamente ad 8 e 16 bit.

A.C. Neve – Esercizi Digitali 34

A.C. Neve – Esercizi Digitali 35

Esercizio: Realizzare il circuito di pilotaggio di un motore passo-passo unipolare.

Un motore passo-passo unipolare è

costituito da quattro avvolgimenti la cui

alimentazione consente lo spostamento o

il bloccaggio del rotore.

L’alimentazione delle quattro fasi, per

mezzo della modalità Full Step, deve

avvenire secondo opportune sequenze

applicate attraverso i quattro transistor

che operano in regime ON-OFF.

Nella tabella seguente è descritta la

sequenza degli stati assunti dai quattro

avvogimenti:

Step Q1 Q2 Q3 Q4 CCW

1 ON OFF ON OFF

2 ON OFF OFF ON

3 OFF ON OFF ON

4 OFF ON ON OFF CW

Il relativo diagramma temporale è il seguente:

Q1

t

Q2

t

Q3

t

Q4

CW

CCW

A secondo dell’evoluzione della sequenza degli stati, la rotazione potrà essere oraria (CW) oppure

antiorario (CCW).

Dal diagramma temporale si può anche notare che: lo stato Q2 è il negato dello stato Q1 e lo stato

Q4 è invece il negato dello stato Q3. Ciò implica che, le quattro fasi potranno essere prelevate dalle

uscite di solo due flip-flop e che i segnali da generare saranno soltanto Q1 e Q3

A.C. Neve – Esercizi Digitali 36

Ai fini della progettazione del contatore le quattro fasi ora esaminate saranno così indicate:

Q1 = Q1 Q 2 = Q 1 Q3 = Q 0 Q4 = Q 0

Le uscite dei due flip-flop avranno le seguenti sequenze temporali:

Q1 = 1 1 0 0

Q0 = 0 1 1 0

Dalle quali otterremo i seguenti grafi degli stati di due distinti contatori:

01 01

00 CCW 11 00 CW 11

10 10

La tabella di transizione del primo contatore (CCW) è la seguente:

Q1 Q0 Q1’ Q0’ J1 K1 J0 K0

1 0 1 1 x 0 1 x

1 1 0 1 x 1 x 0

0 1 0 0 0 x x 1

0 0 1 0 1 x 0 x

Dalla quale si ottiene:

J1 = Q 0 K1 = Q0 J 0 = Q1 K 0 = Q1

La tabella di transizione del secondo contatore (CW) è la seguente:

Q1 Q0 Q1’ Q0’ J1 K1 J0 K0

1 0 1 1 x 1 0 x

1 1 0 1 0 x 1 x

0 1 0 0 1 x x 0

0 0 1 0 x 0 x 1

Dalla quale si ottiene:

J1 = Q0 K1 = Q 0 J 0 = Q1 K 0 = Q1

Osservando i risultati ottenuti per i due tipi di contatori, si può notare dalle simmetrie dei valori che

non sarà necessario realizzare due circuiti separati ma, basterà aggiungere un selezionatore sulle

uscite dei due fòip-flop così da poter riportare sugli ingressi K le uscite Q o Q negata. L’ingresso J è

invece uguale al valore di K negato. L’ingresso si selezione sarà utilizzato per controllare il verso di

rotazione del motore. Nella figura seguente è proposto lo schema completo.

A.C. Neve – Esercizi Digitali 37

Un circuito alternativo ma più efficiente è invece il seguente.

A.C. Neve – Esercizi Digitali 38

You might also like

- Figure 1-1 Basic Gates: A B C A B C And: C A B Or: C A + BDocument39 pagesFigure 1-1 Basic Gates: A B C A B C And: C A B Or: C A + BbikisahuNo ratings yet

- Programmable Logic: Pal, PlaDocument26 pagesProgrammable Logic: Pal, PlaShiak AmeenullaNo ratings yet

- 07 Pal Pla RomDocument26 pages07 Pal Pla RomAnamika PancholiNo ratings yet

- 2 PC AND, 2 Inputs 6 Pcs Inputs, A, B & C 2 PC OR, 2 Inputs 2 PC OutputDocument1 page2 PC AND, 2 Inputs 6 Pcs Inputs, A, B & C 2 PC OR, 2 Inputs 2 PC OutputIrene TisoyNo ratings yet

- Homework 5Document11 pagesHomework 5Kateryna TernovaNo ratings yet

- FPGA Based Digital Logic Design ReviewDocument33 pagesFPGA Based Digital Logic Design ReviewInayat KhanNo ratings yet

- Ans To The Ques No - 2: How To Solve SOP With K-MapDocument5 pagesAns To The Ques No - 2: How To Solve SOP With K-MapMD. SABBIR ALAM 192-15-2847No ratings yet

- ECE-223, Solution For Assignment #8Document4 pagesECE-223, Solution For Assignment #8RUBIONo ratings yet

- Ans To The Ques No - 2: How To Solve SOP With K-MapDocument5 pagesAns To The Ques No - 2: How To Solve SOP With K-MapMD. SABBIR ALAM 192-15-2847No ratings yet

- RECUPERACIONDocument1 pageRECUPERACIONJuan PereiraNo ratings yet

- EE1D11 Instr w4 Quiz1Document20 pagesEE1D11 Instr w4 Quiz1Isa SpolerNo ratings yet

- Tarea 7 - Diseño Decodificador BCD A 7 Segmentos: IntegrantesDocument7 pagesTarea 7 - Diseño Decodificador BCD A 7 Segmentos: IntegrantesPaul SolanoNo ratings yet

- Module-7: Types of Programmable Logic Devices: PLA, PAL, CPLD, FPGA Generic ArchitectureDocument20 pagesModule-7: Types of Programmable Logic Devices: PLA, PAL, CPLD, FPGA Generic ArchitectureRobert RhesaNo ratings yet

- Seven Segment Display1Document7 pagesSeven Segment Display1Victor PrestonNo ratings yet

- Contoh Perancangan 7segment HuJanDocument1 pageContoh Perancangan 7segment HuJanDheny CahyonoNo ratings yet

- ICDocument2 pagesICraven witherNo ratings yet

- Actividad # 6 Respuestas: ̅ - (Con NOR)Document3 pagesActividad # 6 Respuestas: ̅ - (Con NOR)Valeria CardenasNo ratings yet

- Unit1_P1JSPSinghDocument61 pagesUnit1_P1JSPSinghAryan RathoreNo ratings yet

- DLDADocument30 pagesDLDAManoj NaikNo ratings yet

- 2 Funciones y SimplificacionesDocument4 pages2 Funciones y SimplificacionesedwardNo ratings yet

- BCD 12Document3 pagesBCD 12ADOLFO ANTONIO LANDAETA NAVARRONo ratings yet

- Mapas de KarnaughDocument10 pagesMapas de KarnaughYERSON ANTONIO MARQUEZ CORDONNo ratings yet

- Proyecto Final Circuitos Lógicos CombinatoriosDocument4 pagesProyecto Final Circuitos Lógicos CombinatoriosJuan Mateo Páez AlonsoNo ratings yet

- Cont AdoreDocument3 pagesCont AdoreOmar acNo ratings yet

- Display 7 Seg Compuertas LogicasDocument3 pagesDisplay 7 Seg Compuertas Logicasyordy julcahuancaNo ratings yet

- Computer Architecture: Introduction To CA Role of CA in Designs Performance Issues Now Review of Some DLD ConceptsDocument52 pagesComputer Architecture: Introduction To CA Role of CA in Designs Performance Issues Now Review of Some DLD ConceptsSaeed RehmanNo ratings yet

- Display 7 Seg Compuertas LogicasDocument3 pagesDisplay 7 Seg Compuertas LogicasDarney AguasNo ratings yet

- COE/EE 243 Sample Exam #4 SolutionDocument4 pagesCOE/EE 243 Sample Exam #4 SolutionM Naveed ShakirNo ratings yet

- Logic Cpe3 KmapDocument3 pagesLogic Cpe3 Kmapraven witherNo ratings yet

- Digtial CircuitDocument25 pagesDigtial CircuitChetan DahalNo ratings yet

- Digital Circuits: Ashok RanadeDocument39 pagesDigital Circuits: Ashok Ranadehirmay sandesaraNo ratings yet

- Digital Electronics BCD To 7segDocument2 pagesDigital Electronics BCD To 7segtatendaNo ratings yet

- LAB - Majority - Minority Circuits - 1-1Document7 pagesLAB - Majority - Minority Circuits - 1-1Anonymous eWMnRr70qNo ratings yet

- Programmable Logic: Adapted From Slides by R. H. KatzDocument21 pagesProgrammable Logic: Adapted From Slides by R. H. KatzDhaval KolapkarNo ratings yet

- Introduction To Gates AssignmentDocument6 pagesIntroduction To Gates AssignmentyasintharaNo ratings yet

- COE211 CH4 Combinational CircuitsDocument54 pagesCOE211 CH4 Combinational Circuitshm100hm100hm100No ratings yet

- College of Management & IT: Digital LogicDocument4 pagesCollege of Management & IT: Digital Logicswikar AcharyaNo ratings yet

- 8 Introduction - of - Karnough - MAP-dikonversiDocument27 pages8 Introduction - of - Karnough - MAP-dikonversimartinqNo ratings yet

- Chapter 4: Combinational Logic Solutions To Problems: (1, 5, 9, 12, 19, 23, 30, 33)Document14 pagesChapter 4: Combinational Logic Solutions To Problems: (1, 5, 9, 12, 19, 23, 30, 33)Gabriel FernandoNo ratings yet

- Mini Assignment4 SolutionDocument4 pagesMini Assignment4 SolutionHARIKESHNo ratings yet

- Canque, Lorenzo VDocument2 pagesCanque, Lorenzo VLorenzo CanqueNo ratings yet

- Seven Segments ReportDocument12 pagesSeven Segments ReportJun TobiasNo ratings yet

- Boolean logic expressionsDocument4 pagesBoolean logic expressionsValentina RobayoNo ratings yet

- KmapsDocument8 pagesKmapsSrinu TeluguNo ratings yet

- Atividade T4Document2 pagesAtividade T4Marcos TaylonNo ratings yet

- Digital Logic Circuits: Combinational Logic Analysis and ApplicationsDocument64 pagesDigital Logic Circuits: Combinational Logic Analysis and ApplicationsSanthoshkumar SethuramanNo ratings yet

- ECE213 Solved QuestionsDocument89 pagesECE213 Solved QuestionsJundeep SharmaNo ratings yet

- Adder SubtractorDocument11 pagesAdder SubtractorJavedNo ratings yet

- Class 2Document90 pagesClass 2Great GuyNo ratings yet

- Simplification of Boolean Functions: Example 1Document15 pagesSimplification of Boolean Functions: Example 1Orville BalangueNo ratings yet

- SW FinalsDocument4 pagesSW FinalsEdith CastilloNo ratings yet

- Programmable Logic Design (PLD)Document31 pagesProgrammable Logic Design (PLD)swetha gpNo ratings yet

- Chapter 4 - Combinational Logic Solutions To Problems - (1, 5, 9, 12, 23, 30)Document10 pagesChapter 4 - Combinational Logic Solutions To Problems - (1, 5, 9, 12, 23, 30)Sean Matthew L. OcampoNo ratings yet

- 4-Bit Synchronous Counter: Final ProjectDocument7 pages4-Bit Synchronous Counter: Final Projectahmed IsmailNo ratings yet

- Rassoul DialloDocument5 pagesRassoul DialloRassoul DialloNo ratings yet

- Practical File Digital Systems and Applications (Lab) - Experiment 5 Four Variable K-MapDocument10 pagesPractical File Digital Systems and Applications (Lab) - Experiment 5 Four Variable K-MapDevendra SheoranNo ratings yet

- Capter 5Document53 pagesCapter 5surafel5248No ratings yet

- Simplifying Bolean Functions in POS FormDocument8 pagesSimplifying Bolean Functions in POS FormJimmy OrajayNo ratings yet

- Exp 5 Mid OelDocument7 pagesExp 5 Mid OelDelta kuNo ratings yet

- Answers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesFrom EverandAnswers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesRating: 1.5 out of 5 stars1.5/5 (2)

- AD590Document16 pagesAD590Jeziel Vazquez NavaNo ratings yet

- LCL Filter Design and Performance Analysis For Grid Interconnected SystemsDocument7 pagesLCL Filter Design and Performance Analysis For Grid Interconnected SystemsVito LNo ratings yet

- EMI Filter Volume Minimization of A Three-Phase, Three-Level T-Type PWM Converter SystemDocument9 pagesEMI Filter Volume Minimization of A Three-Phase, Three-Level T-Type PWM Converter SystemVito LNo ratings yet

- Littelfuse - EV Charging SolutionsDocument87 pagesLittelfuse - EV Charging SolutionsVito LNo ratings yet

- Optimal Design of LCL Harmonic Filters For Three-Phase PFC RectifiersDocument13 pagesOptimal Design of LCL Harmonic Filters For Three-Phase PFC RectifiersVito LNo ratings yet

- Design of LCL FilterDocument32 pagesDesign of LCL FilterJuanNo ratings yet

- 15 ThreePhase Common Mode PDFDocument12 pages15 ThreePhase Common Mode PDFVito LNo ratings yet

- 302Document3 pages302Anirban GhoseNo ratings yet

- Sic Power Devices and Modules: Application NoteDocument41 pagesSic Power Devices and Modules: Application NoteVito LNo ratings yet

- 302Document3 pages302Anirban GhoseNo ratings yet

- Design Rules For Paralleling of Silicon Carbide Power MosfetsDocument6 pagesDesign Rules For Paralleling of Silicon Carbide Power MosfetsVito LNo ratings yet

- MOSFET Power Losses Calculation Using The Data-Sheet ParametersDocument23 pagesMOSFET Power Losses Calculation Using The Data-Sheet ParametersElvis Yu0% (1)

- AN200907 Advantagesof NPCDocument3 pagesAN200907 Advantagesof NPCPon PerumalNo ratings yet

- 3-Phase Power Factor Correction, Using Vienna Rectifier ApproachDocument13 pages3-Phase Power Factor Correction, Using Vienna Rectifier Approachvdiaz1No ratings yet

- BookOfKnowledge en WEBDocument287 pagesBookOfKnowledge en WEBChand RNo ratings yet

- 3-Phase Power Factor Correction, Using Vienna Rectifier ApproachDocument13 pages3-Phase Power Factor Correction, Using Vienna Rectifier Approachvdiaz1No ratings yet

- EMI in Power SuppliesDocument16 pagesEMI in Power SuppliesHansraj AkilNo ratings yet

- PDFDocument11 pagesPDFch srinivas reddyNo ratings yet

- Sloa 101 BDocument17 pagesSloa 101 Brute silvaNo ratings yet

- Calculation of Power Loss: (Synchronous)Document4 pagesCalculation of Power Loss: (Synchronous)AmmarArshadNo ratings yet

- Sloa 101 BDocument17 pagesSloa 101 Brute silvaNo ratings yet

- Achieve Bidirectional Control and Protection Through Back-To-Back Connected Efuse DevicesDocument10 pagesAchieve Bidirectional Control and Protection Through Back-To-Back Connected Efuse DevicesAman AgarwalNo ratings yet

- 99 Ways To Improve Your English PDFDocument81 pages99 Ways To Improve Your English PDFHakan Citlak100% (1)

- EMC Issues in Cars With Electric Drives: S. Guttowski, S. Weber, E. Hoene, W. John, H. ReichlDocument6 pagesEMC Issues in Cars With Electric Drives: S. Guttowski, S. Weber, E. Hoene, W. John, H. ReichlVito LNo ratings yet

- PDFDocument11 pagesPDFch srinivas reddyNo ratings yet

- MosfetDocument13 pagesMosfetSristick100% (3)

- Achieve Bidirectional Control and Protection Through Back-To-Back Connected Efuse DevicesDocument10 pagesAchieve Bidirectional Control and Protection Through Back-To-Back Connected Efuse DevicesAman AgarwalNo ratings yet

- Mosfet Igbt BJT Difference and ApplicationDocument5 pagesMosfet Igbt BJT Difference and ApplicationSangammeshwra AbNo ratings yet

- Design SMPS TransformersDocument11 pagesDesign SMPS TransformersSuhail AhmedNo ratings yet

- Product+Catalogue+2021+New+Final PreviewDocument34 pagesProduct+Catalogue+2021+New+Final Previewsanizam79No ratings yet

- Work Text INGE09: Understanding The SelfDocument24 pagesWork Text INGE09: Understanding The SelfFrancis Dave MabborangNo ratings yet

- Otimizar Windows 8Document2 pagesOtimizar Windows 8ClaudioManfioNo ratings yet

- Base Case Analysis Best CaseDocument6 pagesBase Case Analysis Best CaseMaphee CastellNo ratings yet

- DLL in Science 5 Q1 W1Document3 pagesDLL in Science 5 Q1 W1Rhinalyn Andaya Barberan100% (2)

- Professor Barry T Hart - BiographyDocument1 pageProfessor Barry T Hart - BiographyadelNo ratings yet

- Technical ManualDocument32 pagesTechnical ManualIstvan MadacsyNo ratings yet

- Social Studies Bece Mock 2024Document6 pagesSocial Studies Bece Mock 2024awurikisimonNo ratings yet

- C27 and C32 Generator Set Engines - Troubleshooting - RENR9348-01 - Jan 2007 - CATERPILLARDocument180 pagesC27 and C32 Generator Set Engines - Troubleshooting - RENR9348-01 - Jan 2007 - CATERPILLARpevare85% (27)

- PricelistDocument2,276 pagesPricelistadilcmsNo ratings yet

- IEC Developer version 6.n compiler error F1002Document6 pagesIEC Developer version 6.n compiler error F1002AnddyNo ratings yet

- Autodesk Revit 2014 ContentDocument6 pagesAutodesk Revit 2014 ContentGatot HardiyantoNo ratings yet

- Review of Train Wheel Fatigue LifeDocument15 pagesReview of Train Wheel Fatigue Lifeabdurhman suleimanNo ratings yet

- Autonomy Necessity and Love by Harry FrankfurtDocument14 pagesAutonomy Necessity and Love by Harry FrankfurtjamesdigNo ratings yet

- Physice 2013 Unsolved Paper Outside Delhi PDFDocument7 pagesPhysice 2013 Unsolved Paper Outside Delhi PDFAbhilashaNo ratings yet

- Practice Exercise For Final Assessment 2221Document3 pagesPractice Exercise For Final Assessment 2221Guneet Singh ChawlaNo ratings yet

- Lecture 8: Dynamics Characteristics of SCR: Dr. Aadesh Kumar AryaDocument9 pagesLecture 8: Dynamics Characteristics of SCR: Dr. Aadesh Kumar Aryaaadesh kumar aryaNo ratings yet

- Testing Methods for Selectivity Bias in Panel Data ModelsDocument24 pagesTesting Methods for Selectivity Bias in Panel Data Modelsstehta16529No ratings yet

- Gathering Statistical DataDocument8 pagesGathering Statistical DataianNo ratings yet

- Company Profile Nadal en PDFDocument2 pagesCompany Profile Nadal en PDFkfctco100% (1)

- Datasheet 1MBH 50D - 60Document5 pagesDatasheet 1MBH 50D - 60jtec08No ratings yet

- Nikon SMZ 10A DatasheetDocument3 pagesNikon SMZ 10A DatasheetNicholai HelNo ratings yet

- Latihan Soal ADS Bab 14-16Document1 pageLatihan Soal ADS Bab 14-16nadea06_20679973No ratings yet

- Quick Guide in The Preparation of Purchase Request (PR), Purchase Order (PO) and Other Related DocumentsDocument26 pagesQuick Guide in The Preparation of Purchase Request (PR), Purchase Order (PO) and Other Related DocumentsMiguel VasquezNo ratings yet

- Supply Chain Management 5th Edition Chopra Solutions ManualDocument3 pagesSupply Chain Management 5th Edition Chopra Solutions Manualdammar.jealousgvg6100% (18)

- Syllabus - EU Institutions and Comparative Political System - 2023springDocument10 pagesSyllabus - EU Institutions and Comparative Political System - 2023springreif annieNo ratings yet

- A320 - Command Upgrade - Trainee1 01 Jan 24Document19 pagesA320 - Command Upgrade - Trainee1 01 Jan 24Ankit YadavNo ratings yet

- History of CAD - CAE CompaniesDocument5 pagesHistory of CAD - CAE CompaniesAntonio C. KeithNo ratings yet

- Free Fall ExperimentDocument31 pagesFree Fall ExperimentLeerzejPuntoNo ratings yet

- 5.talisayon Chapter 3Document12 pages5.talisayon Chapter 3Jinky Marie TuliaoNo ratings yet