Professional Documents

Culture Documents

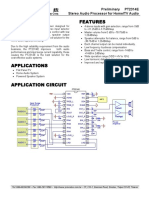

4-Ch Audio Proc w/ Vol, Bass, Treble & Balance Control

Uploaded by

DamianOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

4-Ch Audio Proc w/ Vol, Bass, Treble & Balance Control

Uploaded by

DamianCopyright:

Available Formats

4-Channel Input Audio Processor 7314

DESCRIPTION

7314 is a four-channel input digital audio processor utilizing CMOS Technology. Volume, Bass, Treble

and Balance are incorporated into a single chip. Loudness Function and Selectable Input Gain are also

provided to build a highly effective electronic audio processor having the highest performance and

reliability with the least external components. All functions are programmable using the I2C Bus. The

pin assignments and application circuit are optimized for easy PCB layout and cost saving advantage

for audio application.

FEATURES

• CMOS technology

• Least external components

• Treble and bass control

• Loudness function

• 4 stereo inputs with selectable input gain

• Input/output for external noise reduction system/equalizer

• 2 independent speaker controls for balance control

• Independent mute function

• Volume control in 1.25 dB/step

• Low distortion

• Low noise and DC stepping

• Controlled by I2C bus micro-processor interface

• Available in 28 Pins, DIP or SOP

APPLICATIONS

• Car stereo (Audio)

• Hi-Fi audio system

Note: Purchase of I2C Component of Princeton Technology Corporation (PTC) conveys a license

under Philips I2C Patent Right to use these components in any I2C System, provided that the system

conforms to the I2C Standard Specification defined by Philips

7314 V1.0 -1- January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

BLOCK DIAGRAM

TREBLE_L

LOUD_L

BOUT_L

BIN_L

LOUT

LIN

RB

LIN1 Speaker

LIN1 ATT

Volume &

LIN2 Bass Treble

LIN2 Loudness

OUT_L

LIN3

LIN3 Input

Mute

LIN4

LIN4 Selector

RIN1 &

RIN1

RIN2 Gain Serial Bus Decoder & Latches

RIN2 CLK

RIN3 Control DATA

RIN3

RIN4 DGND

RIN4

Speaker

Volume & ATT

Bass Treble

Loudness

OUT_R

Mute

RB

Supply

RIN

VDD

AGND

REF

ROUT

BOUT_R

LOUD_R

BIN_R

TREBLE_R

7314 V1.0 -2- January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

PIN CONFIGURATION

VDD 1 28 REF

AGND 2 27 CLK

TREB_L 3 26 DATA

TREB_R 4 25 DGND

RIN 5 24 OUT_L

ROUT 6 23 OUT_R

LOUD_R 7 7314 22 BOUT_R

RIN4 8 21 BIN_R

RIN3 9 20 BOUT_L

RIN2 10 19 BIN_L

RIN1 11 18 LOUT

LOUD_L 12 17 LIN

LIN4 13 16 LIN1

LIN3 14 15 LIN2

7314 V1.0 -3- January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

PIN DESCRIPTION

Pin Name I/O Description Pin No.

VDD - Supply Input Voltage 1

AGND - Analog Ground 2

TREB_L I Left Channel Input for Treble Controller 3

TREB_R I Right Channel Input for Treble Control 4

RIN I Audio Processor Right Channel Input 5

ROUT O Gain Output and Input Selector for Right Channel 6

LOUD_R I Right Channel Loudness Input 7

RIN4 I Right Channel Input 4 8

RIN3 I Right Channel Input 3 9

RIN2 I Right Channel Input 2 10

RIN1 I Right Channel Input 1 11

LOUD_L I Left Channel Loudness Input 12

LIN4 I Left Channel Input 4 13

LIN3 I Left Channel Input 3 14

LIN2 I Left Channel Input 2 15

LIN1 I Left Channel Input 1 16

LIN I Audio Processor Left Channel Input 17

LOUT O Gain Output and Input Selector for Left Channel 18

BIN_L I Left Channel Input for Bass Controller 19

BOUT_L O Left Bass Controller Output Channel 20

BIN_R I Right Channel Input for Bass Controller 21

BOUT_R O Right Channel Output for Bass Controller 22

OUT_R O Right Speaker Output 23

OUT_L O Left Speaker Output 24

DGND - Digital Ground 25

DATA I Control Data Input 26

CLK I Clock Input for Serial Data Transmission 27

REF - Analog Reference Voltage (1/2 VDD) 28

7314 V1.0 -4- January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

FUNCTIONAL DESCRIPTION

BUS INTERFACE

Data are transmitted to and from the microprocessor to the 7314 via the DATA and CLK. The DATA

and CLK make up the BUS Interface. It should be noted that the pull-up resistors must be connected to

the positive supply voltage.

DATA VALIDITY

A data on the DATA Line is considered valid and stable only when the CLK Signal is in HIGH State. The

HIGH and LOW State of the DATA Line can only change when the CLK signal is LOW. Please refer to

the figure below.

DATA

CLK

DATA LINE DATA

STABLE, CHANGE

DATA VALID ALLOWED

START AND STOP CONDITIONS

A Start Condition is activated when

1) the CLK is set to HIGH and

2) DATA shifts from HIGH to LOW State.

The Stop Condition is activated when

1) CLK is set to HIGH and

2) DATA shifts from LOW to HIGH State. Please refer to the timing diagram below.

CLK

DATA

START ST OP

BYTE FORMAT

Every byte transmitted to the DATA Line consist of 8 bits. Each byte must be followed by an

Acknowledge Bit. The MSB is transmitted first.

7314 V1.0 -5- January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

ACKNOWLEDGE

During the Acknowledge Clock Pulse, the master (µP) puts a resistive HIGH level on the DATA Line.

The peripheral (audio processor) that acknowledges has to pull-down (LOW) the DATA line during the

Acknowledge Clock Pulse so that the DATA Line is in a Stable Low State during this Clock Pulse.

Please refer to the diagram below.

CLK 1 2 3 4 7 8 9

DATA MSB

AC KNOWLED GE MENT

START F ROM RECE IV ER

The audio processor that has been addressed has to generate an acknowledge after receiving each

byte, otherwise, the DATA Line will remain at the High Level during the ninth (9th) Clock Pulse. In this

case, the master transmitter can generate the STOP Information in order to abort the transfer.

TRANSMISSION WITHOUT ACKNOWLEDGE

If you want to avoid the acknowledge detection of the audio processor, a simpler µP transmission may

be used. Wait one clock and do not check the slave acknowledge of this same clock then send the new

data. If you use this approach, there are greater chances of faulty operation as well as decrease in

noise immunity.

INTERFACE PROTOCOL

The interface protocol consists of the following (see diagram below):

• A Start Condition

• A Chip Address Byte including the 7314 address. The 8th Bit of the Byte must be “0”. 7314 must

always acknowledge the end of each transmitted byte.

• A Data Sequence (N-Bytes + Acknowledge)

• A Stop Condition

7314 Address

MSB First Byte LSB MSB LSB MSB LSB

START 1 0 0 0 1 0 0 0 ACK DATA ACK DATA ACK STOP

DATA TRANSMITTED (N-BYTES+ACKNOWLEDGE)

Note:

ACK = ACKNOWLEDGE

MAX. CLOCK SPEED = 100KBITS/S

7314 V1.0 -6- January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

SOFTWARE SPECIFICATION

7314 ADDRESS

7314 Address is shown below.

1 0

0 0 0 1 0 0

MSB LSB

DATA BYTES

MSB LSB Function

0 0 B2 B1 B0 A2 A1 A0 Volume Control

1 1 0 B1 B0 A2 A1 A0 Speaker ATT L

1 1 1 B1 B0 A2 A1 A0 Speaker ATT R

0 1 0 G1 G0 S2 S1 S0 Audio Switch

0 1 1 0 C3 C2 C1 C0 Bass Control

0 1 1 1 C3 C2 C1 C0 Treble Control

where Ax = 1.25 dB steps; Bx = 10 dB steps; Cx = 2 dB steps; Gx = 3.75 dB/steps

VOLUME

The table below gives a detailed description of the Volume Data Bytes. For example, a volume of -37.5

dB is given by 0 0 0 1 1 1 1 0.

MSB LSB Function

0 0 B2 B1 B0 A2 A1 A0 Volume 1.25 dB steps

0 0 0 0

0 0 1 -1.25

0 1 0 -2.5

0 1 1 -3.75

1 0 0 -5

1 0 1 -6.25

1 1 0 -7.5

1 1 1 -8.75

0 0 B2 B1 B0 A2 A1 A0 Volume 10dB steps

0 0 0 0

0 0 1 -10

0 1 0 -20

0 1 1 -30

1 0 0 -40

1 0 1 -50

1 1 0 -60

1 1 1 -70

7314 V1.0 -7- January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

SPEAKER ATTENUATORS

The table below gives a detailed description of the speaker attenuators data bytes. For example, an

attenuation of 30dB on the Speaker R (Right) is given by: 1 1 1 1 1 0 0 0.

MSB LSB Function

1 1 0 B1 B0 A2 A1 A0 Speaker L

1 1 1 B1 B0 A2 A1 A0 Speaker R

0 0 0 0

0 0 1 -1.25

0 1 0 -2.5

0 1 1 -3.75

1 0 0 -5

1 0 1 -6.25

1 1 0 -7.5

1 1 1 -8.75

0 0 0

0 1 -10

1 0 -20

1 1 -30

1 1 1 1 1 Mute

AUDIO SWITCH DATA BYTE

The following table shows the detailed description of the Audio Switch Data Bytes. For example, a

Stereo 1 Input with Gain of +11.25 dB Loudness ON is given by: 0 1 0 0 0 0 0 0.

MSB LSB Function

0 1 0 G1 G0 S2 S1 S0 Audio Switch

0 0 Stereo 1

0 1 Stereo 2

1 0 Stereo 3

1 1 Stereo 4

0 Loudness ON

1 Loudness OFF

0 0 +11.25dB

0 1 +7.5dB

1 0 +3.75dB

1 1 0dB

7314 V1.0 -8- January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

BASS AND TREBLE DATA BYTES

The following table shows a detailed description of the Bass and Treble Data Byte. For example a

Treble at -12dB is given by: 0 1 1 1 0 0 0 1.

MSB LSB Function

0 1 1 0 C3 C2 C1 C0 Bass

0 1 1 1 C3 C2 C1 C0 Treble

0 0 0 0 -14

0 0 0 1 -12

0 0 1 0 -10

0 0 1 1 -8

0 1 0 0 -6

0 1 0 1 -4

0 1 1 0 -2

0 1 1 1 0

1 1 1 1 0

1 1 1 0 2

1 1 0 1 4

1 1 0 0 6

1 0 1 1 8

1 0 1 0 10

1 0 0 1 12

1 0 0 0 14

Unit: dB

7314 V1.0 -9- January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Rating Unit

Operating supply voltage Vs 10.5 V

Operating temperature Topr -40 to +85 ℃

Storage temperature Tstg -65 to +150 ℃

QUICK REFERENCE DATA

Parameter Symbol Min. Typ. Max. Unit

Supply voltage Vs 6 9 10 V

Max. input signal handling VCL 2 2.5 Vrms

Total harmonic distortion

THD 0.07 0.15 %

(V=1Vrms, f=1KHz)

Signal to noise ratio S/N 95 dB

Channel separation ( f=1KHz) Sc 85 dB

Volume control 1.25dB step -75 0 dB

Bass & treble control 2dB step -14 +14 dB

Balance control 1.25dB step -37.5 0 dB

Input gain 3.75dB step 0 11.25 dB

Mute attenuation 85 dB

7314 V1.0 - 10 - January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

ELECTRICAL CHARACTERISTICS

(Unless specified: Ta=25℃, Vc=9V, RL=10KΩ, Rg = 600Ω, all controls flat (G=0), f=1KHz)

Parameter Symbol Test Condition Min. Typ. Max. Unit

Supply

Supply voltage Vcc 6 9 10 V

Supply current Is 30 40 mA

Input Selectors

Input resistance RII Input 1,2,3 80 100 120 KΩ

Clipping level VCL Av=-8.75 dB ; d=0.3% 2 2.5 Vrms

Input separation (2) SIN 80 100 dB

Min. input gain GINmin -1 0 1 dB

Max. input gain GINmax 11.25 dB

Volume Control

Input resistance RIV 30 40 50 KΩ

Control range CRANGE 65 70 75 dB

Min. attenuation AVMIN -1 0 1 dB

Max. attenuation AVMAX 65 70 75 dB

Step resolution ASTEP 0.5 1.25 1.75 dB

AV=0 to -20dB -1.25 1.25 dB

Attenuation set error EA 0

AV=-20 to –60dB -3.0 2 dB

Speaker Attenuators

Control range CRANGE 35 37.5 40 dB

Step resolution SSTEP 0.5 1.25 1.75 dB

Attenuation set error EA 1.5 dB

Output mute

AMUTE 75 85 dB

attenuation

Bass Control (1)

Control range Gb Max. Boost/Cut ±12 ±14 ±16 dB

Step resolution BSTEP 1 2 3 dB

Internal feedback

RB 34 44 58 KΩ

resistance

Treble Control (1)

Control range Gt Max. Boost/Cut ±13 ±14 ±15 dB

Step resolution TSTEP 1 2 3 dB

7314 V1.0 - 11 - January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

Parameter Symbol Test Condition Min. Typ. Max. Unit

Audio Outputs

Clipping level VOCL d=0.3% 2 2.5 Vrms

Output resistance ROUT 1.7 1.9 2.1 Ω

DC voltage level VOUT 4.2 4.5 4.8 V

General

BW=20-20KHz, flat -97 dB

Output noise eNO Output Muted

-92 dB

All gains=0dB

A Curve All

-100 dB

Gains=0dB

All Gains=0dB

Signal to noise ratio S/N 95 dB

Vo=1Vrms

AV=0, VIN=1Vrms 0.1 0.3 %

AV=-8.75dB,

Distortion d 0.07 0.15 %

VIN=1Vrms

AV=-8.75dB,

0.03 0.1 %

VIN=0.3Vrms

Channel separation

Sc 80 90 dB

left/right

Bus Inputs

Input low voltage VIL 1 V

Input high voltage VIH 3 V

Input current IIN -5 +5 µA

Output voltage SDA

Vo Io=1.6mA 0.4 V

acknowledge

Notes:

1. For the Bass and Treble Response, please, refer to the diagram below. The center frequency and

quality of the resonance behavior can be selected by the external circuitry. A standard first order

bass response can realized by a standard feedback network.

2. The selected input is grounded thru the 2.2µF capacitor.

7314 V1.0 - 12 - January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

RESPONSE (dB)

FREQUENCY (HZ)

Typical Tone Response (with the ext. Components indicated in the test circuit)

dB

Hz

Loudness vs Volume Attenuation Frequency Response (C12=C13=100nF)

7314 V1.0 - 13 - January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

OPEN

10n

100n

dB 56n

33n

220n

Shorted to VREF

Hz

C12, C13 vs Loudness Frequency Response

(Volume=-40dB, All other controls are flat)

7314 V1.0 - 14 - January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

APPLICATION CIRCUIT

R2

5.6K

C11

2.2µ

MCU C13 C16 C17 C19

+ 100n 100n 100n 2.7n

C5 2.2µ 25 26 27 18 17 12 20 19 3

+ R

LIN

DGND

LOUD_L

BOUT_L

BIN_L

TREB_L

LOUT

DATA

CLK

11 RIN1

AM/FM

Tuner + R

16 LIN1

C1 2.2µ C20

C6 2.2µ 10µ

+ R

10 RIN2 OUT_R 23

CD +

Player + R

15 LIN2

C2 2.2µ

C7 2.2µ+ R

7314

9 RIN3 C21

Tape 10µ

+ R OUT_L 24

14 LIN3

+

C3 2.2µ

C8 2.2µ+ R

8 RIN4

Aux + R

LOUD_R

BOUT_R

TREB_R

13 LIN4

BIN_R

AGND

ROUT

VDD

REF

RIN

C4 2.2µ

1 2 28 6 5 7 22 21 4

+ +

C9 C12 C14 C15 C18

VDD 22µ 100n 100n 100n 2.7n

C10

2.2µ

R1

5.6K

Notes:

1. It is suggested that you use Mylar Capacitor for capacitors, C12 ~ C19.

2. Resistor (R) Range = 2.0KΩ to 3.6KΩ

3. Recommended Value of Resistor ( R ) = 2.4KΩ

7314 V1.0 - 15 - January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

ORDER INFORMATION

Valid Part Number Package Type Top Code

7314-D (L) 28 Pins, DIP, 300mil 7314-D

7314 (L) 28 Pins, SOP, 300mil 7314

Notes:

1. (L), (C) or (S) = Lead Free

2. The Lead Free mark is put in front of the date code.

7314 V1.0 - 16 - January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

PACKAGE INFORMATION

28 PINS, DIP, 300 MIL

7314 V1.0 - 17 - January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

Symbol Min. Nom. Max.

A - - 0.210

A1 0.015 - -

A2 0.115 0.130 0.195

b 0.014 0.018 0.022

b1 0.014 0.018 0.020

b2 0.045 0.060 0.070

b3 0.030 0.039 0.045

c 0.008 0.010 0.014

c1 0.008 0.010 0.011

D 1.345 1.365 1.400

D1 0.005 - -

E 0.300 0.310 0.325

E1 0.240 0.250 0.280

e 0.100 BSC

eA 0.300 BSC

eB - - 0.430

eC 0.000 - 0.060

L 0.115 0.130 0.150

Notes:

1. All dimensions are in INCHES.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension A, A1 and L are measured with the package seated in JEDEC Seating Plane Gauge

GS-3.

4. D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions

shall not exceed 0.010 inch.

5. E and eA measured with the leads constrained to be perpendicular to datum -C-.

6. eB and eC are measured at the lead tips with the leads constrained. N is the number of terminal

positions (N=28)

7. Pointed or rounded lead tips are preferred to ease insertion.

8. b2 and b3 maximum dimensions do not include dambar protrusions. Dambar protrusions shall

not exceed 0.010” (0.25mm).

9. This variation is a ½ lead package.

10. Distance between leads including dambar protrusions to be 0.005 inch minimum.

11. Datum plane -H- coincident with the bottom of lead where lead exits body.

12. Refer to JEDEC MS-001 Variation BF.

JEDEC is the registered trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

7314 V1.0 - 18 - January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

28 PINS, SOP, 300 MIL

INDEX H .25 (.010) M B M

AREA

E

-B-

1 2 3

L

SEATING PLANE h X 45

-A- D A

-C-

∞

A1 C

-e-

B .10 (.004)

.25 (.010) M C A M B S

Symbol Min. Nom. Max.

A 2.35 - 2.65

A1 0.10 - 0.30

B 0.33 - 0.51

C 0.23 - 0.32

D 17.70 - 18.10

E 7.40 - 7.60

e 1.27 bsc.

H 10.00 - 10.65

h 0.25 - 0.75

L 0.40 - 1.27

α 0° - 8°

7314 V1.0 - 19 - January, 2007

Free Datasheet http://www.datasheet4u.com/

4-Channel Input Audio Processor 7314

Notes:

1. Dimensioning and tolerancing per ANSI Y14.5M-1982.

2. Dimension “D” does not include mold flash, protrusions or gate burrs. Mold Flash, protrusion or

gate burrs shall not exceed 0.15 mm (0.006 in) per side.

3. Dimension “E” does not include interlead flash or protrusions. Interlead flash or protrusions shall

not exceed 0.25 mm (0.010 in) per side.

4. The chamfer on the body is optional. It is not present, a visual index feature must be located

within the crosshatched area.

5. “L” is the length of the terminal for soldering to a substrate.

6. N is the number of the terminal positions (N=28)

7. The lead width “B” as measured 0.36 mm (0.014 in) or greater above the seating plane, shall not

exceed a maximum value of 0.61 mm (0.24 in).

8. Controlling dimension:MILLIMETER.

9. Refer to JEDEC MS-013, Variation AE.

JEDEC is the trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION.

7314 V1.0 - 20 - January, 2007

Free Datasheet http://www.datasheet4u.com/

You might also like

- CAT C7 Prefix C7S Wiring DiagramsDocument8 pagesCAT C7 Prefix C7S Wiring DiagramsDiego chanez100% (2)

- Henney - The Radio Engineering Handbook 3 Ed 1941Document964 pagesHenney - The Radio Engineering Handbook 3 Ed 1941Carlo StrocchiNo ratings yet

- Presentation 1Document8 pagesPresentation 1hadin0151No ratings yet

- DUL and DUS (2014) PDFDocument18 pagesDUL and DUS (2014) PDFАлексей РепехаNo ratings yet

- Brochure Industrial Ethernet Switches EnglishDocument48 pagesBrochure Industrial Ethernet Switches EnglishMarcelo Rodrigo BovoNo ratings yet

- Scoop Coupling Panel Control CKT DrawingDocument7 pagesScoop Coupling Panel Control CKT DrawingRavi Kumar ramanNo ratings yet

- Description: 4 Channel Audio Processor PT2313LDocument25 pagesDescription: 4 Channel Audio Processor PT2313LCarlos RamirezNo ratings yet

- Description Features: PT7314E Stereo Audio Processor For Home/TV AudioDocument16 pagesDescription Features: PT7314E Stereo Audio Processor For Home/TV AudioJose CazonNo ratings yet

- 8-Channel Premium Mic/Line Mixer: Owner'S ManualDocument28 pages8-Channel Premium Mic/Line Mixer: Owner'S Manualserariro-1No ratings yet

- Dolby Pro Logic Surround Decoder With Discrete 5.1ch Analog InputDocument24 pagesDolby Pro Logic Surround Decoder With Discrete 5.1ch Analog InputChanchal RoyNo ratings yet

- PTC Princeton Tech PT2314E - C90034Document5 pagesPTC Princeton Tech PT2314E - C90034Ajay HaldarNo ratings yet

- Datasheet PDFDocument5 pagesDatasheet PDFOscar Andres Ramirez AmayaNo ratings yet

- 5 1pdfDocument15 pages5 1pdfSaravanan ViswakarmaNo ratings yet

- TDA7439 STMicroelectronicsDocument19 pagesTDA7439 STMicroelectronicsZoran ConstantinescuNo ratings yet

- Digital Controlled Stereo Audio Processor with Loudness and Volume ControlDocument13 pagesDigital Controlled Stereo Audio Processor with Loudness and Volume ControlJose BenavidesNo ratings yet

- Description Features: PT2033 2.1 Channel Audio Processor With Subwoofer OutDocument4 pagesDescription Features: PT2033 2.1 Channel Audio Processor With Subwoofer Outvishnu csNo ratings yet

- Baseband R503Document9 pagesBaseband R503diongueNo ratings yet

- Tda 7440Document17 pagesTda 7440message2tejaNo ratings yet

- Well Area ModifiedDocument10 pagesWell Area ModifiedMuhammad IjazNo ratings yet

- Dolby Pro Logic II DecoderDocument19 pagesDolby Pro Logic II DecoderrohanscreationsNo ratings yet

- R2S15900SP_RenesasTechnologyDocument9 pagesR2S15900SP_RenesasTechnologyhangHT bocNo ratings yet

- TDA7442 TDA7442D: Tone Control and Surround Digitally Controlled Audio ProcessorDocument17 pagesTDA7442 TDA7442D: Tone Control and Surround Digitally Controlled Audio ProcessorTorikul HabibNo ratings yet

- TA2068N ToshibaDocument19 pagesTA2068N ToshibavladislavNo ratings yet

- Pioneer Pml010a DatasheetDocument1 pagePioneer Pml010a DatasheetAbdullah TaniNo ratings yet

- Coolaudio V4220M DatasheetDocument11 pagesCoolaudio V4220M DatasheetMiguelNo ratings yet

- Tivax STB T8.User - ManualDocument24 pagesTivax STB T8.User - ManualEarl TrotterNo ratings yet

- Practical Considerations For Low Noise Amplifier Design: White PaperDocument10 pagesPractical Considerations For Low Noise Amplifier Design: White PaperBelachew AndualemNo ratings yet

- TDA7442Document16 pagesTDA7442gusagus2775No ratings yet

- NJW1153 NewJapanRadioDocument20 pagesNJW1153 NewJapanRadioPavanBasavaniNo ratings yet

- Venu360 Brochure 4 14 17Document2 pagesVenu360 Brochure 4 14 17Alejo PalenciaNo ratings yet

- Planning A Receiver System Is One of ThoseDocument4 pagesPlanning A Receiver System Is One of ThoseDragan IvanovNo ratings yet

- PT12311 Stereo Audio Processor For Car Audio: Input Surge ProtectionDocument4 pagesPT12311 Stereo Audio Processor For Car Audio: Input Surge Protectionand roidNo ratings yet

- Audio routing diagramDocument2 pagesAudio routing diagramPedro Rodríguez FernándezNo ratings yet

- Dual-Port RAM Block DiagramDocument8 pagesDual-Port RAM Block DiagramivanramljakNo ratings yet

- Dual-Port RAM Block DiagramDocument8 pagesDual-Port RAM Block DiagramivanramljakNo ratings yet

- Hệ Thống Chiếu SángDocument3 pagesHệ Thống Chiếu SángVũ Đức HiềnNo ratings yet

- Cobra BravoDocument1 pageCobra Bravonailton pereiraNo ratings yet

- DatasheetDocument16 pagesDatasheetvnaychenko125No ratings yet

- 8-Channel Electronic Volume With Input SelectorDocument22 pages8-Channel Electronic Volume With Input SelectorRADON electronicsNo ratings yet

- Marantz SR 19 ServiceDocument58 pagesMarantz SR 19 ServiceRyan ChouNo ratings yet

- AM7000 Series: GeneralDocument26 pagesAM7000 Series: GeneralBahador YazdiNo ratings yet

- TDA7461N: Car Radio Signal ProcessorDocument31 pagesTDA7461N: Car Radio Signal ProcessorshareatorNo ratings yet

- Rear Wiring Harness LHDocument2 pagesRear Wiring Harness LHLinas PaskocimasNo ratings yet

- HiVAWT - DS-3000 User Manual Ver 2-20100722Document49 pagesHiVAWT - DS-3000 User Manual Ver 2-20100722Rene Alexander Barrera CardenasNo ratings yet

- Stereo Audio Processor for Car AudioDocument5 pagesStereo Audio Processor for Car AudioRec TecNo ratings yet

- Electrical Wiring Diagram for 2008 PZ464 VehicleDocument1 pageElectrical Wiring Diagram for 2008 PZ464 VehicleDragan StanicNo ratings yet

- ORI001102 CDMA WLL BTS3612 Hardware System ISSUE3.0Document69 pagesORI001102 CDMA WLL BTS3612 Hardware System ISSUE3.0api-19974739No ratings yet

- 90 91 PDFDocument2 pages90 91 PDFEgoro KapitoNo ratings yet

- Ti-Rfid ProductsDocument10 pagesTi-Rfid ProductsKhoirul UmamNo ratings yet

- Re PeaterDocument42 pagesRe PeaterAnonymous Y1Htth0GqNo ratings yet

- A2Document1 pageA2engrrjamonNo ratings yet

- CH 08 Yca 1Document1 pageCH 08 Yca 1RUBEN DARIO SandovalNo ratings yet

- Philips NE5534 and NE5532 Aplication NoteDocument12 pagesPhilips NE5534 and NE5532 Aplication NoteDanang PrasetiyoNo ratings yet

- pg4 ShureDocument35 pagespg4 Shurejoaquin espalterNo ratings yet

- TDA7348Document14 pagesTDA7348ClaudiuNo ratings yet

- Copy Tray R1, R2 Parts ListDocument19 pagesCopy Tray R1, R2 Parts ListTecnica CPY Copiadoras del ParaguayNo ratings yet

- Toyota IQ 2008 VSS1 Electrical Wiring Diagram LHD - Installation InstructionsDocument1 pageToyota IQ 2008 VSS1 Electrical Wiring Diagram LHD - Installation InstructionsGerman GruberNo ratings yet

- Boiler wiring diagram decoderDocument2 pagesBoiler wiring diagram decoderDhenil ManubatNo ratings yet

- Dolby Pro-Logic Surround Amplifier/Subwoofer Service ManualDocument25 pagesDolby Pro-Logic Surround Amplifier/Subwoofer Service ManualHristoIlievNo ratings yet

- LM35 Precision Centigrade Temperature Sensors: 1 Features 3 DescriptionDocument34 pagesLM35 Precision Centigrade Temperature Sensors: 1 Features 3 DescriptionAnom ManelaNo ratings yet

- KA2223 Scalony KorektorDocument4 pagesKA2223 Scalony KorektorDamianNo ratings yet

- Basic Function Audio Processor: DescriptionDocument10 pagesBasic Function Audio Processor: DescriptionDamianNo ratings yet

- TDA4650 Philips Elenota - PL PDFDocument13 pagesTDA4650 Philips Elenota - PL PDFDamianNo ratings yet

- Tda7719 PDFDocument45 pagesTda7719 PDFDamianNo ratings yet

- TDA4650 Philips Elenota - PL PDFDocument13 pagesTDA4650 Philips Elenota - PL PDFDamianNo ratings yet

- TDA9860 Philips Elenota - PL PDFDocument18 pagesTDA9860 Philips Elenota - PL PDFDamianNo ratings yet

- Basic Function Audio Processor: DescriptionDocument10 pagesBasic Function Audio Processor: DescriptionDamianNo ratings yet

- TDA4650 Philips Elenota - PL PDFDocument13 pagesTDA4650 Philips Elenota - PL PDFDamianNo ratings yet

- Outdoor Directional Quad-Band Antenna: ODI-065R15M18JJJ02-GDocument2 pagesOutdoor Directional Quad-Band Antenna: ODI-065R15M18JJJ02-GYns KlcNo ratings yet

- Chapter 2Document12 pagesChapter 2Al7asanAmmarNo ratings yet

- Chapter Two: Formatting and Baseband ModulationDocument43 pagesChapter Two: Formatting and Baseband ModulationAhmed Hassan MohammedNo ratings yet

- Leviton 6AS10-Xxx Atlas-X1 Cat 6A SlimLine Patch CordsDocument2 pagesLeviton 6AS10-Xxx Atlas-X1 Cat 6A SlimLine Patch CordsMaria VictoriaNo ratings yet

- PDFDocument2 pagesPDFJosé Ignacio Espigares CuestaNo ratings yet

- Implementation of A Basic AECDocument4 pagesImplementation of A Basic AECquitelargeNo ratings yet

- Bluetooth Beacon Quick Start GuideDocument6 pagesBluetooth Beacon Quick Start GuideAnonymous dGFqrw5vONo ratings yet

- 19 HCS HandoverDocument21 pages19 HCS HandoverWalid BensaidNo ratings yet

- SignalsDocument51 pagesSignalsNaveen KumarNo ratings yet

- Wireless SecurityDocument11 pagesWireless SecurityPavitraNo ratings yet

- Jaws MK 2 CB - Conversión A 10MDocument14 pagesJaws MK 2 CB - Conversión A 10MGeraldrum Zyzcom HdzNo ratings yet

- Microwave Link Engineering Design and Path Profile CalculationDocument39 pagesMicrowave Link Engineering Design and Path Profile CalculationAMIT KUMARNo ratings yet

- T V Antenna - PPT (By A K)Document117 pagesT V Antenna - PPT (By A K)Dharamveer KumarNo ratings yet

- TracStarSV360 ManualDocument66 pagesTracStarSV360 ManualBui NhuNo ratings yet

- Sar & Alerting 7Document23 pagesSar & Alerting 7Kwin LatifahNo ratings yet

- Practical Multibeam Training For HydrographersDocument28 pagesPractical Multibeam Training For HydrographersTudor GeorgetaNo ratings yet

- Ofdm ThesisDocument128 pagesOfdm ThesisRohini SeetharamNo ratings yet

- W61PC Manual V7.3.00Document353 pagesW61PC Manual V7.3.00caraciculaNo ratings yet

- Diversity and QualiPoc - Supported DevicesDocument41 pagesDiversity and QualiPoc - Supported DevicesfmonfasaniNo ratings yet

- Sensors: A Highly Sensitive and Miniature Optical Fiber Sensor For Electromagnetic Pulse FieldsDocument14 pagesSensors: A Highly Sensitive and Miniature Optical Fiber Sensor For Electromagnetic Pulse FieldsThang NguyenNo ratings yet

- Huawei Parameter GuideDocument207 pagesHuawei Parameter Guideanita_83No ratings yet

- Ss AssignmentDocument4 pagesSs AssignmentSandeep ReddyNo ratings yet

- OPC-2078 - 1939 PinoutsDocument4 pagesOPC-2078 - 1939 PinoutsmarcelolilloNo ratings yet

- Comparing Mems Vs Analog Wei Tle October2013Document5 pagesComparing Mems Vs Analog Wei Tle October2013malibrodNo ratings yet

- Exploded View and Component DisposalDocument0 pagesExploded View and Component DisposalSitaru ConstantinNo ratings yet

- HDCDDocument26 pagesHDCDamlNo ratings yet

- Mototrbo Adk OverviewDocument30 pagesMototrbo Adk OverviewDang Van TuyenNo ratings yet

- Product Specifications Product Specifications: RV4PX310B1 RV4PX310B1Document3 pagesProduct Specifications Product Specifications: RV4PX310B1 RV4PX310B1Djamil KaraNo ratings yet