Professional Documents

Culture Documents

Datasheet IT8987E PDF

Uploaded by

Analia Madeled Tovar JimenezOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Datasheet IT8987E PDF

Uploaded by

Analia Madeled Tovar JimenezCopyright:

Available Formats

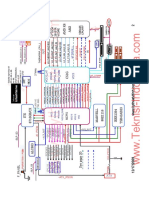

5 4 3 2 1

+3VPCU

L16 BLM15AG121SN1D(120,500MA)_4 +A3VPCU +3VPCU_ECPLL L11 BLM15AG121SN1D(120,500MA)_4

EC(KBC) +3VPCU_EC

S5_ON R602 10K_4

C411 C653 (For PLL Power)

0.1u/16V_4

0.1u/16V_4 +3V_S5

ECAGND

SIO_EXT_SMI# R610 *10K_4

[30] D/C# SB_ACDC [30]

R591 2.2_6 12 mils TP59 SIO_EXT_SCI# R607 *10K_4

1 2 +3VPCU_EC

+3VPCU BT_EN [21]

C652 C654 C371 C396 C660 C424 TP64 +3V

TP65

0.1u/16V_4 0.1u/16V_4 0.1u/16V_4 0.1u/16V_4 0.1u/16V_4 0.1u/16V_4 Layout put in device side SIO_A20GATE R592 *10K_4

KBRST# R603 10K_4

USBON# [25]

R658 33_4 SERIRQ R605 *10K_4

TPD_EN [27]

R239 2.2_6

USB_CHG_MODE [25]

+3V 1 2 +3V_EC

D USB_CHG_EN [25] D

C674 SUSON R593 100K_4

LPC_CLKRUN# [6,23]

C657 R613 *8.2K 180P/50V_4 MAINON R253 100K_4

+3V

VRON R249 100K_4

0.1u/16V_4 PLTRST# R608 100K_4

114

121

106

127

PCH_RSMRST# R584 *10K_4 ITE suggest PCH_RSMRST#

11

26

50

92

74

84

83

82

19

20

99

98

97

96

93

3

U35 CPU_ID R615 *SP@0_4 PD

CPU_ID:CZ Internal PU, CZL External

10 110 PD

GPH7

VCC

AVCC

VSTBY_FSPI

EGCLK/WUI27/GPE3(Dn)

EGCS#/WUI26/GPE2(Dn)

EGAD/WUI25/GPE1(Dn)

L80HLAT/BAO/WUI24/GPE0(Dn)

L80LLAT/WUI7/GPE7(Up)

CLKRUN#/WUI16/GPH0/ID0(Dn)

VSTBY

VSTBY

VSTBY

VSTBY

VSTBY

VSTBY

WUI42/GPH6/ID6(Dn)

WUI41/GPH5/ID5(Dn)

WUI40/GPH4/ID4(Dn)

WUI19/GPH3/ID3(Dn)

[6,21,23] LPC_LAD0 LAD0/GPM0(X) SMCLK0/GPB3(X) MBCLK [30]

9 111

[6,21,23] LPC_LAD1 8 LAD1/GPM1(X) SMDAT0/GPB4(X) 115 MBDATA [30]

[6,21,23] LPC_LAD2 LAD2/GPM2(X) SMCLK1/GPC1(X) 2ND_MBCLK [4,12]

7 VSTBY 116

[6,21,23] LPC_LAD3 LAD3/GPM3(X) SMDAT1/GPC2(X) 2ND_MBDATA [4,12]

22 VCC 117 TP49

+3VPCU [5,21,23] PLTRST# 13 LPCRST#/WUI4/GPD2(Up) VSTBY PECI/SMCLK2/WUI22/GPF6(Up) 118 R660 33_4

SM BUS

[6] CLK_PCI_775 LPCCLK/GPM4(X) VCC SMDAT2/WUI23/GPF7(Up) LID591# [17]

6 C682 180P/50V_4

CLK_PCI_775

[6,21,23] LPC_LFRAME#

17

LFRAME#/GPM5(X) VSTBY

PS2CLK0/TMB0/CEC/GPF0(Up)

85

86

IOAC_RST# [20,21]

SM BUS PU(KBC)

PROCHOT_EC

LPCPD#/WUI6/GPE6(Dn) PS2DAT0/TMB1/GPF1(Up) EC_FPBACK# [17]

2

89

126 PS2CLK2/WUI20/GPF4(Up) 90 TPCLK [27]

D40

[5] SIO_A20GATE GA20/GPB5(X) VSTBY PS2DAT2/WUI21/GPF5(Up) TPDATA [27]

R611 R606 5 +3VPCU

PS/2

RB500V-40 [6,23] SERIRQ SERIRQ/GPM6(X)

100K_4 15 VCC

[5] SIO_EXT_SMI# ECSMI#/GPD4(Up) VSTBY VSTBY VSTBY

23 Layout put in device side

ECSCI#/GPD3(Up) LPC VSTBY

*22_4 MBCLK R597 4.7K_4

[5] SIO_EXT_SCI#

1

WRST# 14 GPIO MBDATA R596 4.7K_4

R604 *short_4 4 WRST# VSTBY

[5] KBRST# KBRST#/GPB6(X) VSTBY

16

[21] IOAC_WLAN_WAKE# PWUREQ#/BBO/SMCLK2ALT/GPC7(Up)/SMCLK2ALT VSTBY Change EC SMBus PU voltage from

C656 C655

*10p/50V_4 1u/6.3V_4 24 +3V_S5 +3V_GFX to +3V_S5 due to it also

PWM0/GPA0(Up) PWRLED# [26] connect to CPU(SIC/SID) and GPU.

25

[28]

[5]

KB_BL_LED

DNBSWON#

113

123 CRX0/GPC0(Dn)

CTX0/TMA0/GPB2(Dn) CIR

IT8987E/BX PWM1/GPA1(Up)

PWM2/GPA2(Up)

PWM3/GPA3(Up)

PWM4/GPA4(Up)

28

29

30

BATLED1# [26]

SUSLED# [26]

BATLED0# [26]

MAINON [33,36]

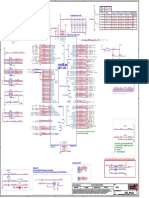

2ND_MBCLK

2ND_MBDATA

R595

R594

4.7K_4

4.7K_4

EC need read CPU temperature even

in UMA mode or GPU off mode

VSTBY 31

PWM5/GPA5(Up) USB_CTL1 [25]

PWM

TP60 80

119 DAC4/DCD0#/GPJ4(X) 47

[5] SUSB# DSR0#/GPG6(X) VSTBY TACH0A/GPD6(Dn) FANSIG [28] CORE_PWM_PROCHOT# [4,30,34,35]

Layout put in device side [5] PWROK_EC

33 48

GINT/CTS0#/GPD5(Up) TACH1A/TMA1/GPD7(Dn)

3

R612 0_4 88 TP68

[4,17] APU_DISP_BLEN 81 PS2DAT1/RTS0#/GPF3(Up) 120

R322 33_4 Q48

[17] TOUCHPANEL_ON DAC5/RIG0#/GPJ5(X) TMRI0/WUI2/GPC4(Dn) SUSON [31,33]

C 87 124 C

[20] IOAC_LAN_WAKE# 109 PS2CLK1/DTR0#/GPF2(Up) TMRI1/WUI3/GPC6(Dn) 2

TP48 TP52 PROCHOT_EC

C678 108 TXD/SOUT0/GPB1(Up)

[22] AMP_MUTE# RXD/SIN0/GPB0(Up)

180P/50V_4

71 VSTBY 107 R609 2N7002K

[24] ODD_POWER ADC5/DCD1#/WUI29/GPI5(X) PWRSW/GPE4(Up) NBSWON# [28]

72 UART port 18

[30] ACIN SUSC# [5]

1

73 ADC6/DSR1#/WUI30/GPI6(X) RI1#/WUI0/GPD0(Up) 21 HWPG 100K_4

[30] TEMP_MBAT ADC7/CTS1#/WUI31/GPI7(X) RI2#/WUI1/GPD1(Up)

35 WAKE UP

[21] IOAC_WLANPWR# RTS1#/WUI5/GPE5(Dn)

Layout put in device side 34

[22] PCBEEP_EC 122 PWM7/RIG1#/GPA7(Up) 112

R625 33_4 TP53

[24] EC_ODD_EJ DTR1#/SBUSY/GPG1/ID7(Dn) RING#/PWRFAIL#/CK32KOUT/LPCRST#/GPB7(Dn) PCH_RSMRST# [5]

95 Layout put in device side

[30] AC_PROTECT 94 CTX1/WUI18/SOUT1/GPH2/SMDAT3/ID2(Dn)

C676 180P/50V_4 R635 33_4

CRX1/WUI17/SIN1/SMCLK3/GPH1/ID1(Dn) RF_EN [21]

R598 CZL@0_4 SPI_SCK_UR_R 105 C675 180P/50V_4 +3VPCU

[6] SPI_SCK

[6] SPI_CS

R601 CZL@0_4 SPI_CS0#_UR 101

102

FSCK/GPG7

FSCE#/GPG3

SPI NOR FLASH(128KB) (KBC)

[6] SPI_SDI

R213 CZL@0_4 SPI_SDI_UR

FMOSI/GPG4 EXTERNAL SERIAL FLASH ICMNT [30] +3VPCU

R214 CZL@0_4 SPI_SDO_UR 103 66

[6] SPI_SDO FMISO/GPG5 ADC0/GPI0(X)

EC_SPI_SCK R587 CZ@0_4 67 C428 10u/6.3V_6 ECAGND

ADC1/GPI1(X) U33

EC_SPI_CS0# R590 CZ@0_4

[28] MY16

56

KSO16/SMOSI/GPC3(Dn) ADC2/GPI2(X)

68

DGPU_AC_DC# [12] 25mA R566

EC_SPI_SDI R589 CZ@0_4 57 69 8 5 EC_SPI_SDI CZ@10K_4

[28] MY17 KSO17/SMISO/GPC5(Dn) ADC3/GPI3(X) VRON [5,34] +3VPCU VCC SPI_SI

EC_SPI_SDO R588 CZ@0_4 CPU_ID 32 70 2 EC_SPI_SDO

PWM6/SSCK/GPA6(Up) ADC4/WUI28/GPI4(X) IOAC_LANPWR# [20] SPI_SO 1 EC_SPI_CS0#

100 3 CS# 6

[31,32,36] S5_ON SSCE0#/GPG2(X) A/DAVCC

D/A R565 EC_SPI_WP#

WP# SPI_SCK

EC_SPI_SCK

125 SPI ENABLE CZ@10K_4

[27] PTP_PWR_EN# SSCE1#/GPG0(X) 76 TP63

36 TACH2/GPJ0(X) 77 TP62 R581 EC_SPI_HOLD# 7 4 C649

[28] MY0 37 KSO0/PD0 GPJ1(X) 78 SPI_HOLD GND

TP61 CZ@10K_4 *CZ@10P/50V_4

[28] MY1 KSO1/PD1 DAC2/TACH0B/GPJ2(X)

38 79 CZ@W25X10CLSNIG

[28] MY2 KSO2/PD2 DAC3/TACH1B/GPJ3(X) CPUFAN# [28]

R600 *10K_4 SPI_SDI_UR 39

[28] MY3 40 KSO3/PD3 VSTBY

R599 *10K_4 SPI_SDO_UR KBMX

[28] MY4 KSO4/PD4

41

[28] MY5 42 KSO5/PD5

[28] MY6 KSO6/PD6

Please do not place any [28] MY7

43

KSO7/PD7

44

pull-up resistor [28] MY8 45 KSO8/ACK#

on GPG0, GPG2, and GPG6 [28]

[28]

MY9

MY10

46 KSO9/BUSY

KSO10/PE

HWPG(KBC) +3V

(Reserved [28] MY11

51

KSO11/ERR# GPJ7

2 TP57

KSI3/SLIN#

KSI1/AFD#

KSI0/STB#

KSI2/INIT#

hardware strapping). 52 128 R300 33_4

B [28] MY12 KSO12/SLCT GPJ6 TPD_INT# [27] B

53 R241

VCORE

[28] MY13 KSO13

AVSS

54

KSI4

KSI5

KSI6

KSI7

[28] MY14

VSS

VSS

VSS

VSS

VSS

55 KSO14 C471

[28] MY15 KSO15 180P/50V_4 10K_4

SM BUS ARRANGEMENT TABLE IT8987E/BX D14 *1N4148WS HWPG

[36] HWPG_0.775VS5 HWPG [5]

58

59

60

61

62

63

64

65

27

49

91

104

75

12

SM Bus 1 Battery D16 *1N4148WS

[36] HWPG_1.8VS5

Layout put in device side

[28] MX0

C401 D17 1N4148WS

[28] MX1 [34] VRM_PWRGD

SM Bus 2 PCH/VGA

ECAGND

[28] MX2

0.1u/16V_4 D13 *1N4148WS

[28] MX3 [33] HWPG_VDDR

[28] MX4

SM Bus 3 N/A D15 *1N4148WS

[28] MX5 [32] HWPG_0.95VS5

[28] MX6

L15 BLM15AG121SN1D(120,500MA)_4 D18 *1N4148WS

[28] MX7 [31] SYS_HWPG

SM Bus 4 N/A

1 3D20 *CZ@1N4148WS

Power sequence Battery B/I SW (SYP) +3VRTC +3VPCU [35] GFX_PWRGD

Q27

CZ@2N7002K

2

+3V R256 CZ@100K/F_4

R641 R642

3

*0_4 *0_4

C437

NBSWON# TP51 CZ@0.22U/10V_4

2

[5] VDDGFX_PD

DNBSWON# TP47

Q26

SUSON TP55 R643 CZ@2N7002K

*10K_4

1

SUSB# +3VRTC

TP54

WRST#

PWROK_EC TP67

1

[30] BI

A PLTRST# TP66 R640 C671 A

3

100K_4 *0.1u/16V_4

HWPG TP18 Vgs = 1.5V

2

MAINON 2 BI_GATE

TP58

Vgs = 1.5V

SW1

1

PCH_RSMRST# TP50

3

4

PJA138K C672 BI_SW

S5_ON Q55 *0.1u/25V_6 6

TP56

1

5

Q56

*PJ4N3KDW

Quanta Computer Inc.

PROJECT : ZRZ

4

1

1

2

Size Document Number Rev

1A

EC (ITE8987E/BX)

Date: Friday, March 06, 2015 Sheet 29 of 41

5 4 3 2 1

You might also like

- Esquema Schematic Dell - Inspiron n4030 WISTRON DJ1 Capella UMA 10212-1 48.4EK19.011Document90 pagesEsquema Schematic Dell - Inspiron n4030 WISTRON DJ1 Capella UMA 10212-1 48.4EK19.011Leandro PereiroNo ratings yet

- Analysis 3v5v Sony MBX223 M960 ICDocument3 pagesAnalysis 3v5v Sony MBX223 M960 ICmadumadawa rajapakshaNo ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFd4l170100% (1)

- VDDC Vcc3V3-St: PWM - 100Hz/100Khz Hi: Max Lum Lo: Min LumDocument13 pagesVDDC Vcc3V3-St: PWM - 100Hz/100Khz Hi: Max Lum Lo: Min LumTavi DumitrescuNo ratings yet

- Z77X-UD3H Rev.1.01 GIGABYTEDocument42 pagesZ77X-UD3H Rev.1.01 GIGABYTEvinuNo ratings yet

- Compal LA-G021P r1.BDocument49 pagesCompal LA-G021P r1.BAnalia Madeled Tovar JimenezNo ratings yet

- Z77X-UD3H Rev.1.01 GIGABYTEDocument42 pagesZ77X-UD3H Rev.1.01 GIGABYTEvinuNo ratings yet

- Nm-A281 R10-Silk-TopDocument1 pageNm-A281 R10-Silk-TopAnalia Madeled Tovar JimenezNo ratings yet

- Question 1 - Mounting MethodDocument3 pagesQuestion 1 - Mounting MethodMuhd IlyasNo ratings yet

- Block Diagram: B85M-E/DASH Repair GuideDocument6 pagesBlock Diagram: B85M-E/DASH Repair GuideLuiz Fernando Cavalcante GonçalvesNo ratings yet

- Ecs V10il1 - 37GV10000-C0 - Rev CDocument32 pagesEcs V10il1 - 37GV10000-C0 - Rev CHendra R. Rattu75% (4)

- Wiistron Raichu WL Pikachu WL 18730 R-1mDocument106 pagesWiistron Raichu WL Pikachu WL 18730 R-1mPhan ThanhNo ratings yet

- Rome2 Apollo Power On SequenceDocument14 pagesRome2 Apollo Power On SequenceMabrouk Med AliNo ratings yet

- Advanced ACPI Controller IntroductionDocument16 pagesAdvanced ACPI Controller IntroductionsttecnicoNo ratings yet

- Dell Inspiron n5010 Wistron Berry Dg15 Intel Discrete Uma Rev A00 SCHDocument92 pagesDell Inspiron n5010 Wistron Berry Dg15 Intel Discrete Uma Rev A00 SCHAhmad BahaaNo ratings yet

- P5G41-M LX: Troubleshooting GuideDocument4 pagesP5G41-M LX: Troubleshooting GuideRodney RibeiroNo ratings yet

- Ssc5x86h ManDocument29 pagesSsc5x86h ManValdenir DuarteNo ratings yet

- BQ24736 Texas Instruments Product Details: Part Number: Worldway Part: Category: Manufacturer: ApplicationsDocument3 pagesBQ24736 Texas Instruments Product Details: Part Number: Worldway Part: Category: Manufacturer: Applicationszaenal mutaqinNo ratings yet

- Sony Vaio VGN-AW Series MBX-194 M780 SD FOXCONN M780 CantigaP WPCE775LDocument77 pagesSony Vaio VGN-AW Series MBX-194 M780 SD FOXCONN M780 CantigaP WPCE775LChetin TekinNo ratings yet

- KDL 40 BX 450Document37 pagesKDL 40 BX 450Jose GonzalesNo ratings yet

- ALi M3329D DVB-S Total SolutionDocument7 pagesALi M3329D DVB-S Total SolutionRajesh100% (1)

- Quanta Et2t r3c SchematicsDocument27 pagesQuanta Et2t r3c Schematicsrmartins_239474No ratings yet

- Introduction To Laptop Fix and DiagnosesDocument51 pagesIntroduction To Laptop Fix and Diagnosesablacon64No ratings yet

- Wistron Tucana-BR MBDocument56 pagesWistron Tucana-BR MBArmando Endzelis PrietoNo ratings yet

- Plasma TV SMPS TroubleshoutingDocument5 pagesPlasma TV SMPS TroubleshoutingmindjokerNo ratings yet

- 8c347 Compal LA-9901P r1.0 2013 PDFDocument64 pages8c347 Compal LA-9901P r1.0 2013 PDFBruno CoutoNo ratings yet

- WWW - Laptopfix.vn: Share ROM Non-Share ROMDocument1 pageWWW - Laptopfix.vn: Share ROM Non-Share ROMJulian Andres RozoNo ratings yet

- Quanta Jm3 Power Sequence Rev 02Document37 pagesQuanta Jm3 Power Sequence Rev 02u6k5lp l2y3z0No ratings yet

- 2 SCHEMATIC MV-4 (Canaima Roja)Document8 pages2 SCHEMATIC MV-4 (Canaima Roja)Rodolfo CarruyoNo ratings yet

- Compal Confidential PIQY1 M/B Schematics DocumentDocument63 pagesCompal Confidential PIQY1 M/B Schematics DocumentMariahaNo ratings yet

- Storm Schematics Signal Routing GuidelinesDocument102 pagesStorm Schematics Signal Routing Guidelineschipmaster86100% (1)

- Gigabyte Ga-Z87x-D3h Rev 1.0 - Structure Introductions Power Sequence Measure PointsDocument18 pagesGigabyte Ga-Z87x-D3h Rev 1.0 - Structure Introductions Power Sequence Measure PointsJerzy LisowskiNo ratings yet

- Buy,contact,Paypal,Alipay detailsDocument33 pagesBuy,contact,Paypal,Alipay detailsdraNo ratings yet

- Block Diagram: LGA 775-Pin SocketDocument20 pagesBlock Diagram: LGA 775-Pin SocketRajesh DhanambalNo ratings yet

- Hisense FA y LED DriveDocument2 pagesHisense FA y LED Driveatomo33No ratings yet

- Intel chipset specs with code names, part numbers and release datesDocument4 pagesIntel chipset specs with code names, part numbers and release datesEletrônica Goiano100% (1)

- PIC PWM ControllerDocument10 pagesPIC PWM Controllerkeitabando100% (2)

- Giga Luoc Do Kich NguonDocument2 pagesGiga Luoc Do Kich NguonNguyễn Văn TặngNo ratings yet

- Gigabyte Ga-B150m-Hd3 DDR3 (Power Sequence)Document2 pagesGigabyte Ga-B150m-Hd3 DDR3 (Power Sequence)Josafat Carrillo Góngora100% (2)

- Fid en Tia L On Fid en Tia L: IPX41-D3Document54 pagesFid en Tia L On Fid en Tia L: IPX41-D3evandro efbasseNo ratings yet

- Fixing A Seagate 7200.11 Hard DriveDocument22 pagesFixing A Seagate 7200.11 Hard Driveajlapria100% (1)

- TPM17.1E EuDocument112 pagesTPM17.1E EuViktor SteinþórssonNo ratings yet

- Compal Secret Schematic DataDocument45 pagesCompal Secret Schematic DataRicardo Olivares100% (1)

- Power Sequence TrainingDocument15 pagesPower Sequence TrainingRaju KhajjidoniNo ratings yet

- LCD TV: Service ManualDocument43 pagesLCD TV: Service Manualmariana acostaNo ratings yet

- Ic Equal ListDocument21 pagesIc Equal ListMohamed Ibrahim AhamedRasmiNo ratings yet

- Laptop Lab ManualDocument41 pagesLaptop Lab ManualShameem HaneefaNo ratings yet

- Intel 815e SchematicsDocument33 pagesIntel 815e SchematicsTilak AmarghdeNo ratings yet

- MT185WHM N10Document28 pagesMT185WHM N10Tmfiros FirosNo ratings yet

- Schematic Diagram: 1. ScalerDocument7 pagesSchematic Diagram: 1. ScalerMilan HouskaNo ratings yet

- Design: IdeasDocument6 pagesDesign: IdeasSamantha EwingNo ratings yet

- Wistron LA710 - 17513 PDFDocument107 pagesWistron LA710 - 17513 PDFArny Mayedo CastilloNo ratings yet

- LGA1150 Cpu: System Chipset: Lynxpoint-H81 Main Memory:: IH81S-MHS IH81S-MHS IH81S-MHSDocument39 pagesLGA1150 Cpu: System Chipset: Lynxpoint-H81 Main Memory:: IH81S-MHS IH81S-MHS IH81S-MHSdương hoàngNo ratings yet

- Vinafix - VN - Asus 1015cx Cedar Trail Training MaterialsDocument67 pagesVinafix - VN - Asus 1015cx Cedar Trail Training Materialsrasrozi51700% (1)

- Research and Development in Non-Mechanical Electrical Power Sources: Proceedings of the 6th International Symposium Held at Brighton, September 1968From EverandResearch and Development in Non-Mechanical Electrical Power Sources: Proceedings of the 6th International Symposium Held at Brighton, September 1968No ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFAnalia Madeled Tovar JimenezNo ratings yet

- Datasheet It8987e PDF FreeDocument1 pageDatasheet It8987e PDF Freemauri kñazovicNo ratings yet

- Datasheet It8987e PDF FreeDocument1 pageDatasheet It8987e PDF Freejhonnattan moreno casilimasNo ratings yet

- Power Input: IN GND BS Comp EN SS SWDocument10 pagesPower Input: IN GND BS Comp EN SS SWjesurajanNo ratings yet

- IT8586EDocument1 pageIT8586EJivko IvanovNo ratings yet

- Lenovo Ideapad 300-15ISK NM-A481Document1 pageLenovo Ideapad 300-15ISK NM-A481Moriel EverNo ratings yet

- Power Input: PDF 文件以 "PDF 制作工厂" 试用版创建 ÿÿÿÿ ÿDocument16 pagesPower Input: PDF 文件以 "PDF 制作工厂" 试用版创建 ÿÿÿÿ ÿkadirov01No ratings yet

- Beko Chassis KT KU Main Code VKT190RDocument18 pagesBeko Chassis KT KU Main Code VKT190RtaviNo ratings yet

- It8586e PDFDocument1 pageIt8586e PDFFacundo TorresNo ratings yet

- gd25lq64c v3.3 20190603 PDFDocument80 pagesgd25lq64c v3.3 20190603 PDFSofía GattiNo ratings yet

- Wistron Dne40-Cr-Mb - Dell Inspiron 5421Document106 pagesWistron Dne40-Cr-Mb - Dell Inspiron 5421Analia Madeled Tovar JimenezNo ratings yet

- Compal - La-A921p Lenovo Yoga 2 13Document38 pagesCompal - La-A921p Lenovo Yoga 2 13eriel kell100% (1)

- WWW - Vinafix.Vn: Prosavage Kl133A Chipset - Vt8364A North Bridge PDocument1 pageWWW - Vinafix.Vn: Prosavage Kl133A Chipset - Vt8364A North Bridge PAnalia Madeled Tovar JimenezNo ratings yet

- 25Q32BVDocument78 pages25Q32BVVictor GarciaNo ratings yet

- Drawing and specifications for Romeo discrete MV buildDocument66 pagesDrawing and specifications for Romeo discrete MV buildAnalia Madeled Tovar JimenezNo ratings yet

- Schematis HP V3000 DV2000 IntelDocument47 pagesSchematis HP V3000 DV2000 Intelmadoo0% (2)

- Sualaptop365.edu - VN: Block DiagramDocument5 pagesSualaptop365.edu - VN: Block DiagramAnalia Madeled Tovar JimenezNo ratings yet

- Dell Inspiron N4110quanta v02 Da0v02mb6e1 Rev 1a Uma 19012011Document44 pagesDell Inspiron N4110quanta v02 Da0v02mb6e1 Rev 1a Uma 19012011Tan Hung LuuNo ratings yet

- Murray Battery Connection DiagramDocument48 pagesMurray Battery Connection Diagramefeln1No ratings yet

- Vinafix.com - CR_KBC_IT8521Document1 pageVinafix.com - CR_KBC_IT8521Analia Madeled Tovar JimenezNo ratings yet

- HP 15-R157 COMPAL LA-A992P (ZS050) Rev 1.0 PDFDocument55 pagesHP 15-R157 COMPAL LA-A992P (ZS050) Rev 1.0 PDFanandabiswas100% (1)

- gd25lq64c v3.3 20190603 PDFDocument80 pagesgd25lq64c v3.3 20190603 PDFSofía GattiNo ratings yet

- Bq24725A Smbus 1-To 4-Cell Li+ Buck Battery Charge Controller With N-Channel Power Mosfet SelectorDocument48 pagesBq24725A Smbus 1-To 4-Cell Li+ Buck Battery Charge Controller With N-Channel Power Mosfet Selectoriq balNo ratings yet

- Lenovo G560 LA-5752PDocument51 pagesLenovo G560 LA-5752PRicardo Olivares100% (1)

- 1 PDFDocument105 pages1 PDFAnalia Madeled Tovar Jimenez100% (1)

- Lenovo G40-70 - G50-70 - ACLU1-ACLU2 ACLU3 ACLU4 NM-A361 NM2710 NM-A271 Rev1.0 PDFDocument59 pagesLenovo G40-70 - G50-70 - ACLU1-ACLU2 ACLU3 ACLU4 NM-A361 NM2710 NM-A271 Rev1.0 PDFflavio_b_703950% (4)

- Micron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q128A FeaturesDocument83 pagesMicron Serial NOR Flash Memory: 3V, Multiple I/O, 4KB Sector Erase N25Q128A FeaturesAnalia Madeled Tovar JimenezNo ratings yet

- SJM11_MS (ZH8) BLOCK DIAGRAMDocument31 pagesSJM11_MS (ZH8) BLOCK DIAGRAMAnalia Madeled Tovar JimenezNo ratings yet

- 25Q32BVDocument78 pages25Q32BVVictor GarciaNo ratings yet

- Lenovo ThinkPad E440 NM-A151 PDFDocument69 pagesLenovo ThinkPad E440 NM-A151 PDFskmishra1972No ratings yet

- Vdkte: LA-9869P Schematic REV 1.0Document52 pagesVdkte: LA-9869P Schematic REV 1.0Analia Madeled Tovar JimenezNo ratings yet

- Oak 14 Schematic EssentialsDocument106 pagesOak 14 Schematic EssentialsLucas LoureiroNo ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFAnalia Madeled Tovar JimenezNo ratings yet

- Schematis HP V3000 DV2000 IntelDocument47 pagesSchematis HP V3000 DV2000 Intelmadoo0% (2)

- X453MA Laptop Repair Guide Block Diagram and Power SequenceDocument5 pagesX453MA Laptop Repair Guide Block Diagram and Power SequenceAnalia Madeled Tovar JimenezNo ratings yet

- HeatEnginesVol 2 Chapter 7 RS PDFDocument29 pagesHeatEnginesVol 2 Chapter 7 RS PDFMahesh Babu TalupulaNo ratings yet

- r5220104 Hydraulics and Hydraulic MachineryDocument1 pager5220104 Hydraulics and Hydraulic MachinerySaitheja SharmaNo ratings yet

- J Kurozawa Marketing ResumeDocument3 pagesJ Kurozawa Marketing ResumeJon KurozawaNo ratings yet

- Brewery Construction Guide: Build Your Own Compact Homebrew SystemDocument23 pagesBrewery Construction Guide: Build Your Own Compact Homebrew SystemCesar Diaz100% (6)

- 23 60 03aDocument16 pages23 60 03aVictor Daniel WaasNo ratings yet

- PGT120 Wolfgang Warmbier Personal Grounding Tester Data Sheet PDFDocument2 pagesPGT120 Wolfgang Warmbier Personal Grounding Tester Data Sheet PDFJesus RodriguezNo ratings yet

- C FunctionsDocument48 pagesC FunctionsSayantan PalNo ratings yet

- Radial Piston PumpDocument10 pagesRadial Piston PumpRavikumar GangadharanNo ratings yet

- Air Deck TechniqueDocument9 pagesAir Deck TechniqueVenkata Ramana100% (1)

- Apply Business Math in Water Refilling StationDocument22 pagesApply Business Math in Water Refilling StationsdfdsfNo ratings yet

- Seminar On Substation TrainingDocument24 pagesSeminar On Substation TrainingPankaj SharmaNo ratings yet

- Design Tank-2Document4 pagesDesign Tank-2evrim77No ratings yet

- A2: Asian Infrastructure Investment Bank - (Correct Alternative)Document28 pagesA2: Asian Infrastructure Investment Bank - (Correct Alternative)Patadi Iti Placement CellNo ratings yet

- Ilovepdf MergedDocument33 pagesIlovepdf MergedNavneet KaurNo ratings yet

- Is 14680 Landslide Control - GuidelinesDocument16 pagesIs 14680 Landslide Control - Guidelinesv2299No ratings yet

- Creating A Safe Home Routine - 19477Document2 pagesCreating A Safe Home Routine - 19477徐海东No ratings yet

- Government of Odisha Rural Development Department Odisha, BhubaneswarDocument179 pagesGovernment of Odisha Rural Development Department Odisha, BhubaneswarPradeepta PatraNo ratings yet

- Aung Ye Htun3409894643578177227Document3 pagesAung Ye Htun3409894643578177227Aungye HtunNo ratings yet

- LPG Cylinder Rate ChartDocument4 pagesLPG Cylinder Rate ChartBest Movie scenesNo ratings yet

- MID LEC 2 User Interfaec DesignDocument10 pagesMID LEC 2 User Interfaec DesignspartaaaanNo ratings yet

- Bombas de Agua PaiDocument17 pagesBombas de Agua PaiEver Rivera50% (2)

- ANSWERDocument1 pageANSWERengr valderrama adrianNo ratings yet

- Q881507-9 Installation and Operating Manual PDFDocument1,059 pagesQ881507-9 Installation and Operating Manual PDFngocanhvyNo ratings yet

- Lean PokaYokeDocument2 pagesLean PokaYokemilou88No ratings yet

- 1.CEK LIST Syringe Pump PDFDocument1 page1.CEK LIST Syringe Pump PDFsri lestariNo ratings yet

- Distributed File SystemsDocument42 pagesDistributed File SystemsGaurav ManurNo ratings yet

- Little Man Computer NotesDocument6 pagesLittle Man Computer Noteskahlilavm0% (1)

- Haier Lt32c360 Chassis Msd306 SMDocument58 pagesHaier Lt32c360 Chassis Msd306 SMgenmassa100% (2)

- 22LS350S, 350T, 359S, 359T, 3500, 3510, 3590Document52 pages22LS350S, 350T, 359S, 359T, 3500, 3510, 3590Kiran VeesamNo ratings yet