Professional Documents

Culture Documents

The Central Processing Unit

Uploaded by

Rafena MustaphaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

The Central Processing Unit

Uploaded by

Rafena MustaphaCopyright:

Available Formats

THE CENTRAL PROCESSING UNIT

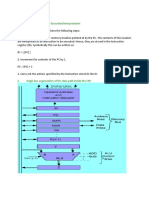

A computer can be divided into three (3) broad categories or subsystems:

1. the central processing unit (CPU)

2. main memory

3. the input/output subsystem

The central processing unit (CPU) performs operations on data. In most architectures, it has three parts:

1. an arithmetic logic unit (ALU)

2. a control unit (CU)

3. a set of registers

The Arithmetic Logic Unit (ALU)

The arithmetic logic unit (ALU) performs logic, shift, and arithmetic operations on data.

Logic operations: NOT, AND, OR, and XOR.

Shift operations: logic shift operations and arithmetic shift operations

Arithmetic operations: arithmetic operations on integers and reals.

The control unit (CU)

• The control unit controls and coordinates all operations.

• It works through a cycle of fetch, decode, and execution.

The fetch-decode-execute cycle

1. Fetch: The Fetch Operation is used for taking the instructions those are given by the user and the

Instructions those are stored into the Main Memory will be fetch by using Registers.

2. Decode: The Decode Operation is used for interpreting the Instructions means the Instructions are

decoded means the CPU will find out which Operation is to be performed on the Instructions.

3. Execute: The Execute Operation is performed by the CPU. And Results those are produced by the CPU

are then Stored into the Memory and after that they are displayed on the user Screen.

• The role of control unit can be summarised as below:

o To fetch / decode / execute instructions;

o To synchronise operation of processor;

o To marshal/control operation of fetch-execute cycle;

o To send control signals/commands to other components of fetch-execute cycle

CAPE Computer Science Unit 1

Registers

Register are used to quickly accept, store, and transfer data and instructions that are being used immediately by

the CPU. These registers are the top of the memory hierarchy, and are the fastest way for the system to

manipulate data. In a very simple microprocessor, it consists of a single memory location, usually called an

accumulator. Registers are built from fast multi-ported memory cell.

1. Memory Address Register (MAR): This register holds the address of memory where CPU wants to read or

write data. When CPU wants to store some data in the memory or reads the data from the memory, it places

the address of the required memory location in the MAR.

2. Memory Buffer Register (MBR): This register holds the contents of data or instruction read from, or

written in memory. The contents of instruction placed in this register are transferred to the Instruction

Register, while the contents of data are transferred to the accumulator or I/O register. In other words you can

say that this register is used to store data/instruction coming from the memory or going to the memory.

3. I/O Address Register (I/O AR): I/O Address register is used to specify the address of a particular I/O

device.

4. I/O Buffer Register (I/O BR): I/O Buffer Register is used for exchanging data between the I/O module and

the processor.

5. Program Counter (PC): Program Counter register is also known as Instruction Pointer Register. This

register is used to store the address of the next instruction to be fetched for execution. When the instruction

is fetched, the value of IP is incremented. Thus this register always points or holds the address of next

instruction to be fetched.

6. Instruction Register (IR): Once an instruction is fetched from main memory, it is stored in the Instruction

Register. The control unit takes instruction from this register, decodes and executes it by sending signals to

the appropriate component of computer to carry out the task.

7. Accumulator Register(AC): The accumulator register is located inside the ALU, It is used during

arithmetic & logical operations of ALU. The control unit stores data values fetched from main memory in

the accumulator for arithmetic or logical operation. This register holds the initial data to be operated upon,

the intermediate results, and the final result of operation. The final result is transferred to main memory

through MBR.

The processor instruction set

Processor instruction set refers to the complete set of all the instructions in machine code that can be recognized

and executed by a central processing unit. Different processors have different instruction sets.

Typical instruction set includes the following common operations:

o LOAD, STORE - data handling and memory operations

o ADD, SUBTRACT, DIVID, MULTIPLY etc - arithmetic operations

o >, <, = etc - comparison operations

o AND, OR, XOR, NOR, NOT etc - logical operations

o Control flow operations - conditional or unconditional

o Logical shifts

CAPE Computer Science Unit 1

o Halt

Instruction sets are differentiated by the following:

• Number of bits per instruction.

• Stack-based or register-based.

• Number of explicit operands per instruction.

• Operand location.

• Types of operations.

• Type and size of operands.

Instruction set formats

Computers only deal with bits 0 and 1s. They do not understand high level languages so compilers or assembled

are required to translate these into the machine code instructions that the microprocessor understands. These

machine-code instructions consist of a sequence of bits within the computer that also locate operands by

defining registers or memory address locations. The instruction is divided into group of bits called a field. The

instruction format may be of the following types:

Variable Instruction Formats

These are the instruction formats in which the instruction length varies on the basis of operation code and

address. These instruction formats are usually difficult to decode.

Fixed Instruction Formats

In this type of instruction format, all instructions the same size. For example, MIPS, POWER PC, Alpha, ARM.

This is much easier to decode.

Addressing Modes

Addressing modes provide different ways to access an address on a processor. Data is stored in the memory and

each instruction requires certain data on which it has to operate. There are various techniques to specify the

address of the required data. These techniques are called addressing modes.

• Direct addressing mode – the address of the operand is given in the instruction and data is available in that

memory location provided in the instruction

• Indirect addressing mode – the instruction specifies a register which contains the address of the operand.

Both internal RAM and external RAM can be accessed via indirect addressing mode.

• Immediate addressing mode – data is given directly in the operand which moves the data in the accumulator

• Relative addressing mode – the effective address is determined by the index mode by using the program

counter instead of a general-purpose process register

• Index addressing mode – the effective address of the operand is generated by adding a content value to the

contents of the register.

CPU clock

CPUs have a working speed, which is regulated by a crystal which is constantly vibrating at a very high rate.

This crystal impulse is sent to the CPU as a clock tick and each pulse can cause the CPU to perform one action.

CAPE Computer Science Unit 1

The number of clock ticks per second is measured in Hertz. Since the CPU’s crystal vibrates millions of times

each second so clock speed is measured in millions of oscillations (MHz or GHz).

Cache memory

A cache memory component is used to store data on a temporary basis. Data stored in the cache memory can be

access faster. Cache memory is faster than main memory, but slower than the CPU and its registers. Cache

memory, which is normally small in size, is placed between the CPU and main memory.

CAPE Computer Science Unit 1

You might also like

- Live Sound 101: Choosing Speakers and Setting Up a Sound SystemDocument14 pagesLive Sound 101: Choosing Speakers and Setting Up a Sound Systemohundper100% (1)

- Framing MMT - Modern Money NetworkDocument23 pagesFraming MMT - Modern Money NetworkUmkc Economists86% (7)

- Dalisaydepisioco : 2039bautistasubdsamala Marquezstbrgysamalamarquez 4104binakayankawitDocument6 pagesDalisaydepisioco : 2039bautistasubdsamala Marquezstbrgysamalamarquez 4104binakayankawitDalisay EpisiocoNo ratings yet

- Strengthening RC Structures with Steel Plate Bonding MethodsDocument29 pagesStrengthening RC Structures with Steel Plate Bonding MethodsSiti Rohani Isdris100% (1)

- Capital Harness XC LaunchDocument36 pagesCapital Harness XC LaunchnizarfebNo ratings yet

- CSEC Economics June 2017 P1Document9 pagesCSEC Economics June 2017 P1Rafena MustaphaNo ratings yet

- Co Notes Module 1Document42 pagesCo Notes Module 1Vinyas M SNo ratings yet

- Quadratics PDFDocument9 pagesQuadratics PDFRafena MustaphaNo ratings yet

- 10 Steps To Dream Building: - A Publication of Center My CenterDocument19 pages10 Steps To Dream Building: - A Publication of Center My CenterRamalakshmi100% (2)

- Computer Organization and Architecture Module 1 (Kerala University) NotesDocument30 pagesComputer Organization and Architecture Module 1 (Kerala University) NotesAssini Hussain100% (11)

- As 3566.1-2002 Self-Drilling Screws For The Building and Construction Industries General Requirements and MecDocument7 pagesAs 3566.1-2002 Self-Drilling Screws For The Building and Construction Industries General Requirements and MecSAI Global - APAC0% (2)

- Day 1 What Is Phased Array How Phased Array Works? Beam Forming Beam Focusing Beam Streeing Sectorial Scan and Linear ScanDocument64 pagesDay 1 What Is Phased Array How Phased Array Works? Beam Forming Beam Focusing Beam Streeing Sectorial Scan and Linear ScanvibinkumarsNo ratings yet

- File Signature LabDocument3 pagesFile Signature LabGheorghe RotariNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Module 1 of Computer OrganizationDocument27 pagesModule 1 of Computer OrganizationNimmymolManuelNo ratings yet

- Auditing Case 3Document12 pagesAuditing Case 3Kenny Mulvenna100% (6)

- Computer Organization and Architecture Module 1Document46 pagesComputer Organization and Architecture Module 1Assini Hussain100% (1)

- Cash Flow Statement and Balance Sheet of A Solar Power Plant in APDocument35 pagesCash Flow Statement and Balance Sheet of A Solar Power Plant in APSriharsha Vavilala100% (1)

- Tax2win's Growth Strategy Through Comprehensive Tax SolutionsDocument6 pagesTax2win's Growth Strategy Through Comprehensive Tax SolutionsAhmar AyubNo ratings yet

- Dhi-Ehs-Hsm-028 Work Over Water Rev0Document5 pagesDhi-Ehs-Hsm-028 Work Over Water Rev0Phạm Đình NghĩaNo ratings yet

- CPU components and instruction cycle explainedDocument11 pagesCPU components and instruction cycle explainedajit mhjNo ratings yet

- Cpu 1Document6 pagesCpu 1mayan nelsonNo ratings yet

- Rukonga Vision School Computer Science Grade 12 Processor and Memory ComponentsDocument8 pagesRukonga Vision School Computer Science Grade 12 Processor and Memory ComponentsireneNo ratings yet

- These RegistersDocument4 pagesThese RegistersArslan AzharNo ratings yet

- Co-2 - CoaDocument46 pagesCo-2 - CoaDAVU REVANTH NAGNo ratings yet

- Lecture 5 - CPU DesignDocument20 pagesLecture 5 - CPU Designnoberth nikombolweNo ratings yet

- Central Processing UnitDocument15 pagesCentral Processing Unithussain korirNo ratings yet

- Chp3.1 MicroarchitectureDocument5 pagesChp3.1 Microarchitectureheyfiez12No ratings yet

- What Is RegisterDocument2 pagesWhat Is RegisterHaris AkramNo ratings yet

- Basics of Operating Systems (IT2019-2) : Assignment IVDocument3 pagesBasics of Operating Systems (IT2019-2) : Assignment IVGiang LeNo ratings yet

- CS8493 Operating Systems - Unit IDocument24 pagesCS8493 Operating Systems - Unit ILokesh Srm100% (2)

- 1.1.1. Structure and Function of The ProcessorDocument7 pages1.1.1. Structure and Function of The Processorthenuk.rodrigoNo ratings yet

- Unit 2Document60 pagesUnit 2Ashish kumarNo ratings yet

- William Stallings Computer Organization and Architecture 8 EditionDocument59 pagesWilliam Stallings Computer Organization and Architecture 8 EditionjumarNo ratings yet

- Computer Architectur1Document31 pagesComputer Architectur1Abigail ChitongoNo ratings yet

- Central Processing UnitDocument12 pagesCentral Processing Unithussain korirNo ratings yet

- Chapter 6-Computer ArchitectureDocument34 pagesChapter 6-Computer ArchitectureVongai MubaiwaNo ratings yet

- CO2: 1. Concept of Program Execution/InterpretationDocument22 pagesCO2: 1. Concept of Program Execution/InterpretationYasmeen SyedNo ratings yet

- Intro To Microcomputers: Block Diagram of A Typical MicrocomputerDocument6 pagesIntro To Microcomputers: Block Diagram of A Typical MicrocomputerShaheer TariqNo ratings yet

- Lec4 Computer ArchitectureDocument37 pagesLec4 Computer ArchitectureAwe HughNo ratings yet

- Chapter 2Document20 pagesChapter 2esubalew sintieNo ratings yet

- Basic Structure of Computer ArchitectureDocument53 pagesBasic Structure of Computer Architecturenikhilmalagi0% (1)

- Computer ArchitectureDocument5 pagesComputer Architectureapi-417400228No ratings yet

- Register Involved in Computer ProcessDocument3 pagesRegister Involved in Computer ProcessMuhammad Husnain KhalidNo ratings yet

- CPU Organization and Main Memory Functions in Under 40Document15 pagesCPU Organization and Main Memory Functions in Under 40Vijay KumarNo ratings yet

- As Computer Science CH4Document4 pagesAs Computer Science CH4Ahmed RazaNo ratings yet

- Register SymbolDocument5 pagesRegister SymbolAdnan AliNo ratings yet

- Central Processing UnitDocument21 pagesCentral Processing Unithussain korirNo ratings yet

- Module 3: Understanding CISC and RISC Architectures and Control Units DesignDocument36 pagesModule 3: Understanding CISC and RISC Architectures and Control Units DesignNeel RavalNo ratings yet

- General Organisation of A Micro ProcessorDocument8 pagesGeneral Organisation of A Micro ProcessornelsrodrigNo ratings yet

- Chapter 2Document37 pagesChapter 2johnNo ratings yet

- Acn CpuDocument9 pagesAcn CpuHarshraj SinghNo ratings yet

- Sodapdf-Mazher 4Document6 pagesSodapdf-Mazher 4Mohammed Mazher40No ratings yet

- Hardware Organisation of Computers and MicroprocessorsDocument33 pagesHardware Organisation of Computers and MicroprocessorsUchenna OgunkaNo ratings yet

- Instruction Set ArchitectureDocument7 pagesInstruction Set ArchitectureKuzo TribeNo ratings yet

- Computer Organization and ArchitectureDocument21 pagesComputer Organization and ArchitectureJoan VincentNo ratings yet

- Module 5 MicroprocessorDocument7 pagesModule 5 MicroprocessornatsuNo ratings yet

- CPU Structure and Functions: Processor OrganizationDocument5 pagesCPU Structure and Functions: Processor OrganizationShahzadNo ratings yet

- Chapter 4 - SGDocument4 pagesChapter 4 - SGGabriel TomagosNo ratings yet

- Basic Design of MicrocomputerDocument3 pagesBasic Design of MicrocomputerBianca Axel GarciaNo ratings yet

- General Register-Based CPU Organization-4Document11 pagesGeneral Register-Based CPU Organization-4Dinesh KumarNo ratings yet

- 502 Reflection 2Document5 pages502 Reflection 2Brahmendra UpputuriNo ratings yet

- COA1Document56 pagesCOA1mayur jagdaleNo ratings yet

- Computer ArchitectureDocument4 pagesComputer ArchitectureAgrippa MungaziNo ratings yet

- CO Unit 1Document43 pagesCO Unit 1Dinkesh JainNo ratings yet

- Hardware (CH#3)Document6 pagesHardware (CH#3)itslilyjulesssNo ratings yet

- Draw The Block Diagram of Simple Microprocessor-Based System and Explain The Function of Each Block (You Can Use MS Word or Google Docs)Document8 pagesDraw The Block Diagram of Simple Microprocessor-Based System and Explain The Function of Each Block (You Can Use MS Word or Google Docs)Riza Pahama MananaongNo ratings yet

- Computer A & Organization NoteDocument16 pagesComputer A & Organization NoteabinetblackmanNo ratings yet

- Interview Questions On Embedded ProcessorsDocument5 pagesInterview Questions On Embedded ProcessorsKALYANNo ratings yet

- CPU Fundamentals: Fetch, Decode, Execute CyclesDocument25 pagesCPU Fundamentals: Fetch, Decode, Execute CyclesTey Wee KitNo ratings yet

- Ca Unit 1Document25 pagesCa Unit 1பவித்ரா வேNo ratings yet

- Examples of Processors With The RISC Architecture Include MIPSDocument4 pagesExamples of Processors With The RISC Architecture Include MIPSashu anyaNo ratings yet

- Meeting2-Block 1-Part 3Document29 pagesMeeting2-Block 1-Part 3Husam NaserNo ratings yet

- COADocument15 pagesCOAprathuasharao2017No ratings yet

- Div2022 Practice SheetDocument2 pagesDiv2022 Practice SheetRafena MustaphaNo ratings yet

- The OSI Model: How Network Protocols WorkDocument5 pagesThe OSI Model: How Network Protocols WorkRafena MustaphaNo ratings yet

- Roots of A Quadratic Equation PDFDocument2 pagesRoots of A Quadratic Equation PDFRafena MustaphaNo ratings yet

- Special Test 1Document2 pagesSpecial Test 1Rafena MustaphaNo ratings yet

- Quiz 5Document2 pagesQuiz 5Rafena MustaphaNo ratings yet

- Network DevicesDocument5 pagesNetwork DevicesRafena MustaphaNo ratings yet

- Control Structures PDFDocument8 pagesControl Structures PDFRafena MustaphaNo ratings yet

- Caribbean Economies PDFDocument16 pagesCaribbean Economies PDFRafena MustaphaNo ratings yet

- Selection SortDocument1 pageSelection SortRafena MustaphaNo ratings yet

- Exercises PDFDocument1 pageExercises PDFRafena MustaphaNo ratings yet

- Series and Sequences PDFDocument7 pagesSeries and Sequences PDFRafena MustaphaNo ratings yet

- 1.remainder and Factor Theorem, Dividind Polynomials PDFDocument7 pages1.remainder and Factor Theorem, Dividind Polynomials PDFGiovanni SlackNo ratings yet

- Bubble SortDocument5 pagesBubble SortRafena MustaphaNo ratings yet

- Queues PDFDocument6 pagesQueues PDFRafena MustaphaNo ratings yet

- Quadratic Inequalities PDFDocument4 pagesQuadratic Inequalities PDFRafena MustaphaNo ratings yet

- Linear Binary Search AlgorithmsDocument2 pagesLinear Binary Search AlgorithmsRafena MustaphaNo ratings yet

- QUEUES: Array ImplementationDocument6 pagesQUEUES: Array ImplementationRafena MustaphaNo ratings yet

- Arrays vs. Linked ListsDocument5 pagesArrays vs. Linked ListsRafena MustaphaNo ratings yet

- Binary SearchDocument4 pagesBinary SearchRafena MustaphaNo ratings yet

- Arrays Practice ProblemsDocument2 pagesArrays Practice ProblemsRafena MustaphaNo ratings yet

- EXERCISES: If-Else Statements and Simple FunctionsDocument1 pageEXERCISES: If-Else Statements and Simple FunctionsRafena MustaphaNo ratings yet

- Control Structures in Programming Languages: SequencingDocument8 pagesControl Structures in Programming Languages: SequencingRafena MustaphaNo ratings yet

- WORKSHEET 1: Input, Output, Variables and Arithmetic in CDocument1 pageWORKSHEET 1: Input, Output, Variables and Arithmetic in CRafena MustaphaNo ratings yet

- CS Review WK 1 - Sept 8 To 13 PDFDocument8 pagesCS Review WK 1 - Sept 8 To 13 PDFRafena MustaphaNo ratings yet

- Unit 2: Further Topics in Computer Science: MODULE 1: Data Structures What Is A Data Structure?Document9 pagesUnit 2: Further Topics in Computer Science: MODULE 1: Data Structures What Is A Data Structure?Rafena MustaphaNo ratings yet

- Iteration Exercises PDFDocument1 pageIteration Exercises PDFRafena MustaphaNo ratings yet

- Answer ALL Questions. Write Down The Letter That Corresponds To The Correct AnswerDocument4 pagesAnswer ALL Questions. Write Down The Letter That Corresponds To The Correct AnswerRafena MustaphaNo ratings yet

- Expository Essay SampleDocument1 pageExpository Essay SampleRafena MustaphaNo ratings yet

- Tourism and Development Planning: Slide 9.1Document19 pagesTourism and Development Planning: Slide 9.1English TimeNo ratings yet

- The Multi Faceted Nature of The Multi Grade TeacherDocument23 pagesThe Multi Faceted Nature of The Multi Grade TeacherTEDLYN JOY ESPINONo ratings yet

- United Nations Manual on Reimbursement for Peacekeeping EquipmentDocument250 pagesUnited Nations Manual on Reimbursement for Peacekeeping EquipmentChefe GaragemNo ratings yet

- Penetron Admix FlyerDocument2 pagesPenetron Admix Flyernght7942No ratings yet

- Best Frequency Strategies - How Often To Post On Social Media PDFDocument24 pagesBest Frequency Strategies - How Often To Post On Social Media PDFLiet CanasNo ratings yet

- Big Kaiser2019 PDFDocument624 pagesBig Kaiser2019 PDFGoto SamNo ratings yet

- Updated Scar Management Practical Guidelines Non-IDocument10 pagesUpdated Scar Management Practical Guidelines Non-IChilo PrimaNo ratings yet

- Caed102: Financial MarketsDocument2 pagesCaed102: Financial MarketsXytusNo ratings yet

- Telecommunications: Office of The Communications Authority (OFCA)Document2 pagesTelecommunications: Office of The Communications Authority (OFCA)ChiWoTangNo ratings yet

- Routine Pile Load Test-Ga-13.04.2021Document1 pageRoutine Pile Load Test-Ga-13.04.2021Digambar JadhavNo ratings yet

- The Influence of Culture Subculture On Consumer BehaviorDocument55 pagesThe Influence of Culture Subculture On Consumer Behaviorvijendra chanda100% (12)

- Design For Six Sigma Za PrevodDocument21 pagesDesign For Six Sigma Za PrevodSrdjan TomicNo ratings yet

- Segilola Gold ProjectDocument11 pagesSegilola Gold ProjectaishaNo ratings yet

- Editable Classroom Officers TemplateDocument6 pagesEditable Classroom Officers TemplateRachelle AbalosNo ratings yet

- Aviation Mechanic Powerplant Question Book1990Document112 pagesAviation Mechanic Powerplant Question Book1990LohnJittleNo ratings yet

- Prison Architect Calculator (V2.0)Document11 pagesPrison Architect Calculator (V2.0)freakman89No ratings yet

- Solenoid Valves 2/2 210: Pilot Operated FL Oating Diaphragm 3/8 To 2Document4 pagesSolenoid Valves 2/2 210: Pilot Operated FL Oating Diaphragm 3/8 To 2AlexanderNo ratings yet