Professional Documents

Culture Documents

CT1 Asic

Uploaded by

skarthikpriyaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CT1 Asic

Uploaded by

skarthikpriyaCopyright:

Available Formats

Reg. No. Reg. No.

SRM INSTITUTE OF SCIENCE AND TECHNOLOGY SRM INSTITUTE OF SCIENCE AND TECHNOLOGY

CYCLE TEST – I Feb-2019 CYCLE TEST – I Feb-2019

VI Semester – Electronics& Communication Engineering VI Semester – Electronics& Communication Engineering

15EC327E – ASIC Design 15EC327E – ASIC Design

Duration: 45 Mins Max. Marks: 25 Duration: 45 Mins Max. Marks: 25

PART – A (5 X 1 = 5 Marks) PART – A (5 X 1 = 5 Marks)

Answer ALL Questions Answer ALL Questions

1. Which design style has the shortest time to market 1. Which design style has the shortest time to market

a.Full custom b. Standard Cell c. Gate array d. FPGA a.Full custom b. Standard Cell c. Gate array d. FPGA

2. OAI221 CMOS logic cell has how many transistor 2. OAI221 CMOS logic cell has how many transistor

a. 10 b.12 c.14 d.8 a. 10 b.12 c.14 d.8

3. Which design style has the longest manufacturing lead time 3. Which design style has the longest manufacturing lead time

a.Full custom b. Standard Cell c. Gate array d. a.Full custom b. Standard Cell c. Gate array d.

FPGA FPGA

4. Advantage of TG when compared to PT 4. Advantage of TG when compared to PT

a)less no. of Transistor b)Faster c)Easy to design d)passes a)less no. of Transistor b)Faster c)Easy to design d)passes

good 0 & 1 good 0 & 1

5. NMOS acts as ………….device 5. NMOS acts as ………….device

a)Pull up b)pull down c)pull back d)pull side a)Pull up b)pull down c)pull back d)pull side

PART – B (2 X 4 = 8 Marks) PART – B (2 X 4 = 8 Marks)

Answer ANY TWO questions Answer ANY TWO questions

6. Realize 2i/p XNOR and XOR using transmission gate. 6. Realize 2i/p XNOR and XOR using transmission gate.

7. Elucidate Photolithographic process. 7. Elucidate Photolithographic process.

8. List some of the Design rules followed while drawing layouts 8. List some of the Design rules followed while drawing layouts

PART – C (1 X 12 = 12 Marks) PART – C (1 X 12 = 12 Marks)

Answer ALL questions Answer ALL questions

9. a. Compare Full custom ASIC design style with Semicustom 9. a. Compare Full custom ASIC design style with Semicustom

ASIC style ASIC style

OR OR

b. Implement D latch and FF using Transmission gates b. Implement D latch and FF using Transmission gates

You might also like

- Conference ContentDocument2 pagesConference ContentskarthikpriyaNo ratings yet

- NBA QP FORMAT - Cycle Test 01 - III Yr - EHOSDocument6 pagesNBA QP FORMAT - Cycle Test 01 - III Yr - EHOSskarthikpriyaNo ratings yet

- Instructors: Dr. Phillip JonesDocument44 pagesInstructors: Dr. Phillip JonesskarthikpriyaNo ratings yet

- Cpre 288 - Introduction To Embedded Systems: Instructors: Dr. Phillip JonesDocument89 pagesCpre 288 - Introduction To Embedded Systems: Instructors: Dr. Phillip JonesskarthikpriyaNo ratings yet

- MPC University LAB QuestionsDocument4 pagesMPC University LAB QuestionsskarthikpriyaNo ratings yet

- VLSI Design Course ECE Professional CoreDocument2 pagesVLSI Design Course ECE Professional CoreskarthikpriyaNo ratings yet

- Conference ContentDocument2 pagesConference ContentskarthikpriyaNo ratings yet

- Short Channel Effects and ScalingDocument23 pagesShort Channel Effects and ScalingskarthikpriyaNo ratings yet

- Cla1 - EhosDocument4 pagesCla1 - EhosskarthikpriyaNo ratings yet

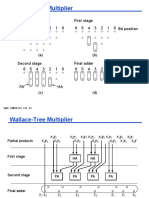

- Wallace-Tree Multiplier: 6 5 4 3 2 1 0 6 5 4 3 2 1 0 Partial Products First Stage Bit PositionDocument2 pagesWallace-Tree Multiplier: 6 5 4 3 2 1 0 6 5 4 3 2 1 0 Partial Products First Stage Bit PositionskarthikpriyaNo ratings yet

- The Interntional Womens Day 1Document1 pageThe Interntional Womens Day 1Karthik SekharNo ratings yet

- Short Channel Effects and ScalingDocument23 pagesShort Channel Effects and ScalingskarthikpriyaNo ratings yet

- 18CSC202J Set2Document1 page18CSC202J Set2skarthikpriyaNo ratings yet

- Water 1Document1 pageWater 1skarthikpriyaNo ratings yet

- 18CSC202J Set1Document1 page18CSC202J Set1skarthikpriyaNo ratings yet

- 18CSC202J Set2 ODD Reg NoDocument1 page18CSC202J Set2 ODD Reg NoskarthikpriyaNo ratings yet

- M.E. Computer Science and Engineering Curriculum and SyllabusDocument99 pagesM.E. Computer Science and Engineering Curriculum and SyllabusskarthikpriyaNo ratings yet

- Verilog Quiz1Document2 pagesVerilog Quiz1skarthikpriyaNo ratings yet

- Configure Serial Communication InterfaceDocument31 pagesConfigure Serial Communication InterfaceskarthikpriyaNo ratings yet

- M.E. Computer Science and Engineering Curriculum and SyllabusDocument99 pagesM.E. Computer Science and Engineering Curriculum and SyllabusskarthikpriyaNo ratings yet

- 18CSC202J Set1 Even Reg NoDocument1 page18CSC202J Set1 Even Reg NoskarthikpriyaNo ratings yet

- UML Component Diagram TutorialDocument3 pagesUML Component Diagram TutorialskarthikpriyaNo ratings yet

- UML - Deployment Diagrams - Tutorialspoint PDFDocument3 pagesUML - Deployment Diagrams - Tutorialspoint PDFskarthikpriyaNo ratings yet

- Optimize CPU time with 8279 keyboard display controllerDocument37 pagesOptimize CPU time with 8279 keyboard display controllerNihar PandaNo ratings yet

- CDC Question TemplateDocument4 pagesCDC Question TemplateskarthikpriyaNo ratings yet

- UML Component Diagram TutorialDocument3 pagesUML Component Diagram TutorialskarthikpriyaNo ratings yet

- Optimize CPU time with 8279 keyboard display controllerDocument37 pagesOptimize CPU time with 8279 keyboard display controllerNihar PandaNo ratings yet

- Configure Serial Communication InterfaceDocument31 pagesConfigure Serial Communication InterfaceskarthikpriyaNo ratings yet

- SCS1202 - Object Oriented Programming Unit 2 Classes and ObjectsDocument17 pagesSCS1202 - Object Oriented Programming Unit 2 Classes and ObjectsakjissNo ratings yet

- Xilinx SDKDocument11 pagesXilinx SDKskarthikpriyaNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Solid State Viva QuestionsDocument7 pagesSolid State Viva QuestionsAnanya SNo ratings yet

- M.E VLSI Technology UNIT IDocument64 pagesM.E VLSI Technology UNIT IMahendra BabuNo ratings yet

- Chapter 4 Problems and SolutionsDocument52 pagesChapter 4 Problems and Solutions박병준No ratings yet

- IRF6215 DatasheetzDocument9 pagesIRF6215 DatasheetzBoniface AsuvaNo ratings yet

- STN2907 (PNP Silicon Transistor) DatasheetDocument4 pagesSTN2907 (PNP Silicon Transistor) Datasheetfraile66No ratings yet

- Tranzistori Predavanja ME PDFDocument12 pagesTranzistori Predavanja ME PDFzententiniNo ratings yet

- Unit-3 Combinational Circuit Adders Subtractor Decoder-Encoder Multiplexers-Demultiplexers Comparator Parity IC FamilyDocument38 pagesUnit-3 Combinational Circuit Adders Subtractor Decoder-Encoder Multiplexers-Demultiplexers Comparator Parity IC Familysai vamsiNo ratings yet

- 2015 - FS-2 - K. W. Lee - Advanced 2.5D3D Hetero-Integration Technologies at GINTI, Tohoku UniversityDocument5 pages2015 - FS-2 - K. W. Lee - Advanced 2.5D3D Hetero-Integration Technologies at GINTI, Tohoku UniversityPham ThaoNo ratings yet

- Sic Appli-EDocument89 pagesSic Appli-EKrishna KumarNo ratings yet

- Presented By, Narendra Kuppili, Analog IC Layout EngineerDocument27 pagesPresented By, Narendra Kuppili, Analog IC Layout EngineermanojkumarNo ratings yet

- Lec02 Ae Ms14Document59 pagesLec02 Ae Ms14Mohsin Abbas ZafarNo ratings yet

- HLF IC List From Gary HongDocument8 pagesHLF IC List From Gary HongAndré CrowleyNo ratings yet

- IR21091(S) half-bridge driver data sheetDocument8 pagesIR21091(S) half-bridge driver data sheetGilsonNo ratings yet

- Vlsi Design Unit 3 2019Document34 pagesVlsi Design Unit 3 2019Ishan Mahendra PatelNo ratings yet

- 2-Metal Semiconductor ContactsDocument32 pages2-Metal Semiconductor ContactsSiddhesh GhodekarNo ratings yet

- Capacitance Fall Into Two Categories Intrinsic Capacitance Extrinsic CapacitanceDocument10 pagesCapacitance Fall Into Two Categories Intrinsic Capacitance Extrinsic Capacitancewajid aliNo ratings yet

- Semiconductor Primer 4.0 0117Document409 pagesSemiconductor Primer 4.0 0117kevinjkrausNo ratings yet

- Si4501BDY: Vishay SiliconixDocument14 pagesSi4501BDY: Vishay SiliconixAndré RegisNo ratings yet

- Questions On Transistor CharacteristicsDocument72 pagesQuestions On Transistor Characteristicskibrom atsbha50% (2)

- Transistor Circuit Manual 1961 - Allan LytelDocument256 pagesTransistor Circuit Manual 1961 - Allan LytelshirtquittersNo ratings yet

- Thyristor Family PSDDocument18 pagesThyristor Family PSDHiren H. Patel100% (1)

- CD4001BM!CD4001BC Quad 2-Input NOR Buffered B Series Gate CD4011BM!CD4011BC Quad 2-Input NAND Buffered B Series GateDocument8 pagesCD4001BM!CD4001BC Quad 2-Input NOR Buffered B Series Gate CD4011BM!CD4011BC Quad 2-Input NAND Buffered B Series Gatehenrique LeonardoNo ratings yet

- Simulation of Organic TFT With TCAD ToolsDocument81 pagesSimulation of Organic TFT With TCAD ToolsdebmallyNo ratings yet

- Troubleshooting For Rb433R3, Rb433Ur2: No Power, Blue Led Isn'T LitDocument7 pagesTroubleshooting For Rb433R3, Rb433Ur2: No Power, Blue Led Isn'T LitJoseAugustoOsteicoechea100% (1)

- EE230 - Fall 2014 Chapter 5: The MOS Capacitor Chapter 6: The MOS TransistorDocument14 pagesEE230 - Fall 2014 Chapter 5: The MOS Capacitor Chapter 6: The MOS TransistorSaied Aly SalamahNo ratings yet

- Lecture 4 - Implementing Logic in CMOSDocument32 pagesLecture 4 - Implementing Logic in CMOSsadia santaNo ratings yet

- Lab ManualsDocument27 pagesLab ManualsPrafulani GajbhiyeNo ratings yet

- Solar Photovoltaics: Fundamentals, Technology and ApplicationsDocument1 pageSolar Photovoltaics: Fundamentals, Technology and ApplicationspksahunitrklNo ratings yet

- SERVICE MANUAL AND ELECTRICAL PARTS LIST FOR CHIME & SIREN PE-9103ADocument5 pagesSERVICE MANUAL AND ELECTRICAL PARTS LIST FOR CHIME & SIREN PE-9103AtrujbNo ratings yet

- Irfp 9140 NDocument9 pagesIrfp 9140 NCodinasound CaNo ratings yet