Professional Documents

Culture Documents

Hybrid Phase Comparator Applied To Distance Protection

Uploaded by

quisi123Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Hybrid Phase Comparator Applied To Distance Protection

Uploaded by

quisi123Copyright:

Available Formats

Hybrid phase comparator applied to distance

protection

P.G. McLaren, B.Sc, M.A., Ph.D., C.Eng., M.I.E.E. and M.A. Redfern, B.Sc.

Indexing terms: Phase comparators, Power system protection, Power transmission lines, Relay protection

Abstract

The paper describes the operation of a 1 bit processor which can be used to measure phase difference, and hence

can be applied to distance protection. The processor averages over one cycle the sign coincidence between its two

input signals and gives an analogue output proportional to their phase difference. Examples are given of its

application to mho and quadrilateral impedance characteristics. Where appropriate its performance is compared

with a block-average comparator.

List of symbols comparator is faster throughout, but it is considerably faster close to

the boundary. As will be seen later, this speed of operation close to

V = voltage at the relaying point the boundary is achieved at the expense of stability with regard to

/ = current at the relaying point boundary faults. An improvement in boundary accuracy can be

ZR = replica impendance

ZL = line impedance

Zs = source impedance

ZF = ZFL<t> = impedance to fault from the relaying point

Wlf W2, W3 = relay inputs

output to

1 Introduction trip-level

detectors

The block-average phase comparator has been widely applied

in distance-protection schemes.1 The block-average principle, how-

ever, can give rise to unacceptably long operating times for fault

impedances not lying on the characteristic impedance of the com-

parator. On the other hand, its boundary accuracy is very high.

The phase comparator described in this paper retains the aver-

aging function of the block-average comparator but reduces the aver- (i) output of the one-bit comparator

aging period to one cycle of the power frequency. The amplitude of the V —<•'•>

the output signal from the device is linearly proportional to phase dif- (n)W,=V-IZR

ference between its input signals. Trip signals are derived from level trip

detectors which monitor the appropriate output level and by incor- level

porating suitable delays in the level detector circuits, the timing charac-

teristic of the comparator can be given any desired shape. The hardware (MI) output of the block-average

necessary to realise the comparator consists of readily available and well comparator.

established small-scale integrated circuits.

Results are given for online tests on a model transmission line and

the performance of a block-average comparator is included for com-

parison. An offline computer simulation is used to give a more varied 8 x 8 bit shift registers

testing facility, and results are given for the comparator used in mho-

and quadrilateral-characteristic applications.

Schmitt trigger

zero-crossing register[ //• 1 register |—

2 Basic comparator detectors

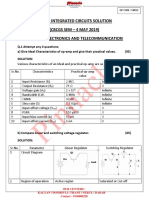

The block diagram of the comparator is shown in Fig. la.

The input signals Wy and W2 are derived from the relaying point trans- input

ducer outputs by suitable mixing circuits. The input amplifiers, which amplifiers summing-amplifier

input resistors

include accurate zero-crossing detectors, convert the input signals

into square waveforms and a polarity comparison is then performed.

The comparison waveform is then sampled at a rate determined by

the master-clock frequency and a '1' or a '0' is loaded into the shift

summing trip-level

register according to whether the sampled signal is positive or zero. amplifier detector

The register length is chosen such that it can hold the number of

samples taken in one cycle (20 ms for 50 Hz). The bit values, either

T or '0', in the register are summed using an analogue summing

amplifier, details of which are given in Fig. \c and in the Appendix

(Section 7), and the output of this amplifier is monitored by level Fig. 1

detectors. The output amplitude is proportional to the phase differ- 1 bit comparator

ence, in the steady state, between Wx and W2 and the level detectors a Block diagram

can be set to correspond to any desired phase-angle trip level. Fig. \b b Typical input and output waveforms, including block-average output for

shows how the summing-amplifier output varies when the phase angle comparison

c Circuit diagram

between Wt = V — IZR and W2 = V changes from 180° prefault to

60° postfault. The block-average output included in Fig. 16 has a

basic minimum operating time of 10 ms. Fig. 2a shows the timing achieved by using trip-time delays and thereby producing any desired

contour of the 1 bit comparator when the trip level is set for ± 90°. shape of timing characteristic.

Fig. 2b shows the corresponding contours for a ±90° block-average

comparator with a basic minimum operating time of 10 ms. The 1 bit 3 Mho characteristic

A hardware unit was built with a register length of 64

Paper 7549 P, first received 21st April and in final form 15th August 1975

locations and the clock frequency was thus set to 3200 Hz. The level

detector trip circuit was set at the level corresponding to 6 = ±90°.

Dr. MacLaren and Mr. Redfern are with the University Engineering Department,

Trumpington Street, Cambridge CB2 1P2, England Voltage and current signals were derived from a single-phase test

PROC. IEE, Vol. 122, No. 11, NOVEMBER 1975 1295

circuit having a source impedance Za of 0-25 p.u. Z_70°, and a line the thyristor in the point-on-wave switch close to current zero.

impedance Z2 of 1 -0 p.u. Z.7O0. A variable fault resistance RF was Fig. \b is for a fault impedance giving 6 equal to 60° and Fig. 3 is for

connected in series with a point-on-wave switch which controlled the a fault impedance giving 0 = 90°. Both Fig. \b and Fig. 3 show that

the 1 bit comparator approaches its steady-state level faster than the

block-average comparator for fault impedances not lying on the

characteristic impedance of the mho circle. They also demonstrate

that the one-bit comparator output may temporarily overshoot its

steady state output.

3O-

time, ms

2O-

-90 -6O -3O 3O 6O 9O

0. deg

time, ms

Fig. 3

Comparator responses to a typical boundary fault condition

a Fault incidence at maximum voltage

b Fault incidence at zero voltage

Zp = 0-96 p.u. Z.56°

(i) 1 bit comparator output

(ii) V-IZR input waveform

(Hi) Block-average comparator output

The operating times for a number of fault impedances are shown

in Fig. 4.; Fig. 4a for faults at zero voltage and Fig. 46 for faults at

maximum voltage. The latter gives maximum overshoot which in

Fig. 4b is of the order of 10%. To minimise this overshoot the level

detector circuit was altered to give the dual trip mechanism shown in

Fig. 5fl. This circuit tripped without delay if the 75° level was reached,

reached, but imposed an 8 ms delay on levels between 90° and 75°.

6O 90

Fig. Sb shows the steady-state timing contour for this trip mechanism.

9. deg

Fig. 6 shows the operating times for the 1 bit-comparator mho relay

with the new trip mechanism. The overshoot has now been reduced

to 3%, without increasing operating times in the heart of the charac-

teristic by more than 2 ms. This overshoot is now of the same order

Fig. 2 as the angular resolution of the device, i.e. 3° in 90°.

Response times for a mho characteristic To investigate the performance of the 1 bit comparator over a

a 1 bit comparator

wider range of fault conditions than could be achieved on the limited

b Block-average comparator online test facilities available, an offline computer simulation of a 128

0 = postfault phase angle bit comparator was set up. The offline simulation used a source

c = minimum timing

d = maximum timing impedance of 0-5 p.u. Z_89°, a line impedance of 1 -0 p.u. Z.85° and a

prefault phase angle = 180° ZR equal to 1 0 p.u. Z_75°. A prefault load impedance of 10 p.u. Z.0 was

connected at the end of the line. The angular resolution of a 128 bit

instant of fault incidence. comparator is 1 -5°. Fig. la shows the comparator responses for an

The voltage V and the current / measured at the junction of the impedance to fault of 0-625 Z.470. This is similar to the fault im-

source and line impedance were transformed and mixed to produce pedance in Fig. \b, and it can be seen that the two outputs are

signals Wx and W2, where Wt = Fand W2 = V~IZR.ZR was set at basically similar. Fig. 1b, c and d show comparator outputs for faults

1 p.u. L15°. A block-average comparator was supplied with the same on Z L . Trip times are shown for the 1 bit comparator with and with-

input signals Wx and W2 in order that the block-average ramp voltage out the dual trip mechanism. By interpolating between Fig. 1c and d

could be compared with the 1 bit comparator output. A storage it would appear that for faults on ZL an overshoot of 3% might be

oscilloscope was used to display expected without the dual trip mechanism and no overshoot with the

dual trip mechanism. Fig. 8a and b show trip times for the basic mho

(a) the 1 bit comparator output comparator for a selection of fault impedances. These same points

(b)W2 = V-IZR will be used in assessing a quadrilateral characteristic in Section 4.

(c) the block-average ramp voltage.

Signals (a) and (c) were arranged to ramp in opposite directions so 4 Quadrilateral characteristic

that the centre line corresponds to the trip level for both comparators. Rushton and Humpage2 have shown that for long lines the

Fig. \b and Fig. 3 show a number of traces for various fault con- mho characteristic has too great a reach in the resistive direction and

ditions. The nonlinearities in W2 were produced by the behaviour of that for short lines it does not include a substantial proportion of the

1296 PROC. IEE, Vol. 122, No. 11, NOVEMBER 1975

anticipated fault area. The same authors conclude that a quadrilateral equivalent delay of 8 x 360/128 = 225°. The effect of this delay is

characteristic is the optimum shape. to rotate the angular data from IZR to positions OA and PB in Fig.

9a. The block diagram for the quadrilateral characteristic relay is

75° trip

trip

comparator output

output

9O°trip —Cj

8ms delay

75 trip ! 90 trip

3O-- I 8ms delay

2O-

10-

3O 60 75 90

O- 9. deg

Fig. 5

Dual-trip comparator

a Block diagram

b Response times

,,+ 18%. 19-5 +

16+ i e \

"+J6 « *

Fig. 4

Trip times for the 1 bit comparator

a Fault incidence at voltage zero

b Fault incidence at voltage maximum,

n.t. = no trip; trip times in milliseconds

Two 1 bit comparators can be used to produce the characteristic

shape shown in Fig. 9a. Comparator one measures the phase angle

between Fand IZR, where ZR = 1 -1 p.u.7.65°, and has trip levels of Fig. 6

—33-25° and +79-25°. Comparator two measures the phase angle Trip times for the dual-trip comparator

between V—IZR andIZR and has trip levels of—22-5°.and +67-5°. a Fault incidence at voltage zero

characteristic includes 1-02 p.u. of the line impedance at 85°. n.t. = no trip; trip times in milliseconds

This characteristic includes 1 -02 p.u. of the line impedance at 85°.

and negative angles. To reduce the angular limits to ± 56-75° for shown in Fig. 9b. Fig. 10 shows trip times for the relay for the same

comparator one and ± 45° for comparator two, the IZR squared grid of fault impedances as were used to test the mho characteristic.

waveform is routed via an 8 location 1 bit shift register to produce an The prefault impedance was 1 -0 p.u. £85° + 10 p.u. L0°. Faults

PROC. IEE, Vol. 122No. 11, NOVEMBER 1975 1297

within the characteristic were found in times varying from 12 to mechanism would add 1 -7 ms to operating times for fault angles up to

20 ms. For faults in the area between ZL and ZR the overshoot was 30°.

comparator output, deg

n.t.

H 1—I

I8O-1-

comparator output, deg

O-r

20 4O 6O 80

180 - *

comparator output, deg

0-r

Fig. 6 (continued)

Trip times for the dual-trip comparator 9O-

b Fault incidence at voltage maximum

n.t. = no trip; trip times in milliseconds

input waveforms from system 180^

Wi=V

W 3 =I

Fig. 7

Input and output waveforms for the lbit comparator

b Zp — 0"5 p.u. ^85°, fault incidence at voltage zero, trip time = 9-53 ms

c Zp — 1-Op.u. L&5°, fault incidence at voltage zero, trip time = 18-91 ms

d Zp = 1-05 p.u. LSS°, fault incidence at voltage zero, no trip

derived waveform

24-84

9O

time, ms

comparator output, deg

OT

n.t.

9O- H 1-

I8O"1-

Fig. 7

Input and output waveforms for the 1 bit comparator Fig. 8

Trip times for the 1 bit comparator mho characteristic

a Zp = 0-63 p.u. Z_47°, fault incidence at 120° after voltage zero, trip time :

lS-31ms a Fault incidence at voltage zero

less than 10%. A dual trip mechanism of direct trip at 30° and a An interesting case is where there is no prefault current, i.e. line

5 ms delay between 45° and 30° would reduce this overshoot to open circuit. Here both comparators indicate a 90° phase shift

within the angular resolution of the comparator (1 -5°). Such a

1298 PROC. IEE, Vol. 122, No. 11, NOVEMBER 1975

prefault and both have to ramp into the trip area when the fault is 5 Conclusions

applied. The directional comparator quickly indicates the direction of

The performance of the 1 bit comparator has been examined

in both mho and quadrilateral-characteristic applications. It has been

n.t. ji.t.

n.t.

n.t.

B (I6-7-I8-9)

B (16-3-19-5)

B (I5-8-2O-O)

B (I5-5-2O-O)

BII5-5-I9-8)

BII5-3-I9-5)

Fig. 8 (continued)

Trip times for the 1 bit comparator mho characteristic

b Fault incidence at voltage maximum

X

comparator two

P

Fig. 10

Trip times for the quadrilateral characteristic

a Fault incidence at voltage zero

1 blocked in 1-4 ms

B2 tripped from 17-0-22-8 ms and 36-3-43-8 ms

B3 tripped from 1 31-22-7 ms and 36-7-63-8 ms

B tripped for times shown in brackets

All times in milliseconds, prefault impedance Zj^ + 10-0 p.u. L0°

comparator one

v

f squaring comparator one trip-

V circuit level

128 bit detector

reference

impedence v

z squaring 8 bit delay trip

and circuit register output

mixing

circuits

i comparator two trip-

v

f"vz squaring level

circuit 128 bit detector

Fig. 9

Quadrilaterla characteristic using two 1 bit comparators

a Characteristic

b Block diagram

shown how the steady-state and transient timing contours can be

altered to suit a given compromise between speed of operation and

the fault and causes little delay in the operation of the protection boundary accuracy.

circuit. A typical result is shown in Fig. 11 for a 95% reach fault. Since the comparator measures rather than monitors phase

PROC. IEE, Vol. 122, No. 11, NOVEMBER 1975 1299

difference the output of the suniming amplifier can be checked during input amplifiers and t.t.l. Schmitt triggers. The resultant waveforms

nonfault conditions by observing that the indicated phase difference therefore contained only the polarity information of the input

input waveforms for comparator one

W| =V

W 3 =IZ R

input waveforms for comparator two

W2 = I Z R

W3=IZR

B (19-7 -21-4)

i i time, ms

B (I9-4-2H)

B (19-7-22-7)

comparator output, degs

O-r

B (19-5-22-7)

9O- •V- 1 h ^ 1 1 1 1

Fig. 10 (continued) Fig. 11

Trip times for the quadrilateral characteristic Input and output waveforms for the quadrilateral characteristic

comparator

b Fault incidence at voltage maximum

1 boundary case, 45 in 19-8 ms but no trip Zp = 0-95 p.u. L8S°, fault incidence at voltage zero

2 blocked in 0-78 ms Output wave forms comparator one • comparator two

B tripped for time shown in brackets

All times in milliseconds, prefault impedance Z/, + 10-0 p.u. L0° signals. These polarity waveforms were then compared using an

Exclusive 'OR' gate. This produced a signal whose value was T if the

is consistent with system operating conditions. The level detector input waveforms were of unlike polarity and '0' if they were of the

circuit could also incorporate an alarm signal which is triggered when same polarity. This polarity coincidence waveform was then sampled

the measured phase angle approaches the trip level by less than a and the samples were loaded into the shift register.

prescribed amount. The shift register was 64 bits long, comprising 8 x 8 bit shift

The use of 1 bit comparators to produce a 3-zone distance element registers in series. At each sampling instant the register's contents

incorporating a distance-to-fault measurement will be considered in were moved along the register by one location and the new sample

another paper. was loaded into the first element. The information in the final

location was discarded. Using a sampling rate of 3-2 kHz, i.e. 64

6 References samples per cycle, the register therefore contained one power

1 JACKSON, L., PATRICKSON, J.B., and WEDEPOHL, L.M.: 'Distance frequency period of coincidence data. The summation of the bit

protection: optimum dynamic design of static relay comparators', values of each element of the shift register provided the measure of

Proc. IEE, 1968, 115, (2), pp. 280-287 duration of polarity noncoincidence for the previous power frequency

2 HUMPAGE, W.D., and RUSHTON, J.: 'Power-system studies for the period, and hence a measure of the phase angle between the input

determination of distance-protection performance', ibid. 1972, 119, (6), waveforms. This summation was achieved using an analogue sum-

pp.677-688

mation amplifier. Input resistors were connected between the outputs

of each element of the shift register and the summing junction input

7 Appendix: Circuitry for the prototype 1 bit

of the output amplifier as shown in Fig. \c and the feedback resistor

comparator was chosen to give an output voltage range equivalent to phase angles

The prototype circuits were designed to use readily available between 0 and 180°. The zero output voltage was equivalent to 90°,

components and to demonstrate the design operations. The principal which when using the mho-circle relay characteristic was the trip

integrated circuits used were the '741' series t.t.l. logic circuits. level. The 64 input resistors for the summing amplifier were all

The comparators input signals were first 'squared' using high-gain and the output voltage varied between ± 10 V.

1300 PROC. IEE, Vol. 122, No. 11, NOVEMBER 1975

You might also like

- Section 5 - Triangles - Part 1 Answer KeyDocument48 pagesSection 5 - Triangles - Part 1 Answer KeyErryn Lowe100% (2)

- IEC 60076-1-Power Transformers PDFDocument96 pagesIEC 60076-1-Power Transformers PDFquisi123No ratings yet

- Network Protection and Automation Guide - Alstom PDFDocument508 pagesNetwork Protection and Automation Guide - Alstom PDFquisi123100% (5)

- IEC 61850-Based Adaptive Protection System For The MV DistributionDocument8 pagesIEC 61850-Based Adaptive Protection System For The MV Distributionquisi123No ratings yet

- Balint Training System 1948Document16 pagesBalint Training System 1948Laura Acosta100% (2)

- Design Considerations For VRM ResponceDocument8 pagesDesign Considerations For VRM ResponceKKKNo ratings yet

- 12 Chapter4 PDFDocument24 pages12 Chapter4 PDFnagarajuNo ratings yet

- Transformer Diagnostic Testing Response: FrequencyDocument10 pagesTransformer Diagnostic Testing Response: Frequencyosvi009No ratings yet

- Calculation of Reference Values:: Ref Ref, A/ B Nom A/bDocument7 pagesCalculation of Reference Values:: Ref Ref, A/ B Nom A/bTufail AlamNo ratings yet

- Adaptive Hysteretic Comparator With Op-Amp Threshold Level Setting-2008Document4 pagesAdaptive Hysteretic Comparator With Op-Amp Threshold Level Setting-2008Suhas ShirolNo ratings yet

- Synthetic-Ripple Modulator For Synchronous Buck ConverterDocument4 pagesSynthetic-Ripple Modulator For Synchronous Buck ConverterBishoo ShenoudaNo ratings yet

- How The Voltage Reference Affects ADC Design Part 2 PDFDocument6 pagesHow The Voltage Reference Affects ADC Design Part 2 PDFThanos van RamNo ratings yet

- AED Notes SECTION ADocument13 pagesAED Notes SECTION AShivam RaiNo ratings yet

- Experiment 5 Integrator, Differentiator and Non-Linear Properties of OpampsDocument7 pagesExperiment 5 Integrator, Differentiator and Non-Linear Properties of OpampsEnes AyduranNo ratings yet

- Silicon Wafer (Substrate) Preparation 2. Epitaxial Growth 3. Oxidation 4. Photolithography 5. Diffusion 6. Ion Implantation 7. Isolation Techniques 8. MetallizationDocument21 pagesSilicon Wafer (Substrate) Preparation 2. Epitaxial Growth 3. Oxidation 4. Photolithography 5. Diffusion 6. Ion Implantation 7. Isolation Techniques 8. MetallizationMangaiyarkarasi VengatachalamNo ratings yet

- PWM Boost DC-DC Converter Small-Signal AnalysisDocument8 pagesPWM Boost DC-DC Converter Small-Signal AnalysisVinhNo ratings yet

- Nonlinear Carrier Control Boosts Power FactorDocument7 pagesNonlinear Carrier Control Boosts Power FactorSv SandeepNo ratings yet

- Experiment 1 - Introduction To Electronic Test Equipment: W.T. Yeung and R.T. HoweDocument14 pagesExperiment 1 - Introduction To Electronic Test Equipment: W.T. Yeung and R.T. HoweFairos ZakariahNo ratings yet

- Design and Simulation of Triggering Circ PDFDocument4 pagesDesign and Simulation of Triggering Circ PDFYimy GarciaNo ratings yet

- A Comparative Study of PWM Control Techniques For Multilevel Cascaded InverterDocument4 pagesA Comparative Study of PWM Control Techniques For Multilevel Cascaded InverterRodovarNo ratings yet

- 11.Zero-Crossing Detector For AcDocument6 pages11.Zero-Crossing Detector For AcSourabh kulkarniNo ratings yet

- Non Ideal BehaviorDocument9 pagesNon Ideal BehaviorTushar DaveNo ratings yet

- Lab#9 (Common Emitter Amplifier)Document6 pagesLab#9 (Common Emitter Amplifier)Muhammad HamzaNo ratings yet

- Resistance Calibration Method Without ExDocument4 pagesResistance Calibration Method Without ExEmil HesenovNo ratings yet

- Network Analyzer Measurements: ELEC 453/6391 Microwave Engineering Experiment #4Document8 pagesNetwork Analyzer Measurements: ELEC 453/6391 Microwave Engineering Experiment #4matt tNo ratings yet

- Lic Solution 1Document29 pagesLic Solution 1Muiz TankiNo ratings yet

- Measuring Ferrite ChokesDocument4 pagesMeasuring Ferrite Chokesdavid reyesNo ratings yet

- A CMOS Bandgap ReferenceDocument10 pagesA CMOS Bandgap ReferencemeslonNo ratings yet

- Cmos Comparator: Term Paper Eem-511: Analog Electronics DesignDocument11 pagesCmos Comparator: Term Paper Eem-511: Analog Electronics Designvipul4792No ratings yet

- IEEE Transactions on Power Apparatus and Systems - Transformer Diagnostic Testing by FRADocument10 pagesIEEE Transactions on Power Apparatus and Systems - Transformer Diagnostic Testing by FRAentindanNo ratings yet

- Analysis and Design of a 5-GHz Low Noise Phase Quadrature VCO Using Varactor DiodeDocument5 pagesAnalysis and Design of a 5-GHz Low Noise Phase Quadrature VCO Using Varactor DiodenavinrkNo ratings yet

- Research Paper of OscillatorsDocument10 pagesResearch Paper of OscillatorsRam MNo ratings yet

- Uc Power Control PDFDocument6 pagesUc Power Control PDFjokerNo ratings yet

- Precision Constant Current Source For Electrical Impedance TomographyDocument5 pagesPrecision Constant Current Source For Electrical Impedance TomographyFitri PuspasariNo ratings yet

- Analog CommunicationDocument48 pagesAnalog CommunicationBrzata Ptica100% (1)

- Effect of Finite Amplifier Gain, Bandwidth, and Non-Idealities of Switches in Switched Capacitor Ladder CircuitsDocument6 pagesEffect of Finite Amplifier Gain, Bandwidth, and Non-Idealities of Switches in Switched Capacitor Ladder CircuitssdfasdfNo ratings yet

- A CMOS Mixed-Signal 100 MB S Receive Architecture For Fast EthernetDocument4 pagesA CMOS Mixed-Signal 100 MB S Receive Architecture For Fast EthernetYX PNo ratings yet

- An Accurate AC Current-to-Voltage Converter Based On A Fully Compensated Current ComparatorDocument2 pagesAn Accurate AC Current-to-Voltage Converter Based On A Fully Compensated Current ComparatorAjvanhoe AjvanhoeNo ratings yet

- A Versatile Monolithic Voltage-to-Frequency ConverterDocument13 pagesA Versatile Monolithic Voltage-to-Frequency ConverterGojko RatkovićNo ratings yet

- Fuzzy logic excitation control for synchronous generatorsDocument6 pagesFuzzy logic excitation control for synchronous generatorswilliamNo ratings yet

- Conditioning and Correction of Arbitrary Waveforms - Part 1: DistortionDocument7 pagesConditioning and Correction of Arbitrary Waveforms - Part 1: DistortionmehralsmenschNo ratings yet

- Capacitance and Tan δDocument7 pagesCapacitance and Tan δWaleed AwanNo ratings yet

- Carrier Based Sinusodial PWM Scheme For The Nine Switch ConverterDocument6 pagesCarrier Based Sinusodial PWM Scheme For The Nine Switch ConverterShankar MukalNo ratings yet

- Am ModulationDocument9 pagesAm ModulationBrzata PticaNo ratings yet

- Jpe 8-4-6 PDFDocument13 pagesJpe 8-4-6 PDF386No ratings yet

- Two Notes On The Performance of Rectifier Modulators by D. G. TUCKER, D.SC, Associate MemberDocument5 pagesTwo Notes On The Performance of Rectifier Modulators by D. G. TUCKER, D.SC, Associate MembershirtquittersNo ratings yet

- Antenna Impedance Matching - Simplified: Dr. Anitha GovindDocument5 pagesAntenna Impedance Matching - Simplified: Dr. Anitha GovindArnab PattanayakNo ratings yet

- Aacd99 BookDocument29 pagesAacd99 BookMahmoud HassanNo ratings yet

- VFD How To Measure Output VoltageDocument4 pagesVFD How To Measure Output Voltageboba78No ratings yet

- Cap. 8 Jacob - AE Leccion AutonomaDocument83 pagesCap. 8 Jacob - AE Leccion AutonomaAngel ZumbaNo ratings yet

- Adaptive Single Pole Auto-Reclosing Using Discrete Wavelet TransformDocument14 pagesAdaptive Single Pole Auto-Reclosing Using Discrete Wavelet TransformmosojiNo ratings yet

- Lecture 4A SignalConditioning DCBRIDGE SVDocument48 pagesLecture 4A SignalConditioning DCBRIDGE SVFazdrul AkiffNo ratings yet

- A 6.1-7.68 GHZ CMOS LC-Voltage Controlled Oscillators (VCO)Document4 pagesA 6.1-7.68 GHZ CMOS LC-Voltage Controlled Oscillators (VCO)dhrubNo ratings yet

- Low Voltage Capacitance & Tan Delta Testing, Measurement Method &Document6 pagesLow Voltage Capacitance & Tan Delta Testing, Measurement Method &intrudentalert100% (1)

- Analysis of Cmos Dynamic Comparators For Low Power and High Speed AdcsDocument7 pagesAnalysis of Cmos Dynamic Comparators For Low Power and High Speed AdcsNoReply ProgramNo ratings yet

- Function Generator Op-Amp Summing Circuits Pulse Width Modulation LM311 ComparatorDocument7 pagesFunction Generator Op-Amp Summing Circuits Pulse Width Modulation LM311 ComparatorMuhammad JunaidNo ratings yet

- Nithinnath 2017Document5 pagesNithinnath 2017يوسف إبراهيمNo ratings yet

- 2.Dpps Module IIDocument93 pages2.Dpps Module IIAshley SureshNo ratings yet

- Selective Harmonic Elimination by Programmable Pulse Width Modulation in InvertersDocument6 pagesSelective Harmonic Elimination by Programmable Pulse Width Modulation in InvertersseventhsensegroupNo ratings yet

- An 95003Document2 pagesAn 95003ClenaNo ratings yet

- Practical Feedback Loop Design Considerations For Switched Mode Power SuppliesDocument14 pagesPractical Feedback Loop Design Considerations For Switched Mode Power SuppliesDiego PhillipeNo ratings yet

- Instrument Transformers For Relaying: W. A. ElmoreDocument13 pagesInstrument Transformers For Relaying: W. A. ElmoreAbhishek RajputNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Building Knowledge For Substation-Based Decision Support Using Rough SetsDocument8 pagesBuilding Knowledge For Substation-Based Decision Support Using Rough Setsquisi123No ratings yet

- 6018 ThreePhaseCircuit Web PDFDocument18 pages6018 ThreePhaseCircuit Web PDFquisi123No ratings yet

- US5367426-Zona de CargaDocument10 pagesUS5367426-Zona de Cargaquisi123No ratings yet

- 6763 TestingLine FC 20160602 WebDocument9 pages6763 TestingLine FC 20160602 Webquisi123No ratings yet

- Knowledge-Based Approach Using Support Vector Machine For Transmission Line Distance Relay Co-OrdinationDocument10 pagesKnowledge-Based Approach Using Support Vector Machine For Transmission Line Distance Relay Co-Ordinationquisi123No ratings yet

- Automated Testing Of Busbar Protection Using System ModelingDocument6 pagesAutomated Testing Of Busbar Protection Using System Modelinggulatimanish1985No ratings yet

- Epso - Meta-Heuristic: Best-Of-Two-Worlds TO Power System ProblemsDocument6 pagesEpso - Meta-Heuristic: Best-Of-Two-Worlds TO Power System Problemsquisi123No ratings yet

- Rough Set Based Data Mining Strategy For Analyzing Distance Protective Relay OperationsDocument7 pagesRough Set Based Data Mining Strategy For Analyzing Distance Protective Relay Operationsquisi123No ratings yet

- Simulation of Mho relay using power system analysis outputsDocument19 pagesSimulation of Mho relay using power system analysis outputsquisi123No ratings yet

- Smart Transmission Grid: Vision and Framework: Abstract-A Modern Power Grid Needs To Become Smarter inDocument10 pagesSmart Transmission Grid: Vision and Framework: Abstract-A Modern Power Grid Needs To Become Smarter inAsraButoolNo ratings yet

- Relay-Performance - Estados Del SEPDocument3 pagesRelay-Performance - Estados Del SEPquisi123No ratings yet

- Network Protection & Automation Guide - NPAG 2011 AlstomDocument508 pagesNetwork Protection & Automation Guide - NPAG 2011 Alstomhenry100% (1)

- Discussion of Relay Protection Testing Technology For Intelligent SubstationDocument6 pagesDiscussion of Relay Protection Testing Technology For Intelligent Substationquisi123No ratings yet

- Comparative Study of CT Modeling Under Transient ConditionsDocument7 pagesComparative Study of CT Modeling Under Transient Conditionsquisi123100% (1)

- Protection and Testing Considerations For IEC 61850 Sampled Values-Based Distance and Line Current Differential SchemesDocument11 pagesProtection and Testing Considerations For IEC 61850 Sampled Values-Based Distance and Line Current Differential Schemesquisi123No ratings yet

- 13IPST068 Fabian PerezDocument7 pages13IPST068 Fabian Perezquisi123No ratings yet

- Case Study Campus 61850Document10 pagesCase Study Campus 61850quisi123No ratings yet

- 3D-360 Degree Antenna Plot Accepting Phased Verticals V2aDocument39 pages3D-360 Degree Antenna Plot Accepting Phased Verticals V2aquisi123No ratings yet

- UC XLPE CatalogueDocument63 pagesUC XLPE CatalogueZafar BakhshNo ratings yet

- Metal-Oxide Surge Arresters in High-Voltage Transmission and Distribution SystemsDocument6 pagesMetal-Oxide Surge Arresters in High-Voltage Transmission and Distribution SystemsBhargavi PadalaNo ratings yet

- CarsonDocument16 pagesCarsonmmilos1No ratings yet

- The Definition and Unit of Ionic StrengthDocument2 pagesThe Definition and Unit of Ionic StrengthDiego ZapataNo ratings yet

- Skills Test Unit 1 Test A EmailDocument4 pagesSkills Test Unit 1 Test A EmailЛиза ОмельченкоNo ratings yet

- Organization Structure in SAP Plant Maintenance: CommentsDocument3 pagesOrganization Structure in SAP Plant Maintenance: CommentsMarco Antônio Claret TeixeiraNo ratings yet

- Kim Hoff PAR 117 JDF 1115 Separation AgreementDocument9 pagesKim Hoff PAR 117 JDF 1115 Separation AgreementlegalparaeagleNo ratings yet

- Maximizing ROI Through RetentionDocument23 pagesMaximizing ROI Through RetentionSorted CentralNo ratings yet

- IN SUNNY SPAIN, 1882-85: "My Country, My Love, My People, I Leave You Now, You Disappear, I Lose Sight of You"Document4 pagesIN SUNNY SPAIN, 1882-85: "My Country, My Love, My People, I Leave You Now, You Disappear, I Lose Sight of You"Mary Claire ComalaNo ratings yet

- Spreadsheet and Presentation Skills SyllabusDocument4 pagesSpreadsheet and Presentation Skills SyllabusGbox CTCNo ratings yet

- Obessive Compulsive Disorder (OCD)Document10 pagesObessive Compulsive Disorder (OCD)marketingmoneyindiaNo ratings yet

- Briefing Ai Trading BotDocument10 pagesBriefing Ai Trading BotMeaningful LifeNo ratings yet

- Are The Risk Management Tools at Your Law Firm Working?Document17 pagesAre The Risk Management Tools at Your Law Firm Working?vantoffNo ratings yet

- Charles Henry Brendt (1862-1929)Document2 pagesCharles Henry Brendt (1862-1929)Everything newNo ratings yet

- ACCT250-Auditing Course OutlineDocument7 pagesACCT250-Auditing Course OutlineammadNo ratings yet

- CV HannahDocument3 pagesCV HannahRoxan DosdosNo ratings yet

- 6 Fsiqiatria-1524041346Document48 pages6 Fsiqiatria-1524041346მირანდა გიორგაშვილიNo ratings yet

- Sustainable Farming FPO Promotes Natural AgricultureDocument4 pagesSustainable Farming FPO Promotes Natural AgricultureSHEKHAR SUMITNo ratings yet

- KluberDocument20 pagesKluberJako MishyNo ratings yet

- Dell in India Targeting SMB Markets - The Differentiation Strategy PDFDocument16 pagesDell in India Targeting SMB Markets - The Differentiation Strategy PDFJatinNo ratings yet

- Zambia Budget 2010Document26 pagesZambia Budget 2010Chola Mukanga100% (3)

- PT JayatamaDocument67 pagesPT JayatamaAminadap. SIL.TNo ratings yet

- Emotion-WPS OfficeDocument2 pagesEmotion-WPS OfficemikaNo ratings yet

- Lesson 5 Classifications of CommunicationDocument48 pagesLesson 5 Classifications of CommunicationRovenick SinggaNo ratings yet

- School RulesDocument2 pagesSchool RulesAI HUEYNo ratings yet

- How to Launder Money in Real EstateDocument58 pagesHow to Launder Money in Real EstateSpeedyGonsalesNo ratings yet

- Literature 1 Study GuideDocument7 pagesLiterature 1 Study GuideEs EsNo ratings yet

- l3 Immunization & Cold ChainDocument53 pagesl3 Immunization & Cold ChainNur AinaaNo ratings yet

- Harsheen Kaur BhasinDocument20 pagesHarsheen Kaur Bhasincalvin kleinNo ratings yet

- Moldavian DressDocument16 pagesMoldavian DressAnastasia GavrilitaNo ratings yet

- Quality Management in Apparel Industry PDFDocument9 pagesQuality Management in Apparel Industry PDFJyoti Rawal0% (1)