Professional Documents

Culture Documents

MCU - PIC24FV32KA304 - MICROCHIP - Programming Specifications PDF

MCU - PIC24FV32KA304 - MICROCHIP - Programming Specifications PDF

Uploaded by

Lodewyk KleynhansOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MCU - PIC24FV32KA304 - MICROCHIP - Programming Specifications PDF

MCU - PIC24FV32KA304 - MICROCHIP - Programming Specifications PDF

Uploaded by

Lodewyk KleynhansCopyright:

Available Formats

PIC24FXXKA1XX/FVXXKA3XX

PIC24FXXKA1XX/FVXXKA3XX Flash Programming

Specifications

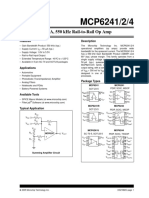

1.0 DEVICE OVERVIEW The Enhanced ICSP method is a faster method, which

takes advantage of the programming executive, as

This document defines the programming specifications illustrated in Figure 2-1. The programming executive

for the PIC24FXXKA1XX/FVXXKA3XX family of 16-bit provides the necessary functionality to erase, program

microcontroller devices. This is required only for and verify the device through a command set. The

developing programming support for the command set allows the programmer to program the

PIC24FXXKA1XX/FVXXKA3XX family. Users of any PIC24FXXKA1XX/FVXXKA3XX devices without having

one of these devices should use the development tools to deal with the low-level programming protocols of the

that are already supporting the device programming. device. Section 4.0 “Device Programming –

The programming specifications are specific to the Enhanced ICSP” describes the ICSP method using the

following devices: programming executive.

• PIC24F08KA101 • PIC24FV32KA301(1)

FIGURE 2-1: PROGRAMMING SYSTEM

• PIC24F16KA101 • PIC24FV16KA302(1) OVERVIEW FOR ENHANCED

• PIC24F08KA102 • PIC24FV32KA302(1) ICSP™ METHOD

• PIC24F16KA102 • PIC24FV16KA304(1) PIC24FXXKAXXX

• PIC24FV16KA301(1) • PIC24FV32KA304(1)

Programming

Note 1: Includes corresponding PIC24FXXKA30X Programmer

Executive

devices.

2.0 PROGRAMMING OVERVIEW

OF THE On-Chip Memory

PIC24FXXKA1XX/FVXXKA3XX

FAMILY

This section describes the two methods 2.1 Power Requirements

of programming the PIC24FXXKA1XX/FVXXKA3XX

family of devices: Devices in the PIC24FXXKA1XX and

PIC24FXXKA3XX families are 3.3V supply designs.

• In-Circuit Serial Programming™ (ICSP™) The core, the peripherals and the I/O pins operate at

• Enhanced In-Circuit Serial Programming 3.3V. The device can operate from 1.8V to 3.6V.

(Enhanced ICSP)

Devices in the PIC24FVXXKA3XX families are 5.0V

The ICSP programming method is the most direct supply designs. The core, the peripherals and the I/O

method for programming the device. However, it is also pins operate at 3.3V. The device can operate from 2.0V

the slower of the two methods. It provides a native, to 5.5V; an internal regulator operates the core logic at

low-level programming capability to erase, program, and 3.25V.

verify the device. Section 3.0 “Device Programming –

Table 2-1 provides the pins that are required for

ICSP” describes the ICSP method.

programming, which are indicated in Figure 2-3. Refer

to the appropriate device data sheet for complete pin

descriptions. Note that all power supply and ground

pins must be connected appropriately for

programming.

2011 Microchip Technology Inc. Advance Information DS39919B-page 1

PIC24FXXKA1XX/FVXXKA3XX

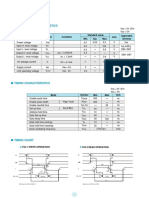

TABLE 2-1: PIN DESCRIPTIONS (DURING PROGRAMMING)

During Programming

Pin Name

Pin Name Pin Type Pin Description

MCLR/VPP MCLR/VPP P Programming Enable

VDD VDD P Power Supply

VSS VSS P Ground

VCAP VCAP P Stabilizing Capacitor for Voltage Regulator(1)

PGECx PGC I Programming Pin Pair: Serial Clock

PGEDx PGD I/O Programming Pin Pair: Serial Data

Legend: I = Input, O = Output, P = Power

Note 1: PIC24FVXXKA3XX devices only.

2.1.1 ON-CHIP VOLTAGE REGULATOR FIGURE 2-2: CONNECTIONS FOR THE

CONNECTIONS ON-CHIP REGULATOR

For PIC24FVXXKA3XX devices, an on-chip regulator

provides power to the core from the other VDD pins. A low

ESR capacitor (such as high-quality ceramic or tantalum) 5.0V

must be connected to the VDDCORE pin (Figure 2-2). This PIC24FVXXKA3XX

helps to maintain the stability of the regulator. The speci- VDD

fications for core voltage and capacitance are listed in

Section 7.0 “AC/DC Characteristics and Timing VCAP

Requirements”.

CEFC

PIC24FXXKA1XX and PIC24FXXKA3XX devices do not (10 F typ) VSS

use an on-chip regulator.

Note 1: These are typical operating voltages. Refer

to Section 7.0 “AC/DC Characteristics and

Timing Requirements” for the full operating

ranges of VDD and VDDCORE.

DS39919B-page 2 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

FIGURE 2-3: PIN DIAGRAMS

20-Pin SPDIP, SOIC 28-Pin PDIP, SOIC

MCLR/VPP 1 20 VDD MCLR/VPP 1 28 VDD

PGEC2 2 19 VSS 2 27 VSS

PIC24F(V)XXKAX01

PGED2 3 18 3 26

PIC24F(V)XXKAX02

PGED1 4 17 PGED1 4 25

PGEC1 5 16 PGEC1 5 24

6 15 6 23

7 14 VCAP(1) 7 22 PGEC2

8 13 VSS 8 21 PGED2

PGED3 9 12 9 20 VCAP(1)

PGEC3 10 11 10 19

11 18

12 17

VDD 13 16

PGED3 14 15 PGEC3

28-Pin QFN 44-Pin QFN

PGED3

PGEC3

MCLR/VPP

VDD

VSS

44

43

42

41

40

39

38

37

36

35

34

VDD

Vss

1 33

2 32

28 27 26 25 24 23 22 31

3

PGED1 1 21 4 30

PGEC1 2 20 5 29 VSS

3 19 PGEC2 6 PIC24F(V)XXKA304 28 VDD

4 PIC24F(V)XXKAX02 18 PGED2 VCAP(1) 7 27

VSS 5 17 VCAP(1) PGED2 8 26

6 16 PGEC2 9 25

7 15 10 24

8 9 10 11 12 13 14 11 23

12

13

14

15

VSS 16

VDD 17

MCLR/VPP 18

19

20

PGED1 21

PGEC1 22

PGED3

PGEC3

VDD

Note 1: PIC24FVXXKA3XX devices only. PIC24FXXKA3XX devices do not use VCAP.

2011 Microchip Technology Inc. Advance Information DS39919B-page 3

PIC24FXXKA1XX/FVXXKA3XX

2.2 Memory Map Table 2-2 provides the program memory and data

EEPROM size, and the number of memory rows

The program memory map for present in each device variant.

PIC24FXXKA1XX/FVXXKA3XX devices extends from

000000h to FFFFFEh. Code storage is located at the The erase operation can be done on one word, half of

base of the memory map and supports up to 11K a row or one row at a time. The program operation can

instruction words (about 32 Kbytes). be done only one word at a time.

Additionally, PIC24FXXKA1XX/FVXXKA3XX family

devices have an on-chip data EEPROM. This data

EEPROM is mapped to the program memory area from

location 7FFE00h to 7FFFFEh.

TABLE 2-2: MEMORY SIZES FOR PIC24FXXKA1XX/FVXXKA3XX DEVICES

Program Memory

Data EEPROM Size

Device Upper Address Rows Rows

(Words)

(Instruction Words)

PIC24F08KA10X 15FEh (2.75K) 88 256 32

PIC24F16KA10X 2BFEh (5.5K) 176 256 32

PIC24FV08KA30X(1) 15FEh (2.75K) 88 256 32

(1)

PIC24FV16KA30X 2BFEh (5.5K) 176 256 32

PIC24FV32KA30X(1) 57FEh (11K) 352 256 32

Note 1: Includes corresponding PIC24FXXKA3XX devices.

Locations 800000h through 8007FEh are reserved for TABLE 2-3: CONFIGURATION REGISTER

executive code memory. This region stores the LOCATIONS

programming executive, the debugging executive and

the Diagnostic Words. The programming executive is Configuration Register Address

used for device programming and the debug executive FBS F80000

is used for in-circuit debugging. This region of memory

FGS F80004

cannot be used to store user code.

FOSCSEL F80006

The device Configuration registers are implemented

from location F80000h to F80010h, and can be erased FOSC F80008

or programmed one register at a time. Table 2-3 FWDT F8000A

provides the implemented Configuration registers and FPOR F8000C

their locations.

FICD F8000E

Locations, FF0000h and FF0002h, are reserved for the FDS F80010

Device ID registers. These bits can be used by the

programmer to identify the device type that is being

programmed. See Section 6.0 “Device ID” for more

information. The Device ID registers read out normally

even after code protection is applied.

Figure 2-4 depicts the memory map for the

PIC24FXXKA1XX/FVXXKA3XX family variants.

DS39919B-page 4 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

FIGURE 2-4: PROGRAM MEMORY MAP

000000h

User Flash

Code Memory

(5632 x 24-bit)

0015FEh/002BFEh/0057FEh (1)

User Memory

Space

Reserved

7FFE00h

Data EEPROM

800000h

Programming Executive

Code Memory

(1016 x 24-bit) 8007F2h

8007F4h

Diagnostic Words

8007FEh

800800h

Configuration Memory

Space

Reserved

F80000h

Configuration Registers

F80010h

FEFFFEh

Device ID FF0000h

(2 x 16-bit) FF0002h

Reserved FF0004h

FFFFFEh

Note 1: The upper address boundaries for user program memory are device-specific. See Table 2-2 for details.

2011 Microchip Technology Inc. Advance Information DS39919B-page 5

PIC24FXXKA1XX/FVXXKA3XX

3.0 DEVICE PROGRAMMING – FIGURE 3-1: HIGH–LEVEL ICSP™

ICSP PROGRAMMING FLOW

The ICSP method is a special programming protocol Start

that allows reading and writing to the

PIC24FXXKA1XX/FVXXKA3XX device family memory.

Enter ICSP™ Mode

ICSP is the most direct method used to program a

device; however, Enhanced ICSP is faster. The ICSP

mode also reads the contents of the executive memory

Perform Bulk

to determine if the programming executive is present. Erase

This is accomplished by applying control codes and

instructions, serially to the device, using PGCx and

PGDx pins. Program Memory

In ICSP mode, the system clock is taken from the

PGCx pin regardless of the device‘s oscillator

Configuration bits. All of the instructions are shifted Verify Program

serially to an internal buffer, loaded into the Instruction

Register (IR), and then executed. No program is

Program Data EEPROM Memory

fetched from the internal memory. Instructions are fed

in 24 bits at a time. PGDx is used to shift data in, and

PGCx is used as both the serial shift clock and the CPU

Verify Data EEPROM Memory

execution clock.

Note: During ICSP operation, the operating

frequency of PGCx should not exceed Program Configuration Bits

8 MHz.

3.1 Overview of the Programming Verify Configuration Bits

Process

Figure 3-1 illustrates the high-level overview of the Exit ICSP Mode

programming process.

After entering the ICSP mode, perform the following: End

1. Bulk Erase the device.

2. Program and verify the code memory.

3. Program and verify the data EEPROM memory. TABLE 3-1: CPU CONTROL CODES IN

4. Program and verify the device configuration. ICSP™ MODE

5. Program the code-protect Configuration bits, if 4-Bit

required. Mnemonic Description

Control Code

0000b SIX Shift in 24-bit instruction

3.2 ICSP Operation and execute.

Upon entry into ICSP mode, the CPU is Idle. An 0001b REGOUT Shift out the VISI

internal state machine governs the execution of the (0784h) register.

CPU. A 4-bit control code is clocked in, using PGCx 0010b-1111b N/A This is reserved.

and PGDx, and this control code is used to command

the CPU (see Table 3-1).

The SIX control code is used to send instructions to the

CPU for execution, and the REGOUT control code is

used to read data out of the device via the VISI register.

DS39919B-page 6 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

3.2.1 SIX SERIAL INSTRUCTION For example, MOV #0x0,W0 followed by MOV

EXECUTION [W0],W1 must have a NOP inserted in between.

The SIX control code allows execution of If a two-cycle instruction modifies a register, which

PIC24FXXKA1XX/FVXXKA3XX family assembly is used indirectly, it requires two following NOPs;

instructions. When the SIX code is received, the CPU is one to execute the second half of the instruction

suspended for 24 clock cycles as the instruction is then and the other to stall the CPU to correct the

clocked into the internal buffer. Once the instruction is pipeline.

shifted in, the state machine allows it to be executed For example, TBLWTL [W0++],[W1] should be

over the next four PGC clock cycles. While the received followed by 2 NOPs.

instruction is executed, the state machine simultane-

• The device Program Counter (PC) continues to

ously shifts in the next 4-bit command (see Figure 3-2).

automatically increment during the ICSP

Coming out of Reset, the first 4-bit control code is instruction execution, even though the Flash

always forced to SIX, and a forced NOP instruction is memory is not being used. As a result, it is

executed by the CPU. Five additional PGCx clocks are possible for the PC to be incremented so that it

needed on start-up; thereby resulting in a 9-bit SIX points to invalid memory locations.

command, instead of the normal 4-bit SIX command.

Examples of invalid memory spaces are

After the forced SIX is clocked in, the ICSP operation unimplemented Flash addresses or the vector

resumes to normal. That is, the next 24 clock cycles space (location 0x0 to 0x1FF).

load the first instruction word to the CPU.

If the PC ever points to these locations, it causes

Note: To account for this forced NOP, all example the device to reset, possibly interrupting the ICSP

codes in this specification begin with a operation. To prevent this, instructions should be

NOP to ensure that no data is lost. periodically executed to reset the PC to a safe

space. The optimal method of achieving this is to

3.2.1.1 Differences Between SIX Instruction perform a “GOTO 0x200”.

Execution and Normal Instruction

Execution 3.2.2 REGOUT SERIAL INSTRUCTION

EXECUTION

There are some differences between executing

instructions using the SIX ICSP command and normal The REGOUT control code allows for the data to be

device instruction execution. As a result, the code extracted from the device in the ICSP mode. It is used

examples in this specification might not match those to clock the contents of the VISI register out of the

required to perform the same operations during normal device over the PGDx pin. After the REGOUT control

device operation. code is received, the CPU is held Idle for 8 cycles. After

this, an additional 16 cycles are required to clock the

The differences are: data out (see Figure 3-3).

• Two-word instructions require 2 SIX operations to The REGOUT code is unique, as the PGDx pin is an

clock in all the necessary data. input when the control code is transmitted to the

Examples of two-word instructions are GOTO and device. However, after the control code is processed,

CALL. the PGDx pin becomes an output as the VISI register is

• Two-cycle instructions require 2 SIX operations to shifted out.

complete. The first SIX operation shifts in the Note 1: After the contents of VISI are shifted out,

instruction and begins to execute it. A second SIX the PIC24FXXKA1XX/FVXXKA3XX

operation, which should shift in a NOP to avoid devices maintain PGDx as an output until

losing data, allows the CPU clocks required to the first rising edge of the next clock is

finish executing the instruction. received.

Examples of two-cycle instructions are table read 2: Data changes on the falling edge and

and table write instructions. latches on the rising edge of PGCx. For

• The CPU does not automatically stall to account all data transmissions, the Least

for pipeline changes. A CPU stall occurs when an Significant bit (LSb) is transmitted first.

instruction modifies a register, which is used by

the instruction immediately following the CPU stall

for Indirect Addressing. During normal operation,

the CPU forces a NOP while the new data is read.

To account for this, while using ICSP, any indirect

references to a recently modified register should

be proceeded with a NOP.

2011 Microchip Technology Inc. Advance Information DS39919B-page 7

PIC24FXXKA1XX/FVXXKA3XX

FIGURE 3-2: SIX SERIAL EXECUTION

P1

1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 8 17 18 19 20 21 22 23 24 1 2 3 4

PGCx

P4 P4A

P3 P1A

P1B

P2

LSB X X X X X X X X X X X X X X MSB

PGDx 0 0 0 0 0 0 0 0 0 0 0 0 0

Execute PC – 1, 24-Bit Instruction Fetch Execute 24-Bit

Fetch SIX Instruction, Fetch

Control Code Only for

Program Next Control Code

Memory Entry

PGDx = Input

FIGURE 3-3: REGOUT SERIAL EXECUTION

1 2 3 4 1 2 7 8 1 2 3 4 5 6 11 12 13 14 15 16 1 2 3 4

PGCx

P4 P4A

P5

PGDx 1 0 0 0 LSb 1 2 3 4 ... 10 11 12 13 14 MSb 0 0 0 0

Execute Previous Instruction, CPU Held in Idle Shift Out VISI Register<15:0> No Execution Takes Place,

Fetch REGOUT Control Code Fetch Next Control Code

PGDx = Input PGDx = Output PGDx = Input

DS39919B-page 8 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

3.3 Entering ICSP Mode 3.3.2 HIGH-VOLTAGE ICSP ENTRY

Entering the ICSP Program/Verify mode, using the VPP

3.3.1 LOW-VOLTAGE ICSP ENTRY pin, is the same as entering the mode using MCLR.

As illustrated in Figure 3-4, the following processes are The only difference is the programming voltage applied

involved in entering ICSP Program/Verify mode using to VPP is VIHH, and before presenting the key sequence

MCLR: on PGDx, an interval of at least P18 should elapse (see

1. MCLR is briefly driven high, then low. Figure 3-5).

2. A 32-bit key sequence is clocked into PGDx. Once the key sequence is complete, an interval of at

3. MCLR is then driven high within a specified least P7 should elapse, and the voltage should remain

period of time and held. at VIHH. The voltage, VIHH, must be held at that level for

as long as the Program/Verify mode is to be main-

The programming voltage VIH IS applied to MCLR; this tained. An interval of at least P7 must elapse before

is VDD in the case of PIC24FXXKA1XX/FVXXKA3XX presenting the data on PGDx.

devices. There is no minimum time requirement for

holding at VIH. After VIH is removed, an interval of at Signals appearing on PGDx before P7 has elapsed will

least P18 must elapse before presenting the key not be interpreted as valid.

sequence on PGDx. Upon a successful entry, the program memory can be

The key sequence is a specific 32-bit pattern: accessed and programmed in serial fashion. While in

‘0100 1101 0100 0011 0100 1000 0101 ICSP mode, all unused I/Os are placed in a

0001‘ (more easily remembered as 4D434851h in high-impedance state.

hexadecimal). The device will enter Program/Verify

3.3.3 CODE-PROTECT ICSP ENTRY

mode only if the sequence is valid. The Most Significant

bit (MSb) of the most significant nibble must be shifted in When code protection is employed on the

first. PIC24FXXKA3XX devices (BWRP, GSS0 or

GWRP = 0), then the voltage on VDD must be above

Once the key sequence is complete, VIH must be

VBULK in order to erase, and then program the device.

applied to MCLR and held at that level for as long as the

Care must be taken in the design and layout of a board

Program/Verify mode is to be maintained. An interval of

so that any parts connected to VDD can withstand what

at least P19 and P7 must elapse before presenting data

may be an increase in voltage if the device is running

on PGDx. Signals appearing on PGCx before P7 has

below VBULK.

elapsed would not be interpreted as valid.

FIGURE 3-4: ENTERING ICSP™ MODE USING LOW-VOLTAGE ENTRY

P6

P14 P19 P7

VIH VIH

MCLR

VDD

Program/Verify Entry Code = 4D434851h

PGDx 0 1 0 0 1 ... 0 0 0 1

b31 b30 b29 b28 b27 b3 b2 b1 b0

PGCx

P18 P1A

P1B

FIGURE 3-5: ENTERING ICSP™ MODE USING HIGH-VOLTAGE ENTRY

P7

P6 VIHH

VPP VIH

VDD

Program/Verify Entry Code = 4D434851h

PGDx 0 1 0 0 1 ... 0 0 0 1

b31 b30 b29 b28 b27 b3 b2 b1 b0

PGCx

P18 P1A

P1B

2011 Microchip Technology Inc. Advance Information DS39919B-page 9

PIC24FXXKA1XX/FVXXKA3XX

3.4 Flash Memory Programming in TABLE 3-2: NVMCON VALUES FOR

ICSP Mode ERASE OPERATIONS

3.4.1 PROGRAMMING OPERATIONS NVMCON

Erase Operation

Value

The NVMCON register controls the Flash memory write

and erase operations. To program the device, set the 4064h Erase the code memory and

NVMCON register to select the type of erase operation Configuration registers (does not erase

(see Table 3-2) or write operation (see Table 3-3). Set programming executive code and

the WR control bit (NVMCON<15>) to initiate the Device ID registers).

program. 404Ch Erase the general segment and

In ICSP mode, all programming operations are Configuration bits associated with it.

self-timed. There is an internal delay between setting 4068h Erase the boot segment and

and automatic clearing of the WR control bit when the Configuration bits associated with it.

programming operation is complete. Refer to 405Ah(1) Erase four rows of code memory.

Section 7.0 “AC/DC Characteristics and Timing

Requirements” for information on the delays 4059h(1) Erase two rows of code memory.

associated with various programming operations. 4058h(1) Erase a row of code memory.

4050h Erase the entire data EEPROM

3.4.2 STARTING AND STOPPING A memory and Configuration bits

PROGRAMMING CYCLE associated with it.

The WR bit (NVMCON<15>) is used to start an erase 405Ah(1) Erase eight words of data EEPROM

or write cycle. Initiate the programming cycle by setting memory.

the WR bit. 4059h(1) Erase four words of data EEPROM

All erase and write cycles are self-timed. The WR bit memory.

should be polled to determine if the erase or write cycle 4058h(1) Erase one word of data EEPROM

is complete. Start a programming cycle as follows: memory.

BSET NVMCON, #WR 4054h Erase all the Configuration registers

(except the code-protect fuses).

4058h(1) Erase Configuration registers except

FBS and FGS.

Note 1: The destination address decides the

region (code memory, data EEPROM

memory or Configuration register) of the

erased rows/words.

TABLE 3-3: NVMCON VALUES FOR

WRITE OPERATIONS

NVMCON

Write Operation

Value

4004h(1) Write one Configuration register.

4004h(1) Program one row (32 instruction words)

of code memory or executive memory.

4004h(1) Program one word of data EEPROM

memory.

Note 1: The destination address decides the

region (code memory, data EEPROM

memory or Configuration register) of the

erased rows/words.

DS39919B-page 10 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

3.5 Erasing Program Memory FIGURE 3-6: BULK ERASE FLOW

To erase the program memory (all of code memory, Start

data memory and Configuration bits, including the

code-protect bits), set the NVMCON to 4064h and then

execute the programming cycle. Write 4064h to NVMCON SFR

Figure 3-6 illustrates the ICSP programming process

for Bulk Erase. This process includes the ICSP

Set the WR bit to Initiate Erase

command code, which must be transmitted (for each

instruction), LSB first, using the PGCx and PGDx pins

(see Figure 3-2).

Delay P11 + P10 Time

Table 3-4 provides the steps for executing serial

instruction for the Bulk Erase mode.

Note: Program memory must be erased before End

writing any data to program memory.

TABLE 3-4: SERIAL INSTRUCTION EXECUTION FOR CHIP ERASE

Command Data

Description

(Binary) (Hex)

Step 1: Exit the Reset vector.

0000 000000 NOP

0000 040200 GOTO 0x200

0000 000000 NOP

Step 2: Set the NVMCON to erase the entire program memory.

0000 24064A MOV #0x4064, W10

0000 883B0A MOV W10, NVMCON

Step 3: Set the TBLPAG and perform dummy table write to select the erased memory.

0000 200000 MOV #<PAGEVAL>, W0

0000 880190 MOV W0, TBLPAG

0000 200000 MOV #0x0000, W0

0000 BB0800 TBLWTL W0, [W0]

0000 000000 NOP

0000 000000 NOP

Step 4: Initiate the erase cycle.

0000 A8E761 BSET NVMCON, #WR

0000 000000 NOP

0000 000000 NOP

Step 5: Repeat this step to poll the WR bit (bit 15 of NVMCON) until it is cleared by the hardware.

0000 000000 NOP

0000 040200 GOTO 0x200

0000 000000 NOP

0000 803B02 MOV NVMCON, W2

0000 883C22 MOV W2, VISI

0000 000000 NOP

0001 <VISI> Clock out the contents of the VISI register.

0000 000000 NOP

2011 Microchip Technology Inc. Advance Information DS39919B-page 11

PIC24FXXKA1XX/FVXXKA3XX

3.6 Writing Code Memory After the write latches are loaded, initiate programming

by writing to the NVMCON register in Steps 7 and 8. In

The procedure for writing code memory is the same as Step 9, the internal PC is reset to 200h. This is a

writing the Configuration registers. The difference is precautionary measure to prevent the PC from

that the 32 instruction words are programmed one at a incrementing to unimplemented memory when large

time. To facilitate this operation, working registers, devices are being programmed. Finally, in Step 10,

W0:W5, are used as temporary holding registers for the repeat Steps 3 through 9 until all of the code memory is

data to be programmed. Figure 3-8 illustrates the code programmed.

memory writing flow.

Table 3-5 provides the ICSP programming details, FIGURE 3-7: PACKED INSTRUCTION

including the serial pattern with the ICSP command WORDS IN W0:W5

code, which must be transmitted LSB first, using the

PGCx and PGDx pins (see Figure 3-2).

15 8 7 0

In Step 1 of Table 3-5, the Reset vector is exited; in

W0 LSW0

Step 2, the NVMCON register is initialized for

programming a full row of code memory, and in Step 3, W1 MSB1 MSB0

the 24-bit starting destination address for programming W2 LSW1

is loaded into the TBLPAG register and W7 register. W3 LSW2

The upper byte of the starting destination address is

W4 MSB3 MSB2

stored in TBLPAG and the lower 16 bits of the

destination address are stored in W7. W5 LSW3

To minimize the programming time, a packed

instruction format is used (see Figure 3-7).

In Step 4 of Table 3-5, four packed instruction words

are stored in working registers, W0:W5, using the MOV

instruction. The Read Pointer, W6, is initialized.

Figure 3-7 illustrates the contents of W0:W5 holding

the packed instruction word data. In Step 5, eight

TBLWT instructions are used to copy the data from

W0:W5 to the write latches of the code memory. Since

code memory is programmed 32 instruction words at a

time, Steps 3 to 5 are repeated eight times to load all

the write latches (see Step 6).

TABLE 3-5: SERIAL INSTRUCTION EXECUTION FOR WRITING CODE MEMORY

Command Data

Description

(Binary) (Hex)

Step 1: Exit the Reset vector.

0000 000000 NOP

0000 040200 GOTO 0x200

0000 000000 NOP

Step 2: Set the NVMCON to program 32 instruction words.

0000 24004A MOV #0x4004, W10

0000 883B0A MOV W10, NVMCON

Step 3: Initialize the Write Pointer (W7) for TBLWT instruction.

0000 200xx0 MOV #<DestinationAddress23:16>, W0

0000 880190 MOV W0, TBLPAG

0000 2xxxx7 MOV #<DestinationAddress15:0>, W7

Step 4: Load W0:W5 with the next 4 instruction words to program.

0000 2xxxx0 MOV #<LSW0>, W0

0000 2xxxx1 MOV #<MSB1:MSB0>, W1

0000 2xxxx2 MOV #<LSW1>, W2

0000 2xxxx3 MOV #<LSW2>, W3

0000 2xxxx4 MOV #<MSB3:MSB2>, W4

0000 2xxxx5 MOV #<LSW3>, W5

DS39919B-page 12 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

TABLE 3-5: SERIAL INSTRUCTION EXECUTION FOR WRITING CODE MEMORY (CONTINUED)

Command Data

Description

(Binary) (Hex)

Step 5: Set the Read Pointer (W6) and load the (next set of) write latches.

0000 EB0300 CLR W6

0000 000000 NOP

0000 BB0BB6 TBLWTL [W6++], [W7]

0000 000000 NOP

0000 000000 NOP

0000 BBDBB6 TBLWTH.B [W6++], [W7++]

0000 000000 NOP

0000 000000 NOP

0000 BBEBB6 TBLWTH.B [W6++], [++W7]

0000 000000 NOP

0000 000000 NOP

0000 BB1BB6 TBLWTL [W6++], [W7++]

0000 000000 NOP

0000 000000 NOP

0000 BB0BB6 TBLWTL [W6++], [W7]

0000 000000 NOP

0000 000000 NOP

0000 BBDBB6 TBLWTH.B [W6++], [W7++]

0000 000000 NOP

0000 000000 NOP

0000 BBEBB6 TBLWTH.B [W6++], [++W7]

0000 000000 NOP

0000 000000 NOP

0000 BB1BB6 TBLWTL [W6++], [W7++]

0000 000000 NOP

0000 000000 NOP

Step 6: Repeat Steps 3 though 5, eight times to load the write latches for 32 instructions.

Step 7: Initiate the write cycle.

0000 A8E761 BSET NVMCON, #WR

0000 000000 NOP

0000 000000 NOP

Step 8: Repeat this step to poll the WR bit (bit 15 of NVMCON) until it is cleared by the hardware.

0000 040200 GOTO 0x200

0000 000000 NOP

0000 803B02 MOV NVMCON, W2

0000 883C22 MOV W2, VISI

0000 000000 NOP

0001 <VISI> Clock out contents of the VISI register.

0000 000000 NOP

Step 9: Reset device internal PC.

0000 040200 GOTO 0x200

0000 000000 NOP

Step 10: Repeat Steps 3 through 9 until the entire code memory is programmed.

2011 Microchip Technology Inc. Advance Information DS39919B-page 13

PIC24FXXKA1XX/FVXXKA3XX

FIGURE 3-8: PROGRAM CODE MEMORY FLOW

Start

N=1

LoopCount = 0

Configure

Device for

Writes

Load 2 Bytes

N=N+1 to Write

Buffer at <Addr>

All

No bytes

written?

N=1 Yes

LoopCount = Start Write Sequence

LoopCount + 1 and Poll for WR bit

to be Cleared

No All

locations

done?

Yes

End

DS39919B-page 14 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

3.7 Writing Data EEPROM Table 3-6 provides the ICSP programming details for

writing data EEPROM.

Figure 3-9 illustrates the flow of programming the data

EEPROM memory. The procedure is the same as Note: When writing to EEPROM, always set the

writing code memory. The only difference is that only TBLPAG register to 7Fh. This is the upper

one word is programmed in each operation. When byte address of all locations of data

writing data EEPROM, one word is programmed during EEPROM.

each operation. Working register, W0, is used as a

temporary holding register for the data to be

programmed.

TABLE 3-6: INSTRUCTION EXECUTION FOR WRITING DATA EEPROM

Command Data

(Hex) Description

(Binary)

Step 1: Exit the Reset vector.

0000 000000 NOP

0000 040200 GOTO 0x200

0000 000000 NOP

Step 2: Set the NVMCON to program 1 data word.

0000 24004A MOV #0x4004, W10

0000 883B0A MOV W10, NVMCON

Step 3: Initialize the Write Pointer (W7) for TBLWT instruction.

0000 2007F0 MOV #0x7F, W0

0000 880190 MOV W0, TBLPAG

0000 2FExx7 MOV #<DestinationAddress15:0>, W7

Step 4: Load W0 with the data word to program and load the write latch.

0000 2xxxx0 MOV #<Data_Word_Value>, W0

0000 BB1B80 TBLWTL W0, [W7++]

0000 000000 NOP

0000 000000 NOP

Step 5: Initiate the write cycle.

0000 A8E761 BSET NVMCON, #WR

0000 000000 NOP

0000 000000 NOP

Step 6: Repeat this step to poll the WR bit (bit 15 of NVMCON) until it is cleared by the hardware.

0000 040200 GOTO 0x200

0000 000000 NOP

0000 803B02 MOV NVMCON, W2

0000 883C22 MOV W2, VISI

0000 000000 NOP

00001 <VISI> Clock out contents of the VISI register.

0000 000000 NOP

Step 7: Reset device internal PC.

0000 040200 GOTO 0x200

0000 000000 NOP

Step 8: Repeat Steps 4 through 7 until the entire data EEPROM memory is programmed.

2011 Microchip Technology Inc. Advance Information DS39919B-page 15

PIC24FXXKA1XX/FVXXKA3XX

FIGURE 3-9: PROGRAM DATA EEPROM MEMORY FLOW

Start

LoopCount = 0

Configure

Device for

Writes

Load 2 Bytes

to Write

Buffer at <Addr>

LoopCount =

LoopCount + 1

Start Write Sequence

and Poll for WR bit

to be Cleared

No All

locations

done?

Yes

End

DS39919B-page 16 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

3.8 Writing Configuration Registers TABLE 3-7: DEFAULT VALUES FOR

CONFIGURATION REGISTER

The procedure for writing the Configuration registers is

SERIAL INSTRUCTION

the same as for writing code memory. The only differ-

ence is that only one word is programmed in each Configuration

Value

operation. When writing Configuration registers, one Registers

word is programmed during each operation; only work-

FBS 0Fh

ing register, W0, is used as a temporary holding

register for the data to be programmed. FGS 03h

Table 3-7 provides the default values of the FOSCSEL 87h

Configuration registers. FOSC FFh

Note: When writing to the Configuration regis- FWDT DFh

ters, always set the TBLPAG register to FPOR(1) FBh

F8h. This is the upper byte address of all FICD(2) C3h

locations of the Configuration registers.

FDS FFh

Table 3-7 provides the ICSP programming details for Note 1: The I2C2SEL bit (FPOR<4>) is not

programming the Configuration registers, including the implemented on PIC24FXXKAX01

serial pattern with the ICSP command code, which devices and should be programmed as ‘1’.

must be transmitted LSB first using the PGCx and

2: The FICD<6> bit is a reserved bit and

PGDx pins (see Figure 3-2). In Step 1 of Table 3-8, the

should be programmed as ‘1’.

Reset vector is exited. In Step 2, the NVMCON register

is initialized for programming code memory. In Step 3,

the 24-bit starting destination address for programming

is loaded into the TBLPAG register and W7 register.

2011 Microchip Technology Inc. Advance Information DS39919B-page 17

PIC24FXXKA1XX/FVXXKA3XX

TABLE 3-8: SERIAL INSTRUCTION EXECUTION FOR WRITING CONFIGURATION REGISTERS

Command Data Command

(Binary) (Hex) (Binary)

Step 1: Exit the Reset vector.

0000 000000 NOP

0000 040200 GOTO 0x200

0000 000000 NOP

Step 2: Initialize the Write Pointer (W7) for the TBLWT instruction.

0000 200007 MOV #0x0000, W7

Step 3: Set the NVMCON register to program Configuration registers.

0000 24004A MOV #0x4004, W10

0000 883B0A MOV W10, NVMCON

Step 4: Initialize the TBLPAG register.

0000 200F80 MOV #0xF8, W6

0000 880190 MOV W0, TBLPAG

Step 5: Load the Configuration register data to W6.

0000 2xxxx6 MOV #<FBS_VALUE>, W6

Step 6: Write the Configuration register data to the write latch and increment the Write Pointer.

0000 000000 NOP

0000 BB1B86 TBLWTL W6, [W7++]

0000 000000 NOP

0000 000000 NOP

Step 7: Initiate the write cycle.

0000 A8E761 BSET NVMCON, #WR

0000 000000 NOP

0000 000000 NOP

Step 8: Repeat this step to poll the WR bit (bit 15 of NVMCON) until it is cleared by the hardware.

0000 040200 GOTO 0x200

0000 000000 NOP

0000 803B02 MOV NVMCON, W2

0000 883C22 MOV W2, VISI

0000 000000 NOP

0001 <VISI> Clock out contents of the VISI register.

0000 000000 NOP

Step 9: Reset device internal PC.

0000 040200 GOTO 0x200

0000 000000 NOP

Step 10: Repeat Steps 5 through 9 to write other fuses, Load W6 with their respective values and W7 with their

respective addresses.

DS39919B-page 18 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

3.9 Reading Code Memory To minimize the reading time, the packed instruction

word format, which was used for writing, is also used

To read the code memory, execute a series of TBLRD for reading (see Figure 3-7). In Step 3, the Write

instructions and clock out the data using the REGOUT Pointer, W7, is initialized. In Step 4, two instruction

command. words are read from code memory, and clocked out of

Table 3-9 provides the ICSP programming details for the device through the VISI register, using the

reading code memory. In Step 1, the Reset vector is REGOUT command. Step 4 is repeated until the

exited. In Step 2, the 24-bit starting source address for required amount of code memory is read.

reading is loaded into the TBLPAG register and the W6

register. The upper byte of the starting source address

is stored in TBLPAG, and the lower 16 bits of the source

address are stored in W6.

TABLE 3-9: SERIAL INSTRUCTION EXECUTION FOR READING CODE MEMORY

Command Data

Description

(Binary) (Hex)

Step 1: Exit Reset vector.

0000 000000 NOP

0000 040200 GOTO 0x200

0000 000000 NOP

Step 2: Initialize TBLPAG and the Read Pointer (W6) for TBLRD instruction.

0000 200xx0 MOV #<SourceAddress23:16>, W0

0000 880190 MOV W0, TBLPAG

0000 2xxxx6 MOV #<SourceAddress15:0>, W6

Step 3: Initialize the Write Pointer (W7) to point to the VISI register.

0000 207847 MOV #VISI, W7

0000 000000 NOP

Step 4: Read and clock out the contents of the next two locations of code memory through the VISI register using

the REGOUT command.

0000 BA1B96 TBLRDL [W6], [W7]

0000 000000 NOP

0000 000000 NOP

0001 <VISI> Clock out contents of VISI register.

0000 000000 NOP

0000 BADBB6 TBLRDH [W6++], [W7]

0000 000000 NOP

0000 000000 NOP

0000 BAD3D6 TBLRDH.B [++W6], [W7--]

0000 000000 NOP

0000 000000 NOP

0001 <VISI> Clock out contents of VISI register.

0000 000000 NOP

0000 BA0BB6 TBLRDL [W6++], [W7]

0000 000000 NOP

0000 000000 NOP

0001 <VISI> Clock out contents of VISI register.

0000 000000 NOP

Step 5: Reset device internal PC.

0000 040200 GOTO 0x200

0000 000000 NOP

Step 6: Repeat Steps 4 and 5 until the required code memory is read.

2011 Microchip Technology Inc. Advance Information DS39919B-page 19

PIC24FXXKA1XX/FVXXKA3XX

3.10 Reading Data EEPROM Memory Table 3-10 provides the ICSP programming details for

reading data memory.

The procedure for reading data EEPROM memory is

the same as reading the code memory. The only differ- Note: When reading from EEPROM, always set

ence is that the 16-bit data words are read instead of the TBLPAG register to 7Fh. This is the

the 24-bit words. upper byte address of all locations of data

EEPROM.

TABLE 3-10: SERIAL INSTRUCTION EXECUTION FOR READING DATA EEPROM MEMORY

Command Data

Description

(Binary) (Hex)

Step 1: Exit Reset vector.

0000 000000 NOP

0000 040200 GOTO 0x200

0000 000000 NOP

Step 2: Initialize TBLPAG and the Read Pointer (W6) for TBLRD instruction.

0000 2007F0 MOV #0x7F, W0

0000 880190 MOV W0, TBLPAG

0000 2FExx6h MOV #<SourceAddress15:0>, W6;(FExx)

Step 3: Initialize the Write Pointer (W7) to point to the VISI register.

0000 207847 MOV #VISI, W7

0000 000000 NOP

Step 4: Read and clock out the contents of the next location of data EEPROM memory through the VISI register

using the REGOUT command.

0000 BA1B96 TBLRDL [W6++], [W7]

0000 000000 NOP

0000 000000 NOP

0001 <VISI> Clock out contents of VISI register.

0000 000000 NOP

Step 5: Repeat Step 4 until the required data EEPROM memory is read.

Step 6: Reset device internal PC.

0000 040200 GOTO 0x200

0000 000000 NOP

DS39919B-page 20 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

3.11 Reading Configuration Memory Table 3-11 provides the ICSP programming details for

reading all of the Configuration registers.

The procedure for reading a Configuration register is

the same as reading the code memory. The only Note: When reading from the Configuration reg-

difference is that the 16-bit data words are read (with isters, always set the TBLPAG register to

the upper byte read being all ‘0‘s) instead of the 24-bit F8h. This is the upper byte address of all

words. There are eight Configuration registers and they locations of the Configuration registers.

are read one register at a time. The Read Pointer, W6, should be

initialized to 00h.

TABLE 3-11: SERIAL INSTRUCTION EXECUTION FOR READING ALL THE CONFIGURATION

REGISTERS

Command Data

Description

(Binary) (Hex)

Step 1: Exit Reset vector.

0000 000000 NOP

0000 040200 GOTO 0x200

0000 000000 NOP

Step 2: Initialize TBLPAG, the Read Pointer (W6) and the Write Pointer (W7) for TBLRD instruction.

0000 200F80 MOV #0xF8, W0

0000 880190 MOV W0, TBLPAG

0000 200007 MOV #0x0000,W6

0000 207847 MOV #VISI, W7

0000 000000 NOP

Step 3: Read the Configuration register and write it to the VISI register (located at 784h), and clock out the

VISI register using the REGOUT command.

0000 BA0BB6 TBLRDL [W6++], [W7]

0000 000000 NOP

0000 000000 NOP

0001 <VISI> Clock out contents of VISI register.

Step 4: Repeat Step 3 to read other fuses. Load W6 with their respective address.

Step 5: Reset device internal PC.

0000 040200 GOTO 0x200

0000 000000 NOP

2011 Microchip Technology Inc. Advance Information DS39919B-page 21

PIC24FXXKA1XX/FVXXKA3XX

3.12 Verifying Code Memory, Data FIGURE 3-10: VERIFY CODE MEMORY

EEPROM Memory and FLOW

Configuration Registers Start

To verify the code memory, read the code memory

space and compare it with the copy held in the

Set TBLPTR = 0

programmer’s buffer. To verify the data EEPROM and

Configuration registers, follow the similar procedure.

Figure 3-10 illustrates the verify process flowchart.

Memory reads occur 1 byte at a time, hence 2 bytes

must be read to compare with the word in the Read Low Byte

with Post-Increment

programmer’s buffer. Refer to Section 3.9 “Reading

Code Memory” for implementation details of reading

code memory. On the same lines, the data EEPROM

Read High Byte

and Configuration registers can be verified.

with Post-Increment

Note: Code memory should be verified

immediately after writing if code protection

is enabled. Since Configuration registers Does

No Failure

Word = Expect Report Error

include the device code protection bit, the Data?

device will not be readable or verifiable if a

device Reset occurs after the code-protect Yes

bits are set (value = 0).

All

No

code memory

verified?

Yes

End

DS39919B-page 22 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

3.13 Reading the Application ID Word 3.14 Exiting ICSP Mode

The Application ID Word is stored in address 8007F0h Exit the Program/Verify mode by removing VIH from

in the executive code memory. To read this memory MCLR/VPP as illustrated in Figure 3-11. The only

location, use the SIX control code to move this program requirement to exit is that an interval of P16 should

memory location to the VISI register. Then, the elapse between the last clock and program signals on

REGOUT control code must be used to clock the PGCx and PGDx before removing VIH.

contents of the VISI register out of the device.

Table 3-12 provides the corresponding control and FIGURE 3-11: EXITING ICSP™ MODE

instruction codes that must be serially transmitted to

the device to perform this operation. P16 P17

After the programmer has clocked out the Application VIH/VIHH

ID Word, it must be inspected. If the Application ID has MCLR/VPP

the value, CBh, the programming executive resides in

the memory and the device can be programmed using VDD

the mechanism described in Section 4.0 “Device

VIH

Programming – Enhanced ICSP”. However, if the PGDx

Application ID has any other value, the programming

executive does not reside in the memory; it must be

PGCx

loaded to memory before the device can be

programmed. Section 5.4 “Programming the

Programming Executive to Memory” describes the PGD = Input

procedure for loading the programming executive to

memory.

TABLE 3-12: SERIAL INSTRUCTION EXECUTION FOR READING THE APPLICATION ID WORD

Command Data

Description

(Binary) (Hex)

Step 1: Exit Reset vector.

0000 000000 NOP

0000 040200 GOTO 0x200

0000 000000 NOP

Step 2: Initialize TBLPAG and the Read Pointer (W0) for TBLRD instruction.

0000 200800 MOV #0x80, W0

0000 880190 MOV W0, TBLPAG

0000 2057F0 MOV #0x7F0, W0

0000 207841 MOV #VISI, W1

0000 000000 NOP

0000 BA0890 TBLRDL [W0], [W1]

0000 000000 NOP

0000 000000 NOP

Step 3: Output the VISI register using the REGOUT command.

0001 <VISI> Clock out contents of the VISI register.

0000 000000 NOP

2011 Microchip Technology Inc. Advance Information DS39919B-page 23

PIC24FXXKA1XX/FVXXKA3XX

4.0 DEVICE PROGRAMMING – 4.1 Overview of the Programming

ENHANCED ICSP Process

Note: The Programming Executive (PE) can be Figure 4-1 illustrates the high-level overview of the

located in the following folder within your programming process.

installation of MPLAB® IDE: Perform the following steps:

...\Microchip\MPLAB IDE\REAL ICE 1. Enter ICSP mode.

and then selecting the hex PE file,

2. Erase the device.

RIPE_01b_xxxxxx.hex.

3. Verify the programming executive.

This section describes the programming of the device 4. Exit ICSP mode.

through Enhanced ICSP and the programming executive. 5. Enter Enhanced ICSP mode.

The programming executive resides in the executive

6. Program the code memory.

memory (separate from user memory space) and is exe-

cuted when Enhanced ICSP Programming mode is 7. Verify the code memory.

entered. The programming executive provides the mech- 8. Program the Configuration registers.

anism for the programmer (host device) to program and 9. Verify the Configuration registers.

verify the PIC24FXXKA1XX/FVXXKA3XX devices using

Steps 7 and 9 ensure that the programming was

a simple command set and communication protocol. The

successful.

basic functions provided by the programming executive

are: After the programming executive is verified in

memory (or loaded if not present), the

• Read Memory

PIC24FXXKA1XX/FVXXKA3XX devices can be

• Program Memory programmed using the command set provided in

• Blank Check Table 4-1.

• Read Executive Firmware Revision

The programming executive performs the low-level FIGURE 4-1: HIGH-LEVEL ENHANCED

tasks required for erasing, programming and verifying ICSP™ PROGRAMMING FLOW

a device. This allows the programmer to program the

device by issuing the appropriate commands and data. Start

Table 4-1 provides these commands. For detailed

descriptions of each command, see Section 5.2 Enter ICSP™ Mode

“Programming Executive Commands”.

Perform Chip

TABLE 4-1: COMMAND SET SUMMARY Erase

Command Description

SCHECK Sanity check. Exit ICSP Mode

READC Read Device ID registers.

READD Read data EEPROM memory.

Enter Enhanced ICSP Mode

READP Read Code register.

PROGC Write User ID. Program and Verify

PROGD Program and verify one word of data Code Memory

EEPROM memory.

Program and verify one row of code Program and Verify

PROGP Data EEPROM Memory

memory or one Configuration register.

QBLANK Query if the code memory is blank.

Program and Verify

QVER Query the software version. Configuration Bits

The programming executive uses the device’s data

RAM for variable storage and program execution. After Exit Enhanced ICSP Mode

the programming executive is run, no assumptions

should be made about the contents of the data RAM.

End

DS39919B-page 24 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

4.2 Confirming the Presence of the FIGURE 4-2: CONFIRMING PRESENCE

Programming Executive OF PROGRAMMING

EXECUTIVE

Before beginning programming, confirm if the

programming executive is stored in the executive

memory and perform the following: Start

1. Enter In-Circuit Serial Programming mode

(ICSP). Enter ICSP™ Mode

2. Read the unique Application ID Word stored in

the executive memory.

Read the

Figure 4-2 illustrates this procedure. Application ID

from Address

If the programming executive is resident, the 8007F0h

Application ID Word is CBh, which means

programming can resume as normal. However, if the

Application ID Word is not CBh, the programming Is

No

Application ID

executive must be programmed to executive code CBh?

memory using the method described in Section 5.4

“Programming the Programming Executive to Yes

Memory”.

Prog. Executive is Prog. Executive must

Section 3.0 “Device Programming – ICSP” describes Resident in Memory be Programmed

the ICSP programming method. Section 3.13 “Reading

the Application ID Word” describes the procedure for

reading the Application ID Word in ICSP mode.

Finish

2011 Microchip Technology Inc. Advance Information DS39919B-page 25

PIC24FXXKA1XX/FVXXKA3XX

4.3 Entering Enhanced ICSP Mode 4.3.2 HIGH-VOLTAGE ENTRY

The procedure for entering Enhanced ICSP

4.3.1 LOW-VOLTAGE ENTRY Program/Verify mode using the VPP pin is the same as

Perform the following steps to enter Enhanced ICSP entering the mode using MCLR. The only differences

Program/Verify mode using MCLR: are that the programming voltage applied to VPP is

1. Briefly drive the MCLR pin high and then low. VIHH, and before presenting the key sequence on

PGDx, an interval of at least P18 should elapse.

2. Clock a 32-bit key sequence into PGDx.

Figure 4-4 illustrates this procedure.

3. Drive the MCLR high within a specified period

and continue to hold high. Once the key sequence is complete, VIHH must be

applied to VPP and held at that level for as long as the

Figure 4-3 illustrates this procedure. Program/Verify mode is to be maintained. An interval of

The programming voltage applied to MCLR is VIH, at least P19 and P7 should elapse before presenting

which is essentially VDD in the case of data on PGDx.

PIC24FXXKA1XX/FVXXKA3XX devices. There is no Signals appearing on PGDx before P7 has elapsed will

minimum time requirement for holding at VIH. After VIH not be interpreted as valid.

is removed, an interval of at least P18 must elapse

before presenting the key sequence on PGDx. On successful entry, the program memory can be

accessed and programmed in serial fashion. While in

The key sequence is a specific 32-bit pattern: ‘0100 the Program/Verify mode, all unused I/Os are placed in

1101 0100 0011 0100 1000 0101 0000‘(more eas- the high-impedance state.

ily remembered as 4D434850h in hexadecimal format).

The device will enter Program/Verify mode only if the key 4.3.3 CODE-PROTECT ICSP ENTRY

sequence is valid. The MSB of the most significant nibble

When code protection is employed on the

must be shifted in first.

PIC24FXXKA3XX devices (BWRP, GSS0 or

Once the key sequence is complete, VIH must be GWRP = 0), then the voltage on VDD must be above

applied to MCLR and held at that level for as long as VBULK in order to erase, and then program the device.

the Program/Verify mode is to be maintained. An Care must be taken in the design and layout of a board

interval of at least P19 and P7 must elapse before so that any parts connected to VDD can withstand what

presenting data on PGDx. Signals appearing on PGDx may be an increase in voltage if the device is running

before P7 has elapsed will not be interpreted as valid. below VBULK.

DS39919B-page 26 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

FIGURE 4-3: ENTERING ENHANCED ICSP™ MODE USING LOW-VOLTAGE ENTRY

P6 P19 P7

P14

VIH VIH

MCLR

VDD

Program/Verify Entry Code = 4D434850h

PGDx 0 1 0 0 1 ... 0 0 0 0

b31 b30 b29 b28 b27 b3 b2 b1 b0

PGCx

P18 P1A

P1B

FIGURE 4-4: ENTERING ENHANCED ICSP™ MODE USING HIGH-VOLTAGE ENTRY

P6

VIHH

VPP P7

VDD

Program/Verify Entry Code = 4D434850h

PGDx 0 1 0 0 1 ... 0 0 0 0

b31 b30 b29 b28 b27 b3 b2 b1 b0

PGCx

P18 P1A

P1B

2011 Microchip Technology Inc. Advance Information DS39919B-page 27

PIC24FXXKA1XX/FVXXKA3XX

4.4 Blank Check 4.5.2 PROGRAMMING VERIFICATION

The term “Blank Check” implies verifying if the device After the code memory is programmed, the contents of

has been successfully erased and has no programmed the memory can be verified to ensure that the

memory locations. A blank or erased memory location programming is successful. Verification requires the

is always read as ‘1’. code memory to be read back and compared with the

copy held in the programmer‘s buffer.

The Device ID registers (FF0002h:FF0000h) can be

ignored by the Blank Check as this region stores device The READP command can be used to read back all of

information that cannot be erased. The device the programmed code memory.

Configuration registers are also ignored by the Blank Alternatively, the programmer can perform the

Check. Additionally, all unimplemented memory space verification after the entire device is programmed using

should be ignored by the Blank Check. a checksum computation.

The QBLANK command is used for the Blank Check. It

determines if the code memory is erased by testing FIGURE 4-5: FLOWCHART FOR

these memory regions. A ‘BLANK’ or ‘NOT BLANK’ PROGRAMMING CODE

response is returned. If it is determined that the device MEMORY

is not blank, it must be erased before attempting to

program the device. Start

4.5 Code Memory Programming

BaseAddress = 00h

4.5.1 PROGRAMMING METHODOLOGY RemainingCmds = 176

Code memory is programmed with the PROGP

command. PROGP programs one row of code memory, Send PROGP

starting from the memory address specified in the Command to Program

command. The number of PROGP commands required BaseAddress

to program a device depends on the number of write

blocks that must be programmed in the device.

Figure 4-5 illustrates an example flowchart for Is

No

programming code memory. In this example, all 5.5K PROGP response

instruction words of a PIC24FXXKA1XX/FVXXKA3XX PASS?

device are programmed.

Yes

• First, the number of commands to send (titled

‘RemainingCmds’ in the flowchart) is set to 176, RemainingCmds =

and the destination address (called RemainingCmds – 1

‘BaseAddress’) is set to ‘0’.

• Next, one write block in the device is programmed BaseAddress =

with a PROGP command. Each PROGP command BaseAddress + 40h

contains data for one row of code memory of the Are

PIC24FXXKA1XX/FVXXKA3XX device. No

RemainingCmds

• After the first command is processed successfully, ‘0‘?

‘RemainingCmds’ is decremented by 1 and

compared with 0. Yes

Since there are more PROGP commands to be sent, Failure

‘BaseAddress’ is incremented by 40h to point to the End Report Error

next row of memory. On the second PROGP command,

the second row is programmed. This process is

repeated until the entire device is programmed. Special

handling should not be performed when a panel

boundary is crossed.

DS39919B-page 28 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

4.6 Data EEPROM Programming FIGURE 4-6: FLOWCHART FOR

PROGRAMMING DATA

4.6.1 PROGRAMMING METHODOLOGY EEPROM

The programming executive uses the PROGD command

Start

to program the data EEPROM. Figure 4.7 illustrates

this process.

RemainingWords = 256 (100h)

• First, the number of words to program BaseAddress = 0

(RemainingWords) is based on the device size

and the destination address (DestAddress) is set Send PROGD

Command to Program

to 0. In this example, 256 words of data EEPROM BaseAddress

will be programmed.

• The first PROGD command programs the first word

of data EEPROM. Is No

PROGD response

• Once the command completes successfully, PASS?

‘RemainingWords’ is decremented by 1 and

Yes

compared with 0.

• Since there are 255 more words to program, RemainingWords =

RemainingWords – 1

‘BaseAddress’ is incremented by 02h to point to

the next word of data EEPROM. BaseAddress =

BaseAddress + 02h

• This process is then repeated until all 256 words

Are

of data EEPROM are programmed. No

RemainingWords

‘0’?

4.6.2 PROGRAMMING VERIFICATION

Yes

Once the data EEPROM is programmed, the contents

Finish Failure

of the memory can be verified to ensure the Report Error

programming was successful. Verification requires the

data EEPROM to be read back and compared with the

copy held in the programmer‘s buffer. The READD

command reads back the programmed data EEPROM.

Alternatively, the programmer can perform the

verification once the entire device is programmed using

a checksum computation, as described in

Section 6.1.1 “Checksum Computation”.

2011 Microchip Technology Inc. Advance Information DS39919B-page 29

PIC24FXXKA1XX/FVXXKA3XX

4.7 Configuration Bits Programming Eight PROGP commands are required to program the

Configuration bits. Figure 4-7 illustrates the flowchart

The PIC24FXXKA1XX/FVXXKA3XX family has eight for Configuration bit programming.

Configuration registers. The bits of these registers can

be set or cleared to select various device configura- Note: If the General Segment Code-Protect bit

tions. There are three types of Configuration bits: (GCP) is programmed to ‘0‘, code mem-

ory is code-protected and cannot be read.

• System Operation Bits

Code memory must be verified before

These bits determine the power-on settings for enabling code protection. See

system-level components, such as the oscillator and Section 4.7.3 “Code-Protect Configura-

Watchdog Timer. tion Bits” for more information on

• Code-Protect Bits code-protect Configuration bits.

These bits prevent program memory from being read

4.7.2 PROGRAMMING VERIFICATION

and written.

After the Configuration bits are programmed, the

• Device ID Bits

contents of memory should be verified to ensure that

These are read-only bits, which are located from the programming was successful. Verification requires

FF0000 to FF0003, and are unique to every device. the Configuration bits to be read back and compared

Table 4-2 provides the Configuration registers. against the copy held in the programmer‘s buffer. The

READP command reads back the programmed

4.7.1 PROGRAMMING METHODOLOGY Configuration bits and verifies that the programming

was successful.

Configuration bits may be programmed, a single byte at

a time, using the PROGP command. This command

specifies the configuration data and Configuration

register address. When Configuration bits are

programmed, any unimplemented or reserved bits

must be programmed with a ‘1’.

FIGURE 4-7: CONFIGURATION BIT PROGRAMMING FLOW

Start

ConfigAddress = F80000h

Send PROGP

Command

Is No

PROGP response

PASS?

Yes

Is

ConfigAddress = No

ConfigAddress

ConfigAddress + 2

F80010h?

Yes

End Failure

Report Error

DS39919B-page 30 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

4.7.3 CODE-PROTECT CONFIGURATION It is imperative that all code protection bits should be ‘1’

BITS while the device is being programmed and verified.

Only after the device is programmed and verified

The FBS and FGS Configuration registers are special

should any of the above bits be programmed to ‘0’ (see

Configuration registers which control the code

Section 4.7 “Configuration Bits Programming”).

protection for the boot segment and general segment,

respectively. For each segment, two forms of code Note: All bits in the FBS and FGS Configuration

protection are provided. One form prevents code registers can only be programmed to a

memory from being written (write protection), while the value of ‘0‘.Bulk Erasing the chip is the

other prevents code memory from being read (read only way to reprogram code-protect bits

protection). from on (‘0’) to off (‘1’).

The BWRP and GWRP bits control write protection and

the BSS0 and GSS0 bits control read protection.

When write protection is enabled, any programming

operation to code memory will fail. When read

protection is enabled, any read from code memory will

cause a 00h to be read, regardless of the actual

contents of code memory. Since the programming

executive always verifies what it programs, attempting

to program code memory with read protection enabled

also results in failure.

TABLE 4-2: PIC24F(V)XXKAXXX FAMILY CONFIGURATION BITS DESCRIPTION

Bit Field Register Description

BOREN<1:0> FPOR<1:0> Brown-out Reset Enable bits

11 = Brown-out Reset enabled in hardware; SBOREN bit disabled

10 = Brown-out Reset enabled only while device is active and disabled in

Sleep; SBOREN bit disabled

01 = Brown-out Reset controlled with the SBOREN bit setting

00 = Brown-out Reset disabled in hardware; SBOREN bit disabled

BORV<1:0> FPOR<6:5> Brown-out Reset Voltage bits

For PIC24FXXKA1XX and PIC24FXXKA3XX devices:

11 = VBOR set to 1.8V min

10 = VBOR set to 2.7V min

01 = VBOR set to 3.0V min

For PIC24FVXXKA3XX devices:

11 = VBOR set to 2.0V min

10 = VBOR set to 2.7V min

01 = VBOR set to 3.0V min

For all devices:

00 = Downside protection on POR enabled – “Zero-power” selected

BSS0 FBS<3> Boot Segment Program Flash Code Protection bit

1 = Standard security enabled

0 = High security enabled

BSZ<1:0> FBS<2:1> Boot Segment Program Flash Size Selection bits(1)

11 = No boot program Flash segment

10 = Boot program Flash segment starts at 200h, ends at 000AFEh

01 = Boot program Flash segment starts at 200h, ends at 0015FEh

For PIC24FV32KA3XX devices:

00 = Reserved

For all other devices:

00 = Reserved

Note 1: Applies only to 28-pin devices.

2: The MCLRE fuse can only be changed when using the VPP-Based Test mode entry. This prevents a user

from accidentally locking out the device from low-voltage test entry.

2011 Microchip Technology Inc. Advance Information DS39919B-page 31

PIC24FXXKA1XX/FVXXKA3XX

TABLE 4-2: PIC24F(V)XXKAXXX FAMILY CONFIGURATION BITS DESCRIPTION (CONTINUED)

Bit Field Register Description

BWRP FBS<0> Boot Segment Program Flash Write Protection bit

1 = Boot segment may be written

0 = Boot segment is write-protected

DEBUG FICD<7> Background Debugger Enable bit

1 = Background debugger disabled

0 = Background debugger functions enabled

DSWDTEN FDS<7> Deep Sleep Watchdog Timer Enable bit

1 = DSWDT enabled

0 = DSWDT disabled

DSWCKSEL FDS<4> DSWDT Reference Clock Select bit

1 = DSWDT uses LPRC as reference clock

0 = DSWDT uses SOSC as reference clock

DSWDTPS<3:0> FDS<3:0> Deep Sleep Watchdog Timer Postscale Select bits

The DSWDT prescaler is 32; this creates an approximate base time unit of

1 ms.

1111 = 1:2,147,483,648 (25.7 days)

1110 = 1:536,870,912 (6.4 days)

1101 = 1:134,217,728 (38.5 hours)

1100 = 1:33,554,432 (9.6 hours)

1011 = 1:8,388,608 (2.4 hours)

1010 = 1:2,097,152 (36 minutes)

1001 = 1:524,288 (9 minutes)

1000 = 1:131,072 (135 seconds)

0111 = 1:32,768 (34 seconds)

0110 = 1:8,192 (8.5 seconds)

0101 = 1:2,048 (2.1 seconds)

0100 = 1:512 (528 ms)

0011 = 1:128 (132 ms)

0010 = 1:32 (33 ms)

0001 = 1:8 (8.3 ms)

0000 = 1:2 (2.1 ms)

DSBOREN FDS<6> Deep Sleep Zero-Power BOR Enable bit

1 = Zero-Power BOR enabled in Deep Sleep

0 = Zero-Power BOR disabled in Deep Sleep (does not affect operation in non

Deep Sleep modes)

FCKSM<1:0> FOSC<7:6> Clock Switching and Monitor Selection Configuration bits

1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

FNOSC<2:0> FOSCSEL<2:0> Oscillator Selection bits

000 = Fast RC Oscillator (FRC)

001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

010 = Primary Oscillator (XT, HS, EC)

011 = Primary Oscillator with PLL module (HS+PLL, EC+PLL)

100 = Secondary Oscillator (SOSC)

101 = Low-Power RC Oscillator (LPRC)

110 = Reserved; do not use

111 = Fast RC Oscillator with divide-by-N (FRCDIV)

Note 1: Applies only to 28-pin devices.

2: The MCLRE fuse can only be changed when using the VPP-Based Test mode entry. This prevents a user

from accidentally locking out the device from low-voltage test entry.

DS39919B-page 32 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

TABLE 4-2: PIC24F(V)XXKAXXX FAMILY CONFIGURATION BITS DESCRIPTION (CONTINUED)

Bit Field Register Description

FWDTEN FWDT<7> Watchdog Timer Enable bit (PIC24FXXKA1XX devices only)

1 = WDT enabled

0 = WDT disabled (control is placed on the SWDTEN bit)

FWDTEN<1:0> FWDT<7,5> Watchdog Timer Enable bit (all PIC24FVXXKA3XX devices)

11 = WDT enabled in hardware

10 = WDT controlled with the SWDTEN bit

01 = WDT enabled only while device active and disabled in Sleep; SWDTEN

bit disabled

00 = WDT disabled in hardware; SWDTEN bit disabled

GSS0 FGS<1> General Segment Code Flash Code Protection bit

1 = No protection

0 = Standard security enabled

GWRP FGS<0> General Segment Code Flash Write Protection bit

1 = General segment may be written

0 = General segment is write-protected

ICS<1:0> FICD<1:0> ICD Pin Placement Select bit

11 = ICD EMUC/EMUD pins are shared with PGEC1/PGED1

10 = ICD EMUC/EMUD pins are shared with PGEC2/PGED2

01 = ICD EMUC/EMUD pins are shared with PGEC3/PGED3

00 = Reserved; do not use

IESO FOSCSEL<7> Internal External Switchover bit

1 = Internal External Switchover mode enabled (Two-Speed Start-up enabled)

0 = Internal External Switchover mode disabled (Two-Speed Start-up disabled)

I2C1SEL(1) FPOR<4> Alternate I2C1 Pin Mapping bit(1)

0 = Alternate location for SCL1/SDA1 pins

1 = Default location for SCL1/SDA1 pins

MCLRE(2) FPOR<7> MCLR Pin Enable bit(2)

1 = MCLR pin enabled; RA5 input pin disabled

0 = RA5 input pin enabled; MCLR disabled

OSCIOFNC FOSC<2> CLKO Enable Configuration bit

1 = CLKO output signal active on the OSCO pin; primary oscillator must be

disabled or configured for the External Clock mode (EC) for the CLKO to

be active (POSCMD<1:0> = 11 or 00)

0 = CLKO output disabled

POSCMD<1:0> FOSC<1:0> Primary Oscillator Configuration bits

11 = Primary oscillator disabled

10 = HS Oscillator mode selected (4 MHz-25 MHz)

01 = XT Oscillator mode selected (100 kHz-4 MHz)

00 = External Clock mode selected

POSCFREQ<1:0> FOSC<4:3> Primary Oscillator Frequency Range Configuration bits

11 = Primary oscillator/external clock input frequency greater than 8 MHz

10 = Primary oscillator/external clock input frequency between 100 kHz and

8 MHz

01 = Primary oscillator/external clock input frequency less than 100 kHz

00 = Reserved, do not use

PWRTEN FPOR<3> Power-up Timer Enable bit

0 = PWRT disabled

1 = PWRT enabled

Note 1: Applies only to 28-pin devices.

2: The MCLRE fuse can only be changed when using the VPP-Based Test mode entry. This prevents a user

from accidentally locking out the device from low-voltage test entry.

2011 Microchip Technology Inc. Advance Information DS39919B-page 33

PIC24FXXKA1XX/FVXXKA3XX

TABLE 4-2: PIC24F(V)XXKAXXX FAMILY CONFIGURATION BITS DESCRIPTION (CONTINUED)

Bit Field Register Description

RTCCKSEL FDS<5> RTCC Reference Clock Select bit (PIC24FXXKA1XX devices only)

1 = RTCC uses SOSC as reference clock

0 = RTCC uses LPRC as reference clock

SOSCSEL FOSC<5> Secondary Oscillator Select bit

1 = Secondary oscillator configured for high-power operation

0 = Secondary oscillator configured for low-power operation

FWPSA FWDT<4> WDT Prescaler

1 = WDT prescaler ratio of 1:128

0 = WDT prescaler ratio of 1:32

WDTPS<3:0> FWDT<3:0> Watchdog Timer Postscale Select bits

1111 = 1:32,768

1110 = 1:16,384

•

•

•

0001 = 1:2

0000 = 1:1

WINDIS FWDT<6> Windowed Watchdog Timer Disable bit

1 = Standard WDT selected; windowed WDT disabled

0 = Windowed WDT enabled

Note 1: Applies only to 28-pin devices.

2: The MCLRE fuse can only be changed when using the VPP-Based Test mode entry. This prevents a user

from accidentally locking out the device from low-voltage test entry.

4.8 Exiting the Enhanced ICSP Mode FIGURE 4-8: EXITING ENHANCED

ICSP™ MODE

To exit the Program/Verify mode, remove VIH from

MCLR/VPP, as illustrated in Figure 4-8. For exiting, an P16 P17

interval, P16, should elapse between the last clock and

VIH/VIHH

program signals on PGCx and PGDx before removing MCLR/VPP

VIH.

VDD

VIH

PGDx

PGCx

PGDx = Input

DS39919B-page 34 Advance Information 2011 Microchip Technology Inc.

PIC24FXXKA1XX/FVXXKA3XX

5.0 THE PROGRAMMING As a 2-wire SPI is used and data transmissions are

half-duplex, a simple protocol is used to control the

EXECUTIVE

direction of PGDx. When the programmer completes a

This section describes the programming executive command transmission, it releases the PGDx line and

communication, programming executive commands, allows the programming executive to drive this line

programming responses, programming the high. The programming executive keeps the PGDx line

programming executive to memory and programming high to indicate that it is processing the command.

verification. After the programming executive has processed the

command, it brings PGDx low for 15 sec to indicate to

5.1 Programming Executive the programmer that the response is available to be

Communication clocked out. The programmer can begin to clock out

the response, 23 sec after PGDx is brought low, and

The programmer and the programming executive have it must provide the necessary amount of clock pulses to

a master-slave relationship, where the programmer is receive the entire response from the programming

the master programming device and the programming executive.

executive is the slave.

After the entire response is clocked out, the

Communication is initiated by the programmer in the programmer should terminate the clock on PGCx until

form of a command. Only one command at a time can be it is time to send another command to the programming

sent to the programming executive. The programming executive; Figure 5.2 displays this protocol.

executive, in turn, only sends one response to the

programmer after receiving and processing a command. 5.1.2 SPI RATE

The programming executive command set is described

In Enhanced ICSP mode, the

in Section 5.2 “Programming Executive

PIC24FXXKA1XX/FVXXKA3XX family devices oper-

Commands”. The response set is described in

ate from the internal Fast RC Oscillator, which has a

Section 5.3 “Programming Executive Responses”.

nominal frequency of 8 MHz. This oscillator frequency

5.1.1 COMMUNICATION INTERFACE yields an effective system clock frequency of 4 MHz. To

ensure that the programmer does not clock too fast, it

AND PROTOCOL

is recommended that a 4 MHz clock be provided by the

The Enhanced ICSP interface is a two-wire SPI, programmer.

implemented using the PGCx and PGDx pins. The

PGCx pin is used as a clock input pin; the programmer FIGURE 5-2: PROGRAMMING

should provide the clock source. The PGDx pin is used

EXECUTIVE SERIAL

to send the command data to, and receive response

TIMING FOR DATA

data from, the programming executive.

TRANSMITTED TO DEVICE

Data transmits to the device should change on the

rising edge and hold on the falling edge of PGCx.

P1

Data receives from the device change on the falling 1 2 3 4 5 6 11 12 13 14 15 16

edge and holds on the rising edge of PGCx. PGCx

P1A

The data transmissions are sent to the MSB first using P1B

P3

16-bit mode (see Figure 5-1 and Figure 5-2). PGDx

P2

MSb 14 13 12 11 ... 5 4 3 2 1 LSb

FIGURE 5-1: PROGRAMMING

EXECUTIVE SERIAL

TIMING FOR DATA

RECEIVED FROM DEVICE

P1

1 2 3 4 5 6 11 12 13 14 15 16

PGCx

P1A

P3

P1B

P2

PGDx MSb ...

14 13 12 11 5 4 3 2 1 LSb

2011 Microchip Technology Inc. Advance Information DS39919B-page 35

PIC24FXXKA1XX/FVXXKA3XX

5.1.3 TIME-OUTS does not have a time-out, it is imperative that the pro-

grammer correctly follow the described communication

The programming executive does not use the Watch-

protocol.

dog Timer or time-out for transmitting responses to the

programmer. If the programmer does not follow the flow As a safety measure, the programmer should use the

control mechanism using PGCx, as described in command time-outs identified and listed in Table 5-1. If

Section 5.1.1 “Communication Interface and Proto- the command time-out expires, the programmer should

col”, it is possible that the programming executive will reset the programming executive and start

behave unexpectedly while trying to send a response programming the device again.

to the programmer. Since the programming executive

FIGURE 5-3: PROGRAMMING EXECUTIVE – PROGRAMMER COMMUNICATION PROTOCOL

Host Transmits Programming Executive

Host Clocks Out Response

Last Command Word Processes Command

1 2 15 16 1 2 15 16 1 2 15 16

PGCx

PGDx MSB X X X LSB 1 0 MSB X X X LSB MSB X X X LSB

P8 P9 P20 P21

PGCx = Input PGCx = Input (Idle) PGCx = Input

PGDx = Input PGDx = Output PGDx = Output

5.2 Programming Executive FIGURE 5-4: COMMAND FORMAT

Commands

15 12 11 0

The programming executive command set is listed in Opcode Length

Table 5-1. This table contains the opcode, mnemonic,

Command Data First Word (if required)

length, time-out and description for each command.

Section 5.2.4 “Command Descriptions” provides •

functional details on each command. •

Command Data Last Word (if required)

5.2.1 COMMAND FORMAT

The programming executive commands have a

The command opcode must match one of those in the

general format consisting of a 16-bit header and any

command set. Any command that is received that does

required data for the command (see Figure 5-4). The