Professional Documents

Culture Documents

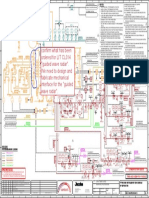

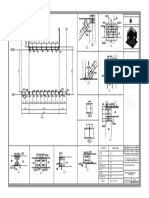

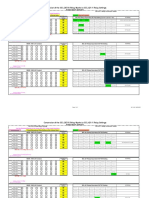

B-PRO 8700 Function Logic Diagram: Output Matrix

Uploaded by

Eric DondebzangaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

B-PRO 8700 Function Logic Diagram: Output Matrix

Uploaded by

Eric DondebzangaCopyright:

Available Formats

B-PRO 8700 Function Logic Diagram

v3.1 sheet 1 of 1

50LS-1 I1a

50LS-1 I1b 100 Logic Gate Switch

50LS-1 I1c T

50LS-1 Input 1 HIGH

0

101

50LS-2 I1a

50LS-2 I1b 102 Logic Gate Switch

0

50LS-2 I1c T

50LS-2 Input 1 HIGH 100ms

0

0

103

100ms

50LS Input 1 Low Set Overcurrent 0

50 I1a (phase current supervision 4% of nominal CT rating) 100ms

50 I1b 104 0

50 I1c 100ms

0

T1

Input 1 50 Trip 50BF-1 Input 1 TRIP 100ms

0

Input 1 51 Trip

OUTPUT RELAY 1-14

0

Input 1 50N Trip

50BF Input 1 Enabled 106 100ms

Input 1 51N Trip

Input 1 46-50 Trip 0

Input 1 46-51 Trip

87B-1 Trip

87B-2 Trip

105 Breaker Failure Initiator

T2

0

50BF-2 Input 1 TRIP

0

100ms

100ms

87T Trip

ProLogic 1-15 0

External Input 1-9 100ms

50BF Input 1 Breaker Failure

0

50 Input 1 Directional Element T T = 10ms or setting, whichever is greater, if 50 is directional 100ms

107 50 Input 1 TRIP

0

I1a 0

Select Maximum Imax > 50 Pickup Level 10ms Timer on alarm pickup delay active only if 51 is directional.

Phase Current for 51 Input 1 ALARM 100ms

I1b 0

50 Element

Imax > 51 Pickup Level 0

I1c 51 Element

108 51 Input 1 TRIP 100ms

51 Input 1 Directional Element

50/51 Input 1 Over Current 0

100ms

50N Input 1 Directional Element T T = 10ms or setting, whichever is greater, if 50N is directional

0

109 50N Input 1 TRIP

0

I1a 100ms

Calculate 3I0 for 3I0 > 50N Pickup Level 10ms Timer on alarm pickup delay active only if 51N is directional.

I1b 50N Element 51N Input 1 ALARM

0

51N Element 3I0 > 51N Pickup Level

I1c

110 51N Input 1 TRIP

51N Input 1 Directional Element

50N/51N Input 1 Neutral Over Current

46-50 Input 1 Directional Element T T = 10ms or setting, whichever is greater, if 46-50 is directional

109 46-50 Input 1 TRIP

0

I1a

Calculate I2 for I2 > 46-50 Pickup Level 10ms Timer on alarm pickup delay active only if 46-51 is directional.

I1b 46-50 Element 46-51 Input 1 ALARM

0

46-51 Element I2 > 46-51 Pickup Level

I1c

110 46-51 Input 1 TRIP FAULT

46-51 Input 1 Directional Element RECORDER

46-50/46-51 Input 1 Negative Sequence Over Current User - Configurable

119 OUTPUT MATRIX

50 Non-Directional 50 Forward

113 131 50 Input 1 Directional Element

50 Reverse

120

121

51 Non-Directional 51 Forward SWING

114 132 51 Input 1 Directional Element RECORDER

51 Reverse

122

111

Output of Directional Element

is logical 1 when Forward and 123

logical 0 when Reverse 50N Non-Directional 50N Forward

115 133 50N Input 1 Directional Element

50N Reverse

Vpos Memory FORWARD 124

ILpos Input 1

Alpha

Beta REVERSE 125

51N Non-Directional 51N Forward

116 134 51N Input 1 Directional Element

51N Reverse

126

59 Vpos (2 volts RMS fixed) 112

50 ILpos Input 1 (4% Inominal RMS fixed) 127

46-50 Non-Directional 46-50 Forward

117 135 46-50 Input 1 Directional Element

46-50 Reverse

128

129

46-51 Non-Directional 46-51 Forward

118 136 46-51 Input 1 Directional Element

46-51 Reverse

130

Input 1 Directional Element

50LS-1 Inputs 2-6 HIGH

Function Block for Inputs 2-6 50LS-2 Inputs 2-6 HIGH

Same functions as Input 1

50BF-1 Inputs 2-6 TRIP

Va

50BF-2 Inputs 2-6 TRIP

Vb (1) 50LS-1 O/C

50 Inputs 2-6 TRIP

Vc (2) 50LS-2 O/C

51 Inputs 2-6 ALARM

(3) 50BF 51 Inputs 2-6 TRIP

I2a - I6a (4) 50/51 50N Inputs 2-6 TRIP

(5) 50N/51N 51N Inputs 2-6 ALARM

I2b - I6b

51N Inputs 2-6 TRIP

I2c - I6c (6) 46-50/46-51

46-50 Inputs 2-6 TRIP

(7) Directional Element

46-51 Inputs 2-6 ALARM

Input Functions (2 to 6) 46-51 Inputs 2-6 TRIP

IOA = I 5 a + I 6 a

IOB = I 5 b + I 6 b

IOC = I 5 c + I 6 c

I5a Wye / Delta

CT Ratio Mismatch

IOA IOB IOC

I5b Correction Input 5 &

3I0 Elimination

I5c

2nd Harmonic Restraint IO 2nd and 5th Harmonic Restraint

Trip A

87T Trip B 137 87T TRIP

Trip C

5th Harmonic Restraint IR

I6a

Wye / Delta

I6b CT Ratio Mismatch

Correction Input 6 &

I6c 3I0 Elimination IRA IRB IRC

Delta Phase and

IRA = (I 5 a + I 6 a ) 2 ROCOD Supervision

IRB = (I 5 b + I 6 b ) 2

IRC = (I 5 c + I 6 c ) 2

87T Transformer Differential

IOA = ∑ I ia

I1a CT Ratio Mismatch IOB = ∑ I ib

Correction Input 1 IOC = ∑ I ic

I1b Vector sum of all inputs

I1c

Set input for Bus1, connected to Bus1 IOA IOB IOC

Bus2 or NC (rec.)

IO External Fault CT Saturation Detector

I2a CT Ratio Mismatch

87B-1 Trip A

Correction Input 2

I2b (Bus1) Trip B 138 87B-1 TRIP

Set input for Bus1,

I2c Bus2 or NC (rec.) Note: Any current input

can be used in either Trip C

87B-1 or 87B-2

IR

I3a CT Ratio Mismatch

Correction Input 3 Magnitude sum / 2 of

all inputs connected

I3b to Bus1 IRA IRB IRC CT Saturation Delta Phase and

Set input for Bus1, and Harmonic ROCOD Supervision

I3c Bus2 or NC (rec.) IRA = ∑ I ia 2 Restraint

IRB = ∑ I ib 2

IRC = ∑ I ic 2

IOA = ∑ I ia

IOB = ∑ I ib

CT Ratio Mismatch

IOC = ∑ I ic

I4a

Correction Input 4 Vector sum of all inputs

connected to Bus2

I4b IOA IOB IOC

Set input for Bus1,

I4c Bus2 or NC (rec.)

IO External Fault CT Saturation Detector

87B-2 Trip A

I5a CT Ratio Mismatch

Correction Input 5 (Bus2) Trip B 139 87B-2 TRIP

I5b Note: Any current input

Set input for Bus1, can be used in either

I5c Bus2 or NC (rec.) 87B-1 or 87B-2 Trip C

IR

Magnitude sum / 2 of

I6a CT Ratio Mismatch all inputs connected Note: 87B1 and 87B2 bus protections also include the summation of zero sequence currents from the inputs in the similar fasion to the phase current shown in here

Correction Input 6 to Bus2 IRA IRB IRC CT Saturation Delta Phase and

I6b and Harmonic ROCOD Supervision

IRA = ∑ I ia 2 Restraint These functions are supervised by the zero sequence delta phase measurement

Set input for Bus1,

I6c Bus2 or NC (rec.) IRB = ∑ I ib 2

IRC = ∑ I ic 2

87B-1 and 87B-2 Bus Differential

59-1 Va

59-1 Vb 140 Logic Gate Switch

59-1 Vc T

59-1 TRIP

0

141

59-2 Va

59-2 Vb 142 Logic Gate Switch

59-2 Vc T

59-2 TRIP

0

143

59 Over Voltage

27-1 Va

27-1 Vb 144 Logic Gate Switch

27-1 Vc T

27-1 TRIP

0

145

27-2 Va

27-2 Vb 146 Logic Gate Switch

27-2 Vc T

27-2 TRIP

0

147

27 Under Voltage

59VA (fixed 0.5 pu)

59VB (fixed 0.5 pu) 148

59VC (fixed 0.5 pu)

10s

150 60 LOP ALARM

0

149

60 Loss of Potential Alarm

81O-1 Frequency

T

200ms 151 81O-1 TRIP

0

Vpos > 0.25 pu (or 5V) 0

81O-2 Frequency

T

200ms 152 81O-2 TRIP

0

Vpos > 0.25 pu (or 5V) 0

81 Over Frequency

81U-1 Frequency

T

200ms 153 81U-1 TRIP

0

Vpos > 0.25 pu (or 5V) 0

81U-2 Frequency

T

200ms 154 81U-2 TRIP

0

81 Under Frequency Vpos > 0.25 pu (or 5V) 0

Self Check Fail

Prologic 1 to 15

External Input 1 to 9

Alarms, ProLogic, Virtual Inputs

Virtual Input 1 to 30

and External Inputs

NOTE: All functions use the extracted fundamental component of the analog inputs.

Revision Date Description of Revision By TITLE:

7 - - -

6 - - B-PRO 8700 FUNCTION LOGIC DIAGRAM

-

5

4

2011/05/11

2010/07/20

Updated for B-PRO 8700 v3.1 Firmware

Updated for B-PRO 8700 v2.3 Firmware

SP

NZ ERL PHASE

Power Technologies Ltd.

Document Identifier Document Revision Page Identifier drawing has

1

3

2

2009/11/24

2008/06/27

Updated for B-PRO 8700 v2.2 Firmware

Modified title block

SP

SP

DSN BY: D. Fedirchuk

M. Poole DATE: 2011-05-01 D02242 R03.10 P1 sheet(s)

1 2004/07/15 Updated for B-PRO 8700 v2.0 Firmware PAG INPUT FILENAME: D02242R03.10.SKF Firmware Version: v3.1

DWN BY: S. Phat DATE: 2011-05-01 PRODUCT NUMBER: 109476 Rev 1.00

0 2002/07/18 Initial Version DSO AUTOSKETCH V8

You might also like

- Electric Wire EL02-22: Ba. Meter Circuit (Except Models For Indonesia (1 of 3) )Document4 pagesElectric Wire EL02-22: Ba. Meter Circuit (Except Models For Indonesia (1 of 3) )Eakkasith BieNo ratings yet

- Act A3 Lgi Iv5 Safetyline 220V EngDocument1 pageAct A3 Lgi Iv5 Safetyline 220V Engoro plataNo ratings yet

- MDDN PDFDocument1 pageMDDN PDFJaime DuranNo ratings yet

- Eurosky Dvb9004-A5 SCH PDFDocument4 pagesEurosky Dvb9004-A5 SCH PDFCarlos RuizNo ratings yet

- TCL Mt55 - Eu - SCH TCL c48p1fs Mt56ct-AP 40-Mt56ee-Mad2hg 40-Mt565sc-Mac2hg - 1Document1 pageTCL Mt55 - Eu - SCH TCL c48p1fs Mt56ct-AP 40-Mt56ee-Mad2hg 40-Mt565sc-Mac2hg - 1Tavi Dumitrescu80% (5)

- 121121212112112telergon IsolatorDocument1 page121121212112112telergon IsolatorSunil SinghNo ratings yet

- Transformer /175W Line Safety Line: MotorDocument1 pageTransformer /175W Line Safety Line: Motororo plataNo ratings yet

- Door Window Detail - A1Document1 pageDoor Window Detail - A1Nikhil KumarNo ratings yet

- Injeção 1.8 8V Sem AbsDocument2 pagesInjeção 1.8 8V Sem AbsLucas Nascimento LopesNo ratings yet

- Esq Nobreak T0726601 Net 4 + 886 SilverblackDocument1 pageEsq Nobreak T0726601 Net 4 + 886 SilverblackGuilherme GelainNo ratings yet

- SMS Nobreak T0726601 Net 4Document1 pageSMS Nobreak T0726601 Net 4Paulo SantanaNo ratings yet

- Esquema Nobreak SMS - T0726601 Net 4 - 886 SilverblackDocument1 pageEsquema Nobreak SMS - T0726601 Net 4 - 886 SilverblackDayamLauthOliveiraNo ratings yet

- Esquema Nobreak SMS Manager Net 4+1400bi 886 Silverblack T0726601Document1 pageEsquema Nobreak SMS Manager Net 4+1400bi 886 Silverblack T0726601Anildo Eldivar De Oliveira SarmentoNo ratings yet

- Profile Weight (KG) : North Direction: MakkahDocument1 pageProfile Weight (KG) : North Direction: MakkahDer3'am Al m7armehNo ratings yet

- 3 - Light Plot - Ladders - Billy Elliot - C01 PDFDocument1 page3 - Light Plot - Ladders - Billy Elliot - C01 PDFMike WoodNo ratings yet

- Wal0079 101 0 PDFDocument1 pageWal0079 101 0 PDFyassir dafallaNo ratings yet

- Act A3 Fujilift Safety Line 220V PDFDocument1 pageAct A3 Fujilift Safety Line 220V PDFGhjNo ratings yet

- C-21051-0012 - CLB ATALANTI - PGL Grillage Foundation On Shelter Deck - Rev01 - 135717944Document1 pageC-21051-0012 - CLB ATALANTI - PGL Grillage Foundation On Shelter Deck - Rev01 - 135717944teopan PanNo ratings yet

- Injeção 1.8 16V Sem AbsDocument2 pagesInjeção 1.8 16V Sem AbsLucas Nascimento LopesNo ratings yet

- Yc01 003 001 (A2)Document1 pageYc01 003 001 (A2)Bach MaiNo ratings yet

- 05 - +GB01 2ha01 Harbour GeneratorDocument13 pages05 - +GB01 2ha01 Harbour GeneratorhamzehNo ratings yet

- 206-Sheet - S 100 C - Excavation Layout-Layout1Document1 page206-Sheet - S 100 C - Excavation Layout-Layout1sameer khanNo ratings yet

- M110 Mech Plan 1Document1 pageM110 Mech Plan 1AlezxNo ratings yet

- Engine Connections: B40i4 Electrical SchematicDocument2 pagesEngine Connections: B40i4 Electrical SchematicChristian BedoyaNo ratings yet

- Panasonic Tnpa4221al PsuDocument7 pagesPanasonic Tnpa4221al PsuwidodoNo ratings yet

- MHW Pid-740-Vu221-Mec-001Document1 pageMHW Pid-740-Vu221-Mec-001Borislav VulicNo ratings yet

- DA42NG Garmin1000 VCDocument1 pageDA42NG Garmin1000 VCLokesh BabuNo ratings yet

- Section B-B Section C-C: 0-8936-2 Golden Triangle Polymers Company LLCDocument1 pageSection B-B Section C-C: 0-8936-2 Golden Triangle Polymers Company LLCLester MuscaNo ratings yet

- 1100x600x130 TDN-1P.C 1100x600x130 TDN-1P.C 1100x600x130 TDN-1P.CDocument1 page1100x600x130 TDN-1P.C 1100x600x130 TDN-1P.C 1100x600x130 TDN-1P.CHipolito MBNo ratings yet

- Dse5510 Diagram PDFDocument1 pageDse5510 Diagram PDFRodrigo ObregonNo ratings yet

- Interland: PD GarbageDocument1 pageInterland: PD GarbageDuy Giáp NguyễnNo ratings yet

- Pefd Baru RevisiDocument1 pagePefd Baru RevisiInnes AzizahNo ratings yet

- Emplazamiento Mercado CampesinoDocument1 pageEmplazamiento Mercado CampesinoAarón Benjazmin Oliva CuevasNo ratings yet

- TC 53 Card Layout DesignDocument1 pageTC 53 Card Layout DesignJ.SathishNo ratings yet

- rt510-rt510rf Brzi VodicDocument2 pagesrt510-rt510rf Brzi VodicAleksandar DekićNo ratings yet

- Crane Ga DrawingDocument1 pageCrane Ga DrawingJitendra Singh50% (2)

- ZX230 270 Eng e PDFDocument1 pageZX230 270 Eng e PDFIksan RadenNo ratings yet

- PLDT Sflu Stair DesignDocument1 pagePLDT Sflu Stair DesignDebussy PanganibanNo ratings yet

- SectionE 47Document1 pageSectionE 47NikNo ratings yet

- SCH V2.0Document1 pageSCH V2.0diegooliveira101010No ratings yet

- Water Tank & Roof FloorDocument17 pagesWater Tank & Roof FloorMahindaNo ratings yet

- Act - LG - Iv5 - Ups - Guvenlik - 220v (2017 - 01 - 12 01 - 33 - 20 UTC)Document1 pageAct - LG - Iv5 - Ups - Guvenlik - 220v (2017 - 01 - 12 01 - 33 - 20 UTC)AhmedNo ratings yet

- Section 1-1: A: Approved Proceed With FabricationDocument1 pageSection 1-1: A: Approved Proceed With FabricationMS MAAHeNo ratings yet

- Tabg Jec 0 000 Pro Pid 0012 - GDocument1 pageTabg Jec 0 000 Pro Pid 0012 - GAfif FadhliNo ratings yet

- SectionE 45Document1 pageSectionE 45NikNo ratings yet

- Entrada CA/Mains Input - 220VCA 2F + PE: Diagrama Elétrico SR - 48V/300ADocument1 pageEntrada CA/Mains Input - 220VCA 2F + PE: Diagrama Elétrico SR - 48V/300AantonioNo ratings yet

- General Elevation PartDocument1 pageGeneral Elevation PartShekh MohammadNo ratings yet

- Praise To The Lord The Almighty - 05 - OboeDocument1 pagePraise To The Lord The Almighty - 05 - OboeMichael DiazNo ratings yet

- Sectores Homogéneos T-1Document12 pagesSectores Homogéneos T-1JAN STEVENS VARGAS CARDONANo ratings yet

- Profile Weight (KG) : North Direction: MakkahDocument1 pageProfile Weight (KG) : North Direction: MakkahDer3'am Al m7armehNo ratings yet

- 2 - VIEW PLAN - Rev 0Document1 page2 - VIEW PLAN - Rev 0Eko YuliantoNo ratings yet

- H033142 Electrico 440Document3 pagesH033142 Electrico 440mario pastranaNo ratings yet

- ACT ACT ACT ACT: TRF 175W Line Safety LineDocument1 pageACT ACT ACT ACT: TRF 175W Line Safety LineShafique AbdiNo ratings yet

- Sergio Layout1Document1 pageSergio Layout1Martin VazquezNo ratings yet

- Field / Campo Remote I/O Cabinet / Gabinete de E/S Remotas: MQ13-02-DR-3210-IN5042 0Document2 pagesField / Campo Remote I/O Cabinet / Gabinete de E/S Remotas: MQ13-02-DR-3210-IN5042 0hugoNo ratings yet

- Ab0321 - 16041-01 - E01-01 Fa5020860, Fa5021860Document2 pagesAb0321 - 16041-01 - E01-01 Fa5020860, Fa5021860Eric DondebzangaNo ratings yet

- Certificate Number: 2777/10366-02/E03-01: Product Reference: DescriptionDocument2 pagesCertificate Number: 2777/10366-02/E03-01: Product Reference: DescriptionEric DondebzangaNo ratings yet

- PowerLogic PM5000 Series - METSEPM5330Document3 pagesPowerLogic PM5000 Series - METSEPM5330Eric DondebzangaNo ratings yet

- Insp n5110 UsDocument7 pagesInsp n5110 UsEric DondebzangaNo ratings yet

- Rsti-Cc-5854Document6 pagesRsti-Cc-5854Eric DondebzangaNo ratings yet

- FT1003Document22 pagesFT1003Eric DondebzangaNo ratings yet

- DS - P6091C P6092 - Brass Square Clamp - Doc205a.VEN Rev1Document1 pageDS - P6091C P6092 - Brass Square Clamp - Doc205a.VEN Rev1Eric DondebzangaNo ratings yet

- Alienware Alienware m15 r7 p109f p109f005 Dell Regulatory and Environmental Datasheet En-UsDocument13 pagesAlienware Alienware m15 r7 p109f p109f005 Dell Regulatory and Environmental Datasheet En-UsEric DondebzangaNo ratings yet

- 487E Test Current Calculator - 13JAN2010Document3 pages487E Test Current Calculator - 13JAN2010Eric Dondebzanga100% (1)

- FT0945Document7 pagesFT0945Eric DondebzangaNo ratings yet

- EN 05SpecSheet C40-55-EU-Kubota Stage 5-EngineDocument6 pagesEN 05SpecSheet C40-55-EU-Kubota Stage 5-EngineEric DondebzangaNo ratings yet

- P14D Enhanced CortecDocument6 pagesP14D Enhanced CortecEric DondebzangaNo ratings yet

- Terex Demag All Terrain Cranes Spec 322404Document22 pagesTerex Demag All Terrain Cranes Spec 322404Eric DondebzangaNo ratings yet

- Awcc Ug 5 X - 2Document28 pagesAwcc Ug 5 X - 2Eric DondebzangaNo ratings yet

- CEWE Prometer: Precision MeteringDocument2 pagesCEWE Prometer: Precision MeteringEric DondebzangaNo ratings yet

- P14N Enhanced CortecDocument5 pagesP14N Enhanced CortecEric DondebzangaNo ratings yet

- International Terms and Conditions: 1. GeneralDocument6 pagesInternational Terms and Conditions: 1. GeneralEric DondebzangaNo ratings yet

- Conversion of The SEL-287V0 Relay Masks To SEL-421-1 Relay Settings Application SpecificDocument3 pagesConversion of The SEL-287V0 Relay Masks To SEL-421-1 Relay Settings Application SpecificEric DondebzangaNo ratings yet

- The Bushing Group - Product SpectrumDocument4 pagesThe Bushing Group - Product SpectrumEric Dondebzanga100% (1)

- Hybrid V V21Document1 pageHybrid V V21Eric DondebzangaNo ratings yet

- CX Series: Dry Insulation: Model CX Up To 72.5 KVDocument4 pagesCX Series: Dry Insulation: Model CX Up To 72.5 KVEric DondebzangaNo ratings yet

- Functions of The Keys: Read This Operating Manual Carefully Observe The Precautions For UseDocument2 pagesFunctions of The Keys: Read This Operating Manual Carefully Observe The Precautions For UseEric DondebzangaNo ratings yet

- C.A 6255 Microhmeter: READ The User Manual Carefully COMPLY The Precautions For UseDocument4 pagesC.A 6255 Microhmeter: READ The User Manual Carefully COMPLY The Precautions For UseEric DondebzangaNo ratings yet

- B Feeder Short-Circuit and Overload ProtectionDocument2 pagesB Feeder Short-Circuit and Overload ProtectionEric DondebzangaNo ratings yet

- Le08301aa 01.PDF Ahr0cdovl2rvy2rpzi5mci5ncnbszwcuy29tl2dlbmvyywwvtuvesufhulavtlatrlqtr1qvteuwodmwmufbltaxlnbkzgDocument4 pagesLe08301aa 01.PDF Ahr0cdovl2rvy2rpzi5mci5ncnbszwcuy29tl2dlbmvyywwvtuvesufhulavtlatrlqtr1qvteuwodmwmufbltaxlnbkzgEric DondebzangaNo ratings yet

- DPT100: Single Phase: Compact, Long Range Site Configurable TransducersDocument4 pagesDPT100: Single Phase: Compact, Long Range Site Configurable TransducersEric DondebzangaNo ratings yet

- Martin Mac 700 ManualDocument48 pagesMartin Mac 700 ManualRhys SiddonsNo ratings yet

- Samsung - rf265 - rf266 - 4Document33 pagesSamsung - rf265 - rf266 - 4ka2uzcNo ratings yet

- Fluke 77 ManualDocument20 pagesFluke 77 Manualhthomas100No ratings yet

- CV-Hardware-Electrical Trainer-HCL TechDocument2 pagesCV-Hardware-Electrical Trainer-HCL TechraveendrareddyeeeNo ratings yet

- Complementary Silicon Power Darlington Transistors: BDW83C BDW84CDocument4 pagesComplementary Silicon Power Darlington Transistors: BDW83C BDW84Cboubker2bessaiNo ratings yet

- Sec 8028Document48 pagesSec 8028Eder LopesNo ratings yet

- Electrical Safety: by Eng. Ahmed SalehDocument42 pagesElectrical Safety: by Eng. Ahmed SalehAbdelaziz RagabNo ratings yet

- Ford Motor Co 5-4L 3v F150 Diagnostics Reference Values PDFDocument3 pagesFord Motor Co 5-4L 3v F150 Diagnostics Reference Values PDFAndrew Porter100% (1)

- BDKDocument4 pagesBDKvivekroy2991No ratings yet

- Air Conditioning Sanyo Service Manual SAP FR99E FTR129EDocument28 pagesAir Conditioning Sanyo Service Manual SAP FR99E FTR129EmdquangNo ratings yet

- Other Members of The Thyristor FamilyDocument7 pagesOther Members of The Thyristor Familynisha sharmsNo ratings yet

- PC5020 V3.2 - Manual Programare PDFDocument46 pagesPC5020 V3.2 - Manual Programare PDFDarie SilviuNo ratings yet

- Inter 140 PDFDocument1 pageInter 140 PDFAman GautamNo ratings yet

- Haf 2015Document11 pagesHaf 2015Muhammad Januar SusantoNo ratings yet

- Application Induction Motor FOR Water Pumping: OF SolarDocument4 pagesApplication Induction Motor FOR Water Pumping: OF Solararadhyula praveenraju yadavNo ratings yet

- Acoustic Image - Combos Series III ManualDocument8 pagesAcoustic Image - Combos Series III ManualazwrazwrNo ratings yet

- Philips 32pfl4509Document92 pagesPhilips 32pfl4509Luis ASCARI LAZOSNo ratings yet

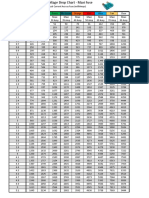

- Fuse Voltage Drop Chart - Maxi FuseDocument2 pagesFuse Voltage Drop Chart - Maxi FuseJose Cespedes88% (8)

- Et200sp Di 8x24vdc HF Manual en-US en-USDocument36 pagesEt200sp Di 8x24vdc HF Manual en-US en-USRafael BrandãoNo ratings yet

- İldam: DF-600 - 600 Liter DF-450 - 450 Liter DF-340 - 340 LiterDocument2 pagesİldam: DF-600 - 600 Liter DF-450 - 450 Liter DF-340 - 340 Literragunatharao0% (1)

- Scorbot-ER III User ManualDocument157 pagesScorbot-ER III User ManualOtto GarciaNo ratings yet

- IC Datasheet FirstDocument13 pagesIC Datasheet FirstSanthoshReddyNo ratings yet

- Dual-Band Omni Antenna Vertical PolarizationDocument1 pageDual-Band Omni Antenna Vertical PolarizationSaif HaiderNo ratings yet

- Ethernet Cable Diagram PDFDocument2 pagesEthernet Cable Diagram PDFCesar0% (1)

- Automatic Irrigation Project SlideDocument18 pagesAutomatic Irrigation Project SlideMd. Rezwanul IslamNo ratings yet

- 1 Magnetic Field Lines Show The Shape and Direction of A Magnetic FieldDocument9 pages1 Magnetic Field Lines Show The Shape and Direction of A Magnetic FieldVenant HakizimanaNo ratings yet

- Conduit Fill RequirementsDocument3 pagesConduit Fill RequirementsManicontrolNo ratings yet

- Updated Simlab ManualDocument46 pagesUpdated Simlab ManualSumanthNo ratings yet

- AR 1215 ManualDocument8 pagesAR 1215 ManualInsam FernandoNo ratings yet

- Mobirad 400 Spec Sheet Sitec 01Document6 pagesMobirad 400 Spec Sheet Sitec 01Edilmaris RinconNo ratings yet