Professional Documents

Culture Documents

MP Interface For A Free-Running A/D Allows Asynchronous Reads

Uploaded by

Beroxi MihaiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MP Interface For A Free-Running A/D Allows Asynchronous Reads

Uploaded by

Beroxi MihaiCopyright:

Available Formats

mP Interface for a Free-Running A/D Allows Asynchronous Reads

National Semiconductor

mP Interface for a Linear Brief 53

Free-Running A/D Allows Tim Regan

July 1981

Asynchronous Reads

In many data acquisition applications it is necessary to have As part of the system power-up initializaton sequence, a

an A to D converter operate as its maximum conversion logic low must be temporarily applied to the SYSTEM

rate. The controlling microprocessor would then be able to RESET input to the A/D to force the converter to start. At

read the most current input data at any point in time as the end of a conversion, the INTR output goes low, and

required by software. To minimize program execution time, both resets the counter outputs to all zeros and signals an-

a DATA READ may not be snychronous to the completion other conversion to start by pulling WR low. The length of

of a conversion, and herein lies a problem. It is entirely pos- time that the INTR output stays low is normally only a few

sible that the processor could assert a READ command internal gate propagation delays (approximately 300 ns) and

right at the instant the A/D converter is updating its output is independent of the A/D clock frequency. The 1000 pF

register. The data read would be the value of the convert- capacitor on this output extends this time to approximately

er’s output lines in transition from the result of the previous 1 ms to insure adequate reset time for the counter.

conversion to the latest result, and would very likely be in A conversion is started on the low to high transition of the

error. INTR and WR pins. The next data update will occur 71 clock

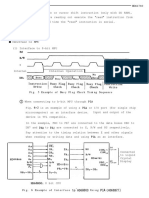

The addition of a simple binary counter to the A/D interface periods after this edge occurs. The counter will signal that a

circuitry can be used to generate a READY signal to the data update is about to occur after 64 clock periods. If the

microprocessor that will prevent a READ during a data up- processor attempts a DATA READ within an 8 clock period

date. The circuit of Figure 1 shows a CD4024BC7-stage rip- time frame around the data update time, its READY input

ple carry binary counter used in conjunction with an line will remain low, signifying a NOT READY condition. The

ADC0801, 8-bit microprocessor compatible A to D convert- processor would then extend the READ cycle time until it

er. Circuit operation relies on two basic properties of the receives a READY indication created by the counter being

A/D converter. First of all, the free-running conversion time reset by INTR. This insures that the latches have already

of the A/D must be a constant number of clock cycles; and been updated and proper data will be read.

secondly, the output latches must be updated prior to the If a READ is attempted during the 64 clock period interval

end of conversion signal. The ADC0801 fulfills both of these after the start of a conversion, the READY IN line to the

requirements. The output data latches are updated one A/D processor will go high to permit a normal READ cycle, and

clock period before the INTR falls low, and the free-running

conversion time is always 72 clock periods long.

Timing Diagram

TL/H/8500 – 1

LB-53

TL/H/8500 – 2

FIGURE 1

C1995 National Semiconductor Corporation TL/H/8500 RRD-B30M115/Printed in U. S. A.

mP Interface for a Free-Running A/D Allows Asynchronous Reads

the data output by the A/D will be the result of the previous The chance of having the processor extend its READ cycle

conversion. The processor READY IN logic, as shown, re- time is 1 in 9 (8 clock periods out of 72) and the maximum

quires that all system devices that may need special READ length of time a READ would be extended is 8 A/D clock

or WRITE timing provide a NOT READY (a Logic 0 on their periods. These two timing considerations are insignificant

READY OUT lines) indication until selected to be read from trade-offs to take to insure that proper A/D data is always

or written to. read.

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or 2. A critical component is any component of a life

systems which, (a) are intended for surgical implant support device or system whose failure to perform can

into the body, or (b) support or sustain life, and whose be reasonably expected to cause the failure of the life

failure to perform, when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can effectiveness.

be reasonably expected to result in a significant injury

to the user.

National Semiconductor National Semiconductor National Semiconductor National Semiconductor

Corporation Europe Hong Kong Ltd. Japan Ltd.

1111 West Bardin Road Fax: (a49) 0-180-530 85 86 13th Floor, Straight Block, Tel: 81-043-299-2309

LB-53

Arlington, TX 76017 Email: cnjwge @ tevm2.nsc.com Ocean Centre, 5 Canton Rd. Fax: 81-043-299-2408

Tel: 1(800) 272-9959 Deutsch Tel: (a49) 0-180-530 85 85 Tsimshatsui, Kowloon

Fax: 1(800) 737-7018 English Tel: (a49) 0-180-532 78 32 Hong Kong

Fran3ais Tel: (a49) 0-180-532 93 58 Tel: (852) 2737-1600

Italiano Tel: (a49) 0-180-534 16 80 Fax: (852) 2736-9960

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

You might also like

- Summit Compressor Control Panel: Prepared By: Coll-Tech Ignition SystemsDocument18 pagesSummit Compressor Control Panel: Prepared By: Coll-Tech Ignition SystemssalehNo ratings yet

- Secure Design Using A Microcontroller (I)Document4 pagesSecure Design Using A Microcontroller (I)Ionela100% (4)

- Bts Brochure Advanced Modular Redundant Technology For Critical Safety and Control SystemsDocument12 pagesBts Brochure Advanced Modular Redundant Technology For Critical Safety and Control SystemsFrancisco Rodriguez G.No ratings yet

- Elec 114Document7 pagesElec 114Egy SimbolonNo ratings yet

- Embedded FirmwareDocument7 pagesEmbedded FirmwareSatya SinhaNo ratings yet

- Automation of Bottle Filling System in Industries Using PLC and ScadaDocument5 pagesAutomation of Bottle Filling System in Industries Using PLC and ScadaVishwa DissanayakeNo ratings yet

- Pacsystems Rx3I Central Processing Unit Ic695Cpe305 Quick Start GuideDocument17 pagesPacsystems Rx3I Central Processing Unit Ic695Cpe305 Quick Start GuideLeandroNo ratings yet

- Research Journal of Pharmaceutical, Biological and Chemical SciencesDocument9 pagesResearch Journal of Pharmaceutical, Biological and Chemical SciencessundarNo ratings yet

- 1.2 Parts of A DAQ SystemDocument37 pages1.2 Parts of A DAQ SystemMaddipati SumanthNo ratings yet

- Gei 100608Document22 pagesGei 100608alaa fadhelNo ratings yet

- Control Sysytems by SuklaDocument51 pagesControl Sysytems by Suklavinay kumar MNo ratings yet

- Mini Project DocumentationDocument43 pagesMini Project Documentationmgitecetech100% (6)

- REM 543 Motor Protection Relay: ApplicationDocument24 pagesREM 543 Motor Protection Relay: ApplicationPrateek SinghNo ratings yet

- Digital RelaysDocument12 pagesDigital RelaysAbdullah Yahya0% (1)

- Unit3 EsdDocument25 pagesUnit3 EsdY19EC2648 JayasreeNo ratings yet

- Embedded Real Time Operating Systems (ECE 367)Document40 pagesEmbedded Real Time Operating Systems (ECE 367)DEVNo ratings yet

- 8259 ADocument16 pages8259 Aapi-26113146100% (1)

- Pedro Soares HP Server Foundation TestDocument22 pagesPedro Soares HP Server Foundation TestPedro Soares50% (4)

- Embedded and Real-Time Operating Systems: Course Code: 70439Document21 pagesEmbedded and Real-Time Operating Systems: Course Code: 70439SrikanthNo ratings yet

- 2.microcontroller Based Transformer Health Monitoring System Using IotDocument38 pages2.microcontroller Based Transformer Health Monitoring System Using IotDinesh KumarNo ratings yet

- MPL User Guide - Oct 2003Document18 pagesMPL User Guide - Oct 2003diazoscurosNo ratings yet

- Tri-GP Technical Product GuideDocument64 pagesTri-GP Technical Product GuideSreekanth Suresh KamathNo ratings yet

- UG SoftMaster 200 V1.7Document740 pagesUG SoftMaster 200 V1.7Lingaraj Suresh LingaianNo ratings yet

- A Smart Sensor Signal Conditioner: Mark I. Schiefer and Michael J. Lally Paul C. EdieDocument7 pagesA Smart Sensor Signal Conditioner: Mark I. Schiefer and Michael J. Lally Paul C. EdieSandy VichuNo ratings yet

- 1746sc-NI8u Manual 0300172 03DDocument130 pages1746sc-NI8u Manual 0300172 03Drfg21100% (1)

- PWM-Inverter Drive Control Operating With A Standard Personal ComputerDocument6 pagesPWM-Inverter Drive Control Operating With A Standard Personal Computeralpha1ahNo ratings yet

- Embedded System DesignDocument163 pagesEmbedded System DesignSUNIL MP100% (4)

- LDSF: Low-Latency Distributed Scheduling Function For Industrial Internet of ThingsDocument12 pagesLDSF: Low-Latency Distributed Scheduling Function For Industrial Internet of ThingsMarco ToledoNo ratings yet

- Unit 5 - Microcontroller & Embedded System - WWW - Rgpvnotes.inDocument7 pagesUnit 5 - Microcontroller & Embedded System - WWW - Rgpvnotes.inDEFENCE MOTIVATIONNo ratings yet

- Mduhm20703a En01Document24 pagesMduhm20703a En01hintetimarwenNo ratings yet

- Quick Start Guide Pacsystems Rx3i Central Processing Unit Ic695cpe305 Quick Start Guide Cpu Embedded Ethernet Emerson en 6295190Document18 pagesQuick Start Guide Pacsystems Rx3i Central Processing Unit Ic695cpe305 Quick Start Guide Cpu Embedded Ethernet Emerson en 6295190Firman DezaNo ratings yet

- Ec8791 - Embedded and Real Time Systems Year / Sem: Iv / 07Document12 pagesEc8791 - Embedded and Real Time Systems Year / Sem: Iv / 07Vinothkumar UrumanNo ratings yet

- Case Study - Designing Protection SystemDocument12 pagesCase Study - Designing Protection SystemAirep OiralihNo ratings yet

- Replacement of Distributed Control System of TG - 4 and Provision of These Parameters On The System Near The Manager Using Networking FacilitiesDocument3 pagesReplacement of Distributed Control System of TG - 4 and Provision of These Parameters On The System Near The Manager Using Networking FacilitiesGunadevan ChandrasekaranNo ratings yet

- Reference Guide: Designdrive Development Kit Iddk V2.2 HardwareDocument29 pagesReference Guide: Designdrive Development Kit Iddk V2.2 HardwareMi HoangNo ratings yet

- Chapter-1: 1.1 Non Real Time Operating SystemsDocument58 pagesChapter-1: 1.1 Non Real Time Operating SystemsAnonymous XybLZfNo ratings yet

- LMTDocument53 pagesLMTneeraj kumarNo ratings yet

- Review of Remote Terminal Unit (RTU) and Gateways For Digital Oilfield DelpoymentsDocument5 pagesReview of Remote Terminal Unit (RTU) and Gateways For Digital Oilfield DelpoymentsHarith FadhilaNo ratings yet

- Active G - Sense Technology 2003Document4 pagesActive G - Sense Technology 2003Morgan James ColmerNo ratings yet

- Functional Design Specification NetworkDocument33 pagesFunctional Design Specification Networkmoch lutfi100% (1)

- VHDL Implementation of Interrupt Controller PDFDocument5 pagesVHDL Implementation of Interrupt Controller PDFKochuzNo ratings yet

- Summa : of or orDocument3 pagesSumma : of or orSantiago BNo ratings yet

- Final Designs of Online Active DAQDocument75 pagesFinal Designs of Online Active DAQAbdul RazzakNo ratings yet

- PLC & SCADA Based Automation of Industrial Reverse OsmosisDocument7 pagesPLC & SCADA Based Automation of Industrial Reverse OsmosisAsim Idrees Osman100% (1)

- Hardware Training Report NEWDocument45 pagesHardware Training Report NEWhr. infotechnogenplNo ratings yet

- Chapter3-Io OrganizationDocument77 pagesChapter3-Io OrganizationPUNITH KUMAR VM100% (1)

- Star DeltaDocument6 pagesStar Deltaa durgadeviNo ratings yet

- An Automated Multi Sensored Green House ManagementDocument4 pagesAn Automated Multi Sensored Green House Managementeditor_ijtelNo ratings yet

- MSD - Ha - Case StudyDocument8 pagesMSD - Ha - Case StudyNIRAJ BHOINo ratings yet

- Multifunction Digital Relays For Generator ProtectionDocument10 pagesMultifunction Digital Relays For Generator Protectionfreddy riveraNo ratings yet

- Handbook On Electronic Interlocking Maintenance Instruction Series I PDFDocument38 pagesHandbook On Electronic Interlocking Maintenance Instruction Series I PDFMatthew Carroll100% (2)

- Chapter 6 - Introduction To An Embedded System and ITs Design - Microcontrollers & Embedded SystemsDocument16 pagesChapter 6 - Introduction To An Embedded System and ITs Design - Microcontrollers & Embedded SystemsAmish VermaNo ratings yet

- 7SR1102-1 Basic ArgusDocument16 pages7SR1102-1 Basic Argusene_platiniNo ratings yet

- Practical, Made Easy Guide To Building, Office And Home Automation Systems - Part OneFrom EverandPractical, Made Easy Guide To Building, Office And Home Automation Systems - Part OneNo ratings yet

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsFrom EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsNo ratings yet

- Practical Data Acquisition for Instrumentation and Control SystemsFrom EverandPractical Data Acquisition for Instrumentation and Control SystemsNo ratings yet

- Digital Filters Digital Filters Digital Filters Digital Filters Digital Filters 55555Document54 pagesDigital Filters Digital Filters Digital Filters Digital Filters Digital Filters 55555Beroxi MihaiNo ratings yet

- One-Dimensional Ffts One-Dimensional Ffts One-Dimensional Ffts One-Dimensional Ffts One-Dimensional Ffts 66666Document9 pagesOne-Dimensional Ffts One-Dimensional Ffts One-Dimensional Ffts One-Dimensional Ffts One-Dimensional Ffts 66666Beroxi MihaiNo ratings yet

- Ai. Pa2 Ais - Os0 at - Rsi PaiDocument10 pagesAi. Pa2 Ais - Os0 at - Rsi PaiBeroxi MihaiNo ratings yet

- One-Dimensional Ffts One-Dimensional Ffts One-Dimensional Ffts One-Dimensional Ffts One-Dimensional FftsDocument12 pagesOne-Dimensional Ffts One-Dimensional Ffts One-Dimensional Ffts One-Dimensional Ffts One-Dimensional FftsBeroxi MihaiNo ratings yet

- E Lab: Design Services OverviewDocument7 pagesE Lab: Design Services OverviewBeroxi MihaiNo ratings yet

- Two-Dimensional Ffts Two-Dimensional Ffts Two-Dimensional Ffts Two-Dimensional Ffts Two-Dimensional FftsDocument32 pagesTwo-Dimensional Ffts Two-Dimensional Ffts Two-Dimensional Ffts Two-Dimensional Ffts Two-Dimensional FftsBeroxi MihaiNo ratings yet

- 386162924chapter 16 PDFDocument8 pages386162924chapter 16 PDFBeroxi MihaiNo ratings yet

- Automatic Video Conference For Grandma With Raspberry Pi: Step 1: Build The UnitDocument16 pagesAutomatic Video Conference For Grandma With Raspberry Pi: Step 1: Build The UnitBeroxi MihaiNo ratings yet

- 1 Interfacing To MpuDocument2 pages1 Interfacing To MpuBeroxi MihaiNo ratings yet

- LCD Module Specification: DMC20481NY-LYDocument15 pagesLCD Module Specification: DMC20481NY-LYBeroxi MihaiNo ratings yet

- Data Acquisition Using INS8048: National Semiconductor Application Note 281 Daniel Hagerty November 1981Document6 pagesData Acquisition Using INS8048: National Semiconductor Application Note 281 Daniel Hagerty November 1981Beroxi MihaiNo ratings yet

- Nokia 6310i EngDocument117 pagesNokia 6310i EngBeroxi MihaiNo ratings yet

- Applying The New CMOS Micro-Dac: National Semiconductor Application Note 271 Tim Regan September 1981Document12 pagesApplying The New CMOS Micro-Dac: National Semiconductor Application Note 271 Tim Regan September 1981Beroxi MihaiNo ratings yet

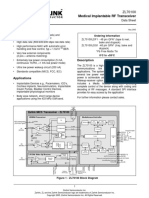

- Features: Medical Implantable RF TransceiverDocument6 pagesFeatures: Medical Implantable RF TransceiverBeroxi MihaiNo ratings yet

- Siem sl55 EngDocument144 pagesSiem sl55 EngBeroxi MihaiNo ratings yet

- MB3793 42 PDFDocument23 pagesMB3793 42 PDFBeroxi MihaiNo ratings yet

- AT5654Document12 pagesAT5654Beroxi MihaiNo ratings yet

- Dual Operational Amplifier: NJM4560D, NJM4560M, NJM4560E NJM4560LDocument5 pagesDual Operational Amplifier: NJM4560D, NJM4560M, NJM4560E NJM4560LBeroxi MihaiNo ratings yet

- Preliminary Product Information 4-Channel BTL Motor Driver Features DescriptionDocument12 pagesPreliminary Product Information 4-Channel BTL Motor Driver Features DescriptionBeroxi MihaiNo ratings yet

- Supported Devices: Serial Configuration (EPCS) Devices DatasheetDocument40 pagesSupported Devices: Serial Configuration (EPCS) Devices DatasheetBeroxi MihaiNo ratings yet

- Low Drop Dual Power Operational Amplifier: DescriptionDocument6 pagesLow Drop Dual Power Operational Amplifier: DescriptionBeroxi MihaiNo ratings yet

- CDCVF2505 3.3-V Clock Phase-Lock Loop Clock Driver: 1 Features 3 DescriptionDocument24 pagesCDCVF2505 3.3-V Clock Phase-Lock Loop Clock Driver: 1 Features 3 DescriptionBeroxi MihaiNo ratings yet

- Ford LaserDocument2 pagesFord LaserJoseMijaresNo ratings yet

- ConverterUnit 56426Document2 pagesConverterUnit 56426Carlo GomezNo ratings yet

- Timing Analysis of Keystrokes and Timing Attacks On SSH - RevisitedDocument19 pagesTiming Analysis of Keystrokes and Timing Attacks On SSH - RevisitedRihards KubilisNo ratings yet

- 2SK2640 PDFDocument3 pages2SK2640 PDFMarko MestrovicNo ratings yet

- The Web-Based Database Management System For The Computer ScienceDocument94 pagesThe Web-Based Database Management System For The Computer ScienceOz GNo ratings yet

- Torque Wrench Calibrator (TWC) Sales LeafletDocument2 pagesTorque Wrench Calibrator (TWC) Sales LeafletPriade SyaputraNo ratings yet

- AsoDocument8 pagesAsoMario KPKNo ratings yet

- EECE 481 Assignment 2022Document3 pagesEECE 481 Assignment 2022SagorNo ratings yet

- Technology Integration-PortfolioDocument2 pagesTechnology Integration-Portfolioapi-403795899No ratings yet

- HUAWEI P40 Pro User Guide - (ELS-N04&NX9, EMUI10.1 - 01, En-Us) PDFDocument213 pagesHUAWEI P40 Pro User Guide - (ELS-N04&NX9, EMUI10.1 - 01, En-Us) PDFMay Thin KhineNo ratings yet

- BW HR AuthorizationDocument20 pagesBW HR AuthorizationKamal RafiNo ratings yet

- Global Positioning System (GPS)Document34 pagesGlobal Positioning System (GPS)Samir2020No ratings yet

- Ex600 Sen1Document75 pagesEx600 Sen1isaias martinezNo ratings yet

- ManojDocument2 pagesManojgarapati anilkumar garapati anilkumarNo ratings yet

- GRPC For WCF DevelopersDocument109 pagesGRPC For WCF Developerschaba dealsNo ratings yet

- SQL OptimizationDocument6 pagesSQL OptimizationjamesNo ratings yet

- Can AnalyzerDocument39 pagesCan Analyzerallaboutanalog100% (1)

- LG l1755s Chassis Lm72aDocument31 pagesLG l1755s Chassis Lm72aEmmanuel Dos santosNo ratings yet

- Series: Model NumberDocument2 pagesSeries: Model Numberrobbi kurniawanNo ratings yet

- Ansible BasicsDocument48 pagesAnsible Basicsshrinath bhat0% (1)

- SOP - MassEdit For NIOS 6.8.6Document12 pagesSOP - MassEdit For NIOS 6.8.6Fahmi YasserNo ratings yet

- 100020326Document34 pages100020326Marko DrobnjakNo ratings yet

- 1 - PAN Terminal Server Agent Install StepsDocument6 pages1 - PAN Terminal Server Agent Install StepsMaciej WaliszkoNo ratings yet

- Learning Typescript FudamentalsDocument43 pagesLearning Typescript FudamentalsHafsa Tufail100% (1)

- QT Appium Course ContentDocument9 pagesQT Appium Course ContentKranti KumarNo ratings yet

- Essential & Practical Circuit AnalysisDocument34 pagesEssential & Practical Circuit AnalysisSubhajit SenguptaNo ratings yet

- Output LogDocument14 pagesOutput LogAndy VictorNo ratings yet

- MM 321 Field ReportDocument15 pagesMM 321 Field ReportSiddhant Vishal Chand0% (1)

- Trimurti Fabricators PVT LTD.: Monsoon Protection PlanDocument4 pagesTrimurti Fabricators PVT LTD.: Monsoon Protection Planalla malikNo ratings yet

- Smart CityDocument16 pagesSmart CityViolet ColorNo ratings yet