Professional Documents

Culture Documents

Quiz2 Soln Fall13 PDF

Quiz2 Soln Fall13 PDF

Uploaded by

bsudheertecOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Quiz2 Soln Fall13 PDF

Quiz2 Soln Fall13 PDF

Uploaded by

bsudheertecCopyright:

Available Formats

CMSC411 Fall 2013 Quiz 2 Solutions

1. (10 pts) Basic pipelining Use the following code fragment:

LW R1, 0(R4) ; R1 ← address (0+R4)

ADDI R2, R1, #8 ; R2 ← R1+8

MULT R3, R1, R1 ; R3 ← R1*R1

SW R3, 4(R2) ; address(4+R2) ← R3

I1→I2 for R1 a. (2 pts) List all RAW (read-after-write) pipeline hazards in the code, regardless of

I1→I3 for R1 whether they cause any stalls. Specify hazards in the form (I3→I5 for R8).

I2→I4 for R2

I3→I4 for R3

Use the classic MIPS five-stage integer pipeline, show the timing of this instruction

sequence. Assume all memory accesses take 1 clock cycle, and a register may be read

and written in the same clock cycle.

b. (2 pts) Assume there is no forwarding or bypassing hardware.

1 2 3 4 5 6 7 8 9 10 11 12 13

I1: LW R1, 0(R4) IF ID EX MEM WB

I2: ADDI R2, R1, #8 IF ST ST ID EX MEM WB

I3: MULT R3, R1, R1 IF ID EX MEM WB

I4: SW R3, 4(R2) IF ST ST ID EX MEM WB

Stalls are needed between both LW/ADDI and MULT/SW due to the RAW pipeline

hazards. Two stalls are needed in each case, to ensure ID stage is executed at same time

as WB stage of previous instruction.

c. (3 pts) Assume normal forwarding and bypassing hardware.

1 2 3 4 5 6 7 8 9 10 11 12 13

I1: LW R1, 0(R4) IF ID EX MEM WB

I2: ADDI R2, R1, #8 IF ST ID EX MEM WB

I3: MULT R3, R1, R1 IF ID EX MEM WB

I4: SW R3, 4(R2) IF ID EX MEM WB

No stalls are needed between DADDI and LD, since forwarding can be used to handle

the RAW pipeline hazard for R1. A stall is needed between LW and ADDI, since the

value for R1 loaded from memory is not available until the end of the MEM stage.

d. (3 pts) Describe all forwarding used in part (c). Use the following format (Im used

EX/MEM→EX from In) to show instruction In forwarded a value from EX/MEM

pipeline register to instruction Im to be used in MEM.

I2 used MEM/WB→EX from I1

I4 used MEM/WB→EX from I2

I4 used MEM/WB→MEM from I3

2. (6 pts) Pipeline hazards. Consider the following MIPS floating point pipeline:

Processors implement logic to check for potential data hazards (such as RAW and

WAW) and forwarding. Recall that the format of MIPS register-register instructions are

rd = rs OP rt, and register immediate instructions (including load/store) are rt = rs OP

immed. Consider the following check:

IF/ID.IR[op] = MUL.D &

A4/MEM.IR[op] = ADD.D &

IF/ID.IR[rt] = A4/MEM.IR[rd]

a. (3 pts) Explain what the logic is checking

Whether the MUL.D instruction is in the IF/ID and ADD.D instruction is in the

A4/MEM pipeline registers, and whether the destination register of the MUL.D

instruction is the same as the operand register of the ADD.D instruction (i.e., whether

RAW hazard exists).

b. (3 pts) Explain whether the check is needed

The check IS needed. If a RAW hazard exists between the MUL.D and the ADD.D

instruction, the value of the MUL.D instruction needs to be forwarded to the EX stage

of the ADD.D instruction, since the MUL.D instruction won’t reach the WB stage until

after the ID stage of the ADD.D instruction has finished.

3. (4 pts) Pipeline performance. Suppose processor X executes instructions in the following

4 stages (no pipeline), where each stages could run this fast. Compare the performance of

a pipelined vs. unpipelined implementation of processor X.

IF&ID 25ns

EX 20ns

a. (2 pts) Compare the performance of a pipelined vs. unpipelined

implementation of processor X. MEM 40ns

WB 15ns

Unpipelined instructions will take 25+20+40+15=100ns.

Pipeline instructions will take (40+40+40+40)/4 = 40ns on average, assuming no stalls.

So performance is improved by 100/40 = 5/2, about 2.5 times.

b. (2 pts) How would the performance of a pipelined implementation of processor X

be affected if every 4th instruction causes a 1 cycle stall?

If a stall occurs every 4th instruction, pipeline instructions will take (40+40+40+40+40)/4

= 50ns on average. Performance compared to pipeline with no stalls would be 40/50 =

4/5, about 0.8 or 80% of the performance with no stalls.

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5811)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- E-Health Care ManagementDocument92 pagesE-Health Care ManagementbsudheertecNo ratings yet

- Cloud Data Lakes For Dummies Snowflake Special Edition V1 4Document10 pagesCloud Data Lakes For Dummies Snowflake Special Edition V1 4CarlosVillamilNo ratings yet

- LANDIS - GYR - DC450 User ManualDocument69 pagesLANDIS - GYR - DC450 User ManualIbrahim SNo ratings yet

- Trends and Research Issues in SOA Validation: January 2011Document23 pagesTrends and Research Issues in SOA Validation: January 2011bsudheertecNo ratings yet

- SequenceData MethodsDocument22 pagesSequenceData MethodsbsudheertecNo ratings yet

- Smart Social Distancing TechniqueDocument86 pagesSmart Social Distancing TechniquebsudheertecNo ratings yet

- CS8261 - C Programming Laboratory - MCQDocument6 pagesCS8261 - C Programming Laboratory - MCQbsudheertecNo ratings yet

- M.E (FT) 2021 Regulation-Ece SyllabusDocument64 pagesM.E (FT) 2021 Regulation-Ece SyllabusbsudheertecNo ratings yet

- SPPM Unit 1Document11 pagesSPPM Unit 1bsudheertecNo ratings yet

- M.E (FT) 2021 Regulation-Cse SyllabusDocument88 pagesM.E (FT) 2021 Regulation-Cse SyllabusbsudheertecNo ratings yet

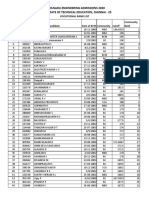

- Tamilnadu Engineering Admissions 2020 Directorate of Technical Education, Chennai - 25Document35 pagesTamilnadu Engineering Admissions 2020 Directorate of Technical Education, Chennai - 25bsudheertecNo ratings yet

- Markov Decision Processes: - The Markov Property - The Markov Decision Process - Partially Observable MdpsDocument24 pagesMarkov Decision Processes: - The Markov Property - The Markov Decision Process - Partially Observable MdpsbsudheertecNo ratings yet

- CS554 - Advanced Database Systems Homework 8: Undo-Log RecordsDocument15 pagesCS554 - Advanced Database Systems Homework 8: Undo-Log RecordsbsudheertecNo ratings yet

- MDP PDFDocument37 pagesMDP PDFbsudheertecNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.bsudheertecNo ratings yet

- Academic Allotments PDFDocument259 pagesAcademic Allotments PDFbsudheertecNo ratings yet

- Deepiris: Iris Recognition Using A Deep Learning ApproachDocument4 pagesDeepiris: Iris Recognition Using A Deep Learning ApproachbsudheertecNo ratings yet

- HW3 Sol PDFDocument44 pagesHW3 Sol PDFbsudheertecNo ratings yet

- ECE 341 Final Exam Solution: Problem No. 1 (10 Points)Document9 pagesECE 341 Final Exam Solution: Problem No. 1 (10 Points)bsudheertecNo ratings yet

- Index PDFDocument19 pagesIndex PDFbsudheertecNo ratings yet

- Waside Graphs PDFDocument4 pagesWaside Graphs PDFbsudheertecNo ratings yet

- Pipeline Review: Here Is The Example Instruction Sequence Used To Illustrate Pipelining On The Previous PageDocument11 pagesPipeline Review: Here Is The Example Instruction Sequence Used To Illustrate Pipelining On The Previous PagebsudheertecNo ratings yet

- I. What Comes Before: Srimathi Sundaravalli Memorial SchoolDocument2 pagesI. What Comes Before: Srimathi Sundaravalli Memorial SchoolbsudheertecNo ratings yet

- Problem Set 4 SolDocument14 pagesProblem Set 4 SolbsudheertecNo ratings yet

- Midterm1 Soln Fall09 PDFDocument6 pagesMidterm1 Soln Fall09 PDFbsudheertecNo ratings yet

- Hazards: CSE378 W, 2001 CSE378 W, 2001Document6 pagesHazards: CSE378 W, 2001 CSE378 W, 2001bsudheertecNo ratings yet

- 45nm Tech FileDocument5 pages45nm Tech FileControl Systems100% (1)

- 06 ChapterDocument279 pages06 ChapterPragya Singh BaghelNo ratings yet

- MeminterfaceececlassDocument9 pagesMeminterfaceececlassNoman AhmedNo ratings yet

- Alcor (Fa00) Aka Au6989sn-Ta - Alcor Au6989sncs-Ta - Alcor (Fa00) + No FidDocument12 pagesAlcor (Fa00) Aka Au6989sn-Ta - Alcor Au6989sncs-Ta - Alcor (Fa00) + No Fidsilberman96301No ratings yet

- Curiosity PIC32MZ EF 2.0 Development Board FeaturesDocument41 pagesCuriosity PIC32MZ EF 2.0 Development Board Featuresguezaki6636No ratings yet

- Bill of Materials For JH. Krautrock Phaser (PCB Mount Components Listed Only.)Document3 pagesBill of Materials For JH. Krautrock Phaser (PCB Mount Components Listed Only.)CristobalzqNo ratings yet

- Computer Science: Chapter: 16 Relatonal DatabaseDocument10 pagesComputer Science: Chapter: 16 Relatonal DatabaseIshika RajputNo ratings yet

- Os Manual Next SemDocument64 pagesOs Manual Next Semswarna_793238588No ratings yet

- MAX1795/MAX1796/ MAX1797 Low-Supply Current, Step-Up DC-DC Converters With True ShutdownDocument13 pagesMAX1795/MAX1796/ MAX1797 Low-Supply Current, Step-Up DC-DC Converters With True ShutdownEletrohelp EletrodomésticosNo ratings yet

- EE305 - Electronics Devices and CircuitsDocument4 pagesEE305 - Electronics Devices and CircuitsBALAKRISHNANNo ratings yet

- New-48v Lifepo4 Battery User ManualDocument19 pagesNew-48v Lifepo4 Battery User Manualhombre pocilgaNo ratings yet

- Williams Raster Monitor Theory & Troubleshooting GuideDocument12 pagesWilliams Raster Monitor Theory & Troubleshooting GuidedustycircuitsboyNo ratings yet

- Part 3: The Medium Access Control Sublayer: More Contents On The Engineering Side of EthernetDocument34 pagesPart 3: The Medium Access Control Sublayer: More Contents On The Engineering Side of Ethernetanon userNo ratings yet

- Basic Structure of Computers: Computer TypesDocument23 pagesBasic Structure of Computers: Computer TypesGahan A V GowdaNo ratings yet

- Viva QuesDocument3 pagesViva Quespoovarasanspoovarasan440No ratings yet

- DatasheetDocument13 pagesDatasheetdanielNo ratings yet

- VLSI Design (Online Lectures) Assignment-1Document3 pagesVLSI Design (Online Lectures) Assignment-1TarushiNo ratings yet

- 8,16,32 Floating Point Processing in ARMDocument25 pages8,16,32 Floating Point Processing in ARMOMKAR BHILARE100% (1)

- Rotograph D InstallationDocument31 pagesRotograph D InstallationVicenteNo ratings yet

- Card Authentication Kit (B) Operation Guide: Print Copy Scan FaxDocument6 pagesCard Authentication Kit (B) Operation Guide: Print Copy Scan FaxcamkornNo ratings yet

- SunLite OTDR+ DatasheetDocument6 pagesSunLite OTDR+ DatasheetjdjimenezNo ratings yet

- 0-60V Dual Variable Power Supply Circuit Using LM317&LM337Document6 pages0-60V Dual Variable Power Supply Circuit Using LM317&LM337Ale AlexNo ratings yet

- Introduction To Vlsi Systems: Historical PerspectiveDocument40 pagesIntroduction To Vlsi Systems: Historical Perspectiveyogesh sharmaNo ratings yet

- MAX8682ETMDocument5 pagesMAX8682ETMmuhammad FikriNo ratings yet

- NareshDocument10 pagesNareshNaresh KumarNo ratings yet

- TMS-374 Programmer Is Supplied byDocument17 pagesTMS-374 Programmer Is Supplied byJefferson Rubio TrujilloNo ratings yet

- Computer Science Coursebook-76-84Document9 pagesComputer Science Coursebook-76-84api-470106119No ratings yet

- Microprocessor: HCMC, 08/2022Document44 pagesMicroprocessor: HCMC, 08/2022loi DuongNo ratings yet