Professional Documents

Culture Documents

LOW POWER VLSI DESIGN July 2017

LOW POWER VLSI DESIGN July 2017

Uploaded by

baburao_kodavatiCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

LOW POWER VLSI DESIGN July 2017

LOW POWER VLSI DESIGN July 2017

Uploaded by

baburao_kodavatiCopyright:

Available Formats

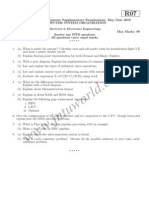

Code No: RT42044C R13 Set No.

1

IV B.Tech II Semester Supplementary Examinations, July/August- 2017

LOW POWER VLSI DESIGN

(Electronics and Communication Engineering)

Time: 3 hours Max. Marks: 70

Question paper consists of Part-A and Part-B

Answer ALL sub questions from Part-A

Answer any THREE questions from Part-B

*****

PART–A (22 Marks)

1. a) Discuss about DIBL [3]

b) Classify the types of multiplier architectures. [3]

c) What is SPICE?. [3]

d) Realize CMOS logic for 1 bit full adder. [4]

e) Write the advantages and disadvantages of MTCMOS circuits. [4]

f) Draw the structure of a six transistor CMOS memory cell. [4]

PART–B (3x16 = 48 Marks)

2. a) Discuss the need of low power VLSI design. [8]

b) What are different types of power dissipation in CMOS circuits and discuss any

three methods in detail. [8]

3. a) Explain the basic concepts of supply voltage scaling. [6]

b) Briefly discuss about pipelining and parallel processing approaches with suitable [10]

examples.

4. Write a notes on

(i) static state power

(ii) gate level capacitance estimation [6+10]

5. Discuss about an 8 bit architecture of CSA and explain with an example. [16]

6. a) What are the building blocks are needed for binary array multiplier and explain [8]

b) Construct Baugh-Wooley Multiplier and explain its operation [8]

7. a) In what way the DRAMs differ from SRAMs? [4]

b) Explain the read and write operations for a one-transistor transistor DRAM cell [12]

1 of 1

||''|''||''||''''''|

You might also like

- Invitation To Computer Science 8th Edition Ebook PDFDocument41 pagesInvitation To Computer Science 8th Edition Ebook PDFerick.stewart39995% (37)

- WCDMA Air Interface Training (Part 5)Document34 pagesWCDMA Air Interface Training (Part 5)Ziya2009No ratings yet

- WWW - Manaresults.co - In: Set No. 1Document1 pageWWW - Manaresults.co - In: Set No. 1HaripriyaNo ratings yet

- WWW - Manaresults.Co - In: Set No. 1Document4 pagesWWW - Manaresults.Co - In: Set No. 1DivyaNo ratings yet

- WWW - Manaresults.Co - In: Set No. 1Document1 pageWWW - Manaresults.Co - In: Set No. 1Rajesh PylaNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document8 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)Adhvay KrishnaNo ratings yet

- WWW - Manaresults.co - In: Digital System Design & Digital Ic ApplicationsDocument1 pageWWW - Manaresults.co - In: Digital System Design & Digital Ic Applicationssailaja kumariNo ratings yet

- 523 BA19 Ad 01Document5 pages523 BA19 Ad 01ramesh1926No ratings yet

- Advanced Computer ArchitectureDocument4 pagesAdvanced Computer ArchitectureSaikumarVavilaNo ratings yet

- WWW - Manaresults.Co - In: Set No. 1Document1 pageWWW - Manaresults.Co - In: Set No. 1surendraloya99No ratings yet

- 9A05704 Advanced Computer ArchitectureDocument4 pages9A05704 Advanced Computer ArchitecturesivabharathamurthyNo ratings yet

- R7310201-Computer System OrganizationDocument4 pagesR7310201-Computer System OrganizationsivabharathamurthyNo ratings yet

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Document2 pagesWWW - Manaresults.Co - In: (Electronics and Communication Engineering)venkiscribd444No ratings yet

- WWW - Manaresults.co - In: Database Management SystemsDocument1 pageWWW - Manaresults.co - In: Database Management SystemsViswanadh JvsNo ratings yet

- r05310201 Computer IonDocument5 pagesr05310201 Computer IonskssushNo ratings yet

- WWW - Manaresults.Co - In: Operating SystemsDocument1 pageWWW - Manaresults.Co - In: Operating SystemsBijayNo ratings yet

- VLSI DESIGN Question Bank: Unit 1Document12 pagesVLSI DESIGN Question Bank: Unit 1Babu GundlapallyNo ratings yet

- WWW - Manaresults.Co - in WWW - Manaresults.Co - In: Set No. 1Document4 pagesWWW - Manaresults.Co - in WWW - Manaresults.Co - In: Set No. 1Sree pujitha DoppalapudiNo ratings yet

- WWW - Manaresults.Co - in WWW - Manaresults.Co - In: Set No. 1Document4 pagesWWW - Manaresults.Co - in WWW - Manaresults.Co - In: Set No. 1Sree pujitha DoppalapudiNo ratings yet

- Data Base Management Systems March 2021Document6 pagesData Base Management Systems March 2021shaik FaizuddinNo ratings yet

- r05320402 Vlsi DesignDocument4 pagesr05320402 Vlsi DesignSRINIVASA RAO GANTANo ratings yet

- WWW - Manaresults.Co - In: Set No. 1Document4 pagesWWW - Manaresults.Co - In: Set No. 1jani28cseNo ratings yet

- SubsystemsDocument1 pageSubsystemsMaheshwar ReddyNo ratings yet

- R7310201-Computer Systems OrganizationDocument1 pageR7310201-Computer Systems OrganizationsudheerkumarakulaNo ratings yet

- B. C. A. (Fifth Semester) EXAMINATION, 2016-17: Note: All Questions Have To Be Attempted. Section-ADocument3 pagesB. C. A. (Fifth Semester) EXAMINATION, 2016-17: Note: All Questions Have To Be Attempted. Section-ARajeev GairolaNo ratings yet

- Mar 17-Cert-CntDocument4 pagesMar 17-Cert-CntmichaelmikealNo ratings yet

- Answer All Questions, Each Carries 3 Marks: Reg No.: - NameDocument2 pagesAnswer All Questions, Each Carries 3 Marks: Reg No.: - NamegjajNo ratings yet

- R7310201 Computer System OrganizationDocument1 pageR7310201 Computer System OrganizationsivabharathamurthyNo ratings yet

- Code No: R05320402Document4 pagesCode No: R05320402chvsrsettiNo ratings yet

- WWW - Manaresults.co - In: Computer NetworksDocument1 pageWWW - Manaresults.co - In: Computer NetworksMurali Krishna ChanapathiNo ratings yet

- Embedded System Design QPsDocument8 pagesEmbedded System Design QPsJ HARSHA YADAVNo ratings yet

- Cad Cam Previous Paper JntukDocument4 pagesCad Cam Previous Paper JntukMD KHALEELNo ratings yet

- WWW - Manaresults.Co - In: Set No. 1Document4 pagesWWW - Manaresults.Co - In: Set No. 1Muneer DasariNo ratings yet

- 07a80506 DistributeddatabasesDocument5 pages07a80506 DistributeddatabasesashivaramakrishnaNo ratings yet

- 1 CS202 Computer Organisation Architecture - Model QPDocument3 pages1 CS202 Computer Organisation Architecture - Model QPjeenaNo ratings yet

- VI Sem Jun-July 2005Document10 pagesVI Sem Jun-July 2005Suraj KumarNo ratings yet

- RT31054112022Document1 pageRT31054112022HúmāyùŋGāzîNo ratings yet

- Dbms Paper 2018Document1 pageDbms Paper 2018Vivek ParmarNo ratings yet

- Vlsi Design: III B. Tech II Semester Regular Examinations, April/May - 2019Document4 pagesVlsi Design: III B. Tech II Semester Regular Examinations, April/May - 2019pawan100% (1)

- Set No. 1Document4 pagesSet No. 1Bhupender RamchandaniNo ratings yet

- r7411001 Vlsi DesignDocument4 pagesr7411001 Vlsi DesignsivabharathamurthyNo ratings yet

- BCN1043 Computer Arc & Org S1 0119Document6 pagesBCN1043 Computer Arc & Org S1 0119m-868020No ratings yet

- WWW - Manaresults.Co - In: Design and Analysis of AlgorithmsDocument1 pageWWW - Manaresults.Co - In: Design and Analysis of AlgorithmsSai DeepthiNo ratings yet

- BE (CSE) DD CT-II QP June 2023Document1 pageBE (CSE) DD CT-II QP June 2023Narendar Reddy MNo ratings yet

- RT 41053112016Document4 pagesRT 41053112016Pratham WakdeNo ratings yet

- Dbms 2021Document2 pagesDbms 2021s14utkarsh2111019No ratings yet

- WWW - Manaresults.Co - In: III B. Tech I Semester Regular Examinations, November-2015 Database Management SystemsDocument4 pagesWWW - Manaresults.Co - In: III B. Tech I Semester Regular Examinations, November-2015 Database Management SystemssnehaNo ratings yet

- Electronic Switching Systems R16 Oct 2019Document4 pagesElectronic Switching Systems R16 Oct 2019yaswanth saiNo ratings yet

- Optical Communication - March 2017Document1 pageOptical Communication - March 2017Sandeep Kumar MekapothulaNo ratings yet

- 44 System Programming CBCS Fresher 2016 17 and OnwardsDocument2 pages44 System Programming CBCS Fresher 2016 17 and Onwardssamir salahNo ratings yet

- B.E. (E&T.C) Computer Networks (404214) (2003 Course) : Total No. of Questions: 12) (Total No. of Pages: 3Document3 pagesB.E. (E&T.C) Computer Networks (404214) (2003 Course) : Total No. of Questions: 12) (Total No. of Pages: 3XXXNo ratings yet

- Ou - 2451 Ou - 2451Document1 pageOu - 2451 Ou - 2451Alaska LalNo ratings yet

- R07 Set No. 2Document4 pagesR07 Set No. 2Naga LakshmiNo ratings yet

- Computer Architecture: CS/B.TECH (CSE-NEW) /SEM-4/CS-403/2012Document8 pagesComputer Architecture: CS/B.TECH (CSE-NEW) /SEM-4/CS-403/2012Avik MitraNo ratings yet

- 07a80402 EmbeddedandrealtimesystemsDocument6 pages07a80402 EmbeddedandrealtimesystemsSharanya ThirichinapalliNo ratings yet

- NotesTracker Guide Version5 1Document1 pageNotesTracker Guide Version5 1Sakshi GuptaNo ratings yet

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiNo ratings yet

- WWW - Manaresults.Co - In: Set No. 1Document4 pagesWWW - Manaresults.Co - In: Set No. 1Harish GollaproluNo ratings yet

- Computer Architecture & Organization: B.E. (Computer Science & Engineering) (New) Third Semester (C.B.S.)Document2 pagesComputer Architecture & Organization: B.E. (Computer Science & Engineering) (New) Third Semester (C.B.S.)Chinmay MokhareNo ratings yet

- Multidisciplinary Design Optimization Supported by Knowledge Based EngineeringFrom EverandMultidisciplinary Design Optimization Supported by Knowledge Based EngineeringNo ratings yet

- ABASTECIMIENTO DE AGUA Y ALCANTARILLADO - A. REGAL Part 2 de 3 PDFDocument40 pagesABASTECIMIENTO DE AGUA Y ALCANTARILLADO - A. REGAL Part 2 de 3 PDFJosé Duncan Miraval BerrospiNo ratings yet

- Graylog-Ubuntu Server 22-04Document5 pagesGraylog-Ubuntu Server 22-04raghda amamiNo ratings yet

- Dell OptiPlex 7010 Spec SheetDocument2 pagesDell OptiPlex 7010 Spec SheetThiago Victor Almeida D'Souza0% (1)

- Digital Forensics Using Data Mining: AbstractDocument13 pagesDigital Forensics Using Data Mining: AbstractTahir HussainNo ratings yet

- ECC800 Data Center Controller V100R002C10 User ManualDocument278 pagesECC800 Data Center Controller V100R002C10 User Manualhadi permanaNo ratings yet

- Query OptimizationDocument30 pagesQuery OptimizationKrishna KumarNo ratings yet

- SO 5600 ReleaseNotesDocument16 pagesSO 5600 ReleaseNotesOem TestNo ratings yet

- Chapter 2 WCDMA RAN Optimization - Accessibility v2Document163 pagesChapter 2 WCDMA RAN Optimization - Accessibility v2Okan IlkerNo ratings yet

- Delta Programmable Logic Controller DVP Series: Automation For A Changing WorldDocument52 pagesDelta Programmable Logic Controller DVP Series: Automation For A Changing Worlddetroja tusharNo ratings yet

- Smart Voice Assistant (7th Sem Project)Document12 pagesSmart Voice Assistant (7th Sem Project)Aniket SharmaNo ratings yet

- Credit Control Configuration: Operation DirectionsDocument27 pagesCredit Control Configuration: Operation DirectionslikameleNo ratings yet

- Flutter With Android IntroductionDocument14 pagesFlutter With Android Introductionusama 7788No ratings yet

- Delhi Govt Scanning OverviewDocument4 pagesDelhi Govt Scanning OverviewmintdollarsNo ratings yet

- Moniplus2 Release 02.03.Xx Global Software Installation and Configuration GuideDocument105 pagesMoniplus2 Release 02.03.Xx Global Software Installation and Configuration GuideRaul David Boucchechter RiveroNo ratings yet

- Label Printing Using Smart FormsDocument9 pagesLabel Printing Using Smart FormsEmil SNo ratings yet

- Samsung NP905S3G ReviewDocument12 pagesSamsung NP905S3G ReviewHigor MaxplanckNo ratings yet

- Cs724 by FarhanDocument18 pagesCs724 by Farhanrhc mongNo ratings yet

- Logic Controller - Modicon M251 - TM251MESEDocument9 pagesLogic Controller - Modicon M251 - TM251MESEjuanbbvNo ratings yet

- Chapter 10 Internetworking DevicesDocument25 pagesChapter 10 Internetworking Deviceshclraj406No ratings yet

- Show Parameters O7 DICTIONARY ACCESSIBILITY Active Instance Count Aq TM Processes Archive Lag Target Asm Diskgroups Asm Diskstring Asm Power Limit Audit File DestDocument6 pagesShow Parameters O7 DICTIONARY ACCESSIBILITY Active Instance Count Aq TM Processes Archive Lag Target Asm Diskgroups Asm Diskstring Asm Power Limit Audit File Destpopo777No ratings yet

- HCSCA107 Operating System OverviewDocument29 pagesHCSCA107 Operating System OverviewJoshua PhiriNo ratings yet

- Online Review 3Document4 pagesOnline Review 3Mandy DuNo ratings yet

- Whitepaper External Sharing With Office 365 September 2016 PDFDocument34 pagesWhitepaper External Sharing With Office 365 September 2016 PDFelisaNo ratings yet

- Computer Studies Junior Secpndary Schemes 2014 CorrectedDocument9 pagesComputer Studies Junior Secpndary Schemes 2014 CorrectedShefat PhiriNo ratings yet

- ROUTE Chapter 1 - CCNP ROUTE (Version 6.0)Document5 pagesROUTE Chapter 1 - CCNP ROUTE (Version 6.0)AS2205100% (7)

- Epson L210 DatasheetDocument2 pagesEpson L210 DatasheetEka S. GunadiNo ratings yet

- How To Select An Analytic DBMS: Overview, Checklists, and TipsDocument39 pagesHow To Select An Analytic DBMS: Overview, Checklists, and TipsjhakanchanjsrNo ratings yet