Professional Documents

Culture Documents

74LVC16245A 74LVCH16245A: 1. General Description

Uploaded by

reza_azadOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

74LVC16245A 74LVCH16245A: 1. General Description

Uploaded by

reza_azadCopyright:

Available Formats

74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

Rev. 12 — 13 February 2012 Product data sheet

1. General description

The 74LVC16245A; 74LVCH16245A are 16-bit transceivers featuring non-inverting

3-state bus compatible outputs in both send and receive directions. The device features

two output enable (nOE) inputs for easy cascading and two send/receive (nDIR) inputs for

direction control. nOE controls the outputs so that the buses are effectively isolated. This

device can be used as two 8-bit transceivers or one 16-bit transceiver.

Inputs can be driven from either 3.3 V or 5 V devices. When disabled, up to 5.5 V can be

applied to the outputs. These features allow the use of these devices in mixed

3.3 V and 5 V applications.

The 74LVCH16245A bus hold on data inputs eliminates the need for external pull-up

resistors to hold unused inputs.

2. Features and benefits

5 V tolerant inputs/outputs for interfacing with 5 V logic

Wide supply voltage range from 1.2 V to 3.6 V

CMOS low power consumption

MULTIBYTE flow-through standard pin-out architecture

Low inductance multiple power and ground pins for minimum noise and ground

bounce

Direct interface with TTL levels

High-impedance when VCC = 0 V

All data inputs have bus hold (74LVCH16245A only)

Complies with JEDEC standard:

JESD8-7A (1.65 V to 1.95 V)

JESD8-5A (2.3 V to 2.7 V)

JESD8-C/JESD36 (2.7 V to 3.6 V)

ESD protection:

HBM JESD22-A114F exceeds 2000 V

MM JESD22-A115-B exceeds 200 V

CDM JESD22-C101E exceeds 1000 V

Specified from 40 C to +85 C and 40 C to +125 C

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

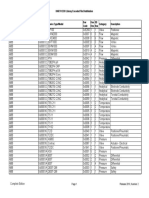

3. Ordering information

Table 1. Ordering information

Type number Temperature range Package

Name Description Version

74LVC16245ADL 40 C to +125 C SSOP48 plastic shrink small outline package; 48 leads; SOT370-1

74LVCH16245ADL body width 7.5 mm

74LVC16245ADGG 40 C to +125 C TSSOP48 plastic thin shrink small outline package; SOT362-1

74LVCH16245ADGG 48 leads; body width 6.1 mm

74LVC16245AEV 40 C to +125 C VFBGA56 plastic very thin fine-pitch ball grid array package; SOT702-1

74LVCH16245AEV 56 balls; body 4.5 7 0.65 mm

74LVC16245ABX 40 C to +125 C HXQFN60 plastic compatible thermal enhanced extremely SOT1134-2

74LVCH16245ABX thin quad flat package; no leads; 60 terminals;

body 4 6 0.5 mm

4. Functional diagram

1DIR 2DIR

1OE 2OE

1A0 2A0

1B0 2B0

1A1 2A1

1B1 2B1

1A2 2A2

1B2 2B2

1A3 2A3

1B3 2B3

1A4 2A4

1B4 2B4

1A5 2A5

1B5 2B5

1A6 2A6

1B6 2B6

1A7 2A7

1B7 2B7

001aaa789

Fig 1. Logic symbol

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 2 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

1OE G3

1DIR 3EN1[BA]

3EN2[AB]

2OE G6

2DIR 6EN1[BA]

6EN2[AB]

1A0 1 1B0

1A1 1B1

1A2 1B2

1A3 1B3

1A4 1B4

1A5 1B5

1A6 1B6

1A7 1B7

2A0 4 2B0

5

2A1 2B1

2A2 2B2

2A3 2B3

2A4 2B4

2A5 2B5

2A6 2B6

2A7 2B7

001aaa790

Fig 2. IEC logic symbol

VCC

data input to internal circuit

mna705

Fig 3. Bus hold circuit

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 3 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

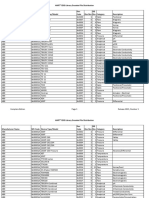

5. Pinning information

5.1 Pinning

74LVC16245A

74LVCH16245A

1DIR 1 48 1OE

1B0 2 47 1A0

1B1 3 46 1A1

GND 4 45 GND

1B2 5 44 1A2

1B3 6 43 1A3

VCC 7 42 VCC

1B4 8 41 1A4

1B5 9 40 1A5

GND 10 39 GND

1B6 11 38 1A6

1B7 12 37 1A7

2B0 13 36 2A0 74LVC16245A

2B1 14 35 2A1 ball A1 74LVCH16245A

index area

GND 15 34 GND 1 2 3 4 5 6

2B2 16 33 2A2

A

2B3 17 32 2A3 B

VCC 18 31 VCC C

D

2B4 19 30 2A4

E

2B5 20 29 2A5 F

GND 21 28 GND G

H

2B6 22 27 2A6

J

2B7 23 26 2A7 K

2DIR 24 25 2OE 001aad111

001aad110 Transparent top view

Fig 4. Pin configuration SOT370-1 (SSOP48) and Fig 5. Pin configuration SOT702-1 (VFBGA56)

SOT362-1 (TSSOP48)

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 4 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

terminal 1

index area

D1 A32 A31 A30 A29 A28 A27 D4

A1 D5 B20 B19 B18 D8 A26

A2 A25

B1 B17

A3 A24

B2 B16

A4 A23

B3 B15

A5 A22

B4 74LVC16245A B14

74LVCH16245A

A6 A21

B5 B13

A7 A20

B6 B12

A8 A19

B7 B11

A9 GND(1) A18

A10 D6 B8 B9 B10 D7 A17

D2 A11 A12 A13 A14 A15 A16 D3

001aai894

Transparent top view

(1) This is not a supply pin. The substrate is attached to this pad using conductive die attach material. There is no electrical or

mechanical requirement to solder this pad. However, if it is soldered, the solder land should remain floating or be connected to

GND.

Fig 6. Pin configuration SOT1134-2 (HXQFN60)

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 5 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

5.2 Pin description

Table 2. Pin description

Symbol Pin Description

SOT370-1 and SOT702-1 SOT1134-2

SOT362-1

1DIR, 2DIR 1, 24 A1, K1 A30, A13 direction control input

1B0 to 1B7 2, 3, 5, 6, 8, 9, 11, B2, B1, C2, C1, D2, D1, B20, A31, D5, D1, A2, data input/output

12 E2, E1 B2, B3, A5

2B0 to 2B7 13, 14, 16, 17, 19, F1, F2, G1, G2, H1, H2, A6, B5, B6, A9, D2, D6, data input/output

20, 22, 23 J1, J2 A12, B8

GND 4, 10, 15, 21, 28, B3, B4, D3, D4, G3, G4, A32, A3, A8, A11, A16, ground (0 V)

34, 39, 45 J3, J4 A19, A24, A27

VCC 7, 18, 31, 42 C3, C4, H3, H4 A1, A10, A17, A26 supply voltage

1OE, 2OE 48, 25 A6, K6 A29, A14 output enable input (active LOW)

1A0 to 1A7 47, 46, 44, 43, 41, B5, B6, C5, C6, D5, D6, B18, A28, D8, D4, A25, data input/output

40, 38, 37 E5, E6 B16, B15, A22

2A0 to 2A7 36, 35, 33, 32, 30, F6, F5, G6, G5, H6, H5, A21, B13, B12, A18, D3, data input/output

29, 27, 26 J6, J5 D7, A15, B10

n.c. - A2, A3, A4, A5, K2, K3, A4, A7, A20, A23, B1, not connected

K4, K5 B4, B7, B9, B11, B14,

B17, B19

6. Functional description

Table 3. Function table[1]

Inputs Outputs

nOE nDIR nAn nBn

L L nAn = nBn inputs

L H inputs nBn = nAn

H X Z Z

[1] H = HIGH voltage level; L = LOW voltage level; X = don’t care; Z = high-impedance OFF-state.

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 6 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

7. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

Symbol Parameter Conditions Min Max Unit

VCC supply voltage 0.5 +6.5 V

IIK input clamping current VI < 0 V 50 - mA

VI input voltage [1] 0.5 +6.5 V

IOK output clamping current VO > VCC or VO < 0 V - 50 mA

VO output voltage output HIGH or LOW [2] 0.5 VCC + 0.5 V

output 3-state [2] 0.5 +6.5 V

IO output current VO = 0 V to VCC - 50 mA

ICC supply current - 100 mA

IGND ground current 100 - mA

Tstg storage temperature 65 +150 C

Ptot total power dissipation Tamb = 40 C to +125 C;

(T)SSOP48 package [3] - 500 mW

VFBGA56 package [4] - 1000 mW

HXQFN60 package [4] - 1000 mW

[1] The minimum input voltage ratings may be exceeded if the input current ratings are observed.

[2] The output voltage ratings may be exceeded if the output current ratings are observed.

[3] Above 60 C the value of Ptot derates linearly with 5.5 mW/K.

[4] Above 70 C the value of Ptot derates linearly with 1.8 mW/K.

8. Recommended operating conditions

Table 5. Recommended operating conditions

Symbol Parameter Conditions Min Typ Max Unit

VCC supply voltage 1.65 - 3.6 V

functional 1.2 - 3.6 V

VI input voltage 0 - 5.5 V

VO output voltage output HIGH or LOW 0 - VCC V

output 3-state 0 - 5.5 V

Tamb ambient temperature in free air 40 - +125 C

t/V input transition rise and fall rate VCC = 1.2 V to 2.7 V 0 - 20 ns/V

VCC = 2.7 V to 3.6 V 0 - 10 ns/V

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 7 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

9. Static characteristics

Table 6. Static characteristics

At recommended operating conditions. Voltages are referenced to GND (ground = 0 V).

Symbol Parameter Conditions 40 C to +85 C 40 C to +125 C Unit

Min Typ[1] Max Min Max

VIH HIGH-level input VCC = 1.2 V 1.08 - - 1.08 - V

voltage VCC = 1.65 V to 1.95 V 0.65 VCC - - 0.65 VCC - V

VCC = 2.3 V to 2.7 V 1.7 - - 1.7 - V

VCC = 2.7 V to 3.6 V 2.0 - - 2.0 - V

VIL LOW-level input VCC = 1.2 V - - 0.12 - 0.12 V

voltage VCC = 1.65 V to 1.95 V - - 0.35 VCC - 0.35 VCC V

VCC = 2.3 V to 2.7 V - - 0.7 - 0.7 V

VCC = 2.7 V to 3.6 V - - 0.8 - 0.8 V

VOH HIGH-level VI = VIH or VIL

output voltage IO = 100 A; VCC 0.2 - - VCC 0.3 - V

VCC = 1.65 V to 3.6 V

IO = 4 mA; VCC = 1.65 V 1.2 - - 1.05 - V

IO = 8 mA; VCC = 2.3 V 1.8 - - 1.65 - V

IO = 12 mA; VCC = 2.7 V 2.2 - - 2.05 - V

IO = 18 mA; VCC = 3.0 V 2.4 - - 2.25 - V

IO = 24 mA; VCC = 3.0 V 2.2 - - 2.0 - V

VOL LOW-level output VI = VIH or VIL

voltage IO = 100 A; - - 0.2 - 0.3 V

VCC = 1.65 V to 3.6 V

IO = 4 mA; VCC = 1.65 V - - 0.45 - 0.65 V

IO = 8 mA; VCC = 2.3 V - - 0.6 - 0.8 V

IO = 12 mA; VCC = 2.7 V - - 0.4 - 0.6 V

IO = 24 mA; VCC = 3.0 V - - 0.55 - 0.8 V

II input leakage VI = 5.5 V or GND; - 0.1 5 - 20 A

current[2] VCC = 3.6 V

IOZ OFF-state output VI = VIH or VIL; - 0.1 5 - 20 A

current[2][3] VO = 5.5 V or GND;

VCC = 3.6 V

IOFF power-off VI or VO = 5.5 V; VCC = 0.0 V - 0.1 10 - 20 A

leakage current

ICC supply current VI = VCC or GND; IO = 0 A; - 0.1 20 - 80 A

VCC = 3.6 V

ICC additional supply per input pin; VI = VCC 0.6 V; - 5 500 - 5000 A

current IO = 0 A; VCC = 2.7 V to 3.6 V

CI input capacitance VCC = 0 V to 3.6 V; - 5.0 - - - pF

VI = GND to VCC

CI/O input/output VCC = 0 V to 3.6 V; - 10 - - - pF

capacitance VI = GND to VCC

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 8 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

Table 6. Static characteristics …continued

At recommended operating conditions. Voltages are referenced to GND (ground = 0 V).

Symbol Parameter Conditions 40 C to +85 C 40 C to +125 C Unit

Min Typ[1] Max Min Max

IBHL bus hold LOW VCC = 1.65; VI = 0.58 V 10 - - 10 - A

current [4][5] VCC = 2.3; VI = 0.7 V 30 - - 25 - A

VCC = 3.0; VI = 0.8 V 75 - - 60 - A

IBHH bus hold HIGH VCC = 1.65; VI = 1.07 V 10 - - 10 - A

current [4][5] VCC = 2.3; VI = 1.7 V 30 - - 25 - A

VCC = 3.0; VI = 2.0 V 75 - - 60 - A

IBHLO bus hold LOW VCC = 1.95 V 200 - - 200 - A

overdrive current V = 2.7 V 300 - - 300 - A

[4][6] CC

VCC = 3.6 V 500 - - 500 - A

IBHHO bus hold HIGH VCC = 1.95 V 200 - - 200 - A

overdrive current V = 2.7 V 300 - - 300 - A

[4][6] CC

VCC = 3.6 V 500 - - 500 - A

[1] All typical values are measured at VCC = 3.3 V (unless stated otherwise) and Tamb = 25 C.

[2] The bus hold circuit is switched off when VI > VCC allowing 5.5 V on the input terminal.

[3] For I/O ports the parameter IOZ includes the input leakage current.

[4] Valid for data inputs of bus hold parts only (74LVCH16245A). Note that control inputs do not have a bus hold circuit.

[5] The specified sustaining current at the data input holds the input below the specified VI level.

[6] The specified overdrive current at the data input forces the data input to the opposite input state.

10. Dynamic characteristics

Table 7. Dynamic characteristics

Voltages are referenced to GND (ground = 0 V). For test circuit see Figure 9.

Symbol Parameter Conditions 40 C to +85 C 40 C to +125 C Unit

Min Typ[2] Max Min Max

tpd propagation nAn to nBn; nBn to nAn; see Figure 7 [1]

delay VCC = 1.2 V - 13.0 - - - ns

VCC = 1.65 V to 1.95 V 1.5 5.2 12.2 1.5 13.8 ns

VCC = 2.3 V to 2.7 V 1.0 2.8 6.0 1.0 6.7 ns

VCC = 2.7 V 1.0 2.7 4.7 1.0 6.0 ns

VCC = 3.0 V to 3.6 V 1.0 2.4 4.5 1.0 6.0 ns

ten enable time nOE to nAn, nBn; see Figure 8 [1]

VCC = 1.2 V - 15.0 - - - ns

VCC = 1.65 V to 1.95 V 1.5 5.9 15.0 1.5 16.9 ns

VCC = 2.3 V to 2.7 V 1.0 3.3 7.9 1.0 8.8 ns

VCC = 2.7 V 1.5 3.5 6.7 1.5 8.5 ns

VCC = 3.0 V to 3.6 V 1.0 2.7 5.5 1.0 7.0 ns

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 9 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

Table 7. Dynamic characteristics …continued

Voltages are referenced to GND (ground = 0 V). For test circuit see Figure 9.

Symbol Parameter Conditions 40 C to +85 C 40 C to +125 C Unit

Min Typ[2] Max Min Max

tdis disable time nOE to nAn, nBn; see Figure 8 [1]

VCC = 1.2 V - 11.0 - - - ns

VCC = 1.65 V to 1.95 V 1.0 4.9 13.1 1.0 14.7 ns

VCC = 2.3 V to 2.7 V 0.5 2.7 7.1 0.5 7.9 ns

VCC = 2.7 V 1.5 3.4 6.6 1.5 8.5 ns

VCC = 3.0 V to 3.6 V 1.5 3.3 5.6 1.5 7.0 ns

CPD power per input; VI = GND to VCC [3]

dissipation VCC = 1.65 V to 1.95 V - 11.5 - - - pF

capacitance

VCC = 2.3 V to 2.7 V - 15.2 - - - pF

VCC = 3.0 V to 3.6 V - 18.5 - - - pF

[1] tpd is the same as tPLH and tPHL.

ten is the same as tPZL and tPZH.

tdis is the same as tPLZ and tPHZ.

[2] Typical values are measured at Tamb = 25 C and VCC = 1.2 V, 1.8 V, 2.5 V, 2.7 V and 3.3 V respectively.

[3] CPD is used to determine the dynamic power dissipation (PD in W).

PD = CPD VCC2 fi N + (CL VCC2 fo) where:

fi = input frequency in MHz; fo = output frequency in MHz

CL = output load capacitance in pF

VCC = supply voltage in Volts

N = number of inputs switching

(CL VCC2 fo) = sum of the outputs.

11. Waveforms

VI

nAn, nBn

VM

input

GND

t PHL t PLH

VOH

nBn, nAn

output VM

VOL mna477

Measurement points are given in Table 8.

Logic levels: VOL and VOH are typical output voltage levels that occur with the output load.

Fig 7. The input (nAn, nBn) to output (nBn, nAn) propagation delays

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 10 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

VI

nOE input VM

GND

tPLZ tPZL

VCC

output

LOW-to-OFF VM

OFF-to-LOW

VX

VOL

tPHZ tPZH

VOH

VY

output

HIGH-to-OFF VM

OFF-to-HIGH

GND

outputs outputs outputs

enabled disabled enabled

mna362

Measurement points are given in Table 8.

Logic levels: VOL and VOH are typical output voltage levels that occur with the output load.

Fig 8. 3-state enable and disable times

Table 8. Measurement points

Supply voltage VM Input

VCC VI tr = tf VX VY

1.2 V 0.5 VCC VCC 2.5 ns VOL + 0.15 V VOH 0.15 V

1.65 V to 1.95 V 0.5 VCC VCC 2.5 ns VOL + 0.15 V VOH 0.15 V

2.3 V to 2.7 V 0.5 VCC VCC 2.5 ns VOL + 0.15 V VOH 0.15 V

2.7 V 1.5 V 2.7 V 2.5 ns VOL + 0.3 V VOH 0.3 V

3.0 V to 3.6 V 1.5 V 2.7 V 2.5 ns VOL + 0.3 V VOH 0.3 V

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 11 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

tW

VI

90 %

negative

pulse VM VM

10 %

0V

tf tr

tr tf

VI

90 %

positive

pulse VM VM

10 %

0V

tW

VEXT

VCC

RL

VI VO

G DUT

RT CL RL

001aae331

Test data is given in Table 9.

Definitions for test circuit:

RL = Load resistance.

CL = Load capacitance including jig and probe capacitance.

RT = Termination resistance should be equal to output impedance Zo of the pulse generator.

VEXT = External voltage for measuring switching times.

Fig 9. Test circuit for measuring switching times

Table 9. Test data

Supply voltage Input Load VEXT

VI tr, tf CL RL tPLH, tPHL tPLZ, tPZL tPHZ, tPZH

1.2 V VCC 2 ns 30 pF 1 k open 2 VCC GND

1.65 V to 1.95 V VCC 2 ns 30 pF 1 k open 2 VCC GND

2.3 V to 2.7 V VCC 2 ns 30 pF 500 open 2 VCC GND

2.7 V 2.7 V 2.5 ns 50 pF 500 open 2 VCC GND

3.0 V to 3.6 V 2.7 V 2.5 ns 50 pF 500 open 2 VCC GND

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 12 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

12. Package outline

SSOP48: plastic shrink small outline package; 48 leads; body width 7.5 mm SOT370-1

D E A

X

y HE v M A

48 25

Q

A2

A1 A

(A 3)

pin 1 index θ

Lp

L

1 24

w M detail X

e bp

0 5 10 mm

scale

DIMENSIONS (mm are the original dimensions)

A

UNIT A1 A2 A3 bp c D (1) E (1) e HE L Lp Q v w y Z (1) θ

max.

mm 2.8

0.4 2.35 0.3 0.22 16.00 7.6 10.4 1.0 1.2 0.85 8o

0.25 0.635 1.4 0.25 0.18 0.1 o

0.2 2.20 0.2 0.13 15.75 7.4 10.1 0.6 1.0 0.40 0

Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC JEITA PROJECTION

99-12-27

SOT370-1 MO-118

03-02-19

Fig 10. Package outline SOT370-1 (SSOP48)

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 13 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

TSSOP48: plastic thin shrink small outline package; 48 leads; body width 6.1 mm SOT362-1

D E A

X

y HE v M A

48 25

Q

A2 (A 3) A

A1

pin 1 index

θ

Lp

L

1 24 detail X

w M

e bp

0 2.5 5 mm

scale

DIMENSIONS (mm are the original dimensions).

A

UNIT A1 A2 A3 bp c D (1) E (2) e HE L Lp Q v w y Z θ

max.

mm 1.2

0.15 1.05 0.28 0.2 12.6 6.2 8.3 0.8 0.50 0.8 8o

0.25 0.5 1 0.25 0.08 0.1 o

0.05 0.85 0.17 0.1 12.4 6.0 7.9 0.4 0.35 0.4 0

Notes

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC JEITA PROJECTION

99-12-27

SOT362-1 MO-153

03-02-19

Fig 11. Package outline SOT362-1 (TSSOP48)

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 14 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

VFBGA56: plastic very thin fine-pitch ball grid array package; 56 balls; body 4.5 x 7 x 0.65 mm SOT702-1

D B A

ball A1

index area

A2

A

E

A1

detail X

e1

C

∅v M C A B

e b

∅w M C y1 C y

1/2 e

K

J

H

e

G

F

e2

E

D 1/2 e

C X

B

A

ball A1

index area 1 2 3 4 5 6

DIMENSIONS (mm are the original dimensions)

A

UNIT A1 A2 b D E e e1 e2 v w y y1 0 2.5 5 mm

max.

mm 1 0.3 0.7 0.45 4.6 7.1 scale

0.65 3.25 5.85 0.15 0.08 0.08 0.1

0.2 0.6 0.35 4.4 6.9

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC JEITA PROJECTION

02-08-08

SOT702-1 MO-225

03-07-01

Fig 12. Package outline SOT702-1 (VFBGA56)

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 15 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

HXQFN60: plastic compatible thermal enhanced extremely thin quad flat package; no leads;

60 terminals; body 4 x 6 x 0.5 mm SOT1134-2

D B A

terminal 1

index area

A A2

E

A1

detail X

e2

b v C A B

w C

e1

eR

v C A B e

eT C

w C 1/2 e

L1 y1 C y

D2 A11 A16 D3

D6 B8 B10 D7

L A10 A17

e

eR eT B11

B7

Eh

e3 e4

1/2 e

B1 B17

A1 A26

terminal 1

index area

D5 B20 B18 D8

eT eR

D1 A32 Dh A27 D4 X

eT K

eR

0 5 mm

Dimensions

Unit A A1 A2 b D Dh E Eh e e1 e2 e3 e4 eR eT K L L1 v w y y1

max 0.50 0.08 0.42 0.28 4.1 1.95 6.1 3.95 0.25 0.28 0.195

mm nom 0.05 0.40 0.23 4.0 1.85 6.0 3.85 0.5 1.0 2.5 3.0 4.5 0.5 0.49 0.20 0.23 0.145 0.1 0.05 0.08 0.1

min 0.02 0.38 0.18 3.9 1.75 5.9 3.75 0.15 0.18 0.095

sot1134-2_po

Outline References European

Issue date

version IEC JEDEC JEITA projection

SOT1134-2 --- --- --- 11-08-15

Fig 13. Package outline SOT1134-2 (HXQFN60)

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 16 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

13. Abbreviations

Table 10. Abbreviations

Acronym Description

CDM Charged Device Model

DUT Device Under Test

ESD ElectroStatic Discharge

HBM Human Body Model

MM Machine Model

TTL Transistor-Transistor Logic

14. Revision history

Table 11. Revision history

Document ID Release date Data sheet status Change notice Supersedes

74LVC_LVCH16245A v.12 20120213 Product data sheet - 74LVC_LVCH16245A v.11

Modifications: • For type number 74LVC16245ABX and 74LVCH16245ABX the sot code has changed to

SOT1134-2.

74LVC_LVCH16245A v.11 20111208 Product data sheet - 74LVC_LVCH16245A v.10

Modifications: • Table 4, Table 5, Table 6, Table 7, and Table 9: values added for lower voltage ranges.

74LVC_LVCH16245A v.10 20110623 Product data sheet - 74LVC_LVCH16245A v.9

Modifications: • type numbers 74LVC16245ABQ and 74LVCH16245ABQ changed to 74LVC16245ABX

and 74LVCH16245ABX.

• Figure 6: figure note 1 changed.

74LVC_LVCH16245A v.9 20100329 Product data sheet - 74LVC_LVCH16245A v.8

74LVC_LVCH16245A v.8 20081106 Product data sheet - 74LVC_LVCH16245A v.7

74LVC_LVCH16245A v.7 20031125 Product specification - 74LVC_LVCH16245A v.6

74LVC_LVCH16245A v.6 20030130 Product specification - 74LVC_LVCH16245A v.5

74LVC_LVCH16245A v.5 20021030 Product specification - 74LVC_H16245A v.4

74LVC_H16245A v.4 19970925 Product specification - 74LVC16245A_

74LVCH16245A v.3

74LVC16245A_ 19970925 Product specification - 74LVC16245A v.2

74LVCH16245A v.3

74LVC16245A v.2 19970801 Product specification - 74LVC16245A v.1

74LVC16245A v.1 - - - -

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 17 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

15. Legal information

15.1 Data sheet status

Document status[1][2] Product status[3] Definition

Objective [short] data sheet Development This document contains data from the objective specification for product development.

Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.

Product [short] data sheet Production This document contains the product specification.

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term ‘short data sheet’ is explained in section “Definitions”.

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status

information is available on the Internet at URL http://www.nxp.com.

15.2 Definitions Suitability for use — NXP Semiconductors products are not designed,

authorized or warranted to be suitable for use in life support, life-critical or

safety-critical systems or equipment, nor in applications where failure or

Draft — The document is a draft version only. The content is still under

malfunction of an NXP Semiconductors product can reasonably be expected

internal review and subject to formal approval, which may result in

to result in personal injury, death or severe property or environmental

modifications or additions. NXP Semiconductors does not give any

damage. NXP Semiconductors and its suppliers accept no liability for

representations or warranties as to the accuracy or completeness of

inclusion and/or use of NXP Semiconductors products in such equipment or

information included herein and shall have no liability for the consequences of

applications and therefore such inclusion and/or use is at the customer’s own

use of such information.

risk.

Short data sheet — A short data sheet is an extract from a full data sheet

Applications — Applications that are described herein for any of these

with the same product type number(s) and title. A short data sheet is intended

products are for illustrative purposes only. NXP Semiconductors makes no

for quick reference only and should not be relied upon to contain detailed and

representation or warranty that such applications will be suitable for the

full information. For detailed and full information see the relevant full data

specified use without further testing or modification.

sheet, which is available on request via the local NXP Semiconductors sales

office. In case of any inconsistency or conflict with the short data sheet, the Customers are responsible for the design and operation of their applications

full data sheet shall prevail. and products using NXP Semiconductors products, and NXP Semiconductors

accepts no liability for any assistance with applications or customer product

Product specification — The information and data provided in a Product design. It is customer’s sole responsibility to determine whether the NXP

data sheet shall define the specification of the product as agreed between Semiconductors product is suitable and fit for the customer’s applications and

NXP Semiconductors and its customer, unless NXP Semiconductors and products planned, as well as for the planned application and use of

customer have explicitly agreed otherwise in writing. In no event however, customer’s third party customer(s). Customers should provide appropriate

shall an agreement be valid in which the NXP Semiconductors product is design and operating safeguards to minimize the risks associated with their

deemed to offer functions and qualities beyond those described in the applications and products.

Product data sheet.

NXP Semiconductors does not accept any liability related to any default,

damage, costs or problem which is based on any weakness or default in the

15.3 Disclaimers customer’s applications or products, or the application or use by customer’s

third party customer(s). Customer is responsible for doing all necessary

testing for the customer’s applications and products using NXP

Limited warranty and liability — Information in this document is believed to

Semiconductors products in order to avoid a default of the applications and

be accurate and reliable. However, NXP Semiconductors does not give any

the products or of the application or use by customer’s third party

representations or warranties, expressed or implied, as to the accuracy or

customer(s). NXP does not accept any liability in this respect.

completeness of such information and shall have no liability for the

consequences of use of such information. NXP Semiconductors takes no Limiting values — Stress above one or more limiting values (as defined in

responsibility for the content in this document if provided by an information the Absolute Maximum Ratings System of IEC 60134) will cause permanent

source outside of NXP Semiconductors. damage to the device. Limiting values are stress ratings only and (proper)

operation of the device at these or any other conditions above those given in

In no event shall NXP Semiconductors be liable for any indirect, incidental,

the Recommended operating conditions section (if present) or the

punitive, special or consequential damages (including - without limitation - lost

Characteristics sections of this document is not warranted. Constant or

profits, lost savings, business interruption, costs related to the removal or

repeated exposure to limiting values will permanently and irreversibly affect

replacement of any products or rework charges) whether or not such

the quality and reliability of the device.

damages are based on tort (including negligence), warranty, breach of

contract or any other legal theory. Terms and conditions of commercial sale — NXP Semiconductors

Notwithstanding any damages that customer might incur for any reason products are sold subject to the general terms and conditions of commercial

whatsoever, NXP Semiconductors’ aggregate and cumulative liability towards sale, as published at http://www.nxp.com/profile/terms, unless otherwise

customer for the products described herein shall be limited in accordance agreed in a valid written individual agreement. In case an individual

with the Terms and conditions of commercial sale of NXP Semiconductors. agreement is concluded only the terms and conditions of the respective

agreement shall apply. NXP Semiconductors hereby expressly objects to

Right to make changes — NXP Semiconductors reserves the right to make applying the customer’s general terms and conditions with regard to the

changes to information published in this document, including without purchase of NXP Semiconductors products by customer.

limitation specifications and product descriptions, at any time and without

notice. This document supersedes and replaces all information supplied prior No offer to sell or license — Nothing in this document may be interpreted or

to the publication hereof. construed as an offer to sell products that is open for acceptance or the grant,

conveyance or implication of any license under any copyrights, patents or

other industrial or intellectual property rights.

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 18 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

Export control — This document as well as the item(s) described herein NXP Semiconductors’ specifications such use shall be solely at customer’s

may be subject to export control regulations. Export might require a prior own risk, and (c) customer fully indemnifies NXP Semiconductors for any

authorization from competent authorities. liability, damages or failed product claims resulting from customer design and

use of the product for automotive applications beyond NXP Semiconductors’

Non-automotive qualified products — Unless this data sheet expressly

standard warranty and NXP Semiconductors’ product specifications.

states that this specific NXP Semiconductors product is automotive qualified,

the product is not suitable for automotive use. It is neither qualified nor tested Translations — A non-English (translated) version of a document is for

in accordance with automotive testing or application requirements. NXP reference only. The English version shall prevail in case of any discrepancy

Semiconductors accepts no liability for inclusion and/or use of between the translated and English versions.

non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in

automotive applications to automotive specifications and standards, customer 15.4 Trademarks

(a) shall use the product without NXP Semiconductors’ warranty of the

Notice: All referenced brands, product names, service names and trademarks

product for such automotive applications, use and specifications, and (b)

are the property of their respective owners.

whenever customer uses the product for automotive applications beyond

16. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

74LVC_LVCH16245A All information provided in this document is subject to legal disclaimers. © NXP B.V. 2012. All rights reserved.

Product data sheet Rev. 12 — 13 February 2012 19 of 20

NXP Semiconductors 74LVC16245A; 74LVCH16245A

16-bit bus transceiver with direction pin; 5 V tolerant; 3-state

17. Contents

1 General description . . . . . . . . . . . . . . . . . . . . . . 1

2 Features and benefits . . . . . . . . . . . . . . . . . . . . 1

3 Ordering information . . . . . . . . . . . . . . . . . . . . . 2

4 Functional diagram . . . . . . . . . . . . . . . . . . . . . . 2

5 Pinning information . . . . . . . . . . . . . . . . . . . . . . 4

5.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

5.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 6

6 Functional description . . . . . . . . . . . . . . . . . . . 6

7 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 7

8 Recommended operating conditions. . . . . . . . 7

9 Static characteristics. . . . . . . . . . . . . . . . . . . . . 8

10 Dynamic characteristics . . . . . . . . . . . . . . . . . . 9

11 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

12 Package outline . . . . . . . . . . . . . . . . . . . . . . . . 13

13 Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . 17

14 Revision history . . . . . . . . . . . . . . . . . . . . . . . . 17

15 Legal information. . . . . . . . . . . . . . . . . . . . . . . 18

15.1 Data sheet status . . . . . . . . . . . . . . . . . . . . . . 18

15.2 Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

15.3 Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

15.4 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 19

16 Contact information. . . . . . . . . . . . . . . . . . . . . 19

17 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Please be aware that important notices concerning this document and the product(s)

described herein, have been included in section ‘Legal information’.

© NXP B.V. 2012. All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 13 February 2012

Document identifier: 74LVC_LVCH16245A

Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

NXP:

74LVC16245ADGG,112 74LVC16245ADGG,118 74LVCH16245ADGG,11 74LVCH16245ADGG:11

74LVCH16245ABX,518 74LVC16245ADGG,512 74LVC16245ADGG,518 74LVC16245ADL,112

74LVC16245ADL,118 74LVC16245AEV,157 74LVC16245AEV/G:55 74LVC16245AEV/G,55 74LVC16245AEV/G,51

74LVC16245AEV,151 74LVC16245AEV,118 74LVCH16245ADGG,51 74LVCH16245ADGG:51

74LVCH16245ADL,112 74LVCH16245ADL,118 74LVCH16245AEV,157 74LVCH16245AEV/G,5

74LVCH16245AEV/G:5 74LVCH16245AEV/G;5 74LVCH16245AEV,151 74LVCH16245AEV,118 74LVC16245AEVE

74LVC16245AEVK 74LVCH16245AEV,551 74LVCH16245AEVK 74LVCH16245AEVY

You might also like

- 74LVC Lvch244a-51459 PDFDocument20 pages74LVC Lvch244a-51459 PDFSaikumarNo ratings yet

- 74HC240 74HCT240: 1. General DescriptionDocument14 pages74HC240 74HCT240: 1. General DescriptionCarlos ReisNo ratings yet

- Description Features: 24-Bit Bus SwitchDocument4 pagesDescription Features: 24-Bit Bus SwitchspotNo ratings yet

- 74HC240 74HCT240: 1. General DescriptionDocument15 pages74HC240 74HCT240: 1. General DescriptionnappiNo ratings yet

- General Description: Dual 4-Input AND GateDocument11 pagesGeneral Description: Dual 4-Input AND GateSandeep SNo ratings yet

- TC74VHC240F, TC74VHC240FK TC74VHC244F, TC74VHC244FKDocument10 pagesTC74VHC240F, TC74VHC240FK TC74VHC244F, TC74VHC244FKFábio Vitor MartinsNo ratings yet

- Hoyea - FWDocument5 pagesHoyea - FWJoel PalaciosNo ratings yet

- HEF4093BDocument12 pagesHEF4093Bbd4ukyNo ratings yet

- CBT3257 DatasheetDocument11 pagesCBT3257 Datasheetfibbo2012No ratings yet

- Am 26 LV 32Document28 pagesAm 26 LV 32Sapta NugrahaNo ratings yet

- Octal Buffer/line Driver 3-State 74LVC244: Amb R FDocument8 pagesOctal Buffer/line Driver 3-State 74LVC244: Amb R FMzsenna Opcional MzsennaNo ratings yet

- 74HC4075 74HCT4075: 1. General DescriptionDocument11 pages74HC4075 74HCT4075: 1. General DescriptionAeylla ZeoraineNo ratings yet

- D D D D D D D: SN54HC244, SN74HC244 Octal Buffers and Line Drivers With 3-State OutputsDocument16 pagesD D D D D D D: SN54HC244, SN74HC244 Octal Buffers and Line Drivers With 3-State Outputsรัตนชัย บัวจํารัสNo ratings yet

- HEF4071B: 1. General DescriptionDocument11 pagesHEF4071B: 1. General DescriptionElectronicos CaldasNo ratings yet

- SN74AVC4 DatasheetDocument19 pagesSN74AVC4 Datasheetzigmund zigmundNo ratings yet

- 74HC HCT366Document17 pages74HC HCT366Juciêr AlcântaraNo ratings yet

- 74HC HCT240Document22 pages74HC HCT240Драгиша Небитни ТрифуновићNo ratings yet

- HEF4081BDocument9 pagesHEF4081BGerman PascucciNo ratings yet

- General Description: Quad 2-Input AND GateDocument10 pagesGeneral Description: Quad 2-Input AND Gateblackslash82No ratings yet

- 54 Ac 164245Document24 pages54 Ac 164245Saurabh TandanNo ratings yet

- HEF4071BDocument9 pagesHEF4071Bkopii0548No ratings yet

- 74AUP1G3208 PhilipsSemiconductorsDocument16 pages74AUP1G3208 PhilipsSemiconductorsCer CerNo ratings yet

- 74AHC08 74AHCT08: 1. General DescriptionDocument14 pages74AHC08 74AHCT08: 1. General Descriptionteranet tbtNo ratings yet

- HEF4001BDocument9 pagesHEF4001BRakeem BernardNo ratings yet

- Hef4001b 2938071Document10 pagesHef4001b 2938071Amit Kumar BasuNo ratings yet

- 74HC HCT04Document13 pages74HC HCT04cooldudepNo ratings yet

- Po54G02A, Po74G02A: 54, 74 Series Noise Cancellation GHZ LogicDocument6 pagesPo54G02A, Po74G02A: 54, 74 Series Noise Cancellation GHZ LogicspotNo ratings yet

- 74AHC08 74AHCT08: 1. General DescriptionDocument14 pages74AHC08 74AHCT08: 1. General DescriptionalexNo ratings yet

- 74AHC08 74AHCT08: 1. General DescriptionDocument14 pages74AHC08 74AHCT08: 1. General DescriptionalexNo ratings yet

- 74LVC245A 74LVCH245A: 1. General DescriptionDocument17 pages74LVC245A 74LVCH245A: 1. General DescriptionsmnguyenNo ratings yet

- 74HC132 74HCT132: 1 General DescriptionDocument18 pages74HC132 74HCT132: 1 General DescriptionSantiago RodríguezNo ratings yet

- Detergent Spare Parts FinalDocument9 pagesDetergent Spare Parts FinalMd HossainNo ratings yet

- 74HC02 74HCT02: 1. General DescriptionDocument16 pages74HC02 74HCT02: 1. General DescriptionmohamadziNo ratings yet

- 74lvc07apw q100j BufferDocument14 pages74lvc07apw q100j BuffersatyamNo ratings yet

- 74HC HCT00Document12 pages74HC HCT00Ghenia MakhloufNo ratings yet

- HEF4049BDocument12 pagesHEF4049BchrisNo ratings yet

- 74LVC2G14Document17 pages74LVC2G14IvanNo ratings yet

- Philips Semiconductors TDA5144 Brushless DC Motor Drive Circuit SpecDocument17 pagesPhilips Semiconductors TDA5144 Brushless DC Motor Drive Circuit SpecCarlos NavarroNo ratings yet

- Philips Semiconductors TDA5144 Brushless DC Motor Drive Circuit SpecDocument17 pagesPhilips Semiconductors TDA5144 Brushless DC Motor Drive Circuit SpecJairoNo ratings yet

- 74LVC245A 74LVCH245A: 1. General DescriptionDocument17 pages74LVC245A 74LVCH245A: 1. General DescriptionDarleiDuarteNo ratings yet

- HEF4050B: 1. General DescriptionDocument12 pagesHEF4050B: 1. General DescriptionTamas VorosNo ratings yet

- HEF4093B: 1. General DescriptionDocument14 pagesHEF4093B: 1. General Descriptionpre freedaNo ratings yet

- 74HCU04Document14 pages74HCU04Javier De La RosaNo ratings yet

- 74HC245 74HCT245: 1. General DescriptionDocument16 pages74HC245 74HCT245: 1. General DescriptionLuis AntunesNo ratings yet

- 74HC HCT14Document16 pages74HC HCT14Alaa MuhameedNo ratings yet

- 74HC HCT154Document17 pages74HC HCT154eyadNo ratings yet

- 74HC HCT4052Document28 pages74HC HCT4052Edson MonteiroNo ratings yet

- 74AHC02 74AHCT02: 1. General DescriptionDocument13 pages74AHC02 74AHCT02: 1. General DescriptionalexNo ratings yet

- HEF4071B: 1. General DescriptionDocument12 pagesHEF4071B: 1. General DescriptionJuan Camilo EspinosaNo ratings yet

- HART EDD Library Encoded File Distribution DDList19 - 2Document53 pagesHART EDD Library Encoded File Distribution DDList19 - 2A N ArunkumarNo ratings yet

- DD ListDocument66 pagesDD ListAlcirlei Ribeiro GomesNo ratings yet

- D D D D D D D D: SN54ABT16646, SN74ABT16646 16-Bit Bus Transceivers and Registers With 3-State OutputsDocument19 pagesD D D D D D D D: SN54ABT16646, SN74ABT16646 16-Bit Bus Transceivers and Registers With 3-State OutputsKhan KakaNo ratings yet

- 74HC HCT08Document13 pages74HC HCT08Adam SchwemleinNo ratings yet

- 74HC HCT4051Document28 pages74HC HCT4051Razak JeyNo ratings yet

- 74HC2G14 74HCT2G14: 1. General DescriptionDocument21 pages74HC2G14 74HCT2G14: 1. General DescriptionNicolas PeresNo ratings yet

- HEF4069UB: 1. General DescriptionDocument17 pagesHEF4069UB: 1. General DescriptionJoel PalzaNo ratings yet

- Dewatering - Fire Protection and Water Supply RupiceDocument132 pagesDewatering - Fire Protection and Water Supply RupiceMateo OstojicNo ratings yet

- 74AHC139 NexperiaDocument14 pages74AHC139 NexperiaJuan PerezNo ratings yet

- 74LVT16244BDL - 3.3V LVT 16-Bit Buffer-Driver 3-StateDocument10 pages74LVT16244BDL - 3.3V LVT 16-Bit Buffer-Driver 3-StateGabriel RacovskyNo ratings yet

- Qsgmii SpecificationDocument20 pagesQsgmii Specificationreza_azadNo ratings yet

- Slla 070 DDocument25 pagesSlla 070 DEngr. AbdullahNo ratings yet

- NB3RL02 Low Phase-Noise Two-Channel Clock Fanout Buffer: Marking DiagramsDocument9 pagesNB3RL02 Low Phase-Noise Two-Channel Clock Fanout Buffer: Marking Diagramsreza_azadNo ratings yet

- NPort 5100 Series - Moxa-Pcomm-Lite-Utility-V1.6.zip - Software Release HistoryDocument4 pagesNPort 5100 Series - Moxa-Pcomm-Lite-Utility-V1.6.zip - Software Release Historyreza_azadNo ratings yet

- Slla 070 DDocument25 pagesSlla 070 DEngr. AbdullahNo ratings yet

- AN-1031 TIA/EIA-422-B Overview: Application ReportDocument11 pagesAN-1031 TIA/EIA-422-B Overview: Application Reportreza_azadNo ratings yet

- Low - Pow Er, 1.62V To 3.63V, 1Mhz To 150Mhz, 1:2 Fanout Buffer IcDocument5 pagesLow - Pow Er, 1.62V To 3.63V, 1Mhz To 150Mhz, 1:2 Fanout Buffer Icreza_azadNo ratings yet

- 74LVC16245A 74LVCH16245A: 1. General DescriptionDocument21 pages74LVC16245A 74LVCH16245A: 1. General Descriptionreza_azadNo ratings yet

- AN1208: Choosing The Correct Oscillator To Meet Your IEEE 1588v2 Network Synchronization Holdover RequirementsDocument17 pagesAN1208: Choosing The Correct Oscillator To Meet Your IEEE 1588v2 Network Synchronization Holdover Requirementsreza_azadNo ratings yet

- Si5338 EVBDocument12 pagesSi5338 EVBreza_azadNo ratings yet

- Stanag / Havequick Synchronization Stanag / Havequick SynchronizationDocument4 pagesStanag / Havequick Synchronization Stanag / Havequick Synchronizationreza_azad100% (2)

- 1 - 8 / 2 - 5 / 3 - 3 V L - J, L - S C B / L T: OW Itter OW KEW Lock Uffer Evel RanslatorDocument20 pages1 - 8 / 2 - 5 / 3 - 3 V L - J, L - S C B / L T: OW Itter OW KEW Lock Uffer Evel RanslatorharshalvikasNo ratings yet

- Description Features: 3-Channel High-Performance TCXO/LVCMOS Clock Buffer Family 5PB12xx DatasheetDocument16 pagesDescription Features: 3-Channel High-Performance TCXO/LVCMOS Clock Buffer Family 5PB12xx Datasheetreza_azadNo ratings yet

- 7 Series FPGAs OverviewDocument16 pages7 Series FPGAs Overviewreza_azadNo ratings yet

- Microsemi Time Interfaces WertheimerDocument29 pagesMicrosemi Time Interfaces Wertheimerreza_azadNo ratings yet

- Femtoclock NG Universal Frequency Translator With Phase Build-OutDocument42 pagesFemtoclock NG Universal Frequency Translator With Phase Build-Outreza_azadNo ratings yet

- Aliant Ommunications: IEEE-1588v2 PTP SlaveDocument2 pagesAliant Ommunications: IEEE-1588v2 PTP Slavereza_azadNo ratings yet

- Aliant Ommunications: IEEE-1588v2 PTP SlaveDocument2 pagesAliant Ommunications: IEEE-1588v2 PTP Slavereza_azadNo ratings yet

- CE Time Catcher 1588Document2 pagesCE Time Catcher 1588reza_azadNo ratings yet

- Stanag / Havequick Synchronization Stanag / Havequick SynchronizationDocument4 pagesStanag / Havequick Synchronization Stanag / Havequick Synchronizationreza_azad100% (2)

- The NMEA 0183 ProtocolDocument28 pagesThe NMEA 0183 ProtocolMarco Cocco100% (5)

- Timespy Elite - Portable Precision Time MeasurementDocument5 pagesTimespy Elite - Portable Precision Time Measurementreza_azadNo ratings yet

- U77c161xx001 PDFDocument4 pagesU77c161xx001 PDFreza_azadNo ratings yet

- P1016 Qoriq Integrated Processor Hardware Specifications: Data Sheet: Technical DataDocument106 pagesP1016 Qoriq Integrated Processor Hardware Specifications: Data Sheet: Technical Datareza_azadNo ratings yet

- THVD 1512Document41 pagesTHVD 1512reza_azadNo ratings yet

- Ulp Aluminum Electrolytic CapacitorsDocument10 pagesUlp Aluminum Electrolytic Capacitorsreza_azadNo ratings yet

- Managing The Impact of Cable DelaysDocument10 pagesManaging The Impact of Cable Delaysreza_azadNo ratings yet

- Samsung DRAM Module Handling Guide - 1128 - 10090119049407 PDFDocument9 pagesSamsung DRAM Module Handling Guide - 1128 - 10090119049407 PDFreza_azadNo ratings yet

- Samsung DRAM Module Handling Guide - 1128 - 10090119049407 PDFDocument9 pagesSamsung DRAM Module Handling Guide - 1128 - 10090119049407 PDFreza_azadNo ratings yet

- Project IdeasDocument1 pageProject Ideasc19138913iNo ratings yet

- Exp 3 Oscilloscope and Voltage MeasurementDocument7 pagesExp 3 Oscilloscope and Voltage MeasurementusmpowerlabNo ratings yet

- Off Grid With Battery Design Simulation Tool Type2Document8 pagesOff Grid With Battery Design Simulation Tool Type2Balamurugan ArumugamNo ratings yet

- IIT Physics - Magnatism Formula SheetDocument9 pagesIIT Physics - Magnatism Formula SheetParas Thakur100% (1)

- MRI BasicsDocument73 pagesMRI BasicsLyla BrjanNo ratings yet

- XBox One Power From ATX Power SupplyDocument5 pagesXBox One Power From ATX Power Supplycolorado wildernessNo ratings yet

- Syllabus of 2nd Semester All 2 PDFDocument43 pagesSyllabus of 2nd Semester All 2 PDFDeepak Kumar gautamNo ratings yet

- Band Theory For SolidsDocument6 pagesBand Theory For SolidsShaji ThomasNo ratings yet

- Disassembly Inkjet 2007109185837Document2 pagesDisassembly Inkjet 2007109185837Oliver TabagNo ratings yet

- The Need For Harmonic Modeling and Mitigation of Generator ApplicationsDocument8 pagesThe Need For Harmonic Modeling and Mitigation of Generator ApplicationssnfulNo ratings yet

- Physics Mathematical2013 PDFDocument7 pagesPhysics Mathematical2013 PDFRAHUL SHARMA mathematics class 10thNo ratings yet

- VX-2100 2200 VHF EuDocument68 pagesVX-2100 2200 VHF EudenariraNo ratings yet

- Service Manual: Micro-Tech - 1200Document43 pagesService Manual: Micro-Tech - 1200ALEJANDRONo ratings yet

- Daka-r Manual 영문 Ver 1 161205Document45 pagesDaka-r Manual 영문 Ver 1 161205ngoctuyenkt1No ratings yet

- 570N EP Tier 4B Final TRACTOR LOADER 55 KW ELECTRICAL SCHEMATICDocument6 pages570N EP Tier 4B Final TRACTOR LOADER 55 KW ELECTRICAL SCHEMATICEl PerroNo ratings yet

- L7800 Series: Positive Voltage RegulatorsDocument25 pagesL7800 Series: Positive Voltage RegulatorsArturo HernandesNo ratings yet

- Applimotion UTH Motor Kits DatasheetDocument3 pagesApplimotion UTH Motor Kits DatasheetElectromateNo ratings yet

- ISC12 Physics Project668Document19 pagesISC12 Physics Project668Ruhi BhattNo ratings yet

- AN91445 Antenna Design and RF Layout GuidelinesDocument60 pagesAN91445 Antenna Design and RF Layout GuidelinesaguiladeoroNo ratings yet

- Radio Station Training ReportDocument37 pagesRadio Station Training Reportapi-26629623100% (1)

- Electrostatic Forces and FieldsDocument16 pagesElectrostatic Forces and FieldsShahbaz KhanNo ratings yet

- Modeling and Applications of Metamaterial Transmission Lines Loaded With Pairs of Coupled Complementary Split-Ring Resonators (CSRRS)Document4 pagesModeling and Applications of Metamaterial Transmission Lines Loaded With Pairs of Coupled Complementary Split-Ring Resonators (CSRRS)Nabil DakhliNo ratings yet

- S9014 NPN transistor audio and converter circuit specsDocument1 pageS9014 NPN transistor audio and converter circuit specsEduardoEj-DjOlaecheaNo ratings yet

- 24 Avajc 11Document3 pages24 Avajc 11m.a.todurkarNo ratings yet

- Installation of Single Conductor CableDocument4 pagesInstallation of Single Conductor CableMrNo ratings yet

- VN5T016AH-E: Single Channel High-Side Driver With Analog Current Sense For 24 V Automotive ApplicationsDocument31 pagesVN5T016AH-E: Single Channel High-Side Driver With Analog Current Sense For 24 V Automotive ApplicationscutoNo ratings yet

- SJ 20101028153047 005 ZXSDR 20R8882 20GUL1812 V2.00 Remote 20radio 20unit 20hardware 20description - 435192Document19 pagesSJ 20101028153047 005 ZXSDR 20R8882 20GUL1812 V2.00 Remote 20radio 20unit 20hardware 20description - 435192glocallNo ratings yet

- MV and Synch Gear As Built-7Document37 pagesMV and Synch Gear As Built-7Sayed Younis SadaatNo ratings yet

- Reliance - Formulas & Calculations PDFDocument5 pagesReliance - Formulas & Calculations PDFkrishbistNo ratings yet

- Capacitores Eletroliticos Panasonic PDFDocument212 pagesCapacitores Eletroliticos Panasonic PDFJose Paulo MarcianoNo ratings yet

- The Fabric of Civilization: How Textiles Made the WorldFrom EverandThe Fabric of Civilization: How Textiles Made the WorldRating: 4.5 out of 5 stars4.5/5 (57)

- Hero Found: The Greatest POW Escape of the Vietnam WarFrom EverandHero Found: The Greatest POW Escape of the Vietnam WarRating: 4 out of 5 stars4/5 (19)

- Packing for Mars: The Curious Science of Life in the VoidFrom EverandPacking for Mars: The Curious Science of Life in the VoidRating: 4 out of 5 stars4/5 (1395)

- Sully: The Untold Story Behind the Miracle on the HudsonFrom EverandSully: The Untold Story Behind the Miracle on the HudsonRating: 4 out of 5 stars4/5 (103)

- Faster: How a Jewish Driver, an American Heiress, and a Legendary Car Beat Hitler's BestFrom EverandFaster: How a Jewish Driver, an American Heiress, and a Legendary Car Beat Hitler's BestRating: 4 out of 5 stars4/5 (28)

- The Intel Trinity: How Robert Noyce, Gordon Moore, and Andy Grove Built the World's Most Important CompanyFrom EverandThe Intel Trinity: How Robert Noyce, Gordon Moore, and Andy Grove Built the World's Most Important CompanyNo ratings yet

- The Weather Machine: A Journey Inside the ForecastFrom EverandThe Weather Machine: A Journey Inside the ForecastRating: 3.5 out of 5 stars3.5/5 (31)

- The Quiet Zone: Unraveling the Mystery of a Town Suspended in SilenceFrom EverandThe Quiet Zone: Unraveling the Mystery of a Town Suspended in SilenceRating: 3.5 out of 5 stars3.5/5 (23)

- Einstein's Fridge: How the Difference Between Hot and Cold Explains the UniverseFrom EverandEinstein's Fridge: How the Difference Between Hot and Cold Explains the UniverseRating: 4.5 out of 5 stars4.5/5 (50)

- Pale Blue Dot: A Vision of the Human Future in SpaceFrom EverandPale Blue Dot: A Vision of the Human Future in SpaceRating: 4.5 out of 5 stars4.5/5 (587)

- The End of Craving: Recovering the Lost Wisdom of Eating WellFrom EverandThe End of Craving: Recovering the Lost Wisdom of Eating WellRating: 4.5 out of 5 stars4.5/5 (80)

- The Beekeeper's Lament: How One Man and Half a Billion Honey Bees Help Feed AmericaFrom EverandThe Beekeeper's Lament: How One Man and Half a Billion Honey Bees Help Feed AmericaNo ratings yet

- Transformed: Moving to the Product Operating ModelFrom EverandTransformed: Moving to the Product Operating ModelRating: 4 out of 5 stars4/5 (1)

- A Place of My Own: The Architecture of DaydreamsFrom EverandA Place of My Own: The Architecture of DaydreamsRating: 4 out of 5 stars4/5 (241)

- The Path Between the Seas: The Creation of the Panama Canal, 1870-1914From EverandThe Path Between the Seas: The Creation of the Panama Canal, 1870-1914Rating: 4.5 out of 5 stars4.5/5 (124)

- 35 Miles From Shore: The Ditching and Rescue of ALM Flight 980From Everand35 Miles From Shore: The Ditching and Rescue of ALM Flight 980Rating: 4 out of 5 stars4/5 (21)

- The Technology Trap: Capital, Labor, and Power in the Age of AutomationFrom EverandThe Technology Trap: Capital, Labor, and Power in the Age of AutomationRating: 4.5 out of 5 stars4.5/5 (46)

- The Future of Geography: How the Competition in Space Will Change Our WorldFrom EverandThe Future of Geography: How the Competition in Space Will Change Our WorldRating: 4.5 out of 5 stars4.5/5 (4)

- Permaculture for the Rest of Us: Abundant Living on Less than an AcreFrom EverandPermaculture for the Rest of Us: Abundant Living on Less than an AcreRating: 4.5 out of 5 stars4.5/5 (33)

- Data-ism: The Revolution Transforming Decision Making, Consumer Behavior, and Almost Everything ElseFrom EverandData-ism: The Revolution Transforming Decision Making, Consumer Behavior, and Almost Everything ElseRating: 3.5 out of 5 stars3.5/5 (12)

- Recording Unhinged: Creative and Unconventional Music Recording TechniquesFrom EverandRecording Unhinged: Creative and Unconventional Music Recording TechniquesNo ratings yet

- Reality+: Virtual Worlds and the Problems of PhilosophyFrom EverandReality+: Virtual Worlds and the Problems of PhilosophyRating: 4 out of 5 stars4/5 (24)

- ChatGPT Money Machine 2024 - The Ultimate Chatbot Cheat Sheet to Go From Clueless Noob to Prompt Prodigy Fast! Complete AI Beginner’s Course to Catch the GPT Gold Rush Before It Leaves You BehindFrom EverandChatGPT Money Machine 2024 - The Ultimate Chatbot Cheat Sheet to Go From Clueless Noob to Prompt Prodigy Fast! Complete AI Beginner’s Course to Catch the GPT Gold Rush Before It Leaves You BehindNo ratings yet

- Dirt to Soil: One Family’s Journey into Regenerative AgricultureFrom EverandDirt to Soil: One Family’s Journey into Regenerative AgricultureRating: 5 out of 5 stars5/5 (125)