Professional Documents

Culture Documents

Obtain Optimum Implementation

Uploaded by

Albert Justiniano MedinaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Obtain Optimum Implementation

Uploaded by

Albert Justiniano MedinaCopyright:

Available Formats

Department of Electrical and Computer Engineering

COEN 312 Dec.4, 2008

Answer all Questions. All questions carry equal marks.

Exam Duration 3 hour

No books or papers are allowed. Examiner: Asim J. Al-Khalili

===============================================================

Question 1

Using Boolean algebra, minimize the following function:

a) F (A,B,C,D) = ABCD + (ABD)’ + ABC’D

b) Given f(x,y,z) = xy +x z’ + yz

i) Implement f in NOR-NOR format

ii) Implement f in AND-OR-INVERT format

Obtain optimum implementation.

Question 2

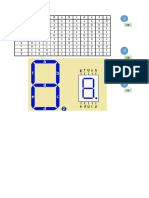

Design a combinational circuit decoder that examines a BCD digit and displays a letter

“L” if the digit was less than or equal 5. Use the Display unit shown below. Implement

the circuit using minimum 2*1 MUXes.

a

b c

d

e f

g

Page 1 of 9 COEN312 Dec.4, 2008

Question 3

a) Design a Half Subtractor.

b) Design a Full Subtractor using two Half Subtractors.

c) Using two 4 * 1 multiplexers implement the Full Subtractor

Question 4

Design a BCD adder that adds two BCD digits and produces a sum digit in BCD. You

may use 4-bit binary adders for your design. Give the circuit diagram.

Question 5

Design a sequential circuit with two JK flip flops A & B and two inputs E &

F. If E=0, the circuit remains in the same state regardless of the value of F.

When E=1 and F=1, the circuit goes through the state transition from 00 to

01 to 10 to 11, back to 00 and repeats. When E=1 and F=0, the circuit goes

through the state transitions from 00 to 11, to 10 to 01, back to 00 and

repeats.

Page 2 of 9 COEN312 Dec.4, 2008

Question 6

Analyze the circuit below fully. Derive the Transition Table, Excitation Table, State

Diagram and the Output. Explain the function of the circuit.

TA

QA

A

FF-A

CLK

TB

B QB

FF-B

CLK

Page 3 of 9 COEN312 Dec.4, 2008

SOLUTION

COEN312, DEC4 2008

Q1.

a.

F(A,B,C,D) =ABCD+(ABD)’+ABC’D

=ABD(C+C’)+(ABD)’=ABD+(ABD)’=1

OR

=ABCD+(ABD)’+ABC’D

=BCD+A’+B’+D’+BC’D

=CD+A’+B’+D’+C’D

=C+A’+B’+D’+C’D

=A’+B’+D’+C+D

=1

b.

f(x,y,z) =xy+xz’+yz

=xy(z+z’)+xz’+yz

=xyz+xyz’+xz’+yz

=xz’+yz

i)

f= Z \ XY 00 01 11 10

0 0 0 1 1

1 0 1 1 0

f=(x+z).(y+z’)

ii)

f= Z \ XY 00 01 11 10

0 1 1 0 0

1 1 0 0 1

f=(x’z’)+(y’z)

Page 4 of 9 COEN312 Dec.4, 2008

Q2.

Segments ‘beg’ has to be on in order to have ‘L’ on the seven-segments display.

A B C D a b c d e f g

0 0 0 0 0 0 1 0 0 1 0 1

1 0 0 0 1 0 1 0 0 1 0 1

2 0 0 1 0 0 1 0 0 1 0 1

3 0 0 1 1 0 1 0 0 1 0 1

4 0 1 0 0 0 1 0 0 1 0 1

5 0 1 0 1 0 1 0 0 1 0 1

6 0 1 1 0 0 0 0 0 0 0 0

7 0 1 1 1 0 0 0 0 0 0 0

8 1 0 0 0 0 0 0 0 0 0 0

9 1 0 0 1 0 0 0 0 0 0 0

a=c=d=f=0

b=e=g =A’B’+A’C’

=A’(B’+C’)

f= AB\CD 00 01 11 10

00 1 1 1 1

01 1 1 0 0

11 X X X X

10 0 0 0 X

Q3.

For the half-subtractor, For the full-subtractor,

a. b.

a b D B a b B_ D B

0 0 0 0 0 0 0 0 0

0 1 1 1 0 0 1 1 1

1 0 1 0 0 1 0 1 1

1 1 0 0 0 1 1 0 1

1 0 0 1 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

D ( a b)

B ab

Page 5 of 9 COEN312 Dec.4, 2008

The K-map tables give:

B= b_\ ab 00 01 11 10

D= b_\ ab 00 01 11 10 0 0 1 0 0

0 0 1 0 1 1 1 1 1 0

1 1 0 1 0 D ab b _ (a b)

D (a b b _) ab b _ ab b _ ab

abb _ abb _ abb _ abb _

Page 6 of 9 COEN312 Dec.4, 2008

Q4.

The algorithm to do binary addition of two BCD numbers, with the result in BCD,

involves a binary adder to do the actual arithmetic operation along with another adder to

offset the result whenever the binary sum exceeds the BCD range, which is from 0 to 9.

When this happens, the addition is scaled up by 6. The operation has to take care of the

carry-out which will be asserted whenever the BCD range is exceeded or the actual

binary addition generates a carry. The Boolean expression for the carry bit is:

C K Z8Z 4 Z8Z 2

Page 7 of 9 COEN312 Dec.4, 2008

Q5.

State Diagram:

State Transition Table:

Present Next

Y1 Y0 EF 00 01 10 11

00 00 00 11 01

01 01 01 00 10

10 10 10 01 11

11 11 11 10 00

K-Maps for next state equations:

Y1+= y1y0\EF 00 01 11 10

00 0 0 0 1

01 0 0 1 0

11 1 1 0 1

10 1 1 1 0

Y1 E y1 Fy1 y0 F y1 y0 EFy1 y0 E F y1 y0

Y0+= y1y0\EF 00 01 11 10

00 0 0 1 1

01 1 1 0 0

11 1 1 0 0

10 0 0 1 1

Y0 E y0 Ey0

Page 8 of 9 COEN312 Dec.4, 2008

Q6.

Analysis:

TA QA QB

TB QA QB

State transition table:

CLK NEXT STATE

QA QB TA TB QA+ QB+

0 0 0 1 0 1

0 1 1 1 1 0

1 0 1 0 0 0

1 1 1 1 0 0

State diagram:

Outputs are of the state itself.

This circuit is a counter “00”->“01”->“10” and back to “00”…, if ever started in “11”

state, then the next state on the pulse will set state to “00”, “01” and so on.

Page 9 of 9 COEN312 Dec.4, 2008

You might also like

- Solution Manual For Digital Systems Design Using Verilog 1st Edition by RothDocument16 pagesSolution Manual For Digital Systems Design Using Verilog 1st Edition by Rotha19397263917% (6)

- Digital Electronics BCD To 7segDocument2 pagesDigital Electronics BCD To 7segtatendaNo ratings yet

- Exam II - Sample - Solution PDFDocument8 pagesExam II - Sample - Solution PDFwael mahfouzNo ratings yet

- S 19202Document4 pagesS 19202Rohit MurarkaNo ratings yet

- ECE-223, Solution For Assignment #8Document4 pagesECE-223, Solution For Assignment #8RUBIONo ratings yet

- Learning Activity 2 + 3: BCD To 7 Segment LEDDocument7 pagesLearning Activity 2 + 3: BCD To 7 Segment LEDVân Anh Tôn QuangNo ratings yet

- Figure 1-1 Basic Gates: A B C A B C And: C A B Or: C A + BDocument39 pagesFigure 1-1 Basic Gates: A B C A B C And: C A B Or: C A + BbikisahuNo ratings yet

- Programmable Logic: Pal, PlaDocument26 pagesProgrammable Logic: Pal, PlaShiak AmeenullaNo ratings yet

- Chapter 4: Combinational Logic Solutions To Problems: (1, 5, 9, 12, 19, 23, 30, 33)Document14 pagesChapter 4: Combinational Logic Solutions To Problems: (1, 5, 9, 12, 19, 23, 30, 33)Gabriel FernandoNo ratings yet

- Seven Segment Display1Document7 pagesSeven Segment Display1Victor PrestonNo ratings yet

- Laboratory Exercise #2 4-Bit BCD Decoder: Submitted To Professor in EE 538/LDocument5 pagesLaboratory Exercise #2 4-Bit BCD Decoder: Submitted To Professor in EE 538/LDSNo ratings yet

- Switching Theory and Logic DesignDocument10 pagesSwitching Theory and Logic DesignRajkumarBattuNo ratings yet

- MACROMEC - Solucion Tarea 01Document1 pageMACROMEC - Solucion Tarea 01jochc2024No ratings yet

- Final Examination Solutions - Spring 2016-2017Document9 pagesFinal Examination Solutions - Spring 2016-2017Ghost BustersNo ratings yet

- Assignment 1Document41 pagesAssignment 1Sai BharathNo ratings yet

- 2.4 Computational Logic End of Unit Quiz Lesson ElementDocument12 pages2.4 Computational Logic End of Unit Quiz Lesson ElementOniNo ratings yet

- Assignment # 3 Solution: Your Work To Receive Full CreditDocument4 pagesAssignment # 3 Solution: Your Work To Receive Full CreditTayyab AbbasNo ratings yet

- DLDADocument30 pagesDLDAManoj NaikNo ratings yet

- Midterm II SolutionsDocument12 pagesMidterm II SolutionsSSTGingNo ratings yet

- Chapter 3Document41 pagesChapter 3HasanNo ratings yet

- ESc201A HA8soln 21 - 10 19Document8 pagesESc201A HA8soln 21 - 10 19Pk KumarNo ratings yet

- 07 Pal Pla RomDocument26 pages07 Pal Pla RomAnamika PancholiNo ratings yet

- DSD Hw2 Spring 2017Document2 pagesDSD Hw2 Spring 2017Lam Pham Phuoc LocNo ratings yet

- Chapter 4 - Combinational Logic Solutions To Problems - (1, 5, 9, 12, 23, 30)Document10 pagesChapter 4 - Combinational Logic Solutions To Problems - (1, 5, 9, 12, 23, 30)Sean Matthew L. OcampoNo ratings yet

- Rank Improvement Batch: Electronics EngineeringDocument9 pagesRank Improvement Batch: Electronics EngineeringRaj AryanNo ratings yet

- Seven Segments ReportDocument12 pagesSeven Segments ReportJun TobiasNo ratings yet

- DLD Lab#5 ReportDocument8 pagesDLD Lab#5 ReportAitazazNo ratings yet

- Cont AdoreDocument3 pagesCont AdoreOmar acNo ratings yet

- Display 7 Seg Compuertas LogicasDocument3 pagesDisplay 7 Seg Compuertas Logicasyordy julcahuancaNo ratings yet

- Lebanese International University School of Arts and Sciences - Department of Computer ScienceDocument6 pagesLebanese International University School of Arts and Sciences - Department of Computer ScienceAli NassarNo ratings yet

- Assignment 1 SolutionDocument4 pagesAssignment 1 SolutionManoranjan DasNo ratings yet

- Comb Circ PDFDocument63 pagesComb Circ PDFSrinivasan KrishnanNo ratings yet

- Comb Circ PDFDocument63 pagesComb Circ PDFMengistu KetemaNo ratings yet

- Practical File Digital Systems and Applications (Lab) - Experiment 5 Four Variable K-MapDocument10 pagesPractical File Digital Systems and Applications (Lab) - Experiment 5 Four Variable K-MapDevendra SheoranNo ratings yet

- Portas Logicas NovoDocument14 pagesPortas Logicas NovoKarina MesquitaNo ratings yet

- Karnaugh Map To Entered Variable Map: Digital Electronic CircuitsDocument13 pagesKarnaugh Map To Entered Variable Map: Digital Electronic CircuitsHari PrasadNo ratings yet

- BCD To OtherDocument18 pagesBCD To Otherarpit sharmaNo ratings yet

- DLD LAB#4 AssignmentDocument8 pagesDLD LAB#4 AssignmentHamza KhanNo ratings yet

- Tutorial 4 AnswersDocument2 pagesTutorial 4 AnswersM Arif SiddiquiNo ratings yet

- EGR 265 Final ExamDocument6 pagesEGR 265 Final Examcompuguy1088No ratings yet

- Display 7 Seg Compuertas LogicasDocument3 pagesDisplay 7 Seg Compuertas LogicasDarney AguasNo ratings yet

- First 23 Girraween 2022 2U Trials & SolutionsDocument41 pagesFirst 23 Girraween 2022 2U Trials & Solutionskilisa2963No ratings yet

- Exercise 3 - SolutionsDocument5 pagesExercise 3 - SolutionsWirnkar Basil NsanyuyNo ratings yet

- Laboratory 5 Iv - Results/ Verification:: Alvin J. Gilay ECE 538 - Logic Circuits and Logic TheoryDocument7 pagesLaboratory 5 Iv - Results/ Verification:: Alvin J. Gilay ECE 538 - Logic Circuits and Logic TheoryAlvin GilayNo ratings yet

- Proyecto Final Circuitos Lógicos CombinatoriosDocument4 pagesProyecto Final Circuitos Lógicos CombinatoriosJuan Mateo Páez AlonsoNo ratings yet

- DD Assignment-2 SolutionDocument10 pagesDD Assignment-2 Solutionsarim rizviNo ratings yet

- Chapter 4 - Logic and BooleanDocument3 pagesChapter 4 - Logic and BooleanSandesh GiriNo ratings yet

- Lecture Notes - Combinational Circuits ExamplesDocument4 pagesLecture Notes - Combinational Circuits Examplesbarstowcollege2012No ratings yet

- Lab01 PDFDocument3 pagesLab01 PDFTrí ĐứcNo ratings yet

- KmapsDocument8 pagesKmapsSrinu TeluguNo ratings yet

- L04 - Combinational LogicDocument27 pagesL04 - Combinational LogicPirzada SwatiNo ratings yet

- Chapter 2: Boolean Algebra & Logic Gates Solutions of Problems: Problem: 2-1Document7 pagesChapter 2: Boolean Algebra & Logic Gates Solutions of Problems: Problem: 2-1GHULAM MOHIUDDINNo ratings yet

- Chapter 9Document40 pagesChapter 9doomachaleyNo ratings yet

- Bolean Algebra & K-MAPDocument11 pagesBolean Algebra & K-MAPAnn RazonNo ratings yet

- Karnaugh MapDocument29 pagesKarnaugh MapRenieNo ratings yet

- Lab Assignment Digital Design - نسخةDocument5 pagesLab Assignment Digital Design - نسخةMaged SarhanNo ratings yet

- Hacettepe University Electrical and Electronics Engineering Ele237 Fundamentals of Digital SystemsDocument6 pagesHacettepe University Electrical and Electronics Engineering Ele237 Fundamentals of Digital SystemsMehmethan AyrımNo ratings yet

- 4a-CHAPTER 7 - ELECTRIC AND ELECTRONICS DEVICES - LOGIC CIRCUIT ANALYZINGDocument5 pages4a-CHAPTER 7 - ELECTRIC AND ELECTRONICS DEVICES - LOGIC CIRCUIT ANALYZINGazrinaishakNo ratings yet

- Student Name Subject: ITNT202/LOGIC Design Information Technology Department Semester 2Document9 pagesStudent Name Subject: ITNT202/LOGIC Design Information Technology Department Semester 2Muhammad IrfanNo ratings yet

- Answers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesFrom EverandAnswers to Selected Problems in Multivariable Calculus with Linear Algebra and SeriesRating: 1.5 out of 5 stars1.5/5 (2)

- S120 Control Unit Equip Man 0619 en-US-2Document360 pagesS120 Control Unit Equip Man 0619 en-US-2DmitriyNo ratings yet

- Chapter 3-Database Systems Eighth Edition PresentationDocument55 pagesChapter 3-Database Systems Eighth Edition PresentationAhsen DerseNo ratings yet

- SSN Project Report PDFDocument27 pagesSSN Project Report PDFErlanggaAdinegoroNo ratings yet

- Android Interview Questions Cheat SheetDocument26 pagesAndroid Interview Questions Cheat SheetNikolett Szabados-SoósNo ratings yet

- DBMS Project Report - $#$&Document22 pagesDBMS Project Report - $#$&Rati Shankar100% (1)

- Server ChecklistDocument22 pagesServer ChecklistMuralidaran KubendranNo ratings yet

- Softube Console 1 ManualDocument83 pagesSoftube Console 1 ManualAdam SmithNo ratings yet

- Foundation Project ProposalDocument10 pagesFoundation Project Proposalapi-658583191No ratings yet

- IDK-1112R-45SVA1E: User ManualDocument41 pagesIDK-1112R-45SVA1E: User Manualamit281276No ratings yet

- Introduction To IoT SyllabusDocument6 pagesIntroduction To IoT Syllabusayrakb2003No ratings yet

- 1640063346-Home Work PDF 05Document62 pages1640063346-Home Work PDF 05Suraj YadavNo ratings yet

- 50 - Define Number Ranges For Each Material Type in SAP MMDocument10 pages50 - Define Number Ranges For Each Material Type in SAP MMRameshNmklNo ratings yet

- Impresoras RICOH 1357 SC CodesDocument111 pagesImpresoras RICOH 1357 SC CodesPablo GuchNo ratings yet

- Cybersecurity in Africa An AssessmentDocument34 pagesCybersecurity in Africa An AssessmentTPK Studies & WorkNo ratings yet

- Java Lab Answer 5Document8 pagesJava Lab Answer 5adithkumar menonNo ratings yet

- Lesson Plan Assure Model SampleDocument5 pagesLesson Plan Assure Model SampleASHBEA LEENo ratings yet

- CSG3X5 4707858 PDFDocument31 pagesCSG3X5 4707858 PDFSorin - Viorel MaresNo ratings yet

- User Manual (89v51rd2)Document4 pagesUser Manual (89v51rd2)rahul_kumbhar05No ratings yet

- Oracle Database Upgrade To 11Gr2: From EtwikiDocument8 pagesOracle Database Upgrade To 11Gr2: From Etwikinehaa_sharma100% (1)

- Connected TV - 2022Document37 pagesConnected TV - 2022scribleNo ratings yet

- Assignment 3 Software Project ManagementDocument3 pagesAssignment 3 Software Project Managementmuhammad mubasher100% (1)

- SV Datatype Lab ExerciseDocument3 pagesSV Datatype Lab Exerciseabhishek singhNo ratings yet

- Using GPS Data With QgisDocument9 pagesUsing GPS Data With QgisRidwan SultanNo ratings yet

- Data AcquisitionDocument28 pagesData Acquisitionvkv.foeNo ratings yet

- Big Ip Virtual Editions DatasheetDocument14 pagesBig Ip Virtual Editions DatasheetasalihovicNo ratings yet

- Cheat Sheet - Gnuplot2Document1 pageCheat Sheet - Gnuplot2Ambar ShuklaNo ratings yet

- The Importance of Grid ComputingDocument5 pagesThe Importance of Grid ComputingShija MafulahyaNo ratings yet

- Source Qualifier Transformation OverviewDocument25 pagesSource Qualifier Transformation Overviewypraju_dwhNo ratings yet

- RDBMSDocument49 pagesRDBMSRameswar ReddyNo ratings yet

- Recommender Systems With Generative RetrievalDocument11 pagesRecommender Systems With Generative RetrievalmanelNo ratings yet