Professional Documents

Culture Documents

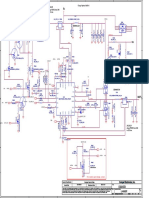

Schematics 1130188 PDF

Uploaded by

OlegOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Schematics 1130188 PDF

Uploaded by

OlegCopyright:

Available Formats

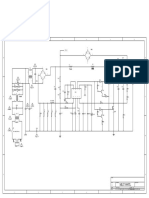

5 4 3 2 1

U5

1 S D 8

2 S D 7

3 S D 6

VDD_5V 4 5

G D

1

J1 CEM9435A(SMD)

D L4 D

2 VIN

2

BEAD_3Ts

1 U6

2N3904

3

3

DC_JACK L2 VDD_3V3

220uH/3A/DIP

P

R2 510,5%

D2

DC_JACK

U1 1N4148/SMD

2

N

L3 R3 200,5% 8 1 + + C20 C53 C54 + + +

P

DRIVER SC D1 C52 C51 C102 C103

SB220/SMD 0.1UF,50V 0.1UF,50V 0.1UF,50V C70

BEAD_3Ts 7 2 R17 47,5% 470U,16V

- 470U,16V

- - 100U,16V

- 100U,16V

-

N

1

N

IPK SE

VDD_5V 10uF,6.3V/SMD

R16 R5 6 3 R69 390K

0.22,5% 0.22,5% VCC TC C7

SMD0805 SMD0805

5 4 470pF,50V

COMP GND

P

C9 C10 RT34063ACS

C8

- 0.1uF,50V 0.1uF,50V R6 1.96K,1%

N

1000uF,25V

R7 C11 0.01uF,50V NC R18 10K,5% NC

1.24K,1%

C C

VDD_3V3

R21 NC

+ R8

P

C58 10K,1%

S

100U,16V

- AMS1117-ADJ/NC

N

C44 6 VCTRLR20 0,5% Q2 VDD_1V8

G

2SB1412

D

0.1uF,50V

L7 31at100MHz,0.6A

R22 R11 R9 +

P

0R/NC 4.99K,1% C57

B B

10K,1% 100U,16V

-

N

VDD_3V3 VDD_3V3 VDD_3V3 VDD_3V3 VDD_3V3 VDD_3V3

C60 C61 C62 C72 C75 C78

0.1UF,50V 0.1UF,50V 0.1UF,50V 0.1UF,50V 0.1UF,50V 0.1UF,50V

Q3 VDD_3V3

1 GND

2 VCC

VDD_3V3

VDD 2

EM6353BX2SP3B-2.6

C29

3 REST 0.1UF,50V

1 3 R10

GND RESET STL8110GCL300

1K/5%/DNE

STL8110GCL300

R4

RESET

RESET_CPU RESET 4,5

100,1%

VDD_3V3

C28

A R66 0.1uF,50V A

10K,1%

S1

2 1 R65 0,5% DEFAULT

DEFAULT 4

WavePlus Technology Co., Ltd.

6F., No.18, Prosperity Road II, Science-Based Industrial Park,

4

3

R67 C88 Hsinchu 300, Taiwan, R.O.C.

100K,1% Designer : Y.S.Liao

1uF,10V

TACT-SWITCH Title

NOT INSERTION 5 PORT Router Demo BOARD "Power & Reset"

Size Document Number Rev

C SCH-051202-01 WP3221 AC DMB 0.4

Date: Tuesday, September 19, 2006 Sheet 3 of 7

5 4 3 2 1

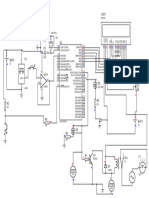

5 4 3 2 1

VDD_1V8 DVDD_3V3

+ + + + + +

P

C91 C92 C14 C37 C67 C69 C71

C76 C81 C83 C89 C90 C93 C94 100uF DIP C41 C59 C63 C64 C65

0.01uF 0.01uF 0.1uF 0.01uF 0.1uF 0.01uF 0.01uF - - - 0.1uF 0.1uF 0.1uF 0.01uF 0.01uF 0.01uF - - -

N

10uF,16V/SMD 0805 10uF,16V/SMD 0805 10uF,16V/SMD 0805 10uF,16V/SMD 0805 10uF,16V/SMD 0805

D D

VDD_3V3

DVDD_3V3

VDD_1V8 DVDD_3V3

C27

0.1uF,50V

VDD_1V8

C33 C34 C35

0.1uF 0.1uF 0.1uF

LINK/ACTIVITY:

ON: LINK

OFF: UNLINK

119

127

93

69

55

66

45

U2-1

2

BLINKING: ACTIVITY

1

VDD:P5

VDD:P4

VDD:P3

VDD:P2

VDD:P1

DVDD:P3

DVDD:P2

DVDD:P1

TDM_RING_INT/GPIOT[4]

SPEED: 41 TDM_MPI_CS/GPIOT[8]

ON: 100M 42 TDM_MPI_CLK/I2S_SCK/GPIOT[7]

OFF: 10M 43 TDM_MPI_DO/GPIOT[6]

44 TDM_MPI_DI/GPIOT[5]

DUPLEX/COL: 46 TDM_DXA/I2S_SDO/GPIOT[3]

ON: FULL DUPLEX 47 TDM_DRA/I2S_SDI/GPIOT[2]

OFF: HALF DUPLEX 48 TDM_FS/I2S_WS/GPIOT[1]

49 TDM_PCLK/I2S_MCLK/GPIOT[0]

BLINKING: COLLISION

C 50 LED[7]/GPIOL[7]

C

51 72 DSI

LED[6]/GPIOL[6] BDM_DSDI/SCAN_EN DSO

52 LED[5]/GPIOL[5] BDM_DSDO 71

LED4 53 70 BKPT

LED3 LED[4]/GPIOL[4] BDM_MBKPTB PSTCLK

54 LED[3]/GPIOL[3] BDM_PSTCLK 68

LED2 56 67 DSCLK

LED1 LED1 LED[2]/GPIOL[2] BDM_DSCLK

P0 R12 LED0

57

58

LED[1]/GPIOL[1]

64

LED0 LED[0]/GPIOL[0] SCAN_MODE RESET

LINK/ACTIVITY 2 1 VDD_3V3 RESET_N 63 RESET 3,5

3 GPIO3 59 I2C_SCL/GPIO[3]

330,1% DEFAULT 60

3 DEFAULT I2C_SDA/GPIO[2]

LEDx1 DIP GPIO_1/UART_RXD 61

GPIO_0/UART_TXD UART_RXD/GPIO[1]

62 UART_TXD/GPIO[0]

73 IO_CS_0_N/GPIO[5]

DGND:G4

DGND:G3

DGND:G2

DGND:G1

GND:G5

GND:G4

GND:G3

GND:G2

GND:G1

74 IO_IRQ_0/GPIO[6]

LED2

P1 R19

75 IO_WAIT_N/GPIO[4]

LINK/ACTIVITY LED1 2 1 VDD_3V3

111

95

85

65

128

103

78

40

39

330,1% WP3220-LQFP128-AA

LEDx1 DIP

LED3

P2 R13

LINK/ACTIVITY LED2 2 1 VDD_3V3

330,1%

LEDx1 DIP

B B

P3 LED4

R14

LINK/ACTIVITY LED3 2 1 VDD_3V3

330,1%

LEDx1 DIP

GPIO_1/UART_RXD

LEDx1 DIP TP1

GPIO_0/UART_TXD

P4 R15 TP2

LINK/ACTIVITY LED4 2 1 VDD_3V3

330,1%

LED5

STATUS

LEDx1 DIP LED6

R68 330,5% 2 1

4 GPIO3 VDD_3V3

R1 330,5% 2 1 VDD_3V3

LEDx1 DIP

A

Power LED7

A

WavePlus Technology Co., Ltd.

6F., No.18, Prosperity Road II, Science-Based Industrial Park,

Hsinchu 300, Taiwan, R.O.C.

Designer : Y.S.Liao

Title

5 PORT Router Demo BOARD "LED & I/O"

Size Document Number Rev

C SCH-051202-01 WP3221 AC DMB 0.4

Date: Tuesday, September 19, 2006 Sheet 4 of 7

5 4 3 2 1

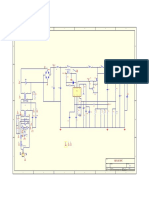

5 4 3 2 1

7 ADDR_[0:14]

DQM2/ADDR_15

DQM0/ADDR_17

DQM0/ADDR_17

DQM1/ADDR_18 RESET

DQM1/ADDR_18 3,4 RESET

D D

RN1 U3

MEM_ADDR0 2 1 ADDR_0

MEM_ADDR1 4 3 ADDR_1 DATA_0 29 25 ADDR_0

MEM_ADDR2 ADDR_2 DATA_1 Q0 A0 ADDR_1

6 5 31 Q1 A1 24

MEM_ADDR3 8 7 ADDR_3 DATA_2 33 23 ADDR_2

DATA_3 Q2 A2 ADDR_3

35 Q3 A3 22

33,1% DATA_4 38 21 ADDR_4

DATA_5 Q4 A4 ADDR_5

40 Q5 A5 20

RN2 DATA_6 42 19 ADDR_6

DQM0 DQM0/ADDR_17 DATA_7 Q6 A6 ADDR_7

8 7 DQM0/ADDR_17 44 Q7 A7 18

MEM_ADDR7 6 5 ADDR_7 DATA_8 30 8 ADDR_8

MEM_ADDR6 ADDR_6 DATA_9 Q8 A8 ADDR_9

4 3 32 Q9 A9 7

MEM_ADDR5 2 1 ADDR_5 DATA_10 34 6 ADDR_10

DATA_11 Q10 A10 ADDR_11

36 Q11 A11 5

33,1% DATA_12 39 4 ADDR_12

RN3 DATA_13 Q12 A12 ADDR_13

41 Q13 A13 3

MEM_ADDR8 2 1 ADDR_8 DATA_14 43 2 ADDR_14

MEM_ADDR9 ADDR_9 DATA_15 Q14 A14 DQM2/ADDR_15

4 3 45 Q15/A-1 A15 1

MEM_ADDR10 6 5 ADDR_10 48 DQM3/ADDR_16

MEM_ADDR11 ADDR_11 A16 DQM0/ADDR_17

8 7 A17 17

FWE 11

33,1% RESET WE VDD_SF

12 RESET VCC 37

MEM_ADDR16 R27 33,1% DQM3/ADDR_16 15

U2-3 MEM_ADDR4 R28 33,1% ADDR_4 FCE0 RY/BY

26 CE GND_1 27

97 FCE0 DQM1 R29 33,1% DQM1/ADDR_18 FOE 28 46

F_CS_0_N DQM1/ADDR_18 OE GND_2

76 SDR_CAS1 R30 33,1% SDR_CAS/ADDR_19 BYTE1_1 47

F_CS_1_N FWE SDR_RAS1 R31 33,1% SDR_RAS/ADDR_20 BYTE DQM1/ADDR_18

C

F_WE_N 82 NC_1 16 C

96 FOE 14

F_OE_N RN4 NC_2

NC_3 13

79 SCE0 MEM_ADDR12 2 1 ADDR_12 10 SDR_RAS/ADDR_20

SDR_CS_0_N MEM_ADDR13 ADDR_13 NC_4 SDR_CAS/ADDR_19

SDR_CS_1_N 77 4 3 NC_5 9

80 SDR_RAS1 MEM_ADDR14 6 5 ADDR_14

SDR_RAS_N/MEM_ADDR[20] SDR_CAS1 MEM_ADDR15 DQM2/ADDR_15

SDR_CAS_N/MEM_ADDR[19] 81 8 7 DQM2/ADDR_15

94 R32 33,1% SDR_CLK

SDR_CLK DQM0 33,1%

SDR_DQM[0]/MEM_ADDR[17] 116 MX29LV400B

92 DQM1

SDR_DQM[1]/MEM_ADDR[18]

MEM_DATA_0 BYTE1_1 R33 1K,1% VDD_SF

MEM_DATA[0] 98

99 MEM_DATA_1

Near the U1

MEM_DATA[1] MEM_DATA_2

MEM_DATA[2] 100

101 MEM_DATA_3 RN5

MEM_DATA[3] MEM_DATA_4 MEM_DATA_0 DATA_0

MEM_DATA[4] 102 2 1

104 MEM_DATA_5 MEM_DATA_1 4 3 DATA_1

MEM_DATA[5] MEM_DATA_6 MEM_DATA_2 DATA_2

MEM_DATA[6] 105 6 5

106 MEM_DATA_7 MEM_DATA_3 8 7 DATA_3

MEM_DATA[7] MEM_DATA_8

MEM_DATA[8] 91

90 MEM_DATA_9 0,1%

MEM_DATA[9] MEM_DATA_10 RN6

MEM_DATA[10] 89

88 MEM_DATA_11 MEM_DATA_4 2 1 DATA_4 U4

MEM_DATA[11] MEM_DATA_12 MEM_DATA_5 DATA_5

MEM_DATA[12] 87 4 3

86 MEM_DATA_13 MEM_DATA_6 6 5 DATA_6 DATA_0 2 21 ADDR_0

MEM_DATA[13] MEM_DATA_14 MEM_DATA_7 DATA_7 DATA_1 I/O0 A0 ADDR_1

MEM_DATA[14] 84 8 7 3 I/O1 A1 22

83 MEM_DATA_15 DATA_2 5 23 ADDR_2

MEM_DATA[15] 0,1% DATA_3 I/O2 A2 ADDR_3

6 I/O3 A3 24

MEM_ADDR0 RN7 DATA_4 ADDR_4

MEM_ADDR[0] 107 8 I/O4 A4 27

108 MEM_ADDR1 MEM_DATA_8 8 7 DATA_8 DATA_5 9 28 ADDR_5

MEM_ADDR[1] MEM_ADDR2 MEM_DATA_9 DATA_9 DATA_6 I/O5 A5 ADDR_6

MEM_ADDR[2] 109 6 5 11 I/O6 A6 29

110 MEM_ADDR3 MEM_DATA_10 4 3 DATA_10 DATA_7 12 30 ADDR_7

MEM_ADDR[3] MEM_ADDR4 MEM_DATA_11 DATA_11 DATA_8 I/O7 A7 ADDR_8

MEM_ADDR[4] 112 2 1 39 I/O8 A8 31

113 MEM_ADDR5 DATA_9 40 32 ADDR_9

MEM_ADDR[5] MEM_ADDR6 0,1% DATA_10 I/O9 A9 ADDR_10

MEM_ADDR[6] 114 42 I/O10 A10 20

115 MEM_ADDR7 RN8 DATA_11 43 19 ADDR_13

MEM_ADDR[7] MEM_ADDR8 MEM_DATA_12 DATA_12 DATA_12 I/O11 A11

MEM_ADDR[8] 117 8 7 45 I/O12

118 MEM_ADDR9 MEM_DATA_13 6 5 DATA_13 DATA_13 46 7 VDD_SF

B MEM_ADDR[9] MEM_ADDR10 MEM_DATA_14 DATA_14 DATA_14 I/O13 VCCQ_1 VDD_SF B

MEM_ADDR[10] 120 4 3 48 I/O14 VCCQ_2 13

121 MEM_ADDR11 MEM_DATA_15 2 1 DATA_15 DATA_15 49 38 VDD_SF

MEM_ADDR[11] MEM_ADDR12 I/O15 VCCQ_3 VDD_SF

MEM_ADDR[12] 122 VCCQ_4 44

123 MEM_ADDR13 0,1% DQM0/ADDR_17 14

MEM_ADDR[13]/BA0 MEM_ADDR14 FWE LDQM VDD_SF

MEM_ADDR[14]/BA1 124 15 WE VCC_1 1

125 MEM_ADDR15 SDR_CAS/ADDR_19 16 25 VDD_SF

MEM_ADDR[15]/SDR_DQM[2] MEM_ADDR16 SDR_RAS/ADDR_20 CAS VCC_2

MEM_ADDR[16]/SDR_DQM[3] 126 17 RAS

SCE0 18 4

WP3220-LQFP128-AA CS GNDQ_1

GNDQ_2 10

VDD_SF 34 41

SDR_CLK CKE GNDQ_3

35 CLK GNDQ_4 47

VDD_SF DQM1/ADDR_18 36 UDQM

GND_1 26

33 NC_1 GND_2 50

37 NC_2

C17 C18 C19

0.1uF,50V 0.1uF,50V 0.1uF,50V IC42S16100

VDD_SF

VDD_3V3

L9 31at100MHz,0.6A

C42 C43 C45 C46 C47 C48 C49

1uF,10V 1uF,10V 1uF,10V 1uF,10V 1uF,10V 1uF,10V 1uF,10V

A A

WavePlus Technology Co., Ltd.

6F., No.18, Prosperity Road II, Science-Based Industrial Park,

Hsinchu 300, Taiwan, R.O.C.

Designer : Y.S.Liao

Title

5 PORT Router Demo BOARD "Flash & SDRAM"

Size Document Number Rev

C SCH-051202-01 WP3221 AC DMB 0.4

Date: Tuesday, September 19, 2006 Sheet 5 of 7

5 4 3 2 1

5 4 3 2 1

VDA_3V3

VDA_3V3 VDD_3V3 VDA_3V3

+ + +

P

C99 L6 31at100MHz,0.6A

C56 C95 C101 C100 C50 C96 C25 C97 C24 C98 C23 C66 C22 C68 C21

10uF,16V/SMD

- 10uF,16V/SMD

- - 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF 0.1uF

N

+

P

100U,16V C55

100U,16V

-

N

D D

TXP4 7 10 TX4+

TD+ TX+

0.1uF

TXN4 5 12 TX4-

C79 TD- TX-

CMT4 RJ4

4 CT CMGND 13

CMT0R38 75,1% R40 75,1% 8

RXP4 RX4+ R39 75,1% BI_D12-

3 RD+ RX+ 14 7 BI_D12+

RX0- 6 TX_D1-

5 BI_D11-

4 BI_D11+

RXN4 1 16 RX4- RX0+ 3

RD- RX-

TX0- TX_D1+

2 RX_D1-

TX0+ 1

FT16-803B RX_D1+

T3T2

TXP3 1 TD+ TX+ 20 TX3+

0.1uF

TXN3 2 TD- TX- 19 TX3-

VDA_3V3 C77

3 CT CMGND 18 CMT3 CMT1 R34 75,1% R36 75,1% 16 BI_D22-

R35 75,1%

14

20

26

32

38

15 BI_D22+

8

U2-2 RXP3 4 RD+ RX+ 17 RX3+ TX1- 14 TX_D2-

13

VDDA1:

VDDA3:

VDDA0

VDDA0_

VDDA2

VDDA4

BI_D21-

REFRES 4 12 BI_D21+

5 TX1+ 11

VCTRL VCTRL 3 TX_D2+

XTAL25I 6 XIN RXN3 5 RD- RX- 16 RX3- RX1- 10 RX_D2-

7 XOUT RX1+ 9

XTAL25O R37 RX_D2+

C 33 TXP4 12.1K,1% C

TXP4 TXN4R41 RXN2

TXN4 34 100,1% 6 RD- RX- 15 RX2-

36 RXP4

RXP4 RXN4 0.1uF

RXN4 37

R42 100,1%

31 TXP3 C84 RXP2 7 RD+ RX+ 14 RX2+

TXP3 TXN3R43 100,1%

TXN3 30

RXP3 28 RXP3 8 CT CMGND 13 CMT2

27 RXN3 CMT2 R54 75,1% R56 75,1% 24

RXN3 BI_D32-

R44 100,1% TXN2 9 TD- TX- 12 TX2- R55 75,1% 23 BI_D32+

21 TXP2 RX2- 22

TXP2 TXN2R45 100,1% TX_D3-

TXN2 22 21 BI_D31-

24 RXP2 20

RXP2 BI_D31+

RXN2 25 RXN2 TXP2 10 TD+ TX+ 11 TX2+ RX2+ 19 TX_D3+

R46 100,1% TX2- 18

TXP1 TX2+ RX_D3-

TXP1 19 17 RX_D3+

18 TXN1R47 100,1% FT20-284B-1

TXN1 RXP1

RXP1 16

15 RXN1

RXN1 R48 100,1% T1

9 TXP0

TXP0 TXN0R49 0.1uF TXP1

TXN0 10 100,1% 1 TD+ TX+ 20 TX1+

12 RXP0

RXP0

VSA4:

VSA0:

RXN0 C82

VSA3

VSA2

VSA1

VSA0

RXN0 13

R50 100,1%

TXN1 2 TD- TX- 19 TX1- CMT3 R51 75,1% R53 75,1% 32 BI_D42-

WP3220-LQFP128-AA R52 75,1% 31

35

29

23

17

11

3

BI_D42+

3 CT CMGND 18 CMT1 TX3- 30 TX_D4-

29 BI_D41-

RXP1 4 RD+ RX+ 17 RX1+ 28 BI_D41+

C85 TX3+ 27

RX3- TX_D4+

26 RX_D4-

1nF,2KV/DIP RX3+ 25 RX_D4+

RXN1 5 RD- RX- 16 RX1-

RJ-45X5

B

RXN0 6 RD- RX- 15 RX0-

B

RXP0 RJ5

7 RD+ RX+ 14 RX0+

CMT4 R57 75,1% R59 75,1% 8 BI_D12-

8 CT CMGND 13 CMT0 R58 75,1% 7 BI_D12+

RX4- 6 TX_D1-

TXN0 9 TD- TX- 12 TX0- C87 5 BI_D11-

4

C86

TXP0 10 TD+ TX+ 11 TX0+

WAN port 1nF,2KV/DIP RX4+

TX4-

TX4+

3

2

1

BI_D11+

TX_D1+

RX_D1-

RX_D1+

0.1uF

FT20-284B-1 RJ-45X5

Y1

1 XIN

X1

2 XOUT

X2

XTAL_25MHz

C6

C73 C74

18pF,50V 18pF,50V FB SMD0805

C12

1nF,2KV NC

A A

C3

1nF,2KV NC

WavePlus Technology Co., Ltd.

6F., No.18, Prosperity Road II, Science-Based Industrial Park,

Hsinchu 300, Taiwan, R.O.C.

Designer : Y.S.Liao

Title

5 PORT Router Demo BOARD "Analog & RJ-45"

Size Document Number Rev

C SCH-051202-01 WP3221 AC DMB 0.4

Date: Tuesday, September 19, 2006 Sheet 6 of 7

5 4 3 2 1

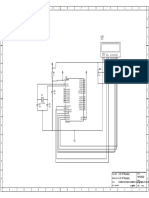

5 4 3 2 1

D D

C C

RJ11 RJ12

5 ADDR_[0:14]

VDD_SF VDD_SF

ADDR_1 R61 1K,1% NC R62 1K,1% NC

ADDR_3 ADDR_4

R60 1K,1% R63 1K,1% NC R64 1K,1% NC

led_direct_mode REF_CLK_SEL

B B

Initial Setting pins:

PIN Function Value

ADDR[1] LED Mode 0: Single LED

1: Matrix Mode

ADDR_[3:4] Freqency Selection 00: 150 MHz

01: 175 MHz

CPU run 175Mhz (Default)

while R58, R70,

R72, R114 DNE

A A

WavePlus Technology Co., Ltd.

6F., No.18, Prosperity Road II, Science-Based Industrial Park,

Hsinchu 300, Taiwan, R.O.C.

Designer : Y.S.Liao

Title

5 PORT Router Demo BOARD "BOOT STRAP"

Size Document Number Rev

C SCH-051202-01 WP3221 AC DMB 0.4

Date: Tuesday, September 19, 2006 Sheet 7 of 7

5 4 3 2 1

You might also like

- LVL - 1 Rev 15 PDFDocument1 pageLVL - 1 Rev 15 PDFskvskvskvskvNo ratings yet

- Schematic PDFDocument1 pageSchematic PDFDi NeverEndingNo ratings yet

- Schematic PDFDocument1 pageSchematic PDFDi NeverEndingNo ratings yet

- DDS Schematic PDFDocument1 pageDDS Schematic PDFjose eliasNo ratings yet

- DDS 4 SCH PDFDocument1 pageDDS 4 SCH PDFAchmad Zaenal ArifinNo ratings yet

- How to connect LED strip to microcontrollerDocument1 pageHow to connect LED strip to microcontrollerEonassis SantosNo ratings yet

- Rpi SCH 2b 1p2 ReducedDocument1 pageRpi SCH 2b 1p2 Reducedvijaykumarn100% (1)

- MH9400 Power SchematicDocument1 pageMH9400 Power SchematicKevinjose marchena moralesNo ratings yet

- Circuit diagram analysisDocument1 pageCircuit diagram analysisGustavo de Vargas DiasNo ratings yet

- HC 14000 MH 9400 SCHDocument1 pageHC 14000 MH 9400 SCHGustavo de Vargas DiasNo ratings yet

- HC 14000 MH 9400 SCHDocument1 pageHC 14000 MH 9400 SCHAudiotec ServiceNo ratings yet

- GND GND GND GND: Sheet - 1Document1 pageGND GND GND GND: Sheet - 1Julio César HCNo ratings yet

- Micro2440 Base SchematicDocument5 pagesMicro2440 Base SchematicAn HoàngNo ratings yet

- Ibanez Ds7 Distortion SchematicDocument1 pageIbanez Ds7 Distortion SchematicsubcomandantemarcosNo ratings yet

- Ckto Frecuencimetro: RA0 RA1Document8 pagesCkto Frecuencimetro: RA0 RA1Nemecio Laguna LoliNo ratings yet

- +3.3Vstb For AVDDA: WWW - Fineprint.cnDocument11 pages+3.3Vstb For AVDDA: WWW - Fineprint.cnAung HeinNo ratings yet

- Schema Shield Invatare ArduinoDocument1 pageSchema Shield Invatare ArduinoTokra2007No ratings yet

- MFS Arduino PDFDocument1 pageMFS Arduino PDFDusmantha AnandaratneNo ratings yet

- AJLickshot SirenDocument1 pageAJLickshot SirenGerardo MoleroNo ratings yet

- MLT199TL: 1.5mH 750uhDocument3 pagesMLT199TL: 1.5mH 750uhAziz KamelNo ratings yet

- z80lcd Rev0 SCMDocument1 pagez80lcd Rev0 SCMCesar GastaldiNo ratings yet

- SensorDocument1 pageSensorLuis German NiñoNo ratings yet

- NAMA WULAN INDRI SAFITRI KELAS B NIM 18061Document1 pageNAMA WULAN INDRI SAFITRI KELAS B NIM 18061Wulan Indri SafitriNo ratings yet

- ALi+M3602+DVB-S+HD+Ver +1 0Document14 pagesALi+M3602+DVB-S+HD+Ver +1 0bruno magalhãesNo ratings yet

- AUT0000983 - 2 Humidity Sensor CableDocument1 pageAUT0000983 - 2 Humidity Sensor CableMallampati RamakrishnaNo ratings yet

- Megmeet mp118t Psu SCHDocument3 pagesMegmeet mp118t Psu SCHali beheshtaeinNo ratings yet

- Inovex Mp118t Power Supply 16051716136862Document22 pagesInovex Mp118t Power Supply 16051716136862lalgalleNo ratings yet

- J5 CON2 battery monitor and protection circuitDocument1 pageJ5 CON2 battery monitor and protection circuitAbdulraouf Defnany100% (3)

- Gene VictorDocument1 pageGene Victorh2jmkjfdpsNo ratings yet

- Kepler-Esp-A Dual Blue 3.0VDocument5 pagesKepler-Esp-A Dual Blue 3.0V주씨No ratings yet

- Schematic1 - Page1Document1 pageSchematic1 - Page1Jeong-geun Kim100% (1)

- LCD At16Document1 pageLCD At16Yudi Wahyu PribadiNo ratings yet

- Pdv-t790 Ser Vice ManualDocument42 pagesPdv-t790 Ser Vice ManualAlexandru Daniel BuleuNo ratings yet

- Nobels Distortion XtremeDocument1 pageNobels Distortion Xtremecaccoloide100% (1)

- Switch controlled LED circuit with voltage regulationDocument1 pageSwitch controlled LED circuit with voltage regulationYuinariNo ratings yet

- RL19560 Schematics XXDocument26 pagesRL19560 Schematics XXAsif AbbasovNo ratings yet

- Tie 2015 UpbDocument4 pagesTie 2015 UpbCristian MăndicăNo ratings yet

- Trans Prot CirDocument1 pageTrans Prot Cirmpkkbtech100% (1)

- Quasar AVR Shematic Diagram PDFDocument1 pageQuasar AVR Shematic Diagram PDFRamazan ÖzenNo ratings yet

- 3.3V 5V 3.3V - A 12V: VIN Vout FB ENDocument2 pages3.3V 5V 3.3V - A 12V: VIN Vout FB ENAytac Gul100% (1)

- Power supply circuit diagramDocument1 pagePower supply circuit diagramjose luis rodriguez caberos100% (1)

- DC Motor ControlDocument1 pageDC Motor ControlDebashishParidaNo ratings yet

- Raspberry Pi 3b v1 170711123515 - 230617 - 004548Document2 pagesRaspberry Pi 3b v1 170711123515 - 230617 - 004548Krzysztof NowackiNo ratings yet

- An SEO-optimized title for an electrical circuit diagramDocument1 pageAn SEO-optimized title for an electrical circuit diagramRavi JagtianiNo ratings yet

- Schematic Combo LedDocument12 pagesSchematic Combo LedH S MannNo ratings yet

- Toro Mata Trumpet IDocument2 pagesToro Mata Trumpet IMilton LosanoNo ratings yet

- Power Audio LPF KEY: WWW - Fineprint.cnDocument1 pagePower Audio LPF KEY: WWW - Fineprint.cnÍcaro Viana100% (1)

- Power Supply - MainboardDocument1 pagePower Supply - MainboardgaikieuucNo ratings yet

- BQ 24737Document1 pageBQ 24737DevendraSharmaNo ratings yet

- Vin Vout: TP13 TP13 TP12 TP12 TP14 TP14 TP15 TP15Document1 pageVin Vout: TP13 TP13 TP12 TP12 TP14 TP14 TP15 TP15Varun Kumar ChillaNo ratings yet

- Obrero 10 30 2022 3 S1Document1 pageObrero 10 30 2022 3 S1Jayson Ayon MendozaNo ratings yet

- OnlyDocument3 pagesOnlyNgọc AnhNo ratings yet

- [HH] KIT STM32F103C8T6 Bản StartDocument1 page[HH] KIT STM32F103C8T6 Bản StartKhang Bùi TấnNo ratings yet

- Decanter Power and Control Wiring DrawingDocument6 pagesDecanter Power and Control Wiring DrawingPrachi DongreNo ratings yet

- Rane DC22 CompDocument3 pagesRane DC22 CompRobert MorrisNo ratings yet

- VDC Input: See ManualDocument1 pageVDC Input: See ManualherlianajayaNo ratings yet

- SO DO KIT TN nguyen ly V3.0Document40 pagesSO DO KIT TN nguyen ly V3.0Bảo HoàngNo ratings yet

- VI200Document1 pageVI200mikeNo ratings yet

- Rsag78204737 Roh Fuente LCD DiagramaDocument2 pagesRsag78204737 Roh Fuente LCD DiagramaNatal2i2100% (1)

- Fill Your Glass With Gold-When It's Half-Full or Even Completely ShatteredFrom EverandFill Your Glass With Gold-When It's Half-Full or Even Completely ShatteredNo ratings yet

- LDORF - Out (200ma) : TendaDocument12 pagesLDORF - Out (200ma) : TendaOlegNo ratings yet

- N/A W3002R Common Product: Product Name:: TendaDocument12 pagesN/A W3002R Common Product: Product Name:: TendaOlegNo ratings yet

- Schematics-478020 RouterDocument5 pagesSchematics-478020 RouterALFONZO DANIELNo ratings yet

- Remove R107 If SI9435 Is Used: AMC34063ADMTDocument8 pagesRemove R107 If SI9435 Is Used: AMC34063ADMTOlegNo ratings yet

- Maximizing signal reception with an adjustable LNA circuitDocument1 pageMaximizing signal reception with an adjustable LNA circuitALFONZO DANIELNo ratings yet

- Schematic 8 129001Document1 pageSchematic 8 129001OlegNo ratings yet

- 1) Move C1013 Out of Shield (Layout) 2) Swap D132 and D143 (Layout) 3) Add R25 For R3000 (Schemaitc and Layout) 4) Change C51 To Through HoleDocument17 pages1) Move C1013 Out of Shield (Layout) 2) Swap D132 and D143 (Layout) 3) Add R25 For R3000 (Schemaitc and Layout) 4) Change C51 To Through HoleOlegNo ratings yet

- Schematic 7 129000Document1 pageSchematic 7 129000OlegNo ratings yet

- Revision History: Module Number 4 LAN+1 WAN+2.4G 2T2R+5G Low Band 2T2R+5G High Band 4T4R +Wps+Reset+Power DIR-3060Document23 pagesRevision History: Module Number 4 LAN+1 WAN+2.4G 2T2R+5G Low Band 2T2R+5G High Band 4T4R +Wps+Reset+Power DIR-3060OlegNo ratings yet

- Schematics 1501010Document9 pagesSchematics 1501010OlegNo ratings yet

- Manual Testing Interview Questions 1704361238Document187 pagesManual Testing Interview Questions 1704361238DrushtidesaiNo ratings yet

- Download ebook Javascript A Beginners Guide Fifth Edition Pdf full chapter pdfDocument67 pagesDownload ebook Javascript A Beginners Guide Fifth Edition Pdf full chapter pdfroberto.duncan209100% (25)

- Embunit User GuideDocument42 pagesEmbunit User GuidesashokcsNo ratings yet

- Scheduling, Preemption and Eviction - KubernetesDocument66 pagesScheduling, Preemption and Eviction - KubernetesFantahun FkadieNo ratings yet

- Strategic Management AssignmentDocument37 pagesStrategic Management AssignmentYashiNo ratings yet

- Sound Particles Manual Version 1.0Document29 pagesSound Particles Manual Version 1.0Caterina PapouliaNo ratings yet

- Module 14Document5 pagesModule 14camille nina jane navarroNo ratings yet

- Adaptive Object-Model Evolution PatternsDocument20 pagesAdaptive Object-Model Evolution Patternsbonip15716No ratings yet

- Python KNC402-2023 (Notes)Document51 pagesPython KNC402-2023 (Notes)Ananya DubeyNo ratings yet

- Use Case DiagramDocument26 pagesUse Case DiagramHamid AliNo ratings yet

- 4 - 2 - Cyber SecurityDocument21 pages4 - 2 - Cyber SecurityLogin TechbdNo ratings yet

- A Study On Customer Satisfaction On Digital Marketing in Online Advertising CompanyDocument109 pagesA Study On Customer Satisfaction On Digital Marketing in Online Advertising Companysonaiya software solutionsNo ratings yet

- Practice 2Document2 pagesPractice 2TTHUNDERBOLTTNo ratings yet

- Jainam Bhavsar: Career ObjectiveDocument1 pageJainam Bhavsar: Career ObjectivejenniferNo ratings yet

- Software ListDocument23 pagesSoftware ListMohammad Bilal SagerNo ratings yet

- Order Capture Exercise GuideDocument75 pagesOrder Capture Exercise Guidemarcin lipiecNo ratings yet

- XVR4104 4108 4116HSDocument3 pagesXVR4104 4108 4116HSWilmar Salgado CañateNo ratings yet

- Linux Commands Cheat Sheet - LinuxForDevicesDocument5 pagesLinux Commands Cheat Sheet - LinuxForDevicesAlain AranaNo ratings yet

- Lecture 18-20Document25 pagesLecture 18-20minimailNo ratings yet

- CrystalMIND UsersGuideDocument74 pagesCrystalMIND UsersGuideDarlan FerreiraNo ratings yet

- BCMI Lab 3.4.2 Complete A Crisis EventDocument14 pagesBCMI Lab 3.4.2 Complete A Crisis EventFeier BogdanNo ratings yet

- Bank Management System ProjectDocument33 pagesBank Management System ProjectPrateek DubeyNo ratings yet

- Windows Sys InfoDocument271 pagesWindows Sys InfoMostafa NouhNo ratings yet

- FDS2022Apr Week 07 - 2. Data Privacy & Computer EthicsDocument4 pagesFDS2022Apr Week 07 - 2. Data Privacy & Computer EthicsTravis TeohNo ratings yet

- It0041Document3 pagesIt0041JAGDISH HARINo ratings yet

- Manual DAQ970A-DAQ973A - Eng - TdsDocument42 pagesManual DAQ970A-DAQ973A - Eng - TdsjanomirNo ratings yet

- Fatigue Analysis (Damage Calculation) Using S-N ApproachDocument7 pagesFatigue Analysis (Damage Calculation) Using S-N ApproachdhanrajNo ratings yet

- Takebishi DeviceXPlorer OPC Server BrochureDocument20 pagesTakebishi DeviceXPlorer OPC Server BrochureRazvan FilipNo ratings yet

- ProcessesDocument2 pagesProcessesmansi bavliyaNo ratings yet

- How To Edit Config Files in UbuntuDocument8 pagesHow To Edit Config Files in UbuntuVeera ManickamNo ratings yet

![[HH] KIT STM32F103C8T6 Bản Start](https://imgv2-1-f.scribdassets.com/img/document/721664121/149x198/67c3560e94/1712717492?v=1)