Professional Documents

Culture Documents

1K/2K/4K Spi Serial Cmos Eeprom Features: Logen Free

Uploaded by

Diab ChekkalOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

1K/2K/4K Spi Serial Cmos Eeprom Features: Logen Free

Uploaded by

Diab ChekkalCopyright:

Available Formats

GEN FR

ALO

EE

CAT25010/20/40

H

1K/2K/4K SPI Serial CMOS EEPROM

LE

A D F R E ETM

FEATURES

■ 1,000,000 program/erase cycles

■ 10 MHz SPI compatible

■ 100 year data retention

■ 1.8 to 6.0 volt operation

■ Self-timed write cycle

■ Hardware and software protection

■ 8-Pin DIP/SOIC, 8-Pin TSSOP and 8-Pin MSOP

■ Low power CMOS technology

■ 16-byte page write buffer

■ SPI modes (0,0 & 1,1)*

■ Block write protection

■ Commercial, industrial, automotive and extended

temperature ranges – Protect 1/4, 1/2 or all of EEPROM array

DESCRIPTION

Chip Select, the clock input (SCK), data in (SI) and data

The CAT25010/20/40 is a 1K/2K/4K Bit SPI Serial out (SO) are required to access the device. The HOLD

CMOS EEPROM internally organized as 128x8/256x8/ pin may be used to suspend any serial communication

512x8 bits. Catalyst’s advanced CMOS Technology without resetting the serial sequence. The CAT25010/

substantially reduces device power requirements. The 20/40 is designed with software and hardware write

CAT25010/20/40 features a 16-byte page write buffer. protection features including Block Write protection. The

The device operates via the SPI bus serial interface and device is available in 8-pin DIP, 8-pin SOIC, 8-pin MSOP

is enabled though a Chip Select (CS). In addition to the and 8-pin TSSOP packages.

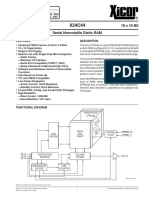

PIN CONFIGURATION BLOCK DIAGRAM

SOIC Package (S, V) MSOP Package (R, Z)*

CS 1 8 VCC SENSE AMPS

CS 1 8 VCC

SO 2 7 HOLD SHIFT REGISTERS

SO 2 7 HOLD WP 3 6 SCK

3 6 SCK VSS 4 5 SI

WP

VSS 4 5 SI *CAT 25010/20 only COLUMN

WORD ADDRESS

BUFFERS DECODERS

DIP Package (P, L) TSSOP Package (U, Y)

CS 1 8 VCC CS 1 8 VCC SO I/O

SO 2 7

SO 2 7 HOLD HOLD SI CONTROL

CONTROL LOGIC

WP 3 6 SCK

WP 3 6 SCK

VSS 4 5 SI CS E2PROM

VSS 4 5 SI SPI XDEC

WP ARRAY

CONTROL

HOLD LOGIC

PIN FUNCTIONS SCK

Pin Name Function BLOCK

PROTECT

SO Serial Data Output LOGIC

SCK Serial Clock DATA IN

STORAGE

WP Write Protect

VCC +1.8V to +6.0V Power Supply HIGH VOLTAGE/

TIMING CONTROL

VSS Ground STATUS

REGISTER

25C128 F02

CS Chip Select

SI Serial Data Input

HOLD Suspends Serial Input

NC No Connect

* Other SPI modes available on request.

© 2004 by Catalyst Semiconductor, Inc. Doc. No. 1006, Rev. L

Characteristics subject to change without notice 1

CAT25010/20/40

ABSOLUTE MAXIMUM RATINGS* *COMMENT

Temperature Under Bias ................. –55°C to +125°C Stresses above those listed under “Absolute Maximum

Storage Temperature ....................... –65°C to +150°C Ratings” may cause permanent damage to the device.

These are stress ratings only, and functional operation

Voltage on any Pin with of the device at these or any other conditions outside of

Respect to VSS(1) .................. –2.0V to +VCC +2.0V those listed in the operational sections of this specifica-

VCC with Respect to VSS ................................ –2.0V to +7.0V tion is not implied. Exposure to any absolute maximum

rating for extended periods may affect device perfor-

Package Power Dissipation mance and reliability.

Capability (Ta = 25°C) ................................... 1.0W

Lead Soldering Temperature (10 secs) ............ 300°C

Output Short Circuit Current(2) ........................ 100 mA

RELIABILITY CHARACTERISTICS

Symbol Parameter Min. Max. Units Reference Test Method

NEND (3) Endurance 1,000,000 Cycles/Byte MIL-STD-883, Test Method 1033

TDR(3) Data Retention 100 Years MIL-STD-883, Test Method 1008

VZAP (3) ESD Susceptibility 2000 Volts MIL-STD-883, Test Method 3015

ILTH(3)(4) Latch-Up 100 mA JEDEC Standard 17

D.C. OPERATING CHARACTERISTICS

VCC = +1.8V to +6.0V, unless otherwise specified.

Limits

Symbol Parameter Min. Typ. Max. Units Test Conditions

ICC1 Power Supply Current 5 mA VCC = 5V @ 5MHz

(Operating Write) SO=open; CS=Vss

ICC2 Power Supply Current 3 mA VCC = 5.5V

(Operating Read) FCLK = 5MHz

ISB(6) Power Supply Current 1 µA CS = VCC

(Standby) VIN = VSS or VCC

ILI Input Leakage Current 2 µA VIN = VSS or VCC

ILO Output Leakage Current 3 µA VOUT = 0V to VCC,

CS = 0V

VIL(5) Input Low Voltage -1 VCC x 0.3 V

VIH(5) Input High Voltage VCC x 0.7 VCC + 0.5 V

VOL1 Output Low Voltage 0.4 V 2.7V≤VCC<5.5V

IOL = 3.0mA

VOH1 Output High Voltage VCC - 0.8 V

IOH = -1.6mA

VOL2 Output Low Voltage 0.2 V 1.8V≤VCC<2.7V

VOH2 Output High Voltage VCC-0.2 V IOL = 150µA

IOH = -100µA

Note:

(1) The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DC

voltage on output pins is VCC +0.5V, which may overshoot to VCC +2.0V for periods of less than 20 ns.

(2) Output shorted for no more than one second. No more than one output shorted at a time.

(3) This parameter is tested initially and after a design or process change that affects the parameter.

(4) Latch-up protection is provided for stresses up to 100 mA on address and data pins from –1V to VCC +1V.

(5) VIL min and VIH max are reference values only and are not tested.

(6) Maximum standby current (ISB ) = 10µA for the Automotive and Extended Automotive temperature range.

Doc. No. 1006, Rev. L

2

CAT25010/20/40

PIN CAPACITANCE (1)

Applicable over recommended operating range from TA=25˚C, f=1.0 MHz, VCC=+5.0V.

Symbol Test Conditions Max. Units Conditions

COUT Output Capacitance (SO) 8 pF VOUT=0V

CIN Input Capacitance (CS, SCK, SI, WP, HOLD) 6 pF VIN=0V

A.C. CHARACTERISTICS

Limits

1.8V-6.0V 2.5V-6.0V 4.5V-5.5V Test

SYMBOL PARAMETER Min. Max. Min. Max. Min. Max. UNITS Conditions

tSU Data Setup Time 50 20 20 ns VIH = 2.4V

tH Data Hold Time 50 20 20 ns CL = 100pF

tWH SCK High Time 250 75 40 ns VOL = 0.8V

tWL SCK Low Time 250 75 40 ns VOH = 2.0v

fSCK Clock Frequency DC 1 DC 5 DC 10 MHz

tLZ HOLD to Output Low Z 50 50 50 ns

tRI(1) Input Rise Time 2 2 2 µs

tFI(1) Input Fall Time 2 2 2 µs

tHD HOLD Setup Time 100 40 40 ns

tCD HOLD Hold Time 100 40 40 ns CC

L L==100pF

50pF

tWC(3) Write Cycle Time 5 5 5 ms (note 2)

tV Output Valid from Clock Low 250 75 40 ns

tHO Output Hold Time 0 0 0 ns

tDIS Output Disable Time 250 75 75 ns

tHZ HOLD to Output High Z 150 50 50 ns

tCS CS High Time 500 100 100 ns

tCSS CS Setup Time 500 100 100 ns

tCSH CS Hold Time 500 100 100 ns

tWPS WP Setup Time 150 50 50 ns

tWPH WP Hold Time 150 50 50 ns

NOTE:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

(2) AC Test Conditions:

Input Pulse Voltages: 0.3VCC to 0.7VCC

Input rise and fall times: ≤10ns

Input and output reference voltages: 0.5VCC

Output load: current source IOL max/IOH max; CL=50pF

(3) tWC is the time from the rising edge of CS after a valid write sequence to the end of the internal write cycle.

Doc. No. 1006, Rev. L

3

CAT25010/20/40

FUNCTIONAL DESCRIPTION the operation to be performed.

The CAT25010/20/40 supports the SPI bus data

transmission protocol. The synchronous Serial Peripheral PIN DESCRIPTION

Interface (SPI) helps the CAT25010/20/40 to interface SI: Serial Input

directly with many of today’s popular microcontrollers. SI is the serial data input pin. This pin is used to input all

The CAT25010/20/40 contains an 8-bit instruction opcodes, byte addresses, and data to be written to the

register. (The instruction set and the operation codes CAT25010/20/40. Input data is latched on the rising

are detailed in the instruction set table) edge of the serial clock for SPI modes (0, 0 & 1, 1).

After the device is selected with CS going low, the first SO: Serial Output

byte will be received. The part is accessed via the SI pin, SO is the serial data output pin. This pin is used to

with data being clocked in on the rising edge of SCK. transfer data out of the CAT25010/20/40. During a read

The first byte contains one of the six op-codes that define cycle, data is shifted out on the falling edge of the serial

Figure 1. Sychronous Data Timing

tCS

VIH

CS

VIL

tCSH

tCSS

VIH

SCK tWH tWL

VIL

tSU tH

VIH

SI VALID IN

VIL

tRI

tFI

tV tHO tDIS

VOH HI-Z HI-Z

SO

VOL

Note: Dashed Line= mode (1, 1) – – – – –

INSTRUCTION SET

Instruction Opcode Operation

WREN 0000 0110 Enable Write Operations

WRDI 0000 0100 Disable Write Operations

RDSR 0000 0101 Read Status Register

WRSR 0000 0001 Write Status Register

READ 0000 X011(1) Read Data from Memory

WRITE 0000 X010(1) Write Data to Memory

Power-Up Timing(2)(3)

Symbol Parameter Max. Units

tPUR Power-up to Read Operation 1 ms

tPUW Power-up to Write Operation 1 ms

Note:

(1) X=0 for 25010, 25020. X=A8 for 25040

(2) This parameter is tested initially and after a design or process change that affects the parameter.

(3) tPUR and tPUW are the delays required from the time VCC is stable until the specified operation can be initiated.

Doc. No. 1006, Rev. L

4

CAT25010/20/40

clock for SPI modes (0,0 & 1,1). WP

WP: Write Protect

WP is the Write Protect pin. The Write Protect pin will

SCK: Serial Clock allow normal read/write operations when held high.

SCK is the serial clock pin. This pin is used to synchronize When WP is tied low all write operations are inhibited.

the communication between the microcontroller and the WP held low while CS is low will interrupt a write to the

CAT25010/20/40. Opcodes, byte addresses, or data CAT25010/20/40. If the internal write cycle has already

present on the SI pin are latched on the rising edge of the been initiated, WP going low will have no effect on any

SCK. Data on the SO pin is updated on the falling edge write operation. Figure 10 illustrates the WP timing

of the SCK for SPI modes (0,0 & 1,1) . sequence during a write operation.

CS

CS: Chip Select HOLD

HOLD: Hold

CS is the Chip select pin. CS low enables the CAT25010/ The HOLD pin is used to pause transmission to the

20/40 and CS high disables the CAT25010/20/40. CS CAT25010/20/40 while in the middle of a serial sequence

high takes the SO output pin to high impedance and without having to re-transmit entire sequence at a later

forces the devices into a Standby Mode (unless an time. To pause, HOLD must be brought low while SCK

internal write operation is underway) The CAT25010/ is low. The SO pin is in a high impedance state during

20/40 draws ZERO current in the Standby mode. A high the time the part is paused, and transitions on the SI pins

to low transition on CS is required prior to any sequence will be ignored. To resume communication, HOLD is

being initiated. A low to high transition on CS after a valid brought high, while SCK is low. (HOLD should be held

write sequence is what initiates an internal write cycle. high any time this function is not being used.) HOLD may

be tied high directly to VCC or tied to VCC through a

resistor. Figure 9 illustrates hold timing sequence.

STATUS REGISTER

7 6 5 4 3 2 1 0

1 1 1 1 BP1 BP0 WEL RDY

BLOCK PROTECTION BITS

Status Register Bits Array Address Protection

BP1 BP0 Protected

0 0 None No Protection

0 1 25010: 60-7F Quarter Array Protection

25020: C0-FF

25040: 180-1FF

1 0 25010: 40-7F Half Array Protection

25020: 80-FF

25040: 100-1FF

1 1 25010: 00-7F Full Array Protection

25020: 00-FF

25040: 000-1FF

Doc. No. 1006, Rev. L

5

CAT25010/20/40

STATUS REGISTER DEVICE OPERATION

The Status Register indicates the status of the device. Write Enable and Disable

The RDY (Ready) bit indicates whether the CAT25010/ The CAT25010/20/40 contains a write enable latch. This

20/40 is busy with a write operation. When set to 1 a latch must be set before any write operation. The device

write cycle is in progress and when set to 0 the device powers up in a write disable state when Vcc is applied.

indicates it is ready. This bit is read only. The WEL (Write WREN instruction will enable writes (set the latch) to the

Enable) bit indicates the status of the write enable latch. device. If WP pin is held low, the write enable latch is

When set to 1, the device is in a Write Enable state and reset to the write disabe state, regardless of the WREN

when set to 0 the device is in a Write Disable state. The Instruction. WRDI instruction will disable writes (reset

WEL bit can only be set by the WREN instruction and can the latch) to the device. Disabling writes will protect the

be reset by the WRDI instruction. device against inadvertent writes.

The BP0 and BP1 (Block Protect) bits indicate which READ Sequence

blocks are currently protected. These bits are set by the The part is selected by pulling CS low. The 8-bit read

user issuing the WRSR instruction. The user is allowed instruction is transmitted to the CAT25010/20/40, followed

to protect quarter of the memory, half of the memory or by the 8-bit address for CAT25010/20/40 (for the 25040,

the entire memory by setting these bits. Once protected, bit 3 of the read data instruction contains address A8).

the user may only read from the protected portion of the

array. These bits are non-volatile. After the correct read instruction and address are sent,

the data stored in the memory at the selected address is

shifted out on the SO pin. The data stored in the memory

at the next address can be read sequentially by continuing

Figure 2. WREN Instruction Timing

CS

SK

SI 0 0 0 0 0 1 1 0

HIGH IMPEDANCE

SO

Note: Dashed Line= mode (1, 1) – – – – –

Figure 3. WRDI Instruction Timing

CS

SK

SI 0 0 0 0 0 1 0 0

HIGH IMPEDANCE

SO

Note: Dashed Line= mode (1, 1) – – – – –

Doc. No. 1006, Rev. L

6

CAT25010/20/40

to provide clock pulses. The internal address pointer is WRITE Sequence

automatically incremented to the next higher address The CAT25010/20/40 powers up in a Write Disable

after each byte of data is shifted out. When the highest state. Prior to any write instructions, the WREN instruction

address is reached, the address counter rolls over to must be sent to CAT25010/20/40. The device goes into

0000h allowing the read cycle to be continued indefinitely. Write enable state by pulling the CS low and then

The read operation is terminated by pulling the CS high. clocking the WREN instruction into CAT25010/20/40.

To read the status register, RDSR instruction should be The CS must be brought high after the WREN instruction

sent. The contents of the status register are shifted out to enable writes to the device. If the write operation is

on the SO line. The status register may be read at any initiated immediately after the WREN instruction without

time even during a write cycle. Read sequece is CS being brought high, the data will not be written to the

illustrated in Figure 4. Reading status register is illustrated

in Figure 5.

Figure 4. Read Instruction Timing

CS

0 1 2 3 4 5 6 7 8 9 10 20 21 22 23 24 25 26 27 28 29 30

SK

OPCODE

SI 0 0 0 0 0 0 1 1 BYTE ADDRESS*

DATA OUT

HIGH IMPEDANCE

SO 7 6 5 4 3 2 1 0

MSB

*Please check the instruction set table for address

Figure 5. RDSR Instruction Timing

CS

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14

SCK

OPCODE

SI 0 0 0 0 0 1 0 1

DATA OUT

HIGH IMPEDANCE

SO 7 6 5 4 3 2 1 0

MSB

Note: Dashed Line= mode (1, 1) – – – – –

Doc. No. 1006, Rev. L

7

CAT25010/20/40

array because the write enable latch will not have been device is ready for the next instruction

properly set. Also, for a successful write operation the

address of the memory location(s) to be programmed Page Write

must be outside the protected address field location The CAT25010/20/40 features page write capability.

selected by the block protection level. After the initial byte, the host may continue to write up to

16 bytes of data to the CAT25010/20/40. After each

Byte Write byte of data received, lower order address bits are

Once the device is in a Write Enable state, the user may internally incremented by one; the high order bits of

proceed with a write sequence by setting the CS low, address will remain constant. The only restriction is that

issuing a write instruction via the SI line, followed by the the X (X=16 for CAT25010/20/40) bytes must reside on

8-bit address for 25010/20/40 (for the 25040, bit 3 of the the same page. If the address counter reaches the end

read data instruction contains address A8). Programming of the page and clock continues, the counter will “roll

will start after the CS is brought high. Figure 6 illustrates over” to the first address of the page and overwrite any

byte write sequence. data that may have been written. The CAT25010/20/40

is automatically returned to the write disable state at the

During an internal write cycle, all commands will be completion of the write cycle. Figure 8 illustrates the

ignored except the RDSR (Read Status Register) page write sequence.

instruction.

To write to the status register, the WRSR instruction

The Status Register can be read to determine if the write should be sent. Only Bit 2 and Bit 3 of the status register

cycle is still in progress. If Bit 0 of the Status Register is can be written using the WRSR instruction. Figure 7

set at 1, write cycle is in progress. If Bit 0 is set at 0, the illustrates the sequence of writing to status register.

Figure 6. Write Instruction Timing

CS

0 1 2 3 4 5 6 7 8 21 22 23 24 25 26 27 28 29 30 31

SK

OPCODE DATA IN

SI 0 0 0 0 0 0 1 0 ADDRESS D7 D6 D5 D4 D3 D2 D1 D0

HIGH IMPEDANCE

SO

Note: Dashed Line= mode (1, 1) – – – – –

*X=0 for 25010, 25020 ; X=A8 for 25040

Figure 7. WRSR Timing

CS

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

SCK

OPCODE DATA IN

SI 0 0 0 0 0 0 0 1 7 6 5 4 3 2 1 0

MSB

HIGH IMPEDANCE

SO

Note: Dashed Line= mode (1, 1) – – – – –

Doc. No. 1006, Rev. L

8

CAT25010/20/40

DESIGN CONSIDERATIONS

The CAT250140/20/40 powers up in a write disable SO is in a high impedance. If an invalid op code is

state and in a low power standby mode. A WREN received, no data will be shifted into the CAT250140/

instruction must be issued to perform any writes to the 20/40, and the serial output pin (SO) will remain in a

device after power up. Also,on power up CS should be high impedance state until the falling edge of CS is

brought low to enter a ready state and receive an detected again.

instruction. After a successful byte/page write or status

register write, the CAT250140/20/40 goes into a write When powering down, the supply should be taken down

disable mode. CS must be set high after the proper to 0V, so that the CAT250140/20/40 will be reset when

number of clock cycles to start an internal write cycle. power is ramped back up. If this is not possible, then,

Access to the array during an internal write cycle is following a brown-out episode, the CAT250140/20/40

ignored and programming is continued. On power up, can be reset by refreshing the contents of the Status

Register (See Application Note AN10).

Figure 8. Page Write Instruction Timing

CS

0 1 2 3 4 5 6 7 8 13 14 15 16-23 24-31 16+(N-1)x8-1..16+(N-1)x8 16+Nx8-1

SK

BYTE ADDRESS DATA IN

OPCODE

Data Data Data Data Byte N

SI 0 0 0 0 0

X* 0 1 0 A7 A0 Byte 1 Byte 2 Byte 3 7..1 0

HIGH IMPEDANCE

SO

Note: Dashed Line= mode (1, 1) – – – – – *X=0 for 25010, 25020 ; X=A8 for 25040

Figure 9. HOLD Timing

CS

tCD tCD

SCK

tHD

tHD

HOLD

tHZ

HIGH IMPEDANCE

SO

tLZ

Note: Dashed Line= mode (1, 1) – – – – –

Doc. No. 1006, Rev. L

9

CAT25010/20/40

Figure 10. WP Timing

t WPS t WPH

CS

SCK

WP

WP

Note: Dashed Line= mode (1, 1) – – – – –

ORDERING INFORMATION

Prefix Device # Suffix

CAT 25040 S I -1.8 TE13

Optional Product Temperature Range Tape & Reel

Company ID Number Blank = Commercial (0°C to +70°C) TE13: 2000/Reel

25040: 4K I = Industrial (-40°C to +85°C)

25020: 2K A = Automotive (-40°C to +105°C)

25010: 1K E = Extended (-40°C to +125°C)

Package

P = 8-pin PDIP Operating Voltage

R = 8-pin MSOP2 Blank (Vcc=2.5 to 6.0V)

S = 8-pin SOIC 1.8 (Vcc=1.8 to 6.0V)

U = 8-pin TSSOP

L = PDIP (Lead free, Halogen free)

V = SOIC, JEDEC (Lead free, Halogen free)

Y = TSSOP (Lead free, Halogen free)

Z = MSOP2 (Lead free, Halogen free)

Notes:

(1) The device used in the above example is a 25040SI-1.8TE13 (SOIC, Industrial Temperature, 1.8 Volt to 6 Volt Operating Voltage,

Tape & Reel)

(2) CAT25010, CAT25020 only

Doc. No. 1006, Rev. L

10

CAT25010/20/40

REVISION HISTORY

Date Rev. Reason

8/3/2004 L Updated Features

Updated DC Operating Characteristics table & notes

Copyrights, Trademarks and Patents

Trademarks and registered trademarks of Catalyst Semiconductor include each of the following:

DPP ™ AE2 ™

Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products. For a complete list of patents

issued to Catalyst Semiconductor contact the Company’s corporate office at 408.542.1000.

CATALYST SEMICONDUCTOR MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS

PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE

RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING

OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.

Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or

other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a

situation where personal injury or death may occur.

Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets

labeled "Advance Information" or "Preliminary" and other products described herein may not be in production or offered for sale.

Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate

typical semiconductor applications and may not be complete.

Catalyst Semiconductor, Inc.

Corporate Headquarters

1250 Borregas Avenue

Sunnyvale, CA 94089

Phone: 408.542.1000 Publication #: 1006

Fax: 408.542.1200 Revison: L

www.catalyst-semiconductor.com Issue date: 8/3/04

Doc. No. 1006, Rev. L

11

You might also like

- CAT25C11/03/05/09/17: 1K/2K/4K/8K/16K SPI Serial CMOS E Prom FeaturesDocument10 pagesCAT25C11/03/05/09/17: 1K/2K/4K/8K/16K SPI Serial CMOS E Prom FeaturesAgnaldo Oliveira SantosNo ratings yet

- CAT25C32/64: 32K/64K-Bit SPI Serial CMOS E Prom FeaturesDocument9 pagesCAT25C32/64: 32K/64K-Bit SPI Serial CMOS E Prom FeaturesTeyfik koyuncuNo ratings yet

- 25c256ke PDFDocument11 pages25c256ke PDFMizael Medeiros dos SantosNo ratings yet

- Atmel DatasheetDocument27 pagesAtmel DatasheetKhoa DangNo ratings yet

- GD25LQ40 Rev1.5Document63 pagesGD25LQ40 Rev1.5mirage0706No ratings yet

- CAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromDocument11 pagesCAT24WC32/64: 32K/64K-Bit I C Serial Cmos EepromAdnen GuedriaNo ratings yet

- 4M-BIT CMOS SERIAL FLASH MEMORYDocument44 pages4M-BIT CMOS SERIAL FLASH MEMORYJairo GuerraNo ratings yet

- Atmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetDocument20 pagesAtmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetalaitsevNo ratings yet

- SST25VF080B: 8 Mbit SPI Serial FlashDocument32 pagesSST25VF080B: 8 Mbit SPI Serial Flashantonio joseNo ratings yet

- CXP82316 - I.C.Document20 pagesCXP82316 - I.C.Andre BaezNo ratings yet

- At25128b 5eb PDFDocument22 pagesAt25128b 5eb PDFMurat BaybükeNo ratings yet

- FM24C08U/09U - 8K-Bit Standard 2-Wire Bus Interface Serial EEPROMDocument15 pagesFM24C08U/09U - 8K-Bit Standard 2-Wire Bus Interface Serial EEPROMlord_beast2.05No ratings yet

- AT25080A, 160A, 320A, 640A Rev04Document23 pagesAT25080A, 160A, 320A, 640A Rev04Bobby HancockNo ratings yet

- CAT24WC01/02/04/08/16: 1K/2K/4K/8K/16K-Bit Serial E Prom FeaturesDocument10 pagesCAT24WC01/02/04/08/16: 1K/2K/4K/8K/16K-Bit Serial E Prom FeaturesAgustin AndrokaitesNo ratings yet

- 24WC01 PDFDocument10 pages24WC01 PDFneko1212121515123001No ratings yet

- Spi Eeprom PDFDocument44 pagesSpi Eeprom PDFEma HarmaNo ratings yet

- A25L016 Series: 16mbit Low Voltage, Serial Flash Memory With 100Mhz Uniform 4Kb SectorsDocument41 pagesA25L016 Series: 16mbit Low Voltage, Serial Flash Memory With 100Mhz Uniform 4Kb SectorsНиколайNo ratings yet

- Use Gal Devices For New Designs: PALCE16V8 and PALCE16V8Z FamiliesDocument32 pagesUse Gal Devices For New Designs: PALCE16V8 and PALCE16V8Z FamiliesGeorge SimmonsNo ratings yet

- k24c02c K LineDocument20 pagesk24c02c K LineTeman NgopiNo ratings yet

- 25AA640A/25LC640A: 64K SPI Bus Serial EEPROMDocument36 pages25AA640A/25LC640A: 64K SPI Bus Serial EEPROMmarino246No ratings yet

- K6X4016C3F Family Cmos Sram: Document TitleDocument10 pagesK6X4016C3F Family Cmos Sram: Document TitledarezenaNo ratings yet

- MB85RS64V DS501 00015 5v0 E-2515457Document37 pagesMB85RS64V DS501 00015 5v0 E-2515457ManunoghiNo ratings yet

- A25L16P Series: 16 Mbit, Low Voltage, Serial Flash Memory Preliminary With 85Mhz Spi Bus InterfaceDocument38 pagesA25L16P Series: 16 Mbit, Low Voltage, Serial Flash Memory Preliminary With 85Mhz Spi Bus Interfaceyounes bessamNo ratings yet

- X24C44 256 Bit 16 X 16 Bit: Features DescriptionDocument15 pagesX24C44 256 Bit 16 X 16 Bit: Features DescriptionJosé FariaNo ratings yet

- X24C44 256 Bit 16 X 16 Bit: Features DescriptionDocument16 pagesX24C44 256 Bit 16 X 16 Bit: Features DescriptionMarinaBogaoNo ratings yet

- 25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Document31 pages25AA256 25LC256 256K SPI Bus Serial EEPROM 20001822harc2Ken AlonsoNo ratings yet

- X24C44 256 Bit 16 X 16 Bit: Features DescriptionDocument16 pagesX24C44 256 Bit 16 X 16 Bit: Features DescriptionAgustin AndrokaitesNo ratings yet

- Features: 1Mb Serial SPI MRAMDocument21 pagesFeatures: 1Mb Serial SPI MRAMsupNo ratings yet

- 25AA256/25LC256: 256K SPI Bus Serial EEPROMDocument32 pages25AA256/25LC256: 256K SPI Bus Serial EEPROMmelquisedecNo ratings yet

- SPI Serial Eeproms: FeaturesDocument25 pagesSPI Serial Eeproms: FeaturesChrisNo ratings yet

- MB85RS4MT: 8) Bit SPIDocument33 pagesMB85RS4MT: 8) Bit SPI20c552244bNo ratings yet

- Macronix MX25L8005M2C 15G DatasheetDocument44 pagesMacronix MX25L8005M2C 15G DatasheetAlex CrofordNo ratings yet

- CAT28C16A 16 KB CMOS Parallel Eeprom: DescriptionDocument11 pagesCAT28C16A 16 KB CMOS Parallel Eeprom: DescriptionLaboratorio GTO Perú S.A.C.No ratings yet

- MB85RS256: 256 K (32 K 8) Bit SPIDocument20 pagesMB85RS256: 256 K (32 K 8) Bit SPIJC_RoseNo ratings yet

- Cat28f020p 12Document16 pagesCat28f020p 12Carlos MarquesNo ratings yet

- HY628400 HynixSemiconductorDocument9 pagesHY628400 HynixSemiconductorHamidNo ratings yet

- Z94RP Rev 1 2Document45 pagesZ94RP Rev 1 2NDCENo ratings yet

- 25L8005 MxicDocument44 pages25L8005 MxicdgsilvaufgNo ratings yet

- 25AA080C/D, 25LC080C/D: 8K SPI Bus Serial EEPROMDocument28 pages25AA080C/D, 25LC080C/D: 8K SPI Bus Serial EEPROMrudy pumacahuaNo ratings yet

- Features: 128Kb Serial SPI MRAMDocument21 pagesFeatures: 128Kb Serial SPI MRAMsupNo ratings yet

- An Elnec en Isp Seep SpiDocument11 pagesAn Elnec en Isp Seep SpiOsvaltronicoNo ratings yet

- AN93Document307 pagesAN93AhmedNo ratings yet

- 16K Microwire Compatible Serial EEPROM: 93AA86A/B/C, 93LC86A/B/C, 93C86A/B/CDocument27 pages16K Microwire Compatible Serial EEPROM: 93AA86A/B/C, 93LC86A/B/C, 93C86A/B/CJesús GutiérrezNo ratings yet

- IS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromDocument16 pagesIS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromPablo Diego Cecere CasadoNo ratings yet

- IS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromDocument16 pagesIS24C01 IS24C02 IS24C04 IS24C08 IS24C16: 1K-bit/2K-bit/4K-bit/8K-bit/16K-bit 2-Wire Serial Cmos EepromPablo Diego Cecere CasadoNo ratings yet

- Datasheet 25c040Document22 pagesDatasheet 25c040Perona PabloNo ratings yet

- 28f102 Flashable Replacement For 27C1024 or 27C210 PDFDocument14 pages28f102 Flashable Replacement For 27C1024 or 27C210 PDFfedeNo ratings yet

- NM24C04/05 - 4K-Bit Standard 2-Wire Bus Interface Serial EEPROMDocument14 pagesNM24C04/05 - 4K-Bit Standard 2-Wire Bus Interface Serial EEPROMAbel RodriguezNo ratings yet

- 25Q16BSIGDocument34 pages25Q16BSIGRiiandaArifSNo ratings yet

- Serial Eeprom: K24C02 / K24C04 / K24C08 / K24C16Document14 pagesSerial Eeprom: K24C02 / K24C04 / K24C08 / K24C16eliarNo ratings yet

- Hy628100alg 70Document9 pagesHy628100alg 70Claudiney BricksNo ratings yet

- 16Mbit Dual and Quad SPI Flash GD25Q16 FeaturesDocument33 pages16Mbit Dual and Quad SPI Flash GD25Q16 FeaturesErick OliveiraNo ratings yet

- Atmel 8535 Seeprom At25320b 640b DatasheetDocument23 pagesAtmel 8535 Seeprom At25320b 640b DatasheetPaulo Vieira de Lima JrNo ratings yet

- CAT28F010: Licensed Intel Second SourceDocument14 pagesCAT28F010: Licensed Intel Second SourceMorteza BaratzadehNo ratings yet

- YaEwN89a PCA9536Document22 pagesYaEwN89a PCA9536vvvNo ratings yet

- SED1278F/D: Dot Matrix LCD Controller DriverDocument13 pagesSED1278F/D: Dot Matrix LCD Controller DriverWilliam GRNo ratings yet

- 25AA320/25LC320/25C320: 32K Spi Bus Serial EEPROMDocument24 pages25AA320/25LC320/25C320: 32K Spi Bus Serial EEPROMHebertAlexMamaniSalomaNo ratings yet

- 8K/16K 5.0V I C Serial Eeproms: Features Package TypesDocument13 pages8K/16K 5.0V I C Serial Eeproms: Features Package Typesarunan55No ratings yet

- Verilog Lecture NotesDocument92 pagesVerilog Lecture NotesRavi KishoreNo ratings yet

- CMOS Inverter Layout Generation and SimulationDocument19 pagesCMOS Inverter Layout Generation and SimulationRajesh HarikrishnanNo ratings yet

- RAM Module Using CoreGenDocument12 pagesRAM Module Using CoreGenBárbara BabNo ratings yet

- CS302 Midterm Paper - 01Document5 pagesCS302 Midterm Paper - 01Manish RauniyarNo ratings yet

- EEE Software Lab Report On PspiceDocument9 pagesEEE Software Lab Report On PspiceSayem Mahmud (Sym)No ratings yet

- COA Module 3 PART 1Document30 pagesCOA Module 3 PART 1Anirban BhattacharjeeNo ratings yet

- Design of Stopwatch Through Digital Logic Design: December 2019Document5 pagesDesign of Stopwatch Through Digital Logic Design: December 2019Dadan Dadic0% (1)

- Single Bit Full Adder Design Using 8 Transistors With Novel 3 Transistors XNOR GateDocument13 pagesSingle Bit Full Adder Design Using 8 Transistors With Novel 3 Transistors XNOR GateAnonymous e4UpOQEPNo ratings yet

- Execution of Instructions Step-by-StepDocument60 pagesExecution of Instructions Step-by-StepKr RanjithNo ratings yet

- VerilogDocument22 pagesVerilogSyurga FathonahNo ratings yet

- COA - Chapter # 7Document41 pagesCOA - Chapter # 7Set EmpNo ratings yet

- 2SB492 Datasheet, Equivalent, Cross Reference SearchDocument2 pages2SB492 Datasheet, Equivalent, Cross Reference Searchbopak111288No ratings yet

- Ryerson University EE 8502 Analog CMOS Integrated Circuits Final ExaminationDocument7 pagesRyerson University EE 8502 Analog CMOS Integrated Circuits Final ExaminationooohlalalaNo ratings yet

- VHDL Intro: Model Digital DesignsDocument30 pagesVHDL Intro: Model Digital DesignsKamleshNo ratings yet

- TED (21) 3134 QPDocument2 pagesTED (21) 3134 QPSreekanth KuNo ratings yet

- Digital Computers I: Organization and Logical DesignDocument9 pagesDigital Computers I: Organization and Logical Designamittutorials1985No ratings yet

- Verilog ProjectDocument15 pagesVerilog ProjectKent SardinaNo ratings yet

- VHDL KeypadDocument17 pagesVHDL Keypadtroid426No ratings yet

- ULN2803AGPDocument12 pagesULN2803AGPFernando SandovalNo ratings yet

- DLD Assignment 1Document5 pagesDLD Assignment 1Asfand Yar0% (1)

- Step by Step Procedure To Run A Program On FPGA BoardDocument11 pagesStep by Step Procedure To Run A Program On FPGA BoardAdiseshuMiddeNo ratings yet

- Draw A State Diagram 2. Draw A State-Transition Table 3. Encode The Next-State Functions 4. Implement The DesignDocument4 pagesDraw A State Diagram 2. Draw A State-Transition Table 3. Encode The Next-State Functions 4. Implement The DesignairplaneunderwaterNo ratings yet

- Car BaseDocument90 pagesCar BaseJUANNo ratings yet

- E MOSFET WorkingDocument14 pagesE MOSFET WorkingSubhash YadavNo ratings yet

- Khx1600c9ad3k2 4GDocument2 pagesKhx1600c9ad3k2 4GVipul KandivalikarNo ratings yet

- Lecture 18 PDFDocument10 pagesLecture 18 PDFattiqueNo ratings yet

- CPU DesignDocument66 pagesCPU DesignAnonymous 0u4X6mgWPNo ratings yet

- Vlsi Design ReportDocument40 pagesVlsi Design ReportUjjwal DhusiaNo ratings yet

- Computer Instruction Formats ExplainedDocument18 pagesComputer Instruction Formats ExplainedSamriddhiNo ratings yet