Professional Documents

Culture Documents

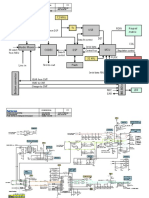

Block Diagram of System/RF Blocks: NSE-3 System Module UP8T

Uploaded by

Владимир КлюевOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Block Diagram of System/RF Blocks: NSE-3 System Module UP8T

Uploaded by

Владимир КлюевCopyright:

Available Formats

System Module UP8T NSE–3

Block Diagram of System/RF Blocks

Original 11/97 3/A3–1

System Module UP8T NSE–3

Circuit Diagram of Baseband (Version 12 Edit 8) for layout version 14

Original 11/97 3/A3–2

System Module UP8T NSE–3

Circuit Diagram of Power Supply (Version 14 Edit 41) for layout version 14

Original 11/97 3/A3–3

System Module UP8T NSE–3

Circuit Diagram of SIM Connectors (Version 14 Edit 9) for layout version 14

Original 11/97 3/A3–4

System Module UP8T NSE–3

Circuit Diagram of CPU Block (Version 14 Edit 23) for layout version 14

NSE–3

(NSE–1)

Original 11/97 3/A3–5

System Module UP8T NSE–3

Circuit Diagram of Audio (Version 14 Edit 27) for layout version 14

Original 11/97 3/A3–6

System Module UP8T NSE–3

Circuit Diagram of IR Module (Version 14 Edit 21) for layout version 14

Original 11/97 3/A3–7

System Module UP8T NSE–3

Circuit Diagram of RF Block (Version 14 Edit 26) for layout version 14

Original 11/97 3/A3–8

System Module UP8T NSE–3

Layout Diagram of UPT8T – Top (Version 14)

testpoint name condition dc–level ac–level testpoint name condition dc–level ac–level

J102 FBUS_RX power on pulsed DC (0V/2.8V) J502 Power control op.amp power level depended

output voltage to N550 pulsed DC

J103 MBUS power on pulsed DC (0V/2.8V)

( Vpd, pin )

J107 LGND 0V

J506 RFC ( 13 MHz sine- 0V typ. 1.0 Vpp min

J110 VPP flash programming nominal 5V (5V flash) or 3.0V wave ) 0.5/max 2.0 Vpp

(3V flash) J510 VRX ( regulated supply 2.8 V min 2.7 / max 2.85 V,

J111 WDDISX power on reset state 0V, normal state 2.8V for RX ) pulsed

J221 5V flash programming nominal 5.0V (5V flash) or 3.0V J514 VTX ( regulated supply 2.8 V min 2.7 / max 2.85 V,

(3V flash) for TX ) pulsed

J222 DSPXF power on pulse active 0V, non–active 2.8V J516 VSYN_1 ( regulated 2.8 V min 2.7 / max 2.85 V

supply for VCOs)

J229 MAD selftest test mode set externally

J518 VREF_2 ( ref. voltage 1.5 V +/– 1.5%

J230 MAD selftest test mode set externally for N500 )

J231 VSIM SIM power on nominal 2.8V (3V SIM card) or J520 AFC ( autom. freq. cntrl 0 – 2.3 V, typ. 1.15 V ( room

5.0V (5V SIM card) ) temp. )

J232 VB (battery voltage in battery connected nominal 3.6V (min 3.0, max 4.2) J522 VXO ( regulated supply 2.8 V min 2.7 / max 2.85 V

baseband) for VCTCXO )

J233 RFCLK active state typ. 1.0Vpp (min J530 71 MHz IF input to –95 dBm @ X540 typ. ca. 1.2 V pulsed typ 100 – 140

0.5Vpp, max & J532 N620 (ext. RF connector ) uVpp balanced

2.0Vpp) voltage at 71

J234 VSRM power on nominal 5.5V (min 5V, max 6V) CCONT switch MHz

mode regulator J540 13 MHz output from –95 dBm @ X540 typ. ca. 1.5 V pulsed typ. ca. 700

ripple voltage N620 to Z620 (ext. RF connector ) uVrms

J236 RAMSELX active state pulse active 0V, non–active 2.8V RXC at level of full

calibrated gain

J250 GND 0V

J550 & 116 MHz TX IF to N500 typ. ca. 1.1 – 1.2 V pulsed typ. ca. 100

J252 COBBARSTX power on reset state 0V, normal state 2.8V J552 mVrms each

J253 COBBAWRX active state pulse active 0V, non–active 2.8V J562 RXC ( receive gain RX gain setting depended control range is 0.5 – 1.45 V,

J254 COBBARDX active state pulse active 0V, non–active 2.8V control voltage ) ,pulsed.

typ. 1.3–1.4 V for calibrated

J255 COBBACLK active state pulsed DC (0V/2.8V) maximum gain

Original 11/97 3/A3–9

System Module UP8T NSE–3

Layout Diagram of UPT8T – Bottom (Version 14)

testpoint name condition dc–level ac–level testpoint name condition dc–level ac–level

J101 FBUS_TX active state pulsed DC (0V72.8V) J500 Control voltage for UHF channel 60 2.25 +/– 0.25 V

VCO module G600 channel 1 > 0.8 V

J104 CCONTCSX (CCONT active state pulse active 0V, non–active

channel 124 < 3.7 V

chip select) 2.8V

J504 Control voltage for VHF typ. 2.0 –2.2 V min 0.5 / max

J108 CHRG_CTRL charger connected pulsed DC (0V/2.8V)

VCO circuit 4.0 V

J220 V5V active state nominal 5.0V (min 4.8V, max

J508 VSYN_2 ( regulated 2.8 V min 2.7 / max 2.85 V

5.2V)

supply for PLLS )

J223 CCONTINT (charger, interrupt pulse active 2.8V, non–active

J534&J5 13 MHz IF output to –95 dBm @ X540 typ ca. 1.0 – 1.1 V pulsed typ. 50 mVpp balanced

RTC interrupt) 0V

36 N250 (ext. RF connector ) min. 0.7 / max. 1.4 V voltage at 13 MHz

J224 VCOBBA active state nominal 2.8V (min 2.7V, max RXC at level of full

2.85V) calibrated gain

J225 EXTSYSRESETX power on reset state 0V, normal state J538 13 MHz output from –95 dBm @ X540 typ. ca. 1.5 V pulsed typ. ca 600 uVrms

2.8V Z620 to N620 (ext. RF connector )

J226 VCXOPWR power on active state 2.8V, non–active RXC at level of full

0V calibrated gain

J227 PURX (power on reset) power up/down reset state 0V, normal state J542 VHF VCO output ( 232 – typ. 400 mVpp.

2.8V MHz ) > 100 mVpp required

J228 SLEEPCLK (32kHz power on pulsed DC (0V/2.8V) J554 TXC ( TX power control @level 19 typ. ca. 0.6 V pulse

clock) voltage ) @level 5 typ ca. 1.8 V pulse

J235 ROM1SELX active state pulse active 0V, non–active J556 TXP ( TX enable ) 2.8 V logic level pulse,

2.8V ( max. 0.8 V ”0” / min 2.0 V ”1” )

J251 AGND pcb ground 0V J558 TXQP ( other half of 0.8 V pulsed 400 mVpp

balanced Q–signal )

J256 COBBADAX active state pulse active 0V, non–active

2.8V J560 TXIP ( other half of bal- 0.8 V pulsed 400 mVpp

anced I–signal )

Original 11/97 3/A3–10

You might also like

- Encl Cyber WarfareDocument367 pagesEncl Cyber WarfareВладимир КлюевNo ratings yet

- Passive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2From EverandPassive and Discrete Circuits: Newnes Electronics Circuits Pocket Book, Volume 2No ratings yet

- TLE4209A Servo BoschDocument14 pagesTLE4209A Servo BoschcarlosyakimchukNo ratings yet

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsFrom EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo ratings yet

- Quick, Cost-Effective Development of Brushed/brushless DC Motor ControllersDocument2 pagesQuick, Cost-Effective Development of Brushed/brushless DC Motor ControllersAditya SrivatsavNo ratings yet

- Block Diagram of System/RF Blocks: NSE-1 System Module UP8RDocument15 pagesBlock Diagram of System/RF Blocks: NSE-1 System Module UP8RCauVong JustinNo ratings yet

- Ezcat Pro V5.3 C&D Software User GuideDocument12 pagesEzcat Pro V5.3 C&D Software User GuideRoberto Agustin Ramos PattersonNo ratings yet

- Nokia 5110Document12 pagesNokia 5110Ionuţ CîrdeiNo ratings yet

- Vibra: Block Diagram of UIFDocument14 pagesVibra: Block Diagram of UIFanjirponselNo ratings yet

- UC3843 ChipsWinnerDocument11 pagesUC3843 ChipsWinnerPareNo ratings yet

- LMK05028 EVM Quick Start GuideDocument35 pagesLMK05028 EVM Quick Start GuideTu PhíNo ratings yet

- Data SheetDocument16 pagesData Sheetcarrei JohnNo ratings yet

- Current Mode PWM Controller Az3842/3/4/5Document13 pagesCurrent Mode PWM Controller Az3842/3/4/5Emmanuel ZambranoNo ratings yet

- Diodes - Inc. AP3842CMTR E1 DatasheetDocument14 pagesDiodes - Inc. AP3842CMTR E1 DatasheetEsteban Elias Marquez EscalanteNo ratings yet

- 2.5 Optional Unit: Port A Port BDocument5 pages2.5 Optional Unit: Port A Port BPhuocTranThienNo ratings yet

- VT-pro 1K-1.5K Service ManualDocument15 pagesVT-pro 1K-1.5K Service ManualCoco Roco100% (1)

- Texas Instrument Gate DriverDocument39 pagesTexas Instrument Gate Driverdev rajanNo ratings yet

- MC33897 (SWC)Document19 pagesMC33897 (SWC)bettinemed2023No ratings yet

- Switch Mode Power Supply With Multiple Linear Regulators: Advance InformationDocument27 pagesSwitch Mode Power Supply With Multiple Linear Regulators: Advance InformationJheremy Sebastian TorresNo ratings yet

- 300ma L.D.O Voltage Regulator Tj1117GsfDocument14 pages300ma L.D.O Voltage Regulator Tj1117GsfkalanghoNo ratings yet

- EnglishDocument4 pagesEnglishoggiNo ratings yet

- Datasheet DMO565RDocument21 pagesDatasheet DMO565RSteve Bravo83% (6)

- RS232 转USB 方案DIY资料,已做成功Document2 pagesRS232 转USB 方案DIY资料,已做成功李宏观No ratings yet

- EM8635 ExcellianceMOSDocument13 pagesEM8635 ExcellianceMOSBruno MartinsNo ratings yet

- Training Material of MT27 Series Chassis 2013jun27 ThurDocument33 pagesTraining Material of MT27 Series Chassis 2013jun27 Thurبوند بوندNo ratings yet

- CE8301 SeriesDocument11 pagesCE8301 SeriesWilly NodaNo ratings yet

- ACT8846 DatasheetDocument44 pagesACT8846 DatasheetsecretobcnNo ratings yet

- cd00000545 1795800Document25 pagescd00000545 1795800Renato Luiz TécnicoNo ratings yet

- Ap3031 PDFDocument17 pagesAp3031 PDFAbel GaunaNo ratings yet

- Fsdm0465re Fsdm0565re Fsdm07652reDocument20 pagesFsdm0465re Fsdm0565re Fsdm07652rejesus cautivoNo ratings yet

- Infineon Bts3408g Ds v01 05 enDocument14 pagesInfineon Bts3408g Ds v01 05 enblessingj19it018No ratings yet

- SLLIMM-nano IPM, 3-phase inverter, 2 A, 1.7 Ω max., 500 V MOSFETDocument20 pagesSLLIMM-nano IPM, 3-phase inverter, 2 A, 1.7 Ω max., 500 V MOSFETРуслан КаргиевNo ratings yet

- Application Note 5531: GNSS Low Noise Amplifier Module (LNA + Filter) With Optional Differential OutputsDocument20 pagesApplication Note 5531: GNSS Low Noise Amplifier Module (LNA + Filter) With Optional Differential OutputsWadh MisNo ratings yet

- Ap2121 PDFDocument21 pagesAp2121 PDFnmo1122No ratings yet

- Dual Channel PWM Controller With Integrated Driver For IMVP8 CPU CORE Power SupplyDocument60 pagesDual Channel PWM Controller With Integrated Driver For IMVP8 CPU CORE Power SupplyDagmar GarciaNo ratings yet

- Wiring Diagrams: VR6 Voltage RegulatorDocument21 pagesWiring Diagrams: VR6 Voltage Regulatorgeorgi15685No ratings yet

- General Description Features: Data SheetDocument23 pagesGeneral Description Features: Data Sheetmemo alfaisalNo ratings yet

- Classc Sim PDFDocument6 pagesClassc Sim PDFmastelecentroNo ratings yet

- Ap 3843 CPDocument13 pagesAp 3843 CPJesus ChaileNo ratings yet

- Powering Your FPGA Applications: White PaperDocument9 pagesPowering Your FPGA Applications: White PaperJeremy VilchezNo ratings yet

- Tps 51650Document51 pagesTps 51650Qomari Ali MustofaNo ratings yet

- Dual-Channel (3-Phase CPU/2-Phase GPU) SVID, D-CAP+ Step-Down Controller For Imvp-7 V With Two Integrated DriversDocument51 pagesDual-Channel (3-Phase CPU/2-Phase GPU) SVID, D-CAP+ Step-Down Controller For Imvp-7 V With Two Integrated DriversJaelaniNo ratings yet

- VT Vrpa1 527 2XV0RTS 2STVDocument8 pagesVT Vrpa1 527 2XV0RTS 2STVpaulaNo ratings yet

- Ap2114h-2 5TRG1Document28 pagesAp2114h-2 5TRG1HauQuyen G530HNo ratings yet

- PQ3RD13: Low Power-Loss Voltage RegulatorDocument3 pagesPQ3RD13: Low Power-Loss Voltage RegulatorBrowsardNo ratings yet

- FT-2200 Serv F6DBL 1993Document125 pagesFT-2200 Serv F6DBL 1993Marcos DanilaviciusNo ratings yet

- Datasheet FSL117MRINDocument15 pagesDatasheet FSL117MRINeurofutabNo ratings yet

- Hochiki H-5001 Rev F FNV 25-50-100 Install (11.07)Document8 pagesHochiki H-5001 Rev F FNV 25-50-100 Install (11.07)eolorojasNo ratings yet

- Microsoft Word - 5011203309-SE09Document1 pageMicrosoft Word - 5011203309-SE09JORGE RODNo ratings yet

- LITIX™ Basic: TLD1314EL 3 Channel High-Side Current SourceDocument28 pagesLITIX™ Basic: TLD1314EL 3 Channel High-Side Current SourceOleg OlegFVNo ratings yet

- Synchronous Buck PWM DC-DC Controller: Fitipower Integrated Technology LNCDocument14 pagesSynchronous Buck PWM DC-DC Controller: Fitipower Integrated Technology LNCEchefisEchefisNo ratings yet

- TDA8587JDocument31 pagesTDA8587JRoolonNo ratings yet

- Max20014 2.2Mhz Sync Boost and Dual Step-Down Converters: General Description Benefits and FeaturesDocument2 pagesMax20014 2.2Mhz Sync Boost and Dual Step-Down Converters: General Description Benefits and Featuresiingos088No ratings yet

- AP2113ADocument12 pagesAP2113AIwak PeyekNo ratings yet

- TT7S10-D XP User ManualDocument2 pagesTT7S10-D XP User ManualnirdosharyaNo ratings yet

- Multi-Phase PWM Controller With PWM-VID Reference: General Description FeaturesDocument24 pagesMulti-Phase PWM Controller With PWM-VID Reference: General Description FeaturesSurendra SharmaNo ratings yet

- ARBO SA. COMMISSIONING - ARBO SE-WLS220-2,1-08 ElektronikaDocument8 pagesARBO SA. COMMISSIONING - ARBO SE-WLS220-2,1-08 ElektronikaTBF1DNo ratings yet

- Usbn9603 28MXDocument62 pagesUsbn9603 28MXEddy SulbaranNo ratings yet

- 7sr1206 Relay ModelDocument1 page7sr1206 Relay ModelSudipto MajumderNo ratings yet

- 1117H PDFDocument24 pages1117H PDFThe RedfireNo ratings yet

- Ti Jane Clift StoryDocument3 pagesTi Jane Clift StoryВладимир КлюевNo ratings yet

- Nokia: ConfidentialDocument12 pagesNokia: ConfidentialВладимир КлюевNo ratings yet

- npm6 Schematics v1 0Document10 pagesnpm6 Schematics v1 0Владимир КлюевNo ratings yet

- NPM5schematics UI V10Document11 pagesNPM5schematics UI V10Владимир КлюевNo ratings yet

- Service Schematics: Exploded View and Component DisposalDocument9 pagesService Schematics: Exploded View and Component DisposalВладимир КлюевNo ratings yet

- RM-74 RM-75 Schematics V2 0Document8 pagesRM-74 RM-75 Schematics V2 0Владимир КлюевNo ratings yet