Professional Documents

Culture Documents

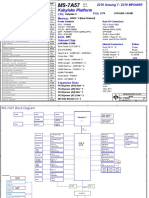

52f2c Foxconn 945P01 PC Mainboard Schematics

Uploaded by

snehalCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

52f2c Foxconn 945P01 PC Mainboard Schematics

Uploaded by

snehalCopyright:

Available Formats

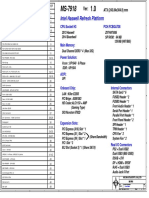

5 4 3 2 1

Page Title of Schematic :

945P01 Rev : 0B D

Page

Title Intel (R) Lakeport-G + ICH7 Chipset

Index Page 1 Intel LGA775 Processor

Topology 2

Reset Map 3

Form Factor Pico BTX

Clock Distribution 4

Power Delivery Map 5 CPU Intel LGA775

Power Sequence 6

System Chipset Intel Lakeport-G (North Bridge)

GPIO / IRQ / IDSEL Map 7 Intel ICH7 (South Bridge)

LGA775 -1 8

On Board Chipset BIOS -- FWH EEPROM

LGA775 -2 9 Codec -- ALC880

LPC Super I/O -- ITE8712F/IX

ICS954128 Clock Gen 10

Remark LAN --Marvell 88E8052

C ACPI Voltage Regulator 11 CLOCK --ICS954128 C

1394--TI TSB43AB22

Lakeport -GMCH -1 12 "Dummy" -> No Stuff

Lakeport -GMCH -2 13 Main Memory 2 DIMM,Dual-Channel DDR2

Lakeport -GMCH -3 14

Expansion Slots PCI Slot * 1

DDR2 Channel A DIMM1 15 Fab A: (Connector) PCI-E X16 Slot * 1

IDE Slot * 1

DDR2 Channel B DIMM2 16 945G SATA Connector * 2 (Two Master)

PCI & PCI-E x16 Slot 17 ICH7 USB Connector * 8 (4 ports on board and 4 ports on Rear I/O)

1394 Connector (1 port on board and 1 port on Rear I/O)

ICH7 -1_DIM,PCI-E,USB,MISC 18

Front Panel, Front Audio, SPDIF-Out, TPM, CD_IN, IrDA, Recovery,

ICH7 -2_IDE,SATA,CPU,FWH 19 Case-Open, WOL, AUX_IN,

FAN Connector (CPUFAN1, CPUFAN2)

ICH7 -3_PCI,Power/ Gnd,FWH 20

MARVELL 88E8052 LAN 21 PWM For CPU VCORE Controller--ISL6561+ISL6614A+ISL6612

ALC880 Azalia Audio-1 22 For 1D5V_CORE Controller--RT9214PS

ALC880 Azalia Audio-2 23

B

Front I/O connector---3 USB ports B

Power / MISC Connectors 24 1 headphone out

SMSC 47M182 SIO KB/MS/FAN 25 1 microphone in

SKU1(8EKS) Rear I/O connectors--1 PS/2 keyboard port, 1 PS/2 mouse port

VGA & Serial / Parallel Con 26

1 VGA, 1 Parallel port, 1 Serial port

TI TSB43AB22 1394 27 2 USB ports + RJ45 port

1394 & Rear-LANUSB Conn 28 6 audio jacks (7.1 HD audio jack)

IEEE 1394 port

VRD10.1 Intersil ISL6561 29

Front I/O connector---4 USB ports

Modify List 30 1 headphone out

SKU1(8KS) 1 microphone in

Rear I/O connectors--1 PS/2 keyboard port, 1 PS/2 mouse port

1 VGA, 1 Parallel port, 1 Serial port

2 USB ports + RJ45 port

6 audio jacks (7.1 HD audio jack)

4 USB ports

A A

FOXCONN PCEG

Title

Index Page

Size Document Number Rev

C 945P01 A

Date: Wednesday, July 20, 2005 Sheet 1 of 30

5 4 3 2 1

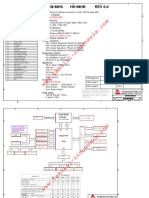

5 4 3 2 1

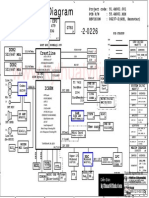

Prescott, Smithfield &

Cedar Mill

VRD 10.1 LGA775 Processor

4 Phase PWM

D Socket T D

For Intel 2005A & Intel 2004B

1066/800/533 FSB

CK-410 Clock

PCI Express x 16 Channel A DDR2

PCI Express x16 Port DDR2 533/667

External Graphics

DIMM1

Card

DIMM2

GMCH DDR2 533/667 Channel B DDR2

VGA Connector

Lakeport DIMM2

C C

Back Panel

USB2.0 Port 1 PCI Express x1 Interface LAN

4 Lanes

USB2.0 Port 2 MARVELL 88E8052

Direct Media Interface (DMI)

USB2.0 Port 3

USB2.0 Port 4

PCI Slot 1

ICH7RW

TI TSB43AB22 1394

Front Panel

USB2.0 Port 5

B

USB2.0 Port 6 B

Header Serial ATA

LPC I/F

SATA Connector 1

USB2.0 Port 7 AHCI, RAID0,1,5,10

ATA100

USB2.0 Port 8 IDE CONN 1 SATA Connector 2

LPC I/F Intel HD Audio

Super I/O Realtek ALC880

IT8712F 8 Channels W/ SPDIF-Out

Firmware HUB

4Mb or 8Mb

PS2 Parallel TPM HEADER

Keyboard / Mouse Serial

A A

FOXCONN PCEG

Title

Topology

Size Document Number Rev

C 945P01 A

Date: Monday, June 13, 2005 Sheet 2 of 30

5 4 3 2 1

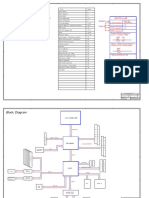

5 4 3 2 1

CPU (Tejas / Prescott)

CPU_PWRGD

CPURST#

D

LGA775 processor D

ATX

Power

PWRGD_3V

PWRGD_PS SIO PWROK CPURST#

PS_ON# Translation

Circuitry GMCH PCI Slost

Lakeport

C

RSTIN# C

TI 1394

ICH7RW

ICH_PWRGD

Marvell LAN

PCIRST#

PLTRST# PCI Express x16

SIO

Front Panel Buffer

PWROK

ATA100

IDE CONN 1

FR_RST SYS_RESET#

B B

SW_ON PWRBTN# AC_RST#

RSMRST#

RST# Audio

RCIN# RST#

SLP_S3# FWH

RST#

TPM

RST#

Power on/off KBRST

circuit RSMRST#

Super IO

SLP_S3#

PSIN

A A

PSOUT#

FOXCONN PCEG

Title

Reset Map

Size Document Number Rev

C 945P01 A

Date: Monday, June 13, 2005 Sheet 3 of 30

5 4 3 2 1

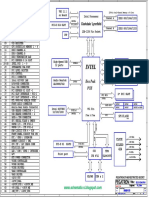

5 4 3 2 1

14.318MHz

CPU XDP

D

CPU 133/200/266 MHz Diff Pair D

XDP 133/200 MHz Diff Pair

MCH 133/200 MHz Diff Pair

DDR2 2 Slots 12 Diff CLKs

PCI Express 100 MHz Diff Pair

PCI Express x16 Gfx Channel A DDR2

GMCH DIMM1

DOT 96 MHz Diff Pair Lakeport DIMM2

Channel B DDR2

DIMM2

PCI Express/DMI 100 MHz Diff Pair

C C

CK-410

PCI Express/DMI 100 MHz Diff Pair

USB/SIO 48 MHz

ICH 33 MHz

REF 14 MHz

FWH 33 MHz FWH

ICH7RW

PCI 33 MHz PCI Slot 1 Azalia Bit Clock

B

PCI 33 MHz IEEE 1394 B

32.768KHz

PCI Express 100 Mhz Diff Pair MARVELL

88E8052 LAN

HD Audio

SIO 14 MHz Super I/O

SATA 100 MHz Diff Pair

A A

TPM 33 MHz TPM

FOXCONN PCEG

Title

CLOCK Distribution

Size Document Number Rev

C 945P01 A

Date: Monday, June 13, 2005 Sheet 4 of 30

5 4 3 2 1

5 4 3 2 1

Voltage Distribution

12V : 12V_SYS 3.3VSB : 3D3V_SB Super I/O

5V : 5V_SYS 1.8VSB : VCC1_8SB

3.3V 3.3V

3.3V : 3D3V_SYS 1.8V for DDR-II : 1_8VSTR

Icc(Max)=50mA

5VSB : 5V_SB_SYS 0.9VTT for DDR-II : VTT_DDR Proceessor

-12V : -12V_SYS 1.5V for ICH and GMCH core : 1D5V_CORE Vccp (CPU Vcore) 3.3SBV

VRD 10.1

for CPU : VCCP 5V_DUAL : 5V_DUAL Voltage=0.8375~1.6V Icc(Max)=50mA(S0)

Switching

2.5V for MCH : 2D5V_MCH Icc(Max)=125A

Four Phase 3.3SBV

D

4-Phases Swithing D

Icc(Max)=38mA(S3)

1.2V FSB

Vtt-5.3A

ATX P/S USB 8 Ports

+5V DUAL=4A(S0, S1)

12V +5V DUAL=20mA(S3)

Lakeport GMCH

5VSB

FSB_Vtt PS2

Linear 1.5V

3.3V 1.2V FSB Vtt +5V DUAL=345mA(S0, S1)

to 1.2V

CK410 6.2A

Icc(Max)=0.9A +5V DUAL=2mA(S3)

5V

Vdd (Core)

3.3V -12V 3.3V FWH

Ivdd(Max)=560mA 1.8V DDR2 I/O=4A(S0,S1)

3.3V=107mA(S0, S1)

1.8V DDR2 I/O= tbd mA(S3)

PCI Express

X16 slot (1)

Vcore (Core Logic)

+12V=5.5A

1.5V

5VDUAL Icc(Max)=13.8A(Integrated) 3.3VSB

C Icc(Max)= Icc(Max)=8.9A(Discrete) Icc(Max)=0.375A(wake) C

DDR2 Channel A/B 4.345A(S0,S1) *1.5V PCIe & DMI 1.5A Icc(Max)=0.02A(no wake)

22mA(S3)

3.3V

+3.3V=3A

Vdd (Core)=1.8V

Ivdd(S0,S1Max)=9.4A(4 2.5V DAC PCI Express

channel) *2.5V DAC=0.07A

Single Phase Switch regulator

2.5V HV=25mA

X1 slot (1)

Ivdd(S3)=400mA(4 5V to 1.8V V_2p5_DAC

channel)

+12V=0.5A

Ivdd(Max)=14A 100mA

Ivdd(Max)=425mA(S3) 3.3VSB

LDO Icc(Max)=0.375A(wake)

Vtt (Core) 1.8V to 0.9V Icc(Max)=0.02A(no wake)

0.9V Ivterm(Max)=1.2A

Ivterm(Max)=200mA 3.3V

+3.3V=3A

(per channel)

ICH7RW

Vin=12V

V_1p5_core 1.2V VCC_CPU-14mA

1.5V PCI Per Slot (2)

Switching=17A -12V

B 1.05V Core=1.31A Icc(Max)=0.1A B

1.5V_A-0.97A

1.5V_B-0.74A 5V

HDA Codec Icc(Max)=5A

Vcc LDO 1.5V- 1.05V -12V

5V 12V LDO 3.3V 3.3V

Icc(Max)=tbdA 3.3V

to 5V Icc(Max)=7.6A

3.3V=0.58A

Vcc 12V

3.3V VccSus

3.3V Icc(Max)=0.5A

Icc(Max)=0.7A

Icc(Max)=tbdA

3.3VSB

5VRef=6mA Icc(Max)=0.375A(wake)

Icc(Max)=0.02A(no wake)

5VrefSus=10mA

1.0V

LDO Lan Core Tekoa GbE Lan

5V_dual to 3.3SB RTC=tbduA V_1p2_ctrl BJT

Icc(Max)=1.5A +1.2V=tbdA

1.8V +2.5V=tbdA BJT

Lan Phy

A V_2p5_ctrl A

RTC

Battery

*Power derived through filter FOXCONN PCEG

Title

Power Delivery Map

Size Document Number Rev

C 945P01 A

Date: Monday, June 13, 2005 Sheet 5 of 30

5 4 3 2 1

5 4 3 2 1

S0->S5

+12V_SYS +12V_SYS

S5->S0

D D

+5V_DUAL +5V_SYS +5V_SYS +5V_DUAL

+3D3V_DUAL +3D3V_SYS +3D3V_SYS +3D3V_DUAL

+1D8V_STR +1D8V_STR

VTT_DDR

VTT_DDR

VTT_VR VTT_VR

Vcc Vcc

1ms to 10ms

Vcc_PWRGD

Vcc_PWRGD

VRM_OUTEN

VRM_OUTEN

VIDPWRGD VIDPWRGD PS_ONJ

C

PS_ONJ C

S0->S3 S3->S0

+12V_SYS +12V_SYS

+5V_SYS +5V_DUAL +5V_DUAL +5V_SYS

+3D3V_SYS +3D3V_DUAL +3D3V_DUAL +3D3V_SYS

B B

+1D8V_STR +1D8V_STR +1D8V_STR +1D8V_STR

VTT_DDR

VTT_DDR

VTT_VR VTT_VR

Vcc Vcc

1ms to 10ms

Vcc_PWRGD

Vcc_PWRGD

VRM_OUTEN

VRM_OUTEN

VIDPWRGD PS_ONJ VIDPWRGD

PS_ONJ

A A

FOXCONN PCEG

Title

Power Sequence

Size Document Number Rev

C 945P01 A

Date: Monday, June 13, 2005 Sheet 6 of 30

5 4 3 2 1

5 4 3 2 1

ICH7 GPIO Summary FWH GPIO Summary

Name Power Well Type Description Name Power Plane Type Description

GPIO0 Vcc3_3 I/O Pull-up through 10K resistor(Unused) FGPI0 Vcc3_3 I IDE1 Cable Detection(33 or 66/100)

GPIO1 V5REF I/O PREQ5J FGPI1 Vcc3_3 I Pull-up through 10K resistor(Unused)

GPIO2 V5REF I/OD INTEJ FGPI2 VccSus3_3 I Pull-up through 10K resistor(Unused)

D D

GPIO3 V5REF I/OD INTFJ FGPI3 VccSus3_3 I Pull-up through 10K resistor(Unused)

GPIO4 V5REF I/OD INTGJ FGPI4 Vcc3_3 I Pull-up through 10K resistor(Unused)

GPIO5 V5REF I/OD INTHJ

GPIO6 Vcc3_3 I/O Pull-up through 10K resistor(Unused)

GPIO7

GPIO8

GPIO9

Vcc3_3

VccSus3_3

VccSus3_3

I/O

I/O

I/O

FWH_WPJ

LPC PME#

S1_LED

PCI Routing Summary

GPIO10 VccSus3_3 I/O S3_LED PCI1 1394

GPIO11 VccSus3_3 I/O RECOVERY INTAJ B F

GPIO12 VccSus3_3 I/O TPM_RSV0 Pull-up through 10K resistor(Unused) INTBJ C

GPIO13 VccSus3_3 I/O TPM_RSV1 Pull-up through 10K resistor(Unused) INTCJ D

GPIO14 VccSus3_3 I/O TPM_RSV2 Pull-up through 10K resistor(Unused) INTDJ A

GPIO15 VccSus3_3 I/O EXTSMI_L (Chassis Intruder) INTEJ

GPIO16 Vcc3_3 I/O (Unused) INTFJ

GPIO17 Vcc3_3 I/O (Unused) INTGJ

GPIO18 Vcc3_3 I/O (Unused) INTHJ

GPIO19 Vcc3_3 I/O Pull-up through 10K resistor(Unused) REG#/GNT# 1 0

GPIO20 Vcc3_3 I/O GPIO_LAN_DISABLEJ IDSEL 17 19

C

GPIO21 Vcc3_3 I/O Pull-up through 10K resistor(Unused) C

GPIO22 Vcc3_3 I/O PREQ4J

GPIO23 Vcc3_3 I/O Pull-up through 10K resistor(Unused)_Dummy

GPIO24 VccSus3_3 I/O (Unused) DDR2 DIMM Config.

GPIO25 VccSus3_3 I/O (Unused) DEVICE ADDRESS CLOCK

GPIO26 VccSus3_3 I/O (Unused) CK_M_200M_P_DDR0_A

DIMM 1 A0H

GPIO27 VccSus3_3 I/O (Unused) CK_M_200M_P_DDR1_A

GPIO28 VccSus3_3 I/O (Unused) CK_M_200M_P_DDR2_A

GPIO29 VccSus3_3 I/O USB_OCJ_FRONT CK_M_200M_P_DDR0_B

DIMM 2 A4H

GPIO30 VccSus3_3 I/O USB_OCJ_FRONT CK_M_200M_P_DDR1_B

GPIO31 VccSus3_3 I/O USB_OCJ_FRONT CK_M_200M_P_DDR2_B

GPIO32 Vcc3_3 I/O TURBOJ

GPIO33 Vcc3_3 I/O (Unused)

GPIO34 Vcc3_3 I/O (Unused)

GPIO35 Vcc3_3 I/O (Unused)

Jumper Setting Summary

GPIO36 Vcc3_3 I/O Pull-up through 10K resistor(Unused)

GPIO37 Vcc3_3 I/O Pull-up through 10K resistor(Unused) Lock JBLOCK1(1-2) Default

GPIO38 Vcc3_3 I/O FWH_TBLJ FWH TBL#

GPIO39 Vcc3_3 I/O Pull-up through 10K resistor(Unused) Unlock JBLOCK1(2-3)

B GPIO40 N/A N/A Not Implemented B

GPIO41 N/A N/A Not Implemented Normal JCMOS1(1-2) Default

GPIO42 N/A N/A Not Implemented CLR_CMOS

GPIO43 N/A N/A Not Implemented Clear JCMOS1(2-3)

GPIO44 N/A N/A Not Implemented

GPIO45 N/A N/A Not Implemented

GPIO46 N/A N/A Not Implemented

GPIO47 N/A N/A Not Implemented

GPIO48 Vcc3_3 I/O (Unused)

GPIO49 V_CPU_IO I/O CPU_PWRGD

Super I/O GPIO Summary

Name Power Plane Type Description

GPIO23 VccSus3_3 I/O DDCA_CLK

GPIO22 VccSus3_3 I/O DDCA_DATA

GPIO21 VccSus3_3 I/O DDCSCL_5V

A GPIO20 VccSus3_3 I/O DDCSDA_5V A

FOXCONN PCEG

Title

GPIO / IRQ / IDSEL Map

Size Document Number Rev

C 945P01 A

Date: Monday, June 13, 2005 Sheet 7 of 30

5 4 3 2 1

5 4 3 2 1

HAJ[31..3]

12 HAJ[31..3]

HDJ[63..0]

HDJ[63..0] 12 U10A

HAJ3 L5 D2 3 OF 7

HAJ4 A03# ADS# HADSJ 12 U10C

P6 A04# BNR# C2 HBNRJ 12

2 OF 7 HAJ5 M5 D4 P2 F26 TESTHI_0

U10B A05# HIT# HITJ 12 19 SMIJ SMI# TESTHI00

HAJ6 L4 H4 K3 W3 TESTHI_1

A06# RSP# 19 A20MJ A20M# TESTHI01

HAJ7 M4 G8 R3 P1 TESTHI_11

A07# BPRI# HBPRIJ 12 19 FERRJ FERR#/PBE# TESTHI11

HDJ0 B4 G16 HDJ32 HAJ8 R4 B2 K1 W2 TESTHI_12

D00# D32# A08# DBSY# HDBSYJ 12 19 INTR LINT0 TESTHI12

HDJ1 C5 E15 HDJ33 HAJ9 T5 C1 L1 F25

D01# D33# A09# DRDY# HDRDYJ 12 19 NMI LINT1 TESTHI02

HDJ2 A4 E16 HDJ34 HAJ10 U6 E4 N2 G25

D02# D34# A10# HITM# HITMJ 12 19 IGNNEJ IGNNE# TESTHI03

HDJ3 C6 G18 HDJ35 HAJ11 T4 AB2 HIERRJ M3 G27

D03# D35# A11# IERR# 19 STPCLKJ STPCLK# TESTHI04

HDJ4 A5 G17 HDJ36 HAJ12 U5 P3 G26

HDJ5 D04# D36# HDJ37 HAJ13 A12# INIT# INITJ 19 TESTHI05

D

B6 D05# D37# F17 U4 A13# LOCK# C3 HLOCKJ 12 9 HVCCA A23 VCCA TESTHI06 G24 D

HDJ6 B7 F18 HDJ38 HAJ14 V5 E3 B23 F24 TESTHI_2_7

D06# D38# A14# TRDY# HTRDYJ 12 9 HVSSA VSSA TESTHI07

HDJ7 A7 E18 HDJ39 HAJ15 V4 AD3 TP3 1 TP_VCCPLL D23 AK6

HDJ8 D07# D39# HDJ40 HAJ16 A15# BINIT# RSVD5 FORCEPH RSVD_G6

A10 D08# D40# E19 W5 A16# DEFER# G7 HDEFERJ 12 9 HVCCIOPLL C23 VCCIOPLL RSVD11 G6

HDJ9 A11 F20 HDJ41 N4 F2

HDJ10 D09# D41# HDJ42 RSVD1 EDRDY# TESTHI_13

B10 D10# D42# E21 12 HREQJ[4..0] P5 RSVD2 MCERR# AB3 TESTHI13 L2

HDJ11 C11 F21 HDJ43 HREQJ0 K4 VID0 AM2 AH2

D11# D43# REQ0# 29 VID0 VID0 RSVD12

HDJ12 D8 G21 HDJ44 HREQJ1 J5 U2 VID1 AL5 N1

D12# D44# REQ1# AP0# 29 VID1 VID1 PWRGOOD CPU_PWRG 18

HDJ13 B12 E22 HDJ45 HREQJ2 M6 U3 VID2 AM3 AL2 PROCHOTJ

D13# D45# REQ2# AP1# 29 VID2 VID2 PROCHOT#

HDJ14 C12 D22 HDJ46 HREQJ3 K6 VID3 AL6 M2

D14# D46# REQ3# 29 VID3 VID3 THERMTRIP# THERMTRIPJ 19

HDJ15 D11 G22 HDJ47 HREQJ4 J6 F3 HBR0J VID4 AK4

D15# D47# HAJ[31..3] REQ4# BR0# HBR0J 12 29 VID4 VID4

HDBIJ0 A8 D19 HDBIJ2 R6 G3 TESTHI_8 VID5 AL4

12 HDBIJ0 DBI0# DBI2# HDBIJ2 12 12 HAJ[31..3] 12 HADSTBJ0 ADSTB0# TESTHI08 29 VID5 VID5

C8 G20 G5 G4 TESTHI_9 TP24 1 TP_VID6 AM5 A13 HCOMP0

12 HDSTBNJ0 DSTBN0# DSTBN2# HDSTBNJ2 12 PCREQ# TESTHI09 FC11 COMP0

B9 G19 H5 TESTHI_10 AM7 T1 HCOMP1

12 HDSTBPJ0 DSTBP0# DSTBP2# HDSTBPJ2 12 TESTHI10 FC12 COMP1

HAJ17 AB6 R286 62R0603 +/-5% VID_SELECT AN7 G2 HCOMP2

HDJ16 HDJ48 HAJ18 A17# TP_DPJ0 TP11 FC16 COMP2 HCOMP3

G9 D16# D48# D20 W6 A18# DP0# J16 1 10 CK_200M_P_CPU F28 BCLK0 COMP3 R1

HDJ17 F8 D17 HDJ49 HAJ19 Y6 H15 TP_DPJ1 1 TP12 G28 J2 HCOMP4

D17# D49# A19# DP1# 10 CK_200M_N_CPU BCLK1 COMP4

HDJ18 F9 A14 HDJ50 HAJ20 Y4 H16 TP_DPJ2 1 TP8 T2 HCOMP5

HDJ19 D18# D50# HDJ51 HAJ21 A20# DP2# TP_DPJ3 TP9 COMP5

E9 D19# D51# C15 AA4 A21# DP3# J17 1 25 SKTOCC_L AE8 SKTOCC#

HDJ20 D7 C14 HDJ52 HAJ22 AD6 N5

D20# D52# A22# 25 THERMDA RSVD13

HDJ21 E10 B15 HDJ53 HAJ23 AA5 H2 HGTLREF_1 AE6

D21# D53# A23# GTLREF1 25 THERMDC RSVD14

HDJ22 D10 C18 HDJ54 HAJ24 AB5 H1 HGTLREF_0 AL1 C9

HDJ23 D22# D54# HDJ55 HAJ25 A24# GTLREF0 CPU_MCH_GTLREF THERMDA RSVD15

F11 D23# D55# B16 AC5 A25# CS_GTLREF E24 MCH_GTLREF_CPU 12 AK1 THERMDC RSVD16 G10

HDJ24 F12 A17 HDJ56 HAJ26 AB4 D16

HDJ25 D24# D56# HDJ57 HAJ27 A26# AN3 RSVD17

D13 D25# D57# B18 AF5 A27# AN3 VCCSENSE RSVD18 A20

HDJ26 E13 C21 HDJ58 HAJ28 AF4 G23 AN4 AN4 E23

HDJ27 D26# D58# HDJ59 HAJ29 A28# RESET# HCPURSTJ 12 VSSSENSE RSVD19

G13 D27# D59# B21 AG6 A29# 29 VCC_SENSE AN5 VCC_MB_REG RSVD21 F23

HDJ28 F14 B19 HDJ60 HAJ30 AG4 B3 AN6 J3

D28# D60# A30# RS0# HRSJ0 12 29 VSS_SENSE VSS_MB_REG RSVD24

HDJ29 G14 A19 HDJ61 HAJ31 AG5 F5

HDJ30 D29# D61# HDJ62 A31# RS1# HRSJ1 12

F15 D30# D62# A22 TP22 1TP_LAG775_PIN_AH4 AH4 A32# RS2# A3 HRSJ2 12

Changed pin name

MSID1 V1 MS_ID1

HDJ31 G15 D31# D63# B22 HDJ63 TP23 1TP_LAG775_PIN_AH5 AH5 A33# F29 from RSV

RSVD9 MSID0 W1 MS_ID0

HDBIJ1 G11 C20 HDBIJ3 TP21 1TP_LAG775_PIN_AJ5 AJ5

12 HDBIJ1 DBI1# DBI3# HDBIJ3 12 A34#

12 HDSTBNJ1 G12 DSTBN1# DSTBN3# A16 HDSTBNJ3 12

TP20 1TP_LAG775_PIN_AJ6 AJ6 A35#

12 HDSTBPJ1 E12 DSTBP1# DSTBP3# C17 HDSTBPJ3 12 AC4 RSVD3 BOOTSELECT Y1

AE4 RSVD4

THERMDA/THERMDC LL_ID0 V2

AD5 1. width=10 mils, spacing=10 mils. AA2 LL_ID1

CPU_Prescott_Rev1.0_LGA775 12 HADSTBJ1 ADSTB1# LL_ID1

2. route the lines in parallel

cpu_lga775h600_945u02 CPU_Prescott_Rev1.0_LGA775

C cpu_lga775h600_945u02 1 OF 7 C

CPU_Prescott_Rev1.0_LGA775

cpu_lga775h600_945u02 LL_ID1

R297

0

FSB routing guidelines: If under 5" OK (pin to pin) R0603

+/-5%

Dummy

C267 AN3

1

* 4.7uF

10V, Y5V, +80%/-20% Loadline ID for Cedar Mill support

C0805 AN4

2

VTT_OUT_LEFT VTT_OUT_LEFT GTLREF voltage should be 0.63*VTT Dummy

12 mils width, 15 mils spacing

divider should be within 1.5" of the GTLREF pin FSB_VTT

Place at CPU end of route R300

R238 62 R0603 +/-5% HBR0J VTT_OUT_RIGHT 124 0.22nF caps should be placed near CPU pin U10D 4 OF 7

+/-1% place series resistor as close to divider HTCK AE1 A29

R292 62 R0603 +/-5% HIERRJ R0603 HTDI TCK VTT1

Place at CPU end of route AD1 TDI VTT2 B25

R272 100 R0603 +/-5% Dummy CPU_PWRG HTDO AF1 B29

R260 TDO VTT3

HTMS AC1 B30

VTT_OUT_RIGHT HGTLREF_1 HTRSTJ TMS VTT4

AG1 TRST# VTT5 C29

VTT6 A26

R239 62 R0603 +/-5% TESTHI_8 R148 62 R0603 +/-5% HCPURSTJ B27

R303 10 C255 HBPM0J VTT7

AJ2 BPM0# VTT8 C28

1

TESTHI_9 R0603 HBPM1J

R249 62 R0603 +/-5% Place at CPU end of route 210 C281

* 220pF AJ1 BPM1# VTT9 A25

1

R244 62 R0603 +/-5% TESTHI_10 R279 130 R0603 +/-5% PROCHOTJ

+/-1%

R0603 * 1uF +/-5%

10V, Y5V, +80%/-20%

50V, X7R, +/-10%

C0603

HBPM2J

HBPM3J

AD2

AG2

BPM2# VTT10 A28

A27

2

C0603 Dummy HBPM4J BPM3# VTT11

AF2 C30

2

R273 62 R0603 +/-5% TESTHI_11 C284 HBPM5J BPM4# VTT12

AG3 BPM5# VTT13 A30

1

R293 62 R0603 +/-5% TESTHI_12 * 0.1uF

16V, Y5V, +80%/-20%

10,18,24 ICH_SYS_RSTJ

ICH_SYS_RSTJ AC2 DBR#

VTT14

VTT15

C25

C26

C0603 C27

2

R270 62 R0603 +/-5% TESTHI_13 VTT16

AK3 ITPCLKOUT0 VTT17 B26

AJ3 ITPCLKOUT1 VTT18 D27

VTT19 D28

R265 60.4 R0603 +/-1% HCOMP4 FSBSEL0 G29 D25

B 10,12 FSBSEL0 FSBSEL1 BSEL0 VTT20 B

10,12 FSBSEL1 H30 BSEL1 VTT21 D26

R277 60.4 R0603 +/-1% HCOMP5 FSBSEL2 G30 B28 VTT_OUT_RIGHT

10,12 FSBSEL2 BSEL2 VTT22 TPEV_VCCFUSEPRG

design guide 1.0 15 mils width VTT23 D29

7 mils spacing VTT_OUT_LEFT D30 TPEV_VIDFUSEPRG VTT_OUT_LEFT

VTT24

max. 1200mils VTTPWRGD AM6 VTTPWRGD 29

VTT_OUT_RIGHT

AA1 VTT_OUT_RIGHT

R241 62 R0603 +/-5% Dummy RSVD_G6 VTT_OUT1 VTT_OUT_LEFT

VTT_OUT2 J1

R240 60.4 R0603 +/-1% HCOMP2 F27

VTT_SEL

R275 60.4 R0603 +/-1% HCOMP3 R288 62 R0603 +/-5% HBPM5J CPU_Prescott_Rev1.0_LGA775

FSB_VTT cpu_lga775h600_945u02

R294 62 R0603 +/-5% HBPM4J VTT_OUT_LEFT

15 mils width 3D3V_SYS

7 mils spacing R291 62 R0603 +/-5% HBPM3J

max. 1200mils R142 62 R0603 +/-5% TESTHI_0

R301 62 R0603 +/-5% HBPM2J R290

Intel reply 60.4 Ohm is corrected 62

R145 62 R0603 +/-5% TESTHI_2_7 R283 62 R0603 +/-5% HBPM1J R139 R0603

1K +/-5%

R295 62 R0603 +/-5% HBPM0J +/-5% Dummy

R188 60.4 R0603 +/-1% HCOMP0 R0603

VTT_OUT_RIGHT Dummy

R281 60.4 R0603 +/-1% HCOMP1 Place BPM termination near CPU MS_ID0 R280 62R0603 +/-5%

15 mils width

7 mils spacing R276 62 R0603 +/-5% TESTHI_1 MS_ID1 R287 62R0603 +/-5%

max. 1200mils

GTLREF voltage should be 0.63*VTT MSID0: VTT = 2005 Mainstream FMB

VTT_OUT_RIGHT 12 mils width, 15 mils spacing Vss = 2005 Performance FMB

VTT_OUT_LEFT

divider should be within 1.5" of the GTLREF pin MSID1: NC = PSC only

0.22nF caps should be placed near CPU pin Vss = Cedar Mill

C283 C268 R269 place series resistor as close to divider

1

R299

62

R306

62

R296

62

R313

62

R302

62 * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20%

124

+/-1%

Intel recommend pull down to VSS

A +/-5% +/-5% +/-5% +/-5% +/-5% C0603 C0603 R0603 A

2

R0603 R0603 R0603 R0603 R0603

Dummy

R266 10 HGTLREF_0

R0603 +/-5%

place TDO termination near XDP connector

HTDO R261 C260

1

210 C256

* 220pF

1

place TCK/TDI/TMS terminations near

CPU within 1.5 inch

+/-1%

R0603 * 1uF

10V, Y5V, +80%/-20%

50V, X7R, +/-10%

C0603

FOXCONN PCEG

2

HTDI C0603 Dummy

2

HTMS Title

HTCK LGA775 -1

Size Document Number Rev

HTRSTJ

place TRSTJ termination anywhere on route

C 945P01 A

Date: Saturday, August 20, 2005 Sheet 8 of 30

5 4 3 2 1

5 4 3 2 1

VCCP VCCP VCCP

U10G 7 OF 7

U10E 5 OF 7 U10F 6 OF 7

AG22 VCCP1 VCCP93 AK12 AF9 VCCP185 VSS41 AL23 H22 VSS126 VSS211 D5

K29 VCCP2 VCCP94 AH22 AF22 VCCP186 VSS42 A12 H21 VSS127 VSS212 A9

AM26 VCCP3 VCCP95 T29 AH11 VCCP187 VSS43 L25 H20 VSS128 VSS213 D3

AL8 VCCP4 VCCP96 AM14 AJ14 VCCP188 VSS44 J7 H19 VSS129 VSS214 B1

AE12 VCCP5 VCCP97 AM25 AH19 VCCP189 VSS45 AE28 H18 VSS130 VSS215 B5

AE11 AE9 AH29 AE29 AB7 B8 FSB_VTT

D VCCP6 VCCP98 VCCP190 VSS46 VSS131 VSS216 D

W23 VCCP7 VCCP99 Y29 AH27 VCCP191 VSS47 K5 H17 VSS132 VSS217 AJ4 PLL Supply Filter

W24 VCCP8 VCCP100 AK25 AG28 VCCP192 VSS48 J4 AJ24 VSS133 VSS218 AE26

W25 VCCP9 VCCP101 AK19 AL26 VCCP193 VSS49 AE30 AM17 VSS134 VSS219 AH1

T25 VCCP10 VCCP102 AG15 AM12 VCCP194 VSS50 AN20 AC3 VSS135 VSS220 E29

1

Y28 VCCP11 VCCP103 J22 J24 VCCP195 VSS51 AF10 H14 VSS136 VSS221 V7

AL18 T24 J13 AE24 P28 C13 L6 L7

VCCP12 VCCP104 VCCP196 VSS52 VSS137 VSS222 L0805 10uH L0805 10uH

AC25 VCCP13 VCCP105 AG21 T28 VCCP197 VSS53 AM24 V6 VSS138 VSS223 AK24

W30 AM21 W28 AN23 AK2 AB30

2

VCCP14 VCCP106 VCCP198 VSS54 VSS139 VSS224

Y30 VCCP15 VCCP107 J25 J12 VCCP199 VSS55 H9 P27 VSS140 VSS225 L6 SRF: >=30MHz SRF: >=30MHz

AN14 VCCP16 VCCP108 U30 J27 VCCP200 VSS56 H8 P26 VSS141 VSS226 L7 Rated I: >=120mA Rated I: >=120mA

AD28 VCCP17 VCCP109 AL21 AG19 VCCP201 VSS57 H13 AM28 VSS142 VSS227 AB29 DCR: <=0.36 ohm DCR: <=0.36 ohm

Y26 VCCP18 VCCP110 AG25 AL9 VCCP202 VSS58 AC6 AJ13 VSS143 VSS228 M1

AC29 VCCP19 VCCP111 AJ18 AD30 VCCP203 VSS59 AC7 W4 VSS144 VSS229 AB28

M29 J19 AF21 AH6 P25 E8 HVCCIOPLL

VCCP20 VCCP112 VCCP204 VSS60 VSS145 VSS230 8 HVCCIOPLL

U24 VCCP21 VCCP113 AH30 Y24 VCCP205 VSS61 C16 AJ20 VSS146 VSS231 AG20

J23 VCCP22 VCCP114 J15 AK14 VCCP206 VSS62 AM16 W7 VSS147 VSS232 AN17

AC27 AG12 J9 AE25 P23 AB27 HVCCA

VCCP23 VCCP115 VCCP207 VSS63 VSS148 VSS233 8 HVCCA

AM18 VCCP24 VCCP116 AJ22 M27 VCCP208 VSS64 AE27 AG13 VSS149 VSS234 AB26

AM19 VCCP25 VCCP117 J20 AF14 VCCP209 VSS65 AJ28 AG16 VSS150 VSS235 AN16

AB8 AH18 J30 AJ7 AG17 M7 EC10 ESL <= 9 nH, ESR < 0.3 ohm

VCCP26 VCCP118 VCCP210 VSS66 VSS151 VSS236

AC26

J8

VCCP27 VCCP119 AH26

W27

AG18

AA8

VCCP211 VSS67 F19

AH13

C7

Y2

VSS152 VSS237 AB25

AB24

* 33uF

35V, +/-20%

VCCP28 VCCP120 VCCP212 VSS68 VSS153 VSS238 CE20D50H110

J28 VCCP29 VCCP121 AL25 AG8 VCCP213 VSS69 AD7 L30 VSS154 VSS239 AB23

T30 AN8 AL29 AH16 L29 N3 check component requirements

VCCP30 VCCP122 VCCP214 VSS70 VSS155 VSS240

AM9 VCCP31 VCCP123 AH14 AD29 VCCP215 VSS71 AK17 D15 VSS156 VSS241 AA30

AF15 VCCP32 VCCP124 U27 W8 VCCP216 VSS72 E17 AL27 VSS157 VSS242 F4 Notes:

AC8 T23 AH8 AH17 Y7 AG10 HVSSA 1. Cap. should be within 1.5" mils of the VCCA and VSSA pins

VCCP33 VCCP125 VCCP217 VSS73 VSS158 VSS243 8 HVSSA

AE14 VCCP34 VCCP126 R8 N24 VCCP218 VSS74 AH20 L27 VSS159 VSS244 AE13 2. VCCA route should be parallel and next to VSSA route to minimize loop area

N23 VCCP35 VCCP127 AK22 AN22 VCCP219 VSS75 AE5 AA29 VSS160 VSS245 AF30 3. VCCIOPLL route should be parallel and next to VSSA route to minimize loop area

W29 VCCP36 VCCP128 AN29 J14 VCCP220 VSS76 AH23 N6 VSS161 VSS246 H28

U29 AG11 K26 AE7 N7 F7 3. Min. 12 mils trace from the filter to the processor pins

VCCP37 VCCP129 VCCP221 VSS77 VSS162 VSS247 4. The inductors should be close to the cap.

AC24 VCCP38 VCCP130 AK26 AF19 VCCP222 VSS78 AM13 AA28 VSS163 VSS248 AF29

AC23 VCCP39 VCCP131 J10 N8 VCCP223 VSS79 AH24 AN13 VSS164 VSS249 AF28

Y23 VCCP40 VCCP132 AJ15 AF12 VCCP224 VSS80 AJ30 AA27 VSS165 VSS250 G1

AN26 VCCP41 VCCP133 AG26 M28 VCCP225 VSS81 AJ10 AA26 VSS166 VSS251 AF27

AN25 VCCP42 VCCP134 AN9 AK9 VCCP226 VSS82 AF3 P4 VSS167 VSS252 AF26

AN11 VCCP43 VCCP135 AH15 VSS83 AK5 AA25 VSS168 VSS253 AF25

C AN18 VCCP44 VCCP136 AF18 VSS84 AJ16 AA24 VSS169 VSS254 AN28 C

Y27 VCCP45 VCCP137 AL15 C10 VSS1 VSS85 AF6 P7 VSS170 VSS255 AN27

Y25 VCCP46 VCCP138 J26 D12 VSS2 VSS86 AK29 E26 VSS171 VSS256 AF24

AD24 VCCP47 VCCP139 J18 VSS87 AJ17 V30 VSS172 VSS257 AF23

AE23 VCCP48 VCCP140 J21 C24 VSS4 VSS88 F22 R2 VSS173 VSS258 AG24

AE22 VCCP49 VCCP141 AG27 K2 VSS5 VSS89 AH3 V29 VSS174 VSS259 AF17

AN19 VCCP50 VCCP142 AK15 C22 VSS6 VSS90 AK10 V28 VSS175 VSS260 AN24

V8 VCCP51 VCCP143 AF11 AN1 VSS7 VSS91 AM10 R5 VSS176 VSS261 H3

K8 VCCP52 VCCP144 AD23 B14 VSS8 VSS92 F16 V27 VSS177

AE21 VCCP53 VCCP145 AM15 K7 VSS9 VSS93 AJ23 R7 VSS178 VSS263 P24

AM30 VCCP54 VCCP146 AF8 AE16 VSS10 VSS94 F13 E20 VSS179 VSS264 AE20

AE19 VCCP55 VCCP147 AK21 B11 VSS11 VSS95 AG7 AN10 VSS180 VSS265 AE17

AC30 VCCP56 VCCP148 AG30 AL10 VSS12 VSS96 F10 V25 VSS181 VSS266 E27

AE15 AJ21 AK23 L26 T3 T7 HS1

VCCP57 VCCP149 VSS13 VSS97 VSS182 VSS267 MTG-HOLE-8_0

M30 VCCP58 VCCP150 AM11 H12 VSS14 VSS98 AD4 V24 VSS183 VSS268 R30

K27 AL11 AF7 H11 V23 AJ27 VTT_OUT_RIGHT

VCCP59 VCCP151 VSS15 VSS99 VSS184 VSS269

M24 VCCP60 VCCP152 AJ11 AK7 VSS16 VSS100 L24 T6 VSS185 VSS270 AB1

AN21 VCCP61 VCCP153 K30 H7 VSS17 VSS101 L23 AL7 VSS186 VSS271 AM4

6

5

T8 AL14 E14 AM23 E25 V26 R285 60.4 R0603 +/-1% HCOMP6

VCCP62 VCCP154 VSS18 VSS102 VSS187 VSS272

AC28 VCCP63 VCCP155 AN30 L28 VSS19 VSS103 A15 U1 VSS188 VSS273 AA23 7 4

N25 AH25 Y5 AH10 R29 AL28 8 3 R298 60.4 R0603 +/-1% HCOMP7

VCCP64 VCCP156 VSS20 VSS104 VSS189 VSS274

AE18 VCCP65 VCCP157 AL12 E11 VSS21 VSS105 H29 GTLREF_SEL R28 VSS190 VSS275 AF20 9 2

W26 AJ9 AL16 B24 R27 AG23

1

VCCP66 VCCP158 VSS22 VSS106 VSS191 VSS276

AD25 VCCP67 VCCP159 AK11 AL24 VSS23 VSS107 L3 R26 VSS192

15 mils width

M8 AG14 AK13 H27 R25 LKPT_HS_ATX 7 mils spacing

VCCP68 VCCP160 VSS24 VSS108 VSS193

N30 VCCP69 VCCP161 N29 AL3 VSS25 VSS109 A21 U7 VSS194 max. 1200mils

AD26 VCCP70 VCCP162 AL30 D21 VSS26 VSS110 AE2 R24 VSS195

AJ26 VCCP71 VCCP163 AJ25 AL20 VSS27 VSS111 AJ29 R23 VSS196

AM29 VCCP72 VCCP164 AH9 D18 VSS28 VSS112 A24 P30 VSS197

M25 VCCP73 VCCP165 J29 AN2 VSS29 VSS113 AK27 V3 VSS198

M26 VCCP74 VCCP166 J11 AK16 VSS30 VSS114 AK28 P29 VSS199

L8 VCCP75 VCCP167 K25 AK20 VSS31 VSS115 B20 AF16 VSS200 RSVD26 F6 IMPSEL

U25 VCCP76 VCCP168 P8 AM27 VSS32 VSS116 AM20 AE10 VSS201

Y8 VCCP77 VCCP169 K23 AM1 VSS33 VSS117 H26 AF13 VSS202 RSVD28 Y3 HCOMP6 vccp

AJ12 AL19 AL13 B17 H6 AE3 HCOMP7

VCCP78 VCCP170 VSS34 VSS118 VSS203 RSVD29

AD27 VCCP79 VCCP171 AM8 AL17 VSS35 VSS119 H25 A18 VSS204

U23 VCCP80 VCCP172 T26 C19 VSS36 VSS120 H24 A2 VSS205 RSVD31 E7

B

M23 VCCP81 VCCP173 N28 E28 VSS37 VSS121 AA3 E2 VSS206 RSVD32 B13 B

AG29 AH12 AH7 AA7 D9 D14 TC3 100uF CTD

VCCP82 VCCP174 VSS38 VSS122 VSS207 RSVD33

*

N27 AL22 AK30 H23 C4 E6 2V, +/-20%

VCCP83 VCCP175 VSS39 VSS123 VSS208 RSVD34

AM22 VCCP84 VCCP176 AN15 D24 VSS40 VSS124 AA6 A6 VSS209 RSVD35 D1

U28 VCCP85 VCCP177 AJ8 VSS125 H10 D6 VSS210 RSVD36 E5

K28 VCCP86 VCCP178 U26

U8 AJ19 CPU_Prescott_Rev1.0_LGA775 CPU_Prescott_Rev1.0_LGA775 TC4 100uF CTD

VCCP87 VCCP179

*

AK18 T27 cpu_lga775h600_945u02 cpu_lga775h600_945u02 2V, +/-20%

VCCP88 VCCP180

AD8 VCCP89 VCCP181 AK8

K24 VCCP90 VCCP182 AN12

AH28 VCCP91 VCCP183 AG9 Place caps within socket

AH21 VCCP92 VCCP184 N26 cavity solder side

CPU_Prescott_Rev1.0_LGA775

cpu_lga775h600_945u02

Put under CPU Heat-Sink

VCCP VCCP 0.8V~1.55V/ 119A

C220 C204 C208 C182 C187 C202 C214 C216 C196 C189 C205 C215 C179 C197 C217 C210 C207 C201 C496

EC11 EC23 EC31 EC30 EC22 EC13 EC16 EC26 EC28 EC27

1

22uF

* 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * 22uF * * 560uF * 560uF * 560uF * 560uF * 560uF * 560uF * 560uF * 560uF * 560uF * 560uF

CE35D80H200

CE35D80H200

CE35D80H200

CE35D80H200

CE35D80H200

CE35D80H200

CE35D80H200

CE35D80H200

CE35D80H200

CE35D80H200

Dummy

Dummy

Dummy

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

6.3V, X5R, +/-20% 2

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

C1206

4V, +/-20%

4V, +/-20%

4V, +/-20%

4V, +/-20%

4V, +/-20%

4V, +/-20%

4V, +/-20%

4V, +/-20%

4V, +/-20%

4V, +/-20%

A A

Dummy Dummy Dummy Dummy Dummy Dummy Dummy Dummy Dummy Dummy Dummy Dummy Dummy FOXCONN PCEG

Title

LGA775 -2

Size Document Number Rev

C 945P01 A

Date: Saturday, July 16, 2005 Sheet 9 of 30

5 4 3 2 1

5 4 3 2 1

3D3V_SYS 3D3V_SYS

3D3V_SYS

Analog/SRC/CPU Power Filter

3D3V_SYS

3D3V_CLK_A_SRC_CPU

C32

*

1

* 0.1uF L2

*

R76 L1 16V, Y5V, +80%/-20% FB L0805 300 Ohm

4.7K FB L0805 300 Ohm C0603 3D3V_CLK_A_SRC_CPU

2

+/-5%

R0603

3D3V_CLK_PCI_REF_USB

TURBOJ

C29 C24 C89 C88

1

D

Real time input pin to change frequency * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20% D

to a pre_programmed under or over clock C0603 C0603 C0603 C0603

2

entries located in the ROM table C66 C90 C26 C28 C27 C77

1

* 10uF

10V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20%

C1206 C0603 C0603 C0603 C0603 C0603

2

place near pin 5, 56 place near pin 48 Dummy

place near pin 19, 28, 34 place near pin 43 place near pin 37

3D3V_CLK_PCI_REF_USB

3D3V_CLK_A_SRC_CPU

C20 C25

1

R0603 XDP/PCI-E selection * 10uF

10V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20%

+/-5% High=XDP enable C1206 C0603

2

4.7K Dummy

R77 Low=PCI-E enable

place near pin 10

20 CK_33M_ICH

R78 Ce = 2*32pf - 5pf -

4.7K 2.8pf = 56.2p

+/-5% -> 56pf = C182 = C183

R0603 R62 33R0603 +/-5% 33M_1394 U3

Dummy

1 56 3D3V_CLK_PCI_REF_USB X1 XTAL 14.31818MHz

R59 33R0603 +/-5% 33M_PCI2 GND VDDPCI 33M_TPM R18 33R0603 +/-5%

27 CK_33M_1394 2 PCICLK2 PCICLK1 55 CK_33M_TPM 24 1 2

R60 33R0603 +/-5% 3 54 33M_PCI1 R19 33R0603 +/-5%

19 CK_33M_FWH PCICLK3 PCICLK0 CK_33M_PCI1 17

4 53 C70 C67

GND Reset# ICH_SYS_RSTJ 8,18,24

1

TURBOJ 3D3V_CLK_PCI_REF_USB 14M_ICH

C

18 TURBOJ

R61 0 R0603 +/-5% 5

6

VDDPCI

*Turbo#

REF0/FS_C

GND

52

51 ICS_FSBSEL2

R5

R20

15R0603 +/-5%

10R0603 +/-5%

CK_14M_ICH

CK_14M_SIO

18

25

* 56pF

50V, NPO, +/-5% * 56pF

50V, NPO, +/-5% C

ICS_FSBSEL0 7 50 C0603 C0603

2

R63 33R0603 +/-5% 33M_SIO ITP_EN/PCICLK_F0 X1

25 CK_33M_SIO 8 FS_A/PCICLK_F1 X2 49

9 48 3D3V_CLK_PCI_REF_USB

ICS_FSBSEL1 FS_B/PCICLK_F2 VDDREF

10 VDD48 SCLK 47 SMB_CLK_MAIN 15,16,25

11 **SEL24_48#/24_48MHz SDATA 46 SMB_DATA_MAIN 15,16,25

R82 33R0603 +/-5% 48M_ICH 12 45 200M_P_GMCH R22 33R0603 +/-5%

18 CK_48M_ICH USB_48MHz CPUCLKT0 CK_200M_P_GMCH 12

13 44 200M_N_GMCH R23 33R0603 +/-5%

GND CPUCLKC0 CK_200M_N_GMCH 12

R65 33R0603 +/-5% 96M_DOT_P 14 43 3D3V_CLK_A_SRC_CPU

12 CK_96M_P_GMCH DOTT_96MHz VDDCPU

R66 33R0603 +/-5% 96M_DOT_N 15 42 200M_P_CPU R24 33R0603 +/-5%

12 CK_96M_N_GMCH DOTC_96MHz CPUCLKT1 CK_200M_P_CPU 8

CLK_VTT_PWRGDJ 16 41 200M_N_CPU R25 33R0603 +/-5%

Vtt_PwrGd#_PD CPUCLKC1 CK_200M_N_CPU 8

R67 33R0603 +/-5% 17 40

21 CK_PE_100M_P_LAN R68 33R0603 +/-5% PCIEXT0 GND CLK_IREF R11 475 R0603 +/-1%

21 CK_PE_100M_N_LAN 18 PCIEXC0 IREF 39

3D3V_CLK_A_SRC_CPU 19 38

VDDPCIEX GNDA 3D3V_CLK_A_SRC_CPU

20 GND VDDA 37 making the IREF 2.32 mA

R69 33R0603 +/-5% PE_100M_P_16PORT 21 36

17 CK_PE_100M_P_16PORT PCIEXT1 CPUCLK_ITP/PCIEXT5

R70 33R0603 +/-5% PE_100M_N_16PORT 22 35

17 CK_PE_100M_N_16PORT PCIEXC1 CPUCLK_ITP/PCIEXC5

R71 22 R0603 +/-5% PE_100M_P_ICH 23 34 3D3V_CLK_A_SRC_CPU

18 CK_PE_100M_P_ICH PCIEXT2 VDDPCIEX

R72 22 R0603 +/-5% PE_100M_N_ICH 24 33

18 CK_PE_100M_N_ICH PCIEXC2 PCIEXT4

25 GND PCIEXC4 32

R73 27R0603 +/-5% SATA_100M_P_ICH 26 31 PE_100M_P_GMCH R26 33R0603 +/-5%

19 CK_SATA_100M_P_ICH SRCCLKT_SATA PCIEXT3 CK_PE_100M_P_GMCH 12

R74 27R0603 +/-5% SATA_100M_N_ICH 27 30 PE_100M_N_GMCH R27 33R0603 +/-5%

19 CK_SATA_100M_N_ICH SRCCLKC_SATA PCIEXC3 CK_PE_100M_N_GMCH 12

3D3V_CLK_A_SRC_CPU 28 29

VDDSRC GND

R83 R84 R85 R86 R87 R88 R89 R90 R91 R92 ICS954128AFLF R12 R13 R7 R8 R9 R10

49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9 49.9

+/-1% +/-1% +/-1% +/-1% +/-1% +/-1% +/-1% +/-1% +/-1% +/-1% +/-1% +/-1% +/-1% +/-1% +/-1% +/-1%

R0603 R0603 R0603 R0603 R0603 R0603 R0603 R0603 R0603 R0603 R0603 R0603 R0603 R0603 R0603 R0603

SMBus Address :1101-0010

100 MHz(PCIEX) 100 MHz(SRC SATA)

FSB_VTT

R79

PCIEX1 X16 connector SRCCLK_SATA ICH7

B FSBSEL0 8,12 B

PCIEX2 ICH7 BSEL TABLE 470

VCCP 3D3V_CLK_A_SRC_CPU R0603

PCIEX3 GMCH FS_C FS_B FS_A FSB Frequency +/-5%

R80

R40 R55 0 0 1 133MHz(533)

220 10K

FSBSEL1 8,12

+/-5% +/-5% 0 1 0 200MHz(800)

R39

R0603 R0603

CLK_VTT_PWRGDJ 470

0 0 0 266MHz(1066) R0603

C

+/-5%

Q10 4.7K

B R6

MMBT3904 R0603

+/-5%

FSBSEL2 8,12

E

470

R0603

+/-5%

1D8V_STR

CK_33M_ICH

CK_33M_FWH C468

1

CK_33M_TPM

* 0.1uF

16V, Y5V, +80%/-20%

C0603

2

Dummy

C91 C87 C14

1

* 10pF

50V, NPO, +/-5% * 10pF

50V, NPO, +/-5% * 10pF

50V, NPO, +/-5%

C0603 C0603 C0603 ICS_FSBSEL0 R64 2.2K

FSBSEL0 8,12

2

Dummy Dummy Dummy R0603 +/-5%

3D3V_SYS

A C234 A

1

CK_48M_ICH

* 0.1uF

16V, Y5V, +80%/-20% ICS_FSBSEL1 R81 2.2K

FSBSEL1 8,12

CK_33M_SIO C0603 R0603 +/-5%

2

CK_33M_1394

C93 C92 C86

1

* 10pF

50V, NPO, +/-5% * 10pF

50V, NPO, +/-5% * 10pF

50V, NPO, +/-5%

5V_SYS

C0603 C0603 C0603 C74 C248 C124

FOXCONN PCEG

2

Dummy Dummy Dummy

* 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20%

ICS_FSBSEL2 R21

R0603

2.2K

+/-5%

FSBSEL2 8,12

C0603 C0603 C0603 Title

2

ICS954128 ClockGen

Size Document Number Rev

C

945P01 A

Date: Saturday, August 20, 2005 Sheet 10 of 30

5 4 3 2 1

5 4 3 2 1

12V_SYS

R155

5V_SYS 10

+/-5%

R165

R0805 D2

Vout=Vref(1+R2/R1)+IadjR2

ANODE CATHODE C130 1 2 0.1uF 15V_PHASE R1 is Up Resistor.

*

C0603 25V, Y5V, +80%/-20%

Iadj=50uA 1D05V_ICH(1.5A)

*

For RT9202 1N4148W

10 15V_3VIN Chock 1.2uH L4 5V_SYS

R170 R0805 R171 C141 Vref=1.25V

1

20K +/-5% 20K

* 4.7uF EC9 EC8 C118

1

+/-5% Dummy +/-5% 16V, Y5V, +80%/-20% * 1500uF * 1500uF

* 4.7uF 5V_DUAL 3D3V_SB 1D5V_CORE

D

5

R0603 R0603 C1206 U9 6.3V, +/-20% 6.3V, +/-20% 10V, Y5V, +80%/-20% Max. output current = 3A

2

Dummy 1 Q18 CE35D80H200 CE35D80H200 C0805 U15 AMS1085

VCC

D

2

BOOT

3 VIN VOUT 2 R125

4

7 2 R138 0 R0805 +/-5%15V_UG1 G PHD45N03LTA 1.5V Power requires 1D5V_CORE U5A Q24

D COMP/OCSET UGATE D

17A maximum current 1D5V_CORE 3 +

ADJ

N-CH / TO-252 R243 1 G PHD45N03LTA

*

S

6 8 R168 0 R0805 +/-5% 15V_PHASE L5 Choke Coil 3.3uH 301 2

FB PHASE 1K -

+/-1% LM324

GND

S

1

4 C266 R0603 EC32 R0603 R136

11

LGATE

1

*

EC14

EC24

EC17

R175

* 1uF 220uF +/-1% R124 1K

D

R167 RT9214PS 2.2 C151 10V, Y5V, +80%/-20% 3D3VADJ 6.3V, +/-20% 2.1K +/-5% 1D05V_ICH

1

140 Dual-Layout Q22 +/-5%

* 0.1uF * * * C0603 CE20D50H110 +/-1% R0603

2

+/-1% with RT9214 R0805 16V, Y5V, +80%/-20% R0603

CE35D80H200

6.3V, +/-20%

1000uF

CE35D80H200

6.3V, +/-20%

1000uF

CE35D80H200

6.3V, +/-20%

1000uF

R0603 R147 0 R0805 +/-5%15V_LG1 G PHD45N03LTA C155 C0603 R242

2

1

VOUT= 0.8V(1+Rt / Rb) Near MOSFET N-CH / TO-252 * 0.1uF

16V, Y5V, +80%/-20%

499

+/-1% *

EC12

100uF

S

C0603 R0603 16V, +/-20%

2

CE20D50H110

R166 124

R0603 +/-1%

1.5V Voltage

R169 60.4 C152 1 2 18nF C0603 50V, Y5V, +80%/-20%

*

R0603 +/-1%

5V_SB_SYS 12V_SYS

5V_SYS 5V_SYS 5V_SYS

R42 R36

VCC25_EN 4.7K 1K

+/-5% +/-5%

See page 261

C

R14 2.5V R0603 R0603

S

3D3V_SB B Q4 Q67 close to IDE

MMBT3904 G G G

2D5V_MCH

C

10K E

1D5V_CORE VDDQ L

R0603 3D3V_SB 0.7V B Q7 R44

C

R34 R35 MMBT3904

+/-5% R33 4.7K Q25 Q23 Q67

D

B Q1 10 0.7V +/-5% AOD412 AOD412 AOD412

E

C22 MMBT3904 R15 +/-5% R0603 Dummy

C

R41

1

R17

* 1uF 100 R0805

E

0 2.2K 10K 10V, Y5V, +80%/-20% +/-5% Q6 5V_DUAL

C B C

C

R0603 R0603 SLP_S3# 24,25 PWRG_ATX MMBT3904 L

+/-5% C0603 R0603

2

+/-5% R0603 +/-5% B Q5

E

Dummy MMBT3904 S5 L 4.7K H

C

R16 VCC3 R0603 C31 C158

E

1

S0 H H

18,24,25 SLP_S3J

C18

B Q2

MMBT3904

1D5V_CORE +/-5%

H * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20%

G

1

VCC25_EN S3 H

* 1uF C0603 C0603

E

2

3.3K 10V, Y5V, +80%/-20% H

D1

R0603 C0603 1 S D

1D5V_CORE 5V_SB_SYS

2

+/-5% 3 L

2D5V_MCH

2

APM2301A

Q8

BAT54C

3D3V_SB 12V_SYS 1D5V_CORE

VTT_DDR2 Voltage Supplier C448 C156

1

3D3V_SYS

R467

R127

1.05K * 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20%

+/-1% C0603 C0603

D

2

2

1D8V_STR R0603

3

4

Q21

2 Q51 VTT_DDR 5 U5B

10K +

4

U23C HA8050 7 G PHD45N03LTA

R0603 10 R126 6

1

+ -

+/-1% 8 604 LM324

S

9 +/-1%

11

-

1

C449 R496 EC51 EC52 R0603 FSB_VTT

1

* 0.1uF R455 LM324 150 2 Q52 * 1000uF * 1000uF

11

16V, Y5V, +80%/-20% 10K +/-5% HA8550 6.3V, +/-20% 6.3V, +/-20% R172 1K R0603 +/-5%

C0603 +/-1% R0805 CE35D80H200 CE35D80H200

2

B B

R0603

S

EC15

Reserve large copper C116 1 2 0.1uF C0603 16V, Y5V, +80%/-20% G * 1000uF

*

Dummy 6.3V, +/-20%

CE35D80H200

Q20

3D3V_SB 3D3V_SB 5V_SB_SYS VCC1_8SB 1D8V_STR 1.8V Standby Voltage FDT458P

D 4

R493

R500 R479 10K VCC1_8SB

A

S

10K 8.2K +/-5% Q57

+/-5% +/-5% R0603 G 5V_DUAL

B

4

R0603 R0603 3D3V_SYS

VCC1_8SB U25

Vout 4

1.8V Power requires SOT223

V_2P5_MCH(100mA)

C

ADJ

APM2301A 3D3V_SB

Vin

15.2A maximum current

D

S

B Q58 Q49 EC35

MMBT3904 G * 1000uF AME1117 3D3V_SYS

C

1

Q56 6.3V, +/-20% R386

E

B R443 CE35D80H200 1K

0 +/-1%

D

MMBT3904 +/-5% AOD434L R0603

E

4

R0603 R465 Q13

R492 100 2.7V 180 VCC25_EN 10 U5C 2D5V_MCH

18,25 SLP_S4J +

R0603 +/-5% BC7 EC50 +/-1% 2.5V 8 G

24,25 PWRG_ATX

*

EC49

470uF * 0.1uF

16V, Y5V, +80%/-20%

* 1000uF

6.3V, +/-20%

* EC38

1000uF Vref=1.25V

R0603

R379

9 -

LM324

2N7002

S

6.3V, +/-20% C0603 CE35D80H200 6.3V, +/-20% 3.16K

11

CE35D80H200 CE35D80H200 EC48 R456 +/-1% R95

Dummy * 100uF 86.6 R0603 1K

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

16V, +/-20% +/-1% +/-5%

12V_SYS CE20D50H110 R0603 R0603 C172 C117 C497

1

VCC1_8SB

C96 1 2 0.1uF

* 0.1uF

* 0.1uF

* 10uF

*

C431 C0603 16V, Y5V, +80%/-20% C0603 C0603 C1206

2

1

A

R472

1K * 0.1uF

16V, Y5V, +80%/-20%

Dummy

A

R0603 C0603

A B C

D

2

+/-5%

C

4

Q50

1.8V 12 U23D

+

14 G

SLP4_L ATXPOK P-MOS N-MOS Power from

S

Q59 13 AOD434L

- S5 L L H Off Off Nothing

4

G LM324 R484

S

1K U5D

S0(Before ATXPOK) H L L On Off Standby 1.8V 12

11

+

R475 +/-5% 14

APM2301A

60.4K

+/-1%

R0603

S0(After ATXPOK) H H H Off ON Vcc3 13 -

LM324

FOXCONN PCEG

D

R0603 C469 1 2 0.1uF Title

S3 H L L On Off Standby 1.8V

11

*

Dummy 16V, Y5V, +80%/-20%

C0603 ACPI Voltage Regulator

Size Document Number Rev

close U12 C 945P01 A

Date: Saturday, August 20, 2005 Sheet 11 of 30

5 4 3 2 1

5 4 3 2 1

U14A HDJ[63..0]

8 HAJ[31..3] HDJ[63..0] 8

HAJ3 J39 HA3* 1.0 HD0* P41 HDJ0 U14D Place close to GMCH

HAJ4 K38 HA4* HD1* M39 HDJ1 Within 500 mils

HAJ5

HAJ6

J42 HA5*

HA6*

HD2*

HD3*

P42 HDJ2

HDJ3

U14G FSBSEL0 BSEL0 1.0 HSYNC_P R202 39 R0603 +/-5%

K35 M42 F21 HSYNC D17 HSYNC 26

HAJ7 J37 HA7* HD4* N41 HDJ4 FSBSEL1 H21 BSEL1 VSYNC C17 VSYNC_P R205 39 R0603 +/-5%

HAJ8

HAJ9

M34

N35

HA8*

HA9* FSB HD5*

HD6*

M40

L40

HDJ5

HDJ6 17

17

EXP_RXP0

EXP_RXN0

EXP_RXP0

EXP_RXN0

G12

F12

EXP_RX0

EXP_RX0*

1.0 EXP_TX0

EXP_TX0*

D14

C13

EXP_TXP0

EXP_TXN0

EXP_TXP0

EXP_TXN0

17

17

FSBSEL2

TP_ALLZTEST

L20

K18

BSEL2

ALLZTEST RED F17

VSYNC

RED

26

26

HAJ10 R33 HA10* HD7* M41 HDJ7

17 EXP_RXP1

EXP_RXP1 D11 EXP_RX1 EXP_TX1 A13 EXP_TXP1

EXP_TXP1 17

TP_XORTEST H20 XORTEST GREEN K17 GREEN 26

VGA

HAJ11 N32 HA11* HD8* K42 HDJ8

17 EXP_RXN1

EXP_RXN1 D12 EXP_RX1* EXP_TX1* B12 EXP_TXN1

EXP_TXN1 17

TP_RSV_TP5 L18 RSV_TP5 BLUE H18 BLUE 26

HAJ12 N34 HA12* HD9* G39 HDJ9

17 EXP_RXP2

EXP_RXP2 J13 EXP_RX2 EXP_TX2 A11 EXP_TXP2

EXP_TXP2 17

GMCH_EXP_SLR K21 EXP_SLR RED* G17 REDJ

HAJ13 M38 HA13* HD10* J41 HDJ10

17 EXP_RXN2

EXP_RXN2 H13 EXP_RX2* EXP_TX2* B10 EXP_TXN2

EXP_TXN2 17

TP_RSV_TP4 L21 RSV_TP4 GREEN* J17 GREENJ R248 R254 R258

D

HAJ14 N42 HA14* HD11* G42 HDJ11

17 EXP_RXP3

EXP_RXP3 E10 EXP_RX3 EXP_TX3 C10 EXP_TXP3

EXP_TXP3 17

GMCH_EXP_EN F20 EXP_EN BLUE* J18 BLUEJ 150 150 150

D

HAJ15 N37 HA15* HD12* G40 HDJ12 EXP_RXN3 F10 EXP_RX3* EXP_TX3* C9 EXP_TXN3

EXP_TXN3 17

TP_RSV_TP6 N21 RSV_TP6 +/-1% +/-1% +/-1%

PCIE

17 EXP_RXN3 DDC_DATA

HAJ16 N38 HA16* HD13* G41 HDJ13

17 EXP_RXP4

EXP_RXP4 J9 EXP_RX4 EXP_TX4 A9 EXP_TXP4

EXP_TXP4 17

1D5V_CORE N18 DDCA_DATA DDCA_DATA

R0603

25

R0603 R0603

HAJ17 R32 HA17* HD14* F40 HDJ14

17 EXP_RXN4

EXP_RXN4 H10 EXP_RX4* EXP_TX4* B7 EXP_TXN4

EXP_TXN4 17 DDC_CLK N20 DDCA_CLK DDCA_CLK 25

Place close to

HAJ18 R36 HA18* HD15* F43 HDJ15

17 EXP_RXP5

EXP_RXP5 F7 EXP_RX5 EXP_TX5 D7 EXP_TXP5

EXP_TXP5 17 M17 RESERVED GMCH

HAJ19 HA19* HD16* HDJ16 EXP_RXN5 EXP_RX5* EXP_TXN5 REFSET A20 REFSET Within 500 mils

U37 F37 17 EXP_RXN5 F9 EXP_TX5* D6 EXP_TXN5 17 L17 RESERVED

HAJ20 R35 HA20* HD17* E37 HDJ17

17 EXP_RXP6

EXP_RXP6 C4 EXP_RX6 EXP_TX6 A6 EXP_TXP6

EXP_TXP6 17 DREFCLKP J15 CK_96M_P_GMCH CK_96M_P_GMCH 10

HAJ21 R38 HA21* HD18* J35 HDJ18

17 EXP_RXN6

EXP_RXN6 D3 EXP_RX6* EXP_TX6* B5 EXP_TXN6

EXP_TXN6 17 RESERVED

R27 DREFCLKN H15 CK_96M_N_GMCH CK_96M_N_GMCH 10

2D5V_MCH

HAJ22 V33 HA22* HD19* D39 HDJ19

17 EXP_RXP7

EXP_RXP7 G6 EXP_RX7 EXP_TX7 E2 EXP_TXP7

EXP_TXP7 17 RESERVED

U27

HAJ23 U34 HA23* HD20* C41 HDJ20 EXP_RXN7 J6 EXP_RX7* EXP_TX7* F1 EXP_TXN7

EXP_TXN7 17 RESERVED

M15 EXTTS* J20 EXTTSJ R183 10K R0603 +/-5%

17 EXP_RXN7

HAJ24 U32 HA24* HD21* B39 HDJ21

17 EXP_RXP8

EXP_RXP8 K9 EXP_RX8 EXP_TX8 G2 EXP_TXP8

EXP_TXP8 17 RESERVED

L15 RESERVED M11

HAJ25 V42 HA25* HD22* B40 HDJ22

17 EXP_RXN8

EXP_RXN8 K8 EXP_RX8* EXP_TX8* J1 EXP_TXN8

EXP_TXN8 17 Intel Symbol 1.0 update RESERVED V30

HAJ26 HA26* HDJ23 EXP_RXP9 EXP_TXP9 NC PLTRSTJ

HAJ27

U35

Y36 HA27*

HD23*

HD24*

H34

C37 HDJ24 17

17

EXP_RXP9

EXP_RXN9

EXP_RXN9

F4

G4

EXP_RX9

EXP_RX9*

EXP_TX9

EXP_TX9*

J3

K4 EXP_TXN9

EXP_TXP9

EXP_TXN9

17

17

BB2

BA2 NC MISC RSTIN*

PWROK

AJ12

AJ9 PWRGD_3V

PLTRSTJ

PWRGD_3V

18,19,24,25

18,25,27

HAJ28 Y38 HA28* HD25* J32 HDJ25 EXP_RXP10 M6 EXP_RX10 EXP_TX10 L4 EXP_TXP10

EXP_TXP10 17 AW26 NC ICH_SYNC* M18 ICH_SYNCJ

ICH_SYNCJ 18

17 EXP_RXP10 NC

HAJ29 AA37 HA29* HD26* B35 HDJ26

17 EXP_RXN10

EXP_RXN10 M7 EXP_RX10* EXP_TX10* M4 EXP_TXN10

EXP_TXN10 17 AW2

HAJ30 V32 HA30* HD27* J34 HDJ27

17 EXP_RXP11

EXP_RXP11 K2 EXP_RX11 EXP_TX11 M2 EXP_TXP11

EXP_TXP11 17 AV27 NC RESERVED A43

HAJ31 Y34 HA31* HD28* B34 HDJ28 EXP_RXN11 L1 EXP_RX11* EXP_TX11* N1 EXP_TXN11

EXP_TXN11 17 AV26 NC REDJ R246 0 R0603 +/-5%

17 EXP_RXN11 NC

TP_FSB_AA35 AA35 RSVD HD29* F32 HDJ29

17 EXP_RXP12

EXP_RXP12 U11 EXP_RX12 EXP_TX12 P2 EXP_TXP12

EXP_TXP12 17 E35 NC BC43 GREENJ R252 0 R0603 +/-5%

TP_FSB_AA42 AA42 RSVD HD30* L32 HDJ30 EXP_RXN12 U10 EXP_RX12* EXP_TX12* T1 EXP_TXN12

EXP_TXN12 17 C42 NC NC BC42 BLUEJ R256 0 R0603 +/-5%

17 EXP_RXN12 NC

TP_FSB_AA34 AA34 RSVD HD31* J31 HDJ31

17 EXP_RXP13

EXP_RXP13 R8 EXP_RX13 EXP_TX13 T4 EXP_TXP13

EXP_TXP13 17 B42 NC BC2

TP_FSB_AA38 AA38 RSVD HD32* H31 HDJ32 EXP_RXN13 R7 EXP_RX13* EXP_TX13* U4 EXP_TXN13

EXP_TXN13 17 B41 NC NC BC1

17 EXP_RXN13

HD33* M33 HDJ33

17 EXP_RXP14

EXP_RXP14 P4 EXP_RX14 EXP_TX14 U2 EXP_TXP14

EXP_TXP14 17 NC BB43

HD34* K31 HDJ34 EXP_RXN14 N3 EXP_RX14* EXP_TX14* V1 EXP_TXN14

EXP_TXN14 17 AJ27 RESERVED NC BB1

8 HREQJ[4..0] HREQJ0 HD35* HDJ35 17 EXP_RXN14 EXP_RXP15 EXP_TXP15 RESERVED

E41 HREQ0* M27 17 EXP_RXP15 Y10 EXP_RX15 EXP_TX15 V3 EXP_TXP15 17 AG27 NC C2

HREQJ1 D41 HREQ1* HD36* K29 HDJ36 EXP_RXN15 Y11 EXP_RX15* EXP_TX15* W4 EXP_TXN15

EXP_TXN15 17 AG26 RESERVED NC B43

HD37* 17 EXP_RXN15 RESERVED

HREQJ2 K36 HREQ2* F31 HDJ37 AG25 NC B3

HREQJ3 G37 HREQ3* HD38* H29 HDJ38 DMI_RXP0 Y7 DMI_RX0 AJ24 RESERVED NC B2

18 DMI_RXP0 DMI_TX0

HREQJ4 E42 HREQ4* HD39* F29 HDJ39

18 DMI_RXN0

DMI_RXN0 Y8 DMI_RX0* W2 DMI_TXP0

DMI_TXP0 18 NC A42

HD40* L27 HDJ40 DMI_RXP1 AA9 DMI_RX1 DMI_TX0* Y1 DMI_TXN0

DMI_TXN0 18 AD30 RESERVED

18 DMI_RXP1

8

8

HADSTBJ0

HADSTBJ1

M36

V35

HADSTB0*

HADSTB1*

HD41*

HD42*

M24

J26

HDJ41

HDJ42 18

18

DMI_RXN1

DMI_RXP2

DMI_RXN1

DMI_RXP2

AA10

AA6

DMI_RX1*

DMI_RX2 DMI DMI_TX1

DMI_TX1*

AA2

AB1

DMI_TXP1

DMI_TXN1

DMI_TXP1

DMI_TXN1

18

18

1D5V_PE_GMCH

AC34

Y30

RESERVED

RESERVED

RESERVED

RESERVED

AK21

AJ23

HD43* K26 HDJ43

18 DMI_RXN2

DMI_RXN2 AA7 DMI_RX2* DMI_TX2 Y4 DMI_TXP2

DMI_TXP2 18 Y33 RESERVED RESERVED AJ26 2D5V_DAC

K41 HDSTBP0 HD44* G26 HDJ44 DMI_RXP3 AC9 DMI_RX3 DMI_TX2* AA4 DMI_TXN2

DMI_TXN2 18 AF31 RESERVED RESERVED AL29

8 HDSTBPJ0 18 DMI_RXP3 RESERVED RESERVED

8 HDSTBNJ0 L43 HDSTBN0* HD45* H24 HDJ45

18 DMI_RXN3

DMI_RXN3 AC8 DMI_RX3* DMI_TX3 AB3 DMI_TXP3

DMI_TXP3 18 AD31 AL20

8 HDBIJ0

HDBIJ0 K40 HDINV_0* HD46* K24 HDJ46 DMI_TX3* AC4 DMI_TXN3

DMI_TXN3 18 R237 U30 RESERVED RESERVED AJ21

8 HDSTBPJ1 F35 HDSTBP1 HD47* F24 HDJ47

10 CK_PE_100M_P_GMCH

CK_PE_100M_P_GMCH B14 GCLKP V31 RESERVED RESERVED AL26

G34 HDSTBN1* HD48* E31 HDJ48

10 CK_PE_100M_N_GMCH

CK_PE_100M_N_GMCH B16 GCLKN EXP_COMPO AC12 GMCH_EXP_COMP AA30 RESERVED RESERVED AK27

C

8

8

HDSTBNJ1

HDBIJ1

HDBIJ1 A38 HDINV_1* HD49* A33 HDJ49 Dummy EXP_COMPI AC11 AC30 RESERVED 5 OF 7 RESERVED AJ29 R247 R253 R257 C

J27 HDSTBP2 HD50* E40 HDJ50 R181 0 R0603 +/-5% F15 SDVO_CTRLDATA RESERVED AG29 0 0 0

8 HDSTBPJ2 17 SDVO_CTRLDATA 24.9

8 HDSTBNJ2 M26 HDSTBN2* HD51* D37 HDJ51

17 SDVO_CTRLCLK

R179 0 R0603 +/-5% E15 SDVO_CTRLCLK width 10 mils, spacing 7 mils +/-5% +/-5% +/-5%

HDBIJ2 HDINV_2* HDJ52 Dummy R0603 RED R0603 R0603 R0603

8 HDBIJ2 E29 HD52* C39

8 HDSTBPJ3 E34 HDSTBP3 HD53* D38 HDJ53

2 OF 7 +/-1% GREEN Dummy Dummy Dummy

B37 HDSTBN3* HD54* D33 HDJ54 unstuff when no internal BLUE

8 HDSTBNJ3 HDBIJ3 HDJ55

8 HDBIJ3 B32 HDINV_3* HD55* C35

graphics connection

HD56* D34 HDJ56 FSBSEL0 1D5V_CORE 2D5V_DAC

8,10 FSBSEL0

8 HADSJ W42 HADS* HD57* C34 HDJ57 5V_SYS

8 HTRDYJ W40 HTRDY* HD58* B31 HDJ58

8 HDRDYJ V41 HDRDY* HD59* C31 HDJ59 2D5V_MCH

8,10 FSBSEL1

FSBSEL1

8 HDEFERJ P40 HDEFER* HD60* C32 HDJ60 R267 R177

8 HITMJ W41 HHITM* HD61* D32 HDJ61 2.7K 0 R245 R251 R255

8 HITJ U41 HHIT* HD62* B30 HDJ62 CRB 1.03 pull-up to 2.5V

8,10 FSBSEL2

FSBSEL2 +/-5% +/-5% 0 0 0

8 HLOCKJ U40 HLOCK* HD63* D30 HDJ63 R0603 CK_96M_P_GMCH R0603 +/-5% +/-5% +/-5%

8 HBR0J AA41 HBREQ0* DDCA_CLK CK_96M_N_GMCH Dummy REDJ R0603 R0603 R0603

8 HBNRJ U39 HBNR* HSWING B27 HSWING R182 R180 GREENJ Dummy Dummy Dummy

8 HBPRIJ D42 HBPRI* HSCOMP C27 HSCOMP 4.7K 4.7K R268 R176 BLUEJ

8 HDBSYJ U42 HDBSY* HRCOMP A28 HRCOMP +/-5% +/-5% 3D3V_SYS 2.7K 1D5V_CORE 0

T40 HRS0* R0603 R0603 +/-5% +/-5%

8 HRSJ0

8 HRSJ1 Y43 HRS1* HDVREF D27 MCH_GTLREF Dummy Dummy R0603 R178 R0603

T43 HRS2* HACCVREF D28 0 Dummy HSYNC_P

8 HRSJ2 R164 +/-5% VSYNC_P

8 HCPURSTJ C30 HCPURST*

F38 HPCREQ* HCLKP M31 1K CK_PE_100M_P_GMCH R0603 R204 R203

CK_200M_P_GMCH 10

Y40 HEDRDY* HCLKN M29 +/-5% CK_PE_100M_N_GMCH Dummy 10K 10K 2D5V_DAC

CK_200M_N_GMCH 10

R0603 +/-5% +/-5%

1 OF 7 Dummy 5V_SYS R185 R0603 R0603

0 Dummy Dummy

GMCH_EXP_EN_HDR GMCH_EXP_EN +/-5% R191

17 GMCH_EXP_EN_HDR R262 R0603 0

2.7K Dummy +/-5%

+/-5% R0603

Signal termination (follow Intel reference 0p7) R0603 Dummy

FSB_VTT COMP SIGNAL TERMINATION DDCA_DATA REFSET

FSB_VTT Intel confirm

R263

R192

2.7K stuff when no internal

R198 REFSET +/-5%

B R197 graphics connection B

301 R0603

+/-1% HSCOMP place near GMCH

R0603 255

15 mils width

C200 R0603

R206 60.4 20 mils spacing

1

HSWING R0603 * 2.2pF

50V, NPO, +/-0.25pF

+/-1%

+/-1% C0603

2

Dummy

R199 C183 62

1

R0603

84.5

+/-1% * 10nF

25V, X7R, +/-10% +/-5%

R184

R0603

1K

+/-5%

GMCH_EXP_SLR

R0603 C0603 5 mils width, 5 mils spacing in the breakout

2

5 mils width, 8 mils spacing after the breakout ATX dummy

HSWING voltage should be 0.22*FSB_VTT max. 750 mils BTX pop

12 mils width, 10 mils spacing

max. 3 inches long

caps should be placed near GMCH pin.

FSB_VTT

R213

HRCOMP

R195

16.9 124

R0603 +/-1%

+/-1% R0603

MCH_GTLREF_CPU 8

U14_5 10 mils width, 7 mils spacing R193

max. 500 mils

MCH_GTLREF

R194 C178 10 C177

1

1

R0603

210

+/-1% * 0.1uF

16V, Y5V, +80%/-20% +/-5% * 220pF

50V, X7R, +/-10%

R0603 C0603 C0603

2

U14_1 U14_2 U14_3 U14_4 2 Dummy

A A

Heatsink Clip_2P Clip_2P Clip_2P Clip_2P GTLREF voltage should be 0.63*VTT = 0.75V

Need to apply Heatsink for Lakeport 12 mils width, 15 mils spacing

chipset. For GMCH heatsink hook divider should be within 1.5" of the GTLREF pin

0.22nF caps should be placed near MCH pin

place series resistor as close to divider

FOXCONN PCEG

Title

Lakeport GMCH -1

Size Document Number Rev

C 945P01 A

Date: Saturday, August 20, 2005 Sheet 12 of 30

5 4 3 2 1

5 4 3 2 1

U14B U14C

16 M_MAA_B[13..0] M_DQS_B[7..0] 16

15 M_MAA_A[13..0] M_MAA_A0 SMA_A0 1.0 SDQS_A0 M_DQS_A0

M_DQS_A[7..0] 15

M_MAA_B0

M_MAA_B1

BB22 SMA_B0 1.0 SDQS_B0 AM8 M_DQS_B0

M_DQS_BJ0

M_DQS_BJ[7..0] 16

BA32 AU4 M_DQS_AJ[7..0] 15 BB21 SMA_B1 SDQS_B0* AM6 M_DQM_B[7..0] 16

M_MAA_A1 AW32 SMA_A1 SDQS_A0* AR2 M_DQS_AJ0

M_DQM_A[7..0] 15

M_MAA_B2 BA21 SMA_B2 SDM_B0 AL11 M_DQM_B0

M_DATA_B[63..0] 16

M_MAA_A2 BB30 SMA_A2 SDM_A0 AR3 M_DQM_A0

M_DATA_A[63..0] 15

M_MAA_B3 AY21 SMA_B3

M_MAA_A3 BA30 SMA_A3 M_MAA_B4 BC20 SMA_B4 SDQ_B0 AL6 M_DATA_B0

M_MAA_A4 AY30 SMA_A4 SDQ_A0 AP3 M_DATA_A0 M_MAA_B5 AY19 SMA_B5 SDQ_B1 AL8 M_DATA_B1

M_MAA_A5 BA27 SMA_A5 SDQ_A1 AP2 M_DATA_A1 M_MAA_B6 AY20 SMA_B6 SDQ_B2 AP8 M_DATA_B2

M_MAA_A6 BC28 SMA_A6 SDQ_A2 AU3 M_DATA_A2 M_MAA_B7 BA18 SMA_B7 SDQ_B3 AP9 M_DATA_B3

M_MAA_A7 AY27 SMA_A7 SDQ_A3 AV4 M_DATA_A3 M_MAA_B8 BA19 SMA_B8 SDQ_B4 AJ11 M_DATA_B4

M_MAA_A8 AY28 SMA_A8 SDQ_A4 AN1 M_DATA_A4 M_MAA_B9 BB18 SMA_B9 SDQ_B5 AL9 M_DATA_B5

M_MAA_A9 BB27 SMA_A9 SDQ_A5 AP4 M_DATA_A5 M_MAA_B10 BA22 SMA_B10 SDQ_B6 AM10 M_DATA_B6

M_MAA_A10 AY33 SMA_A10 SDQ_A6 AU5 M_DATA_A6 M_MAA_B11 BB17 SMA_B11 SDQ_B7 AP6 M_DATA_B7

D

M_MAA_A11 AW27 SMA_A11 SDQ_A7 AU2 M_DATA_A7 M_MAA_B12 BA17 SMA_B12 M_DQS_B[7..0] 16 D

M_MAA_A12 BB26 SMA_A12 M_DQS_A[7..0] 15

M_MAA_B13 AW42 SMA_B13 SDQS_B1 AV7 M_DQS_B1

M_DQS_BJ[7..0] 16

M_MAA_A13 BC38 SMA_A13 SDQS_A1 BA3 M_DQS_A1

M_DQS_AJ[7..0] 15 SDQS_B1* AR9 M_DQS_BJ1

M_DQM_B[7..0] 16

SDQS_A1* BB4 M_DQS_AJ1 BB23 SWE_B* SDM_B1 AW7 M_DQM_B1

M_DQM_A[7..0] 15 16 M_WE_BJ M_DATA_B[63..0] 16

BB35 SWE_A* SDM_A1 AY2 M_DQM_A1 AY24 SCAS_B*

15 M_WE_AJ M_DATA_A[63..0] 15 16 M_CAS_BJ

BA37 SCAS_A* BA23 SRAS_B* SDQ_B8 AU7 M_DATA_B8

15 M_CAS_AJ 16 M_RAS_BJ M_DATA_B9

15 M_RAS_AJ BA34 SRAS_A* 16 M_BS_B[2..0] SDQ_B9 AV6

SDQ_A8 AW3 M_DATA_A8 M_BS_B0 AW23 SBS_B0 SDQ_B10 AV12 M_DATA_B10

M_BS_A0 BC33 SBS_A0 SDQ_A9 AY3 M_DATA_A9 M_BS_B1 AY23 SBS_B1 SDQ_B11 AM11 M_DATA_B11

M_BS_A1 AY34 SBS_A1 SDQ_A10 BA7 M_DATA_A10 M_BS_B2 AY17 SBS_B2 SDQ_B12 AR5 M_DATA_B12

M_BS_A2 BA26 SBS_A2 SDQ_A11 BB7 M_DATA_A11 SDQ_B13 AR7 M_DATA_B13

15 M_BS_A[2..0]

SDQ_A12 AV1 M_DATA_A12

16 M_SCS_B0J BA40 SCS_B0* SDQ_B14 AR12 M_DATA_B14

BB37 SCSB_A0* SDQ_A13 AW4 M_DATA_A13 AW41 SCS_B1* SDQ_B15 AR10 M_DATA_B15

15 M_SCS_A0J SDQ_A14 M_DATA_A14 16 M_SCS_B1J

15 M_SCS_A1J BA39 SCSB_A1* BC6 BA41 SCS_B2* M_DQS_B[7..0] 16

BA35 SCSB_A2* SDQ_A15 AY7 M_DATA_A15 AW40 SCS_B3* SDQS_B2 AV13 M_DQS_B2

M_DQS_BJ[7..0] 16

AY38 SCSB_A3* M_DQS_A[7..0] 15

SDQS_B2* AT13 M_DQS_BJ2

M_DQM_B[7..0] 16

SDQS_A2 AY11 M_DQS_A2

M_DQS_AJ[7..0] 15

M_SCKE_B0 BA14 SCKE_B0 SDM_B2 AP13 M_DQM_B2

M_DATA_B[63..0] 16

SCKE_A0 16 M_SCKE_B0

15 M_SCKE_A0

M_SCKE_A0 BB25 SDQS_A2* BA10 M_DQS_AJ2

M_DQM_A[7..0] 15 16 M_SCKE_B1

M_SCKE_B1 AY16 SCKE_B1

15 M_SCKE_A1

M_SCKE_A1 AY25 SCKE_A1 SDM_A2 BB10 M_DQM_A2

M_DATA_A[63..0] 15 BA13 SCKE_B2 SDQ_B16 AM15 M_DATA_B16

BC24 SCKE_A2 BB13 SCKE_B3 SDQ_B17 AM13 M_DATA_B17

BA25 SCKE_A3 SDQ_A16 AW12 M_DATA_A16 SDQ_B18 AV15 M_DATA_B18

SDQ_A17 AY10 M_DATA_A17 M_ODT_B0 AY42 SODT_B0 SDQ_B19 AM17 M_DATA_B19

SODT_A0 16 M_ODT_B0 SDQ_B20

15 M_ODT_A0

M_ODT_A0 AW37 SDQ_A18 BA12 M_DATA_A18

16 M_ODT_B1

M_ODT_B1 AV40 SODT_B1 AN12 M_DATA_B20

M_ODT_A1 AY39 SODT_A1 SDQ_A19 BB12 M_DATA_A19 AV43 SODT_B2 SDQ_B21 AR13 M_DATA_B21

15 M_ODT_A1 M_DATA_A20 SDQ_B22 M_DATA_B22

AY37 SODT_A2 SDQ_A20 BA9 AU40 SODT_B3 AP15

BB40 SODT_A3 SDQ_A21 BB9 M_DATA_A21 SDQ_B23 AT15 M_DATA_B23

SDQ_A22 BC11 M_DATA_A22

M_DQS_B[7..0] 16

SDQ_A23 AY12 M_DATA_A23 SDQS_B3 AU23 M_DQS_B3

SCLK_A0 M_DQS_BJ[7..0] 16

BB32 M_DQS_A[7..0] 15 AM29 SCLK_B0 SDQS_B3* AR23 M_DQS_BJ3

M_DQM_B[7..0] 16

15 CK_M_200M_P_DDR0_A SCLK_A0* SDQS_A3 M_DQS_A3 16 CK_M_200M_P_DDR0_B SCLK_B0* M_DQM_B3

15 CK_M_200M_N_DDR0_A AY32 AU18 M_DQS_AJ[7..0] 15 16 CK_M_200M_N_DDR0_B AM27 SDM_B3 AP23 M_DATA_B[63..0] 16

15 CK_M_200M_P_DDR1_A AY5 SCLK_A1 SDQS_A3* AR18 M_DQS_AJ3

M_DQM_A[7..0] 15 16 CK_M_200M_P_DDR1_B AV9 SCLK_B1

15 CK_M_200M_N_DDR1_A BB5 SCLK_A1* SDM_A3 AP18 M_DQM_A3

M_DATA_A[63..0] 15 16 CK_M_200M_N_DDR1_B AW9 SCLK_B1* SDQ_B24 AM24 M_DATA_B24

15 CK_M_200M_P_DDR2_A AK42 SCLK_A2 16 CK_M_200M_P_DDR2_B AL38 SCLK_B2 SDQ_B25 AM23 M_DATA_B25

AK41 SCLK_A2* SDQ_A24 AM20 M_DATA_A24 AL36 SCLK_B2* SDQ_B26 AV24 M_DATA_B26

15 CK_M_200M_N_DDR2_A 16 CK_M_200M_N_DDR2_B

BA31 SCLK_A3 SDQ_A25 AM18 M_DATA_A25 AP26 SCLK_B3 SDQ_B27 AM26 M_DATA_B27

BB31 SCLK_A3* SDQ_A26 AV20 M_DATA_A26 AR26 SCLK_B3* SDQ_B28 AP21 M_DATA_B28

AY6 SCLK_A4 SDQ_A27 AM21 M_DATA_A27 AU10 SCLK_B4 SDQ_B29 AR21 M_DATA_B29

BA5 SCLK_A4* SDQ_A28 AP17 M_DATA_A28 AT10 SCLK_B4* SDQ_B30 AP24 M_DATA_B30

C AH40 SCLK_A5 SDQ_A29 AR17 M_DATA_A29 AJ38 SCLK_B5 SDQ_B31 AT24 M_DATA_B31 C

AH43 SCLK_A5* SDQ_A30 AP20 M_DATA_A30 AJ36 SCLK_B5* M_DQS_B[7..0] 16

SDQ_A31 AT20 M_DATA_A31 SDQS_B4 AT29 M_DQS_B4

M_DQS_BJ[7..0] 16

BC16 RSVD M_DQS_A[7..0] 15 SDQS_B4* AV29 M_DQS_BJ4

M_DQM_B[7..0] 16

AY14 RSVD SDQS_A4 AU35 M_DQS_A4

M_DQS_AJ[7..0] 15 SDM_B4 AR29 M_DQM_B4

M_DATA_B[63..0] 16

AW17 RSVD SDQS_A4* AV35 M_DQS_AJ4

M_DQM_A[7..0] 15

AW18 RSVD SDM_A4 AT34 M_DQM_A4

M_DATA_A[63..0] 15 SDQ_B32 AU27 M_DATA_B32

AL39 RSVD SDQ_B33 AN29 M_DATA_B33

SDQ_A32 AP32 M_DATA_A32 SDQ_B34 AR31 M_DATA_B34

SDQ_A33 AV34 M_DATA_A33 SDQ_B35 AM31 M_DATA_B35

SDQ_A34 AV38 M_DATA_A34 SDQ_B36 AP27 M_DATA_B36

SDQ_A35 AU39 M_DATA_A35 SDQ_B37 AR27 M_DATA_B37

SDQ_A36 AV32 M_DATA_A36 SDQ_B38 AP31 M_DATA_B38

AK40 RSVD SDQ_A37 AT32 M_DATA_A37 DDR_GMCH_VREF_B AM2 SVREF1 SDQ_B39 AU31 M_DATA_B39

SDQ_A38 AR34 M_DATA_A38

M_DQS_B[7..0] 16

SDQ_A39 AU37 M_DATA_A39 SDQS_B5 AP36 M_DQS_B5

M_DQS_BJ[7..0] 16

SDQS_B5* AM35 M_DQS_BJ5

M_DQS_A[7..0] 15 M_DQM_B[7..0] 16

SDQS_A5 M_DQS_A5 M_DQM_B5

DDR_GMCH_VREF_A AM4 SVREF0 SDQS_A5*

SDM_A5

AP42

AP40

AP39

M_DQS_AJ5

M_DQM_A5

M_DQS_AJ[7..0] 15

M_DQM_A[7..0] 15

M_DATA_A[63..0] 15

DDR_B SDM_B5

SDQ_B40

AR38

AP35 M_DATA_B40

M_DATA_B[63..0] 16

SDQ_B41 AP37 M_DATA_B41

SDQ_A40 AR41 M_DATA_A40 TP_RSV_AK18 AK18 RSV_TP3 SDQ_B42 AN32 M_DATA_B42

DDR_A SDQ_A41

SDQ_A42

SDQ_A43

AR42

AN43

AM40

M_DATA_A41

M_DATA_A42

M_DATA_A43

1D8V_STR

WW39 MOW/CRB1.01 update

(must remove pull-down resistor)

Double check in DG1.0

TP_RSV_AK23 AK23 RSV_TP2 SDQ_B43

SDQ_B44

SDQ_B45

AL35

AR35

AU38

M_DATA_B43

M_DATA_B44

M_DATA_B45

SDQ_A44 AU41 M_DATA_A44 SDQ_B46 AM38 M_DATA_B46

SDQ_A45 AU42 M_DATA_A45 TP_SMOCDCOMP1 AM3 SOCOMP1 SDQ_B47 AM34 M_DATA_B47

TP_RSV_AL17 AL17 RSV_TP1 SDQ_A46 AP41 M_DATA_A46

R274

TP_SMOCDCOMP0 AJ8 SOCOMP0 M_DQS_B[7..0] 16

TP_RSV_AK17 AK17 RSV_TP0 SDQ_A47 AN40 M_DATA_A47 SRCOMP1 AJ6 SRCOMP1 SDQS_B6 AG34 M_DQS_B6

M_DQS_BJ[7..0] 16

SRCOMP0 AL5 SRCOMP0 SDQS_B6* AG32 M_DQS_BJ6

M_DQS_A[7..0] 15 M_DQM_B[7..0] 16

SDQS_A6 AG42 M_DQS_A6

M_DQS_AJ[7..0] 15 SDM_B6 AJ39 M_DQM_B6

M_DATA_B[63..0] 16

SDQS_A6* AG41 M_DQS_AJ6

M_DQM_A[7..0] 15 80.6

SDM_A6 AG40 M_DQM_A6

M_DATA_A[63..0] 15

C462 SDQ_B48 AL34 M_DATA_B48

1

R0603 SDQ_B49

SDQ_A48 AL41 M_DATA_A48 * 0.1uF

16V, Y5V, +80%/-20% +/-1%

R271

80.6 SDQ_B50

AJ34

AF32

M_DATA_B49

M_DATA_B50

SDQ_A49 AL42 M_DATA_A49 C0603 +/-1% SDQ_B51 AF34 M_DATA_B51

2

SDQ_A50 AF39 M_DATA_A50 R0603 SDQ_B52 AL31 M_DATA_B52

SDQ_A51 AE40 M_DATA_A51 SDQ_B53 AJ32 M_DATA_B53

B B

SDQ_A52 AM41 M_DATA_A52 SDQ_B54 AG35 M_DATA_B54

SDQ_A53 AM42 M_DATA_A53 SDQ_B55 AD32 M_DATA_B55

SDQ_A54 AF41 M_DATA_A54

M_DQS_B[7..0] 16

SDQ_A55 AF42 M_DATA_A55 SDQS_B7 AD36 M_DQS_B7

M_DQS_BJ[7..0] 16

SDQS_B7* AD38 M_DQS_BJ7

M_DQS_A[7..0] 15 M_DQM_B[7..0] 16

SDQS_A7 AC42 M_DQS_A7

M_DQS_AJ[7..0] 15 SDM_B7 AD39 M_DQM_B7

M_DATA_B[63..0] 16

SDQS_A7* AC41 M_DQS_AJ7 SRCOMP[1:0]

M_DQM_A[7..0] 15

SDM_A7 AC40 M_DQM_A7

M_DATA_A[63..0] 15 10 mils width, 10 mils spacing, max 1.5" length SDQ_B56 AC32 M_DATA_B56

place cap/res within 1" of GMCH package SDQ_B57 AD34 M_DATA_B57

SDQ_A56 AD40 M_DATA_A56 SDQ_B58 Y32 M_DATA_B58

SDQ_A57 AD43 M_DATA_A57 SDQ_B59 AA32 M_DATA_B59

SDQ_A58 AA39 M_DATA_A58 SDQ_B60 AF35 M_DATA_B60

SDQ_A59 AA40 M_DATA_A59 SDQ_B61 AF37 M_DATA_B61

SDQ_A60 AE42 M_DATA_A60 SDQ_B62 AC33 M_DATA_B62

SDQ_A61 M_DATA_A61 SDQ_B63 M_DATA_B63

SDQ_A62

AE41

AB41 M_DATA_A62 4 OF 7 AC35

3 OF 7 SDQ_A63 AB42 M_DATA_A63

1D8V_STR 1D8V_STR

R336 R321

1K 1K

+/-1% +/-1%

R0603 R0603

DDR_GMCH_VREF_A DDR_GMCH_VREF_B

R333 C290 R324 C285

1

A 1K

+/-1% * 0.1uF

16V, Y5V, +80%/-20%

1K

+/-1% * 0.1uF

16V, Y5V, +80%/-20%

A

R0603 C0603 R0603 C0603

2

FOXCONN PCEG

width 12 mils, spacing 12 mils Title

5 mils width/spacing minimum for a max. of 300 mils

in the GMCH break-out area Lakeport GMCH -2

place each cap to Vref pin Size Document Number Rev

C 945P01 A

Date: Monday, June 13, 2005 Sheet 13 of 30

5 4 3 2 1

5 4 3 2 1

U14E 1D8V_STR

1D5V_CORE

VCCSM BC18

N17 VCC 1.0 VCCSM BC22

P17 VCC VCCSM BC26

AH4 VCC VCCSM BC31 1D5V_CORE 1D5V_CORE

AJ5 VCC VCCSM BC35 U14F U14I

VCC VCCSM U14H

AK4 BC13

AF30 VCC VCCSM BB42 A16 VSS VSS AL2 BB39 VSS VSS M10

AK20 VCC VCCSM BB38 AJ15 VCC 1.0 VCC AC15 A22 VSS VSS AL21 BB41 VSS VSS M13

AK3 VCC VCCSM BB33 AG23 VCC VCC AC17 A26 VSS VSS AL23 BB6 VSS VSS M20

AK2 VCC VCCSM BB28 AG22 VCC VCC AC18 A31 VSS VSS AL24 BC4 VSS VSS M21

AJ14 VCC VCCSM BB24 AG21 VCC VCC AC20 A35 VSS VSS AL27 BC9 VSS VSS M3

AK14 VCC VCCSM BB20 AG20 VCC VCC AC24 A4 VSS VSS AL3 C12 VSS VSS M35

AK15 VCC VCCSM BB16 AG19 VCC VCC AC26 A40 VSS VSS AL32 C14 VSS VSS M37

AJ13 VCC VCCSM AY41 AG18 VCC VCC AC27 AA11 VSS VSS AL33 C22 VSS VSS M5

D

AH2 VCC VCCSM AW21 AG17 VCC VCC AD15 AA12 VSS VSS AL37 C3 VSS VSS M8 D

AH1 VCC VCCSM AW13 AG15 VCC VCC AD17 AA14 VSS VSS AL43 C40 VSS VSS M9

AG14 VCC VCCSM AV31 AB18 VCC VCC AJ17 AA21 VSS VSS AL7 C5 VSS VSS N13

AG13 VCC VCCSM AV21 Y27 VCC VCC AD19 AA23 AM33 C7 N15

VCC VSS VSS VSS VSS

AG12 VCC VCCSM AW35 Y25 VCC AD21 AA25 VSS VSS AM36 D1 VSS VSS N2

AG11 VCC VCCSM AW34 Y19 VCC VCC AD23 AA27 AM37 D10 N24

VSS VSS VSS VSS

AG10 VCC VCCSM AW31 Y18 VCC VCC AD25 AA29 VSS VSS AM39 D16 VSS VSS N26

AG9 VCC VCCSM AW29 W27 VCC VCC AD26 AA3 VSS VSS AM5 D2 VSS VSS N27

AG8 VCC VCCSM AW24 W26 VCC VCC AE17 AA31 AM7 D20 N29

VCC VSS VSS VSS VSS

AG7 VCCSM AW20 W20 VCC VCC AE18 AA33 VSS VSS AM9 D21 VSS VSS N31

AG6 VCC VCCSM AW15 U19 VCC VCC AE20 AA36 VSS VSS AN13 D43 VSS VSS N33

AG5 VCC VCCSM AV42 U18 VCC VCC AE22 AA8 VSS VSS AN15 D5 VSS VSS N36

AG4 VCC VCCSM AV23 U17 VCC VCC AE24 AB2 VSS VSS AN17 E12 VSS VSS N39

AG3 VCC VCCSM AV18 U15 VCC VCC AJ18 AB43 VSS VSS AN18 E13 VSS VSS N43

AG2 VCC R24 VCC VCC AE26 AC10 VSS VSS AN2 E17 VSS VSS N6

AF14 VCC 1D5V_PE_GMCH R23 VCC VCC AE27 AC14 VSS VSS AN20 E18 VSS VSS N8

AF13 VCC R21 VCC VCC AF15 AC19 VSS VSS AN21 E20 VSS VSS P14

AF12 VCC VCC_EXP AD4 R20 VCC VCC AF17 AC2 VSS VSS AN23 E21 VSS VSS P15

VCC VCC_EXP VCC VCC

POWER

AF11 AD5 R18 AF19 AC21 VSS VSS AN24 E3 VSS VSS P24

POWER

AF10 VCC VCC_EXP AD6 AF29 VCC VCC AF21 AC23 VSS VSS AN26 E32 VSS VSS P26

AF9 VCC VCC_EXP AD8 R17 VCC VCC AF23 1D8V_STR AC25 VSS VSS AN27 E4 VSS VSS P27

AF8 VCC VCC_EXP AD10 R15 VCC VCC AJ20 AC29 VSS VSS AN31 E7 VSS VSS P29

AF7 VCC VCC_EXP AD12 U20 VCC AC3 VSS VSS AN4 E9 VSS VSS P3

AF6 VCC VCC_EXP N5 U21 VCC VCCSM BC40 AC31 VSS VSS AN42 F13 VSS VSS P30

AD14 VCC VCC_EXP N7 U22 VCC VCCSM AY43 AC36 VSS VSS AP10 F18 VSS VSS R12

AC22 VCC VCC_EXP N9 U23 VCC AC37 VSS VSS AP12 F2 VSS VSS R14

AB23 VCC VCC_EXP N10 U24 VCC AC38 VSS VSS AP29 F26 VSS VSS R26

AB22 VCC VCC_EXP N12 U25 VCC AC39 AP34 F34 R29

VSS VSS VSS VSS

AB21 VCC VCC_EXP R5 U26 VCC AC7 VSS VSS AP38 F42 VSS VSS R30

AA22 VCC VCC_EXP R10 V15 VCC AD11 VSS VSS AP5 F6 VSS VSS R31

P21 VCC VCC_EXP AE2 V17 VCC AD13 VSS VSS AP7 G10 VSS VSS R34

P20 VCC VCC_EXP R11 V18 VCC AD18 VSS VSS AR1 G13 VSS VSS R37

FSB_VTT P18 VCC VCC_EXP R13 AF25 VCC AD20 VSS VSS AR15 G15 VSS VSS R39

VCC_EXP U6 AF26 VCC AD22 VSS VSS AR20 G18 VSS VSS R6

F27 VTT VCC_EXP U7 AF27 VCC AD24 AR24 G20 R9

VCC_EXP VSS VSS VSS VSS

G23 VTT U8 AG24 VCC AD27 VSS VSS AR32 G21 VSS VSS T2

H23 VTT VCC_EXP U13 V19 VCC AD29 AR37 G24 T42

VSS VSS VSS VSS

J23 VTT VCC_EXP V5 V20 VCC AD33 VSS VSS AR39 G27 VSS VSS U12

C K23 VTT VCC_EXP V6 V21 VCC AD35 VSS VSS AR43 G29 VSS VSS U14 C

L23 VTT VCC_EXP V7 V22 VCC AD37 VSS VSS AR6 G3 VSS VSS U29

M23 VTT VCC_EXP V9 V23 VCC AD42 VSS VSS AT12 G31 VSS VSS U3

A24 VTT VCC_EXP AE3 V25 VCC AD7 VSS VSS AT17 G32 VSS VSS U31

N23 VTT VCC_EXP V10 V27 VCC AD9 VSS VSS AT18 G35 VSS VSS U33

C26 VTT VCC_EXP V13 W17 VCC AE19 VSS VSS AT21 G38 VSS VSS U36

D23 VTT VCC_EXP Y13 W18 VCC AE21 VSS VSS AT23 G5 VSS VSS U38

D24 VTT VCC_EXP AA5 W19 VCC AE23 VSS VSS AT26 G7 VSS VSS U5

D25 VTT VCC_EXP AA13 W22 VCC AE25 VSS VSS AT27 G9 VSS VSS U9

P23 VTT VCC_EXP AC5 W24 VCC AF1 VSS VSS AT31 H12 VSS VSS V11

F23 VTT VCC_EXP AC6 Y15 VCC AF18 VSS VSS AU12 H17 VSS VSS V12

E27 VTT VCC_EXP AC13 Y17 VCC AF2 VSS VSS AU13 H26 VSS VSS V14

E26 VTT VCC_EXP AD1 Y21 VCC AF20 VSS VSS AU15 H27 VSS VSS V2

E24 VTT VCC_EXP AD2 Y23 VCC AF22 VSS VSS AU17 H32 VSS VSS V24

E23 VTT VCC_EXP AE4 AA15 VCC AF24 VSS VSS AU20 J10 VSS VSS V26

C25 VTT VCC_EXP N11 AA17 VCC AF3 VSS VSS AU21 J12 VSS VSS V29

C23 VTT AA18 VCC AF33 VSS VSS AU24 J2 VSS VSS V34

B26 VTT AA19 VCC AF36 VSS VSS AU26 J21 VSS VSS V36

B25 VTT AA20 VCC AF38 VSS VSS AU29 J24 VSS VSS V37

B24 VTT AA24 VCC AF43 VSS VSS AU32 J29 VSS VSS V38

B23 VTT AA26 VCC AF5 VSS VSS AU34 J38 VSS VSS V39

AB17 VCC AG30 VSS VSS AU6 J43 VSS VSS V43

VCCA_DPLLB B19 VCCA_DPLLB AB19 VCC AG31 AU9 J5 V8

VCCA_SMPLL VSS VSS VSS VSS

2D5V_DAC VCCA_SMPLL B20 AB20 VCC AG33 VSS VSS AV10 J7 VSS VSS W21

VCCA_HPLL C21 VCCA_HPLL AB24 VCC AG36 VSS VSS AV17 K10 VSS VSS W23

2D5V_MCH VCCA_DPLLA C19 VCCA_DPLLA AB25 VCC AG37 AV2 K12 W25

VSS VSS VSS VSS

C18 VCCA_DAC AB26 VCC AG38 VSS VSS AV37 K13 VSS VSS W3

B18 VCCA_DAC AB27 VCC AG39 VSS VSS AW10 K15 VSS VSS Y12

D19 VCC2 7 OF 7 AH42 VSS VSS AY1 K20 VSS VSS Y14

AJ10 VSS VSS B11 K27 VSS VSS Y2

AJ30 VSS VSS B13 K3 VSS VSS Y20

VCCA_EXPPLL B17 VCCA_EXPPLL AJ31 VSS VSS B21 K32 VSS VSS Y22

A18 VSSA_DAC 6 OF 7 AJ33 VSS VSS B22 K34 VSS VSS Y24

AJ35 VSS VSS B28 K37 VSS VSS Y26

AJ37 VSS VSS B33 K39 VSS VSS Y29

AJ7 VSS VSS B38 K5 VSS VSS Y31

1D5V_CORE 1D5V_CORE 1D5V_CORE AK24 B4 K6 Y35

VSS VSS VSS VSS

B

AK26 VSS VSS B6 K7 VSS VSS Y37 B

L16 R200 AK29 VSS VSS B9 L12 VSS VSS Y39

AK30 BA4 L13 Y42

*

VCCA_EXPPLL C490 C489 VSS VSS VSS VSS

AL1 VSS VSS BA42 L2 VSS VSS Y5

1

L0805 1uH

0.5

C175 C185

2D5V_MCH L15 from GMCH to 1st cap must be less than 1 inch

* 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20%

AL10

AL12

VSS

VSS

VSS

VSS

BB11

BB14

L24

L26

VSS

VSS

VSS

VSS

Y6

Y9

1

* 10uF

* 0.1uF

* 2D5V_DAC C0603 C0603 AL13 BB19 L29

2

R0603 10V, Y5V, +80%/-20% 16V, Y5V, +80%/-20% Dummy Dummy VSS VSS VSS

AL15 VSS VSS BB3 L31 VSS

+/-1% C1206 C0603 AL18 BB34 L42

2

FB L0805 180 Ohm EC19 C173 C174 VSS VSS VSS

1

* 100uF

16V, +/-20% * 0.1uF

16V, Y5V, +80%/-20% * 10nF

25V, X7R, +/-10%

QG82945G<REV> QG82945G <REV>

L12 Double check high-frequency requirements for GMCH in new DG or CRB

CE20D50H110 C0603 C0603

<PART_SYM_NUM> <PART_SYM_NUM>

2

2

*

VCCA_HPLL

1D5V_CORE 1D5V_CORE

C191 2D5V_DAC Filter

L1206 10uH

1

* 0.1uF

16V, Y5V, +80%/-20%

C0603 C492 C491

2

1

L10

* 0.1uF

16V, Y5V, +80%/-20% * 0.1uF

16V, Y5V, +80%/-20%

C0603 C0603

2

2

*

VCCA_DPLLA Dummy Dummy

1D5V_CORE from GMCH to 1st cap must be less than 1 inch

EC21 C194

L1206 10uH

1

* 220uF

6.3V, +/-20% * 0.1uF

16V, Y5V, +80%/-20%

L20 1 2 L1206 0.1uH 1D5V_PE_GMCH

place GMCH backside

1D5V_CORE

Place in 1D5V_CORE plane as close to the GMCH as possible

*

CE20D50H110 C0603 L19 L0805 0.1uH EC29 C238 C237

2

Dummy * 220uF

6.3V, +/-20% * 10uF

6.3V, Y5V, +80%/-20% * 10uF

6.3V, Y5V, +80%/-20%

L9

CE20D50H110 C0805 C0805 C242 C243 C244

2

2

*

1

VCCA_DPLLB

1D8V_STR Connect ground sides of caps with * 10uF

6.3V, Y5V, +80%/-20% * 10uF

6.3V, Y5V, +80%/-20% * 10uF

6.3V, Y5V, +80%/-20%

EC20 C193 co-layout with inductor traces to GND balls C0805 C0805 C0805

2

L1206 10uH

1

* 220uF

6.3V, +/-20% * 0.1uF

16V, Y5V, +80%/-20% PCI Express Filter

(less than 100 mils from the package)

CE20D50H110 C0603

2

Place in FSB_VTT plane as close to the GMCH as possible C274 C275 C276 1D5V_CORE Decoupling

1

A

L11

(less than 100 mils from the package) * 2.2uF

6.3V, Y5V, +80%/-20% * 2.2uF

6.3V, Y5V, +80%/-20% * 2.2uF

6.3V, Y5V, +80%/-20%

A

FSB_VTT C0603 C0603 C0603

2

2

*

VCCA_SMPLL

C190

L1206 10uH

1

* 0.1uF C203 C209 C129 C192

1

16V, Y5V, +80%/-20%

* 10uF

* 10uF

* 10uF

* 0.1uF C273 C277 C270

1

C0603 6.3V, Y5V, +80%/-20% 6.3V, Y5V, +80%/-20% 6.3V, Y5V, +80%/-20% 16V, Y5V, +80%/-20%

* 2.2uF

* 2.2uF

* 2.2uF

2

C0805 C0805 C0805 C0603 6.3V, Y5V, +80%/-20% 6.3V, Y5V, +80%/-20% 6.3V, Y5V, +80%/-20%

FOXCONN PCEG

2

C0603 C0603 C0603

2

FSB_VTT Decoupling Title

from GMCH to 1st cap must be less than 1 inch. Lakeport GMCH -3

If 0.5 Ohm, +/- 1%, R0603 is not easy get, you could replace by GMCH Memory Decoupling

Size Document Number Rev

0 Ohm, +/- 1%, R0603.

C 945P01 A

Date: Saturday, July 16, 2005 Sheet 14 of 30

5 4 3 2 1

5 4 3 2 1

DIMM1

DDR2 Channel A DIMM1 DDR2 Channel A Termination

2 VSS NC 68

5 VSS NC/TEST 102

8 VSS NC 19

11 VSS

1D8V_STR 14 VSS M_ODT_A1

17 VSS ODT1 77 M_ODT_A1 13

20 195 M_ODT_A0

VSS ODT0 M_ODT_A0 13

23 VSS

26 VSS green color , P/N: AT24011-H3G

29 VSS

R361 32 42 blue color , P/N: AT24011-H3L

1K VSS CB<0>

35 VSS CB<1> 43

+/-1% 38 48

R0603 VSS CB<2>

41 VSS CB<3> 49

D

44 VSS CB<4> 161 D

47 162 VTT_DDR

VSS CB<5> M_BS_A[2..0] 13

SMVREF_A 50 167 RN20

VSS CB<6>

65

66

VSS CB<7> 168 *1 2

M_MAA_A5

M_MAA_A8

M_MAA_A[13..0] 13

R366 C343 VSS 3 4 M_MAA_A6

79 VSS 5 6

1

1K

+/-1% * 0.1uF

16V, Y5V, +80%/-20%

82

85

VSS

VSS M_DQS_AJ[7..0] 13

7 8

M_MAA_A4

R0603 C0603 88 33

2

VSS M_DQS_A0 +/-5%

91 VSS DQS<0> 7

94 6 8P4R0402

VSS DQS#<0> M_DQS_AJ0 VTT_DDR

97 VSS

100 16 M_DQS_A1 R405 33 R0402 +/-5% M_MAA_A10

VSS DQS<1>

103 VSS DQS#<1> 15

Place this cap at the resistor divider circuit 106 M_DQS_AJ1

VSS M_DQS_A2 RN22 R406 43 R0402 +/-5%

109 VSS DQS<2> 28 M_SCS_A0J 13

112

115

VSS DQS#<2> 27

M_DQS_AJ2

*1 2

M_MAA_A3

M_MAA_A2 R410 43 R0402 +/-5%

M_SCS_A1J 13

VSS M_DQS_A3 3 4 M_MAA_A1

118 VSS DQS<3> 37 5 6

121 36 M_MAA_A0

VSS DQS#<3> M_DQS_AJ3 7 8

124 VSS

127 84 M_DQS_A4 33

1D8V_STR VSS DQS<4> +/-5% R408 43 R0402 +/-5% M_ODT_A0

130 VSS DQS#<4> 83

133 M_DQS_AJ4 8P4R0402

VSS M_DQS_A5

136 VSS DQS<5> 93

139 92 RN19

VSS DQS#<5>

142

145

VSS

105

M_DQS_AJ5

M_DQS_A6

*1 2

M_MAA_A12

M_MAA_A11

R411 43 R0402 +/-5% M_ODT_A1

Dummy

Dummy

VSS DQS<6> 3 4

EC34

EC41

EC53