Professional Documents

Culture Documents

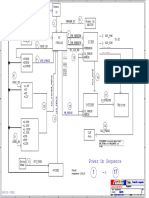

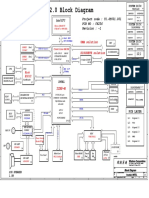

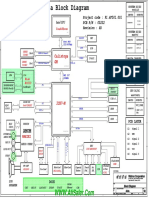

Blok Diagram

Uploaded by

Muhammad MaimanaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Blok Diagram

Uploaded by

Muhammad MaimanaCopyright:

Available Formats

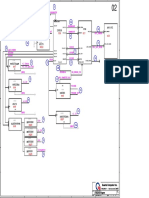

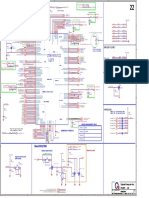

5 4 3 2 1

SLP_S3#(SUSB#): 4 39

S3 Sleep Power plane control Assertion of SLP_S3# shuts off power to non-critical components NBSWON#

when system transitions to S3, S4, or S5 states. 5 +5VPCU +5V_S5

SLP_S4#(SUSC#): MOS

S5_ON PQ33

S4 Sleep Power plane control - Assertion of SLP_S4# shuts power off to non-critical components 6

when system transitions to S4 or S5 state. (S5D)

2 +3VPCU +3V_S5

1 MOS

AC Adapter +3VPCU PQ12

Always System power

BATT Charger VIN

D Regulator 7 D

PU2 +5VPCU

Battery EC_RSMRST#

PU2 RSMRST#

10 8

3

DNBSWON#

SUSON(SUSD) PWRBTN#

13 SUSC# 9

SLP_S4#

MAINON(MAIND)

EC SUSB#

14 SLP_S3#

MAIND +3VPCU/+5VPCU +3V

MOS +5V 22

23 PCH

ECPWROK

TPT_PWROK

PWRGD

MAIND +1.5VSUS

+1.5V

MOS

100ms

C

MAINON C

+RC VIN 15

+1.05V

VR

HWPG_1.05V VRM_PWRGOOD

16

CPU_PG PLTRST#

VIN +VCC_CORE

17

Regulator VCCGFX

PU8

HWPG_SYS

+3.3V_PRIME_ON IMVP_PWRGD/ HWPG_VCCGFX 18

(From EC)

19a 21

+3V 19b HWPG CK505 24 25

+3V_PRIME

MOS EN

PQ9 H_PWRGD PLTRST_N

B B

20 HWPG_1.8V D

+3VSUS

MOS MAINON_ON_G NMOS

+1.8V HWPG_1.5V G

PU7 S

D

GND

NMOS MAINON_ON_G 12

G For Power Down Sequence PWRGD RESET_L

S For Power Down Sequence

DDR3_VCCA_PWROK

GND

MAINON +0.75V_DDR_VTT

VIN

CPU

SUSON Regulator +SMDDR_VREF

+1.5VSUS

PU5 DDR3_DRAM_PWROK

11

+3VPCU

SUSD MOS +3VSUS

PQ22

A A

Quanta Computer Inc.

PROJECT : ZE7

Size Document Number Rev

power sequence block diagram 1B

Date: Wednesday, November 02, 2011 Sheet 39 of 40

5 4 3 2 1

You might also like

- Samsung RV408 6 - BA41-01335A 01334A 01336ADocument1 pageSamsung RV408 6 - BA41-01335A 01334A 01336AHumberto AndujarNo ratings yet

- Scahematic HP Dm1Document31 pagesScahematic HP Dm1hernanNo ratings yet

- f81f4 Quanta nm9 R1a Schematics PDFDocument31 pagesf81f4 Quanta nm9 R1a Schematics PDFsaleemNo ratings yet

- Wistron Power ON - SequenceDocument1 pageWistron Power ON - SequenceCarlos Gomes100% (1)

- Reset: LPC1343 LPC1768 LPC1343 LPC1768Document1 pageReset: LPC1343 LPC1768 LPC1343 LPC1768FernandoAdriánNo ratings yet

- Dell Power On 2Document1 pageDell Power On 2Rajesh BarangeNo ratings yet

- RTC 6705Document12 pagesRTC 6705a637888No ratings yet

- LAPTOP POWER SequenceDocument1 pageLAPTOP POWER SequenceIshwer Rao100% (1)

- Acer Aspire - 5338 - 5736G - 5738 - 5738G - 5738DG - 5738 1 08245-1 - JV50-MV - 01 - Finger - Print - BoardDocument1 pageAcer Aspire - 5338 - 5736G - 5738 - 5738G - 5738DG - 5738 1 08245-1 - JV50-MV - 01 - Finger - Print - BoardffffNo ratings yet

- Quanta DAKL2FMB8F0 Lenovo Y460P 2Document1 pageQuanta DAKL2FMB8F0 Lenovo Y460P 2ougeyfNo ratings yet

- IT8587Document1 pageIT8587greardo jose rodriguezNo ratings yet

- Acer Aspire 5738 Aspire 5338 JV50 - MV - SBDocument60 pagesAcer Aspire 5738 Aspire 5338 JV50 - MV - SBTsukamoto TsukushiNo ratings yet

- 5738Z JV50-MV Schematic DiagramDocument60 pages5738Z JV50-MV Schematic DiagramSelmn Şnlı100% (1)

- Schematis HP V3000 DV2000 IntelDocument47 pagesSchematis HP V3000 DV2000 Intelmadoo0% (2)

- JM41/JM51 UMA Block Diagram: Intel CPUDocument41 pagesJM41/JM51 UMA Block Diagram: Intel CPUAlexander BronnikovNo ratings yet

- ACER Aspire 7736 GM45 JV71-MV - DDR3Document62 pagesACER Aspire 7736 GM45 JV71-MV - DDR3miecho1985No ratings yet

- Wistron DW50 Winery15 - 48.4et06.0sa 09628-Sa - Dcin BoardDocument9 pagesWistron DW50 Winery15 - 48.4et06.0sa 09628-Sa - Dcin BoardWillian Angelo50% (2)

- Schematic DiagramDocument1 pageSchematic DiagramMartunis HasanNo ratings yet

- Project Code: 91.4S401.001 PCB P/N:06230 Revision: SC: Intel CPUDocument1 pageProject Code: 91.4S401.001 PCB P/N:06230 Revision: SC: Intel CPUEgeNo ratings yet

- Giga Luoc Do Kich NguonDocument2 pagesGiga Luoc Do Kich NguonNguyễn Văn TặngNo ratings yet

- Giga Luoc Do Kich NguonDocument2 pagesGiga Luoc Do Kich NguonĐiện LươngNo ratings yet

- Y015/Y016 Point To Point Diagram 1/2: Main BoardDocument3 pagesY015/Y016 Point To Point Diagram 1/2: Main BoardWilliam LozadaNo ratings yet

- S802 MBX Ref Basic V03 131212 ReDocument16 pagesS802 MBX Ref Basic V03 131212 ReyhyzhjNo ratings yet

- JM41 Block Diagram: Intel CPUDocument40 pagesJM41 Block Diagram: Intel CPUMayank Mani SinghNo ratings yet

- Compal LS-5656P r10 PWR BoardDocument1 pageCompal LS-5656P r10 PWR BoardQuenitoLucianoJoãoNo ratings yet

- Anote2 SC 0112 1330 Final PDFDocument58 pagesAnote2 SC 0112 1330 Final PDFivan bogdanNo ratings yet

- Schematics V3000aDocument39 pagesSchematics V3000aBack UpsNo ratings yet

- Lpcxpresso1115 With Cmsis Dap SCHDocument4 pagesLpcxpresso1115 With Cmsis Dap SCHAnkur SharmaNo ratings yet

- Something About Some Electronic Components That You Will Never UseDocument47 pagesSomething About Some Electronic Components That You Will Never UseIosef Nee-MeNo ratings yet

- ASUS A8E A8S F8S Power On SequenceDocument1 pageASUS A8E A8S F8S Power On SequenceEduinMaracuchoFernandezChaparroNo ratings yet

- Mu5dc CH7DC (Rev 2.0)Document86 pagesMu5dc CH7DC (Rev 2.0)aka.virtuozNo ratings yet

- Anote2.0 Block Diagram: UMA Solution DISCRETE SolutionDocument58 pagesAnote2.0 Block Diagram: UMA Solution DISCRETE SolutionIIIkwarkaNo ratings yet

- XT1710-Moto Z2 Play - L3 BB Troubleshooting Guide V1.0Document102 pagesXT1710-Moto Z2 Play - L3 BB Troubleshooting Guide V1.0karenchristinasantos87100% (1)

- Fully Integrated Electronic Stability Control/electronic Stability Program Braking ChipDocument135 pagesFully Integrated Electronic Stability Control/electronic Stability Program Braking Chipwen huNo ratings yet

- 990FXA-UD5Document2 pages990FXA-UD5Ady PutraNo ratings yet

- Acer Aspire Timeline 4810 5810Document48 pagesAcer Aspire Timeline 4810 5810butbutterNo ratings yet

- JM41/JM51 Discrete Block Diagram: Intel CPUDocument49 pagesJM41/JM51 Discrete Block Diagram: Intel CPUAlexander BronnikovNo ratings yet

- Compal LS-5657P r10 Led BoardDocument1 pageCompal LS-5657P r10 Led BoardQuenitoLucianoJoãoNo ratings yet

- Acer Aspire 4410-4410t 1 WISTRON jm41 - 08266-1Document40 pagesAcer Aspire 4410-4410t 1 WISTRON jm41 - 08266-1Maintenance broNo ratings yet

- PICKit2 Clone - SchematicDocument1 pagePICKit2 Clone - SchematicArmando HernandezNo ratings yet

- PC Adapter HelpDocument2 pagesPC Adapter Helpdaniel contrerasNo ratings yet

- HP Pavilion dv2000 Intel 945 Akita 05232 Rev SD SchematicsDocument39 pagesHP Pavilion dv2000 Intel 945 Akita 05232 Rev SD SchematicsGyan PrakashNo ratings yet

- STM32F103VET6Document1 pageSTM32F103VET6HuseyinNo ratings yet

- SCHEMATIC MiniQDocument1 pageSCHEMATIC MiniQwinterzhangNo ratings yet

- MP4 Diagram PDFDocument2 pagesMP4 Diagram PDFAriel MedinaNo ratings yet

- HP DV6 DV7 Colossus 15 17 Discrete Block Diagram SMBus PCH KBCDocument1 pageHP DV6 DV7 Colossus 15 17 Discrete Block Diagram SMBus PCH KBCzigmund zigmundNo ratings yet

- Tidu 466Document8 pagesTidu 466KINGS entertainment KHANNo ratings yet

- Sony VGN-CR MBX - 177 - Quanta Gd1 - TouchpadDocument1 pageSony VGN-CR MBX - 177 - Quanta Gd1 - TouchpadNicolás TorresNo ratings yet

- PackardBell EasyNote ML65 WISTRON SJM50-PUDocument56 pagesPackardBell EasyNote ML65 WISTRON SJM50-PUu6k5lp l2y3z0No ratings yet

- DDCSCL Ddcsda: ST - DetDocument14 pagesDDCSCL Ddcsda: ST - DetMaria PerezNo ratings yet

- Toshiba Satellite 30CDT (Compal LA-971)Document36 pagesToshiba Satellite 30CDT (Compal LA-971)Barton EletronicsNo ratings yet

- Schematic Franzininho STM32 2023-07-06Document1 pageSchematic Franzininho STM32 2023-07-06Entendendo as CoisasNo ratings yet

- Debugger Lure Rev-ADocument1 pageDebugger Lure Rev-AtomNo ratings yet

- IT8987EDocument1 pageIT8987ElioNo ratings yet

- CNC-fabtroller SchematicDocument1 pageCNC-fabtroller SchematicTomi OzzyNo ratings yet

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsFrom EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsRating: 1 out of 5 stars1/5 (1)

- Learn Digital and Microprocessor Techniques On Your Smartphone: Portable Learning, Reference and Revision Tools.From EverandLearn Digital and Microprocessor Techniques On Your Smartphone: Portable Learning, Reference and Revision Tools.No ratings yet

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsFrom EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsNo ratings yet

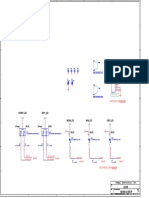

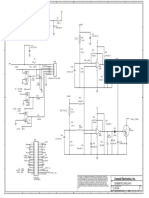

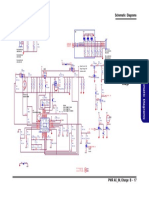

- PWR AC - IN, Charge: Schematic DiagramsDocument1 pagePWR AC - IN, Charge: Schematic DiagramsMuhammad MaimanaNo ratings yet

- Product Information: Infovision Optoelectronics (Kunshan) Co.,LtdDocument30 pagesProduct Information: Infovision Optoelectronics (Kunshan) Co.,LtdMuhammad MaimanaNo ratings yet

- ZAAA x32 Ironman SK (ZAA) & Captain SK (ZAAA) MB 6L E Version PDFDocument48 pagesZAAA x32 Ironman SK (ZAA) & Captain SK (ZAAA) MB 6L E Version PDFSebastian StanacheNo ratings yet

- Data SheetDocument39 pagesData SheetMuhammad MaimanaNo ratings yet

- M1115 PDFDocument74 pagesM1115 PDFcastelectorNo ratings yet

- ZAAA x32 Ironman SK (ZAA) & Captain SK (ZAAA) MB 6L E Version PDFDocument48 pagesZAAA x32 Ironman SK (ZAA) & Captain SK (ZAAA) MB 6L E Version PDFSebastian StanacheNo ratings yet

- SM-A217F Manual de Servicio Anibal Garcia IrepairDocument24 pagesSM-A217F Manual de Servicio Anibal Garcia IrepairMatias Alejandro Ruiz DiazNo ratings yet

- Mode S Introduction INDRA PDFDocument113 pagesMode S Introduction INDRA PDFafrinaldy ismailNo ratings yet

- PX4 i&PX6 I Service ManualDocument282 pagesPX4 i&PX6 I Service Manualbramirez8098No ratings yet

- Notes On Essential of ItDocument9 pagesNotes On Essential of ItDrRam Singh KambojNo ratings yet

- Tic 300 Pro Tic TracerDocument2 pagesTic 300 Pro Tic Traceredwin-cuchieyesNo ratings yet

- AFT Series PDFDocument2 pagesAFT Series PDFFahim YaseenNo ratings yet

- Design and Construction of The CircuitsDocument10 pagesDesign and Construction of The Circuitsepi guzmanNo ratings yet

- Improved-Power Quality Bridgeless - Converter-Based Multiple-Output SmpsDocument11 pagesImproved-Power Quality Bridgeless - Converter-Based Multiple-Output SmpsKalyan Reddy AnuguNo ratings yet

- July - 2020: VIT Research Entrance ExaminationDocument35 pagesJuly - 2020: VIT Research Entrance ExaminationAnbumaniNo ratings yet

- DSNGDocument222 pagesDSNGSimpatikus SimpatikusNo ratings yet

- SA 16200AHD 2 1U Specs 1 PDFDocument1 pageSA 16200AHD 2 1U Specs 1 PDFEdwin EliasNo ratings yet

- Device Tree Tut - Power - ePAPR - APPROVED - v1.1 PDFDocument108 pagesDevice Tree Tut - Power - ePAPR - APPROVED - v1.1 PDFafdgtdsghfNo ratings yet

- Chaptersix: Microwave ResonatorsDocument91 pagesChaptersix: Microwave ResonatorsnaingNo ratings yet

- 6n1 SPK Prot Rev 1.2B - With Basic Function How It WorksDocument34 pages6n1 SPK Prot Rev 1.2B - With Basic Function How It Worksអំភ្លី សំលេងNo ratings yet

- LF351 Wide Bandwidth JFET Input Operational Amplifier: Literature Number: SNOSBH2Document14 pagesLF351 Wide Bandwidth JFET Input Operational Amplifier: Literature Number: SNOSBH2elettroiceNo ratings yet

- VocoderDocument12 pagesVocoderKola OladapoNo ratings yet

- DatasheetDocument2 pagesDatasheetJuliaaplicNo ratings yet

- LM117/217 LM317: 1.2V To 37V Voltage RegulatorDocument11 pagesLM117/217 LM317: 1.2V To 37V Voltage RegulatorchzelNo ratings yet

- Lab 1 Silicon Diode S21314Document5 pagesLab 1 Silicon Diode S21314Muhd RzwanNo ratings yet

- DP Chipset 15035 DriversDocument598 pagesDP Chipset 15035 DriversJuan Carlos Gonzalez LNo ratings yet

- Low Power 8-Bit ALU Design Using Full Adder and Multiplexer: Anitesh Sharma Ravi TiwariDocument5 pagesLow Power 8-Bit ALU Design Using Full Adder and Multiplexer: Anitesh Sharma Ravi TiwariShanmuga PriyaNo ratings yet

- CCN Lab 2.Document3 pagesCCN Lab 2.buntuNo ratings yet

- Unit III Resonance and Coupled CircuitsDocument28 pagesUnit III Resonance and Coupled CircuitsSaravana SelvanNo ratings yet

- LECTURE - 6 (IOTPP) Faculty Copy RoughDocument33 pagesLECTURE - 6 (IOTPP) Faculty Copy Roughrega OpNo ratings yet

- Cree Direct Attach™ Da1000™ Leds: Cxxxda1000-Sxxx00-2-GDocument6 pagesCree Direct Attach™ Da1000™ Leds: Cxxxda1000-Sxxx00-2-GidrisssoftNo ratings yet

- Panasonic Th-37pv80pa Th-37px80ba Th-37px80ea Th-42pv80pa Th-42px80ba Th-42px80ea Chassis Gph11deDocument175 pagesPanasonic Th-37pv80pa Th-37px80ba Th-37px80ea Th-42pv80pa Th-42px80ba Th-42px80ea Chassis Gph11depagy snvNo ratings yet

- Handout03c Troubleshooting Guide3aDocument5 pagesHandout03c Troubleshooting Guide3aBit CoinNo ratings yet

- Classification of Control SystemsDocument15 pagesClassification of Control SystemsMohankumar V.No ratings yet

- VW T4 Campervan Wiring DiagramDocument2 pagesVW T4 Campervan Wiring DiagramWhatton0% (1)

- Ghulam Murtaza CVDocument2 pagesGhulam Murtaza CVSheikh Usman MunirNo ratings yet