0% found this document useful (0 votes)

382 views18 pagesAddressing Modes Explained

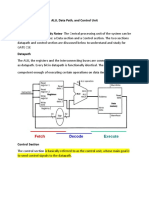

This document discusses different addressing modes used in computer architecture. It defines addressing modes as rules for interpreting the address field of an instruction to determine the effective address of an operand. There are several types of addressing modes described, including implied, immediate, register, register indirect, auto-increment/decrement, direct, indirect, and relative addressing modes. Examples are provided to illustrate how each addressing mode calculates the effective address.

Uploaded by

Kirubel EsayasCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

382 views18 pagesAddressing Modes Explained

This document discusses different addressing modes used in computer architecture. It defines addressing modes as rules for interpreting the address field of an instruction to determine the effective address of an operand. There are several types of addressing modes described, including implied, immediate, register, register indirect, auto-increment/decrement, direct, indirect, and relative addressing modes. Examples are provided to illustrate how each addressing mode calculates the effective address.

Uploaded by

Kirubel EsayasCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 18