Professional Documents

Culture Documents

Question Paper Code:: (10×2 20 Marks)

Uploaded by

Samraj JebasinghOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Question Paper Code:: (10×2 20 Marks)

Uploaded by

Samraj JebasinghCopyright:

Available Formats

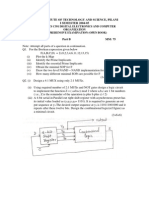

*X20389*

Reg. No. :

Question Paper Code : X 20389

B.E./B.Tech. Degree Examinations, NOVEMBER/DECEMBER 2020

Second Semester

Computer Science and Engineering

cs 6201 – digital principles and system design

(Common to Information Technology)

(Regulations 2013)

(Common to PTCS 6201 – Digital Principles and System Design for B.E.

(Part-Time) – Computer Science and Engineering – First Semester (Regulations 2014))

Time : Three Hours Maximum : 100 Marks

Answer all questions

Part – A (10×2=20 Marks)

1. Convert (126)10 to octal number and binary number.

2. Write short notes on weighted binary codes.

3. Implement a full adder with 4 × 1 Multiplexer.

4. Write the Data flow description of a 4-bit Comparator.

5. State the excitation table of JK-Flip Flop.

6. A seven bit Hamming code is received as 1111110. What is the correct code ?

7. When do race conditions occur ?

8. Define merger graph.

9. List the major differences between PLA and PAL.

10. What is memory decoding ?

Part – B (5×16=80 Marks)

11. a) Simplify the following Boolean expression in

i) Sum-of-product

ii) Product-of-sum using Karnaugh map

AC′ + B′D + A′CD + ABCD (16)

(OR)

X 20389 *X20389*

b) i) Express the following function in sum of min-terms and product of

max-terms :

F(x, y, z) = x + yz. (8)

ii) Convert the following logic system into NAND gates only. (8)

12. a) Design a full adder with inputs x, y, z and two outputs S and C. The circuits

performs x + y + z, z is the input carry, C is the output carry and S is the

sum. (16)

(OR)

b) Design a logic circuit that accepts a 4-bit Grey Code and convert it into 4-bit

binary code. (16)

13. a) Design a sequence detector that detects a sequence of three or more consecutive

1’s in a string of bits coming through an input line and produces an output

whenever this sequence is detected. (16)

(OR)

b) Design a three bit synchronous counter with T flip flop and draw the

diagram. (16)

14. a) Explain the analysis and design procedures of synchronous sequential

circuits. (16)

(OR)

b) With necessary example and diagram, explain the concept of reduction of

state and flow tables. (16)

15. a) Design a 16 bit RAM array (4 × 4 RAM) and explain the operation. (16)

(OR)

b) Explain the following :

i) ASIC (8)

ii) Field Programmable Gate Array. (8)

–––––––––––––

You might also like

- NCR AtmDocument54 pagesNCR Atmchanito0007No ratings yet

- Field Control Processor 270 (FCP270) User's Guide: I/A Series SystemDocument120 pagesField Control Processor 270 (FCP270) User's Guide: I/A Series SystemAnonymous u0wETydFNo ratings yet

- Assessment Method-Based Instructions and Guidelines: Skills TestDocument22 pagesAssessment Method-Based Instructions and Guidelines: Skills TestKEVINNo ratings yet

- RTL9210-VB-CG Demo V203 PDFDocument5 pagesRTL9210-VB-CG Demo V203 PDFCenusa MihaiNo ratings yet

- Ecac Cep Edscb Web Update 19 October 2018Document15 pagesEcac Cep Edscb Web Update 19 October 2018aionica100% (1)

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- Question Paper Code:: (10 2 20 Marks)Document2 pagesQuestion Paper Code:: (10 2 20 Marks)AbdulAzizNo ratings yet

- 2018 Winter Question Paper (Msbte Study Resources)Document4 pages2018 Winter Question Paper (Msbte Study Resources)Parth patkarNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Monica NareshNo ratings yet

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- Cs PaperDocument37 pagesCs PaperAshish BokilNo ratings yet

- 2EC6302-Digital Electronics QBDocument12 pages2EC6302-Digital Electronics QBSurendar PNo ratings yet

- Sathyabama University: Semester: IV Max - Marks: 80Document5 pagesSathyabama University: Semester: IV Max - Marks: 80GAURAVKINHANo ratings yet

- 08ab303 - Digital Logic CircuitsDocument3 pages08ab303 - Digital Logic CircuitsChandru RamaswamyNo ratings yet

- 22323-2019-Winter-Question-Paper (Msbte Study Resources)Document3 pages22323-2019-Winter-Question-Paper (Msbte Study Resources)Parth patkarNo ratings yet

- Third Homework AssignmentDocument4 pagesThird Homework AssignmentTara Shankar ChakrabortyNo ratings yet

- Important 16 Mark Questions-19!1!2024Document5 pagesImportant 16 Mark Questions-19!1!2024FLOWERNo ratings yet

- DLCDocument4 pagesDLCramNo ratings yet

- 08af302 - Digital Integrated Circuits and Logic DesignDocument4 pages08af302 - Digital Integrated Circuits and Logic DesignChandru RamaswamyNo ratings yet

- EC6302-Digital ElectronicsDocument14 pagesEC6302-Digital Electronicsmagy1989No ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- TED (15) 3133 qp-1Document2 pagesTED (15) 3133 qp-1Anna JoseNo ratings yet

- DellDocument6 pagesDellamu_manuNo ratings yet

- 9a04306-Digital Logic DesignDocument1 page9a04306-Digital Logic DesignSheikh Noor MohammadNo ratings yet

- 9A04306 Digital Logic DesignDocument2 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- Computer Science GATE Que Paper 1992Document9 pagesComputer Science GATE Que Paper 1992Pranjal GoreNo ratings yet

- Question Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodeDocument2 pagesQuestion Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodePrabu KumarNo ratings yet

- Seat No.: InstructionsDocument4 pagesSeat No.: InstructionsYogesh KuteNo ratings yet

- Ec2203 Digital Electronics r8Document3 pagesEc2203 Digital Electronics r8jenifar777No ratings yet

- EE3302-DLC MODEL QP UpdatedDocument3 pagesEE3302-DLC MODEL QP UpdatedKeerthana SahadevanNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- Nov - Dec 2018Document5 pagesNov - Dec 2018Pandyselvi BalasubramanianNo ratings yet

- Subject Code/ Title: Ee6301 Digital Logic Circuits Year/ Sem/Branch: Ii/ Iii/ EeeDocument16 pagesSubject Code/ Title: Ee6301 Digital Logic Circuits Year/ Sem/Branch: Ii/ Iii/ EeePavithra ManiNo ratings yet

- 08ab303 Digital Logic Circuits - 1Document3 pages08ab303 Digital Logic Circuits - 1Chandru RamaswamyNo ratings yet

- DLDM Question BankDocument8 pagesDLDM Question BankMayur PatilNo ratings yet

- 07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrDocument8 pages07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrObula ReddyNo ratings yet

- Digital Logic CircuitsDocument20 pagesDigital Logic CircuitsrameshsophidarlaNo ratings yet

- Question Paper Code:: Reg. No.Document3 pagesQuestion Paper Code:: Reg. No.Saravanan SadhasivamNo ratings yet

- Network Basics CollectionDocument11 pagesNetwork Basics Collectionrocks66aryanNo ratings yet

- Isro Question Paper 2008Document16 pagesIsro Question Paper 2008singaramani3870No ratings yet

- MCA (Revised) Term-End Examination - Une, 2409Document4 pagesMCA (Revised) Term-End Examination - Une, 2409ammanNo ratings yet

- 15A04306 Digital Logic Design4Document2 pages15A04306 Digital Logic Design4Lakshmi PrashanthNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- Digital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Document4 pagesDigital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNo ratings yet

- Question Bank FDEDocument2 pagesQuestion Bank FDEroyal brotherNo ratings yet

- Ec1312 QBDocument7 pagesEc1312 QBGopinathan MuthusamyNo ratings yet

- Cs2202 ANNA UNIV Question Paper 2Document3 pagesCs2202 ANNA UNIV Question Paper 2kunarajNo ratings yet

- Ec6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesDocument12 pagesEc6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesSurendar PNo ratings yet

- Dica Question BankDocument4 pagesDica Question BankOmprakash KuswahaNo ratings yet

- Digital Logic CircuitsDocument15 pagesDigital Logic CircuitsskblkoNo ratings yet

- 2019 Summer Question Paper (Msbte Study Resources)Document3 pages2019 Summer Question Paper (Msbte Study Resources)Ashutosh PatilNo ratings yet

- FAQs - CS1202 Digital Principles and System DesignDocument13 pagesFAQs - CS1202 Digital Principles and System DesignsridharanchandranNo ratings yet

- March 2008 Paper 2Document2 pagesMarch 2008 Paper 2many1tothe11No ratings yet

- Rr210203 Switching Theory and Logic DesignDocument9 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao GNo ratings yet

- Bebop to the Boolean Boogie: An Unconventional Guide to ElectronicsFrom EverandBebop to the Boolean Boogie: An Unconventional Guide to ElectronicsRating: 4 out of 5 stars4/5 (3)

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesFrom EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNo ratings yet

- PC Engine / TurboGrafx-16 Architecture: Architecture of Consoles: A Practical Analysis, #16From EverandPC Engine / TurboGrafx-16 Architecture: Architecture of Consoles: A Practical Analysis, #16No ratings yet

- SNES Architecture: Architecture of Consoles: A Practical Analysis, #4From EverandSNES Architecture: Architecture of Consoles: A Practical Analysis, #4No ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Combinatorial Algorithms: For Computers and CalculatorsFrom EverandCombinatorial Algorithms: For Computers and CalculatorsRating: 4 out of 5 stars4/5 (2)

- Course File: Name of The Faculty: Mr. MOUSAM CHATTERJEEDocument25 pagesCourse File: Name of The Faculty: Mr. MOUSAM CHATTERJEESamraj JebasinghNo ratings yet

- Program 1Document2 pagesProgram 1Samraj JebasinghNo ratings yet

- QP. CodeDocument3 pagesQP. CodeRaja SekarNo ratings yet

- QP. CodeDocument2 pagesQP. CodeSamraj JebasinghNo ratings yet

- QP. CodeDocument3 pagesQP. CodeSamraj JebasinghNo ratings yet

- Syllabus SamDocument7 pagesSyllabus SamSamraj JebasinghNo ratings yet

- Sri Vidya College of Engineering & Technology Ec-I - NotesDocument48 pagesSri Vidya College of Engineering & Technology Ec-I - NotesSamraj JebasinghNo ratings yet

- Program 1Document2 pagesProgram 1Samraj JebasinghNo ratings yet

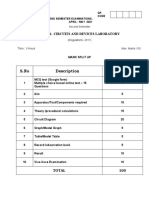

- S.No Description Marks Allotted: Ec 8261-Circuits and Devices LaboratoryDocument5 pagesS.No Description Marks Allotted: Ec 8261-Circuits and Devices LaboratorySamraj JebasinghNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)Samraj JebasinghNo ratings yet

- QP. CodeDocument3 pagesQP. CodeSamraj JebasinghNo ratings yet

- X10556 (Ge8076)Document2 pagesX10556 (Ge8076)Samraj JebasinghNo ratings yet

- Ec 8261 - Circuits and Devices Laboratory: Second SemesterDocument5 pagesEc 8261 - Circuits and Devices Laboratory: Second SemesterSamraj JebasinghNo ratings yet

- Question Paper Code: X10375: Reg. NoDocument2 pagesQuestion Paper Code: X10375: Reg. NoSamraj JebasinghNo ratings yet

- Question Paper Code:: Reg. No.Document3 pagesQuestion Paper Code:: Reg. No.Samraj JebasinghNo ratings yet

- Question Paper Code: X10326: Computer Science and EngineeringDocument2 pagesQuestion Paper Code: X10326: Computer Science and EngineeringSamraj JebasinghNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)Samraj JebasinghNo ratings yet

- Question Paper Code:: Reg. No.Document3 pagesQuestion Paper Code:: Reg. No.Samraj JebasinghNo ratings yet

- GoTN - List of Polytechnic CollegesDocument12 pagesGoTN - List of Polytechnic CollegesSamraj Jebasingh0% (1)

- Question Paper Code:: Reg. No.Document5 pagesQuestion Paper Code:: Reg. No.Samraj JebasinghNo ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Samraj JebasinghNo ratings yet

- Question Paper Code:: (10 2 20 Marks)Document5 pagesQuestion Paper Code:: (10 2 20 Marks)Samraj JebasinghNo ratings yet

- FDP Program Test On Micro Electro Mechanical SystemDocument12 pagesFDP Program Test On Micro Electro Mechanical SystemSamraj JebasinghNo ratings yet

- Anna Univ Part Time Mech SylabusDocument69 pagesAnna Univ Part Time Mech SylabusmayilsamythangarajuNo ratings yet

- 10 1 1 35Document4 pages10 1 1 35Samraj JebasinghNo ratings yet

- NewDocument1 pageNewSamraj JebasinghNo ratings yet

- CN Lab Manual PDFDocument62 pagesCN Lab Manual PDFsandhiya .vNo ratings yet

- CN Lab Manual PDFDocument62 pagesCN Lab Manual PDFsandhiya .vNo ratings yet

- A Study of Various Image Compression TechniquesDocument5 pagesA Study of Various Image Compression TechniquesjadolyoNo ratings yet

- Lenovo Legion 5 Pro 16ACH6H SpecDocument7 pagesLenovo Legion 5 Pro 16ACH6H SpecJorge LaraNo ratings yet

- Windows Administrator L1 Interview Question - System AdministratorDocument8 pagesWindows Administrator L1 Interview Question - System AdministratorkalimireddyNo ratings yet

- Magnetic Encoding Format1Document2 pagesMagnetic Encoding Format1ravipati46No ratings yet

- Why Switched FICON? (Switched FICON vs. Direct-Attached FICON)Document12 pagesWhy Switched FICON? (Switched FICON vs. Direct-Attached FICON)chapterNo ratings yet

- Understanding Operating Systems Seventh EditionDocument70 pagesUnderstanding Operating Systems Seventh EditionJp TibayNo ratings yet

- Chapter 2 - Introduction Big DataDocument36 pagesChapter 2 - Introduction Big DataMuhammad rizky fauzi nurrohmanNo ratings yet

- Cisco Packet Tracer Mobile Android 2 - 0 Release NotesDocument4 pagesCisco Packet Tracer Mobile Android 2 - 0 Release NotesVicente Morocho MallaNo ratings yet

- Lenovo A6000 Plus Secret CodesDocument3 pagesLenovo A6000 Plus Secret CodesyatishjainkotaNo ratings yet

- Windows Power Shell Workflow - WMF3 CTP2Document14 pagesWindows Power Shell Workflow - WMF3 CTP2ChiTownITNo ratings yet

- IOT Based Agriculture Monitoring SystemDocument16 pagesIOT Based Agriculture Monitoring SystemMuhammad UmairNo ratings yet

- Hanacleaner - Sap Note 2399996: Sap Note Presents A Tool That Can Help With Housekeeping TasksDocument38 pagesHanacleaner - Sap Note 2399996: Sap Note Presents A Tool That Can Help With Housekeeping TasksmbadashrafNo ratings yet

- Papercut MF - Dell MFP Embedded ManualDocument43 pagesPapercut MF - Dell MFP Embedded Manualsaid waelNo ratings yet

- MN Hmwin User Peweu enDocument530 pagesMN Hmwin User Peweu enMarius PredaNo ratings yet

- Phoenix v2 Ds GB Rev0Document2 pagesPhoenix v2 Ds GB Rev0wesleysenna25No ratings yet

- Multiping ReadmeDocument2 pagesMultiping ReadmemuhizimudinNo ratings yet

- Model 793.00 System SoftwareDocument750 pagesModel 793.00 System SoftwareMichel Zarzosa RojasNo ratings yet

- Wireshark Display FiltersDocument315 pagesWireshark Display FiltersKaushal KishorNo ratings yet

- Huawei Mar-Lx1a 10.0.0.150 (C431e8r2p7) Dual Eea Release NotesDocument10 pagesHuawei Mar-Lx1a 10.0.0.150 (C431e8r2p7) Dual Eea Release NotesjuanqwNo ratings yet

- Gujarat Technological UniversityDocument3 pagesGujarat Technological UniversitypatelNo ratings yet

- D945GTP TechProdSpecDocument92 pagesD945GTP TechProdSpecDOMINGOSERPA4148No ratings yet

- New Microsoft Word DocumentDocument20 pagesNew Microsoft Word Documentfsdfnsfbsd99-0No ratings yet

- Cloudera User ManualDocument44 pagesCloudera User ManualcharpentierNo ratings yet

- Changing OverclockingDocument7 pagesChanging Overclockingmario_gNo ratings yet

- Pa 10 Display HR Personnel FileDocument5 pagesPa 10 Display HR Personnel FileBrian GriffithNo ratings yet

- Os Finals Thankyou SirDocument4 pagesOs Finals Thankyou SirChed Lorenz ToledoNo ratings yet