Professional Documents

Culture Documents

VLSI Design Module 1 Introduction

Uploaded by

Valmik GholapOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VLSI Design Module 1 Introduction

Uploaded by

Valmik GholapCopyright:

Available Formats

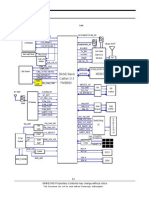

Module 1 : Introduction to VLSI Design

Lecture 1 : Motivation of the Course

Objectives

In this lecture you will learn the following:

• Motivation of the course

• Course Objectives

1.1 Motivation of the course

Why do some circuits work the first time and some circuits take over a year and multiple

design iterations to work properly? Why can, for some circuits, the produced quantities

easily be ramped up, and for others both circuit and process optimisation is needed.

Why are some circuits running red-hot requiring expensive cooling solutions while other

circuits, for similar performance, are running from small batteries in hand held gadgets?

Why do some companies make money with successful innovations and why do some

companies loose hundreds of millions of dollars of revenue just because they did not get

their product on market in time.

The answer to these questions is (a lack of) system engineering: analysis and design of

a system's relevant electrical parameters. The deep submicron CMOS technologies have

moved the bottleneck from device and gate level issues to interconnects and

communication (metal wires) bottle necks, where we currently do not have any design

automation. This course aims to provide a working knowledge of system electrical issues

at chip level related to remove or live with these new bottle-necks (so that the disasters

in design can be avoided with proper structures and performance budgeting).

1.2 Course Objectives

The course provides for final year undergraduates a solid and fundamental engineering

view of digital system operation and how to design systematically well performing digital

VLSI systems exceeding consistently, customer expectations and competitor fears. The

aim is to teach the critical methods and circuit structures to identify the key 1 % of the

circuitry on-chip which dominates the performance, reliability, manufacturability, and

the cost of the VLSI circuit. With the current utilisation of the deep submicron CMOS

technologies (0.25 micron and below design rules) the major design paradigm shift is

associated with the fact that the interconnections (metal Al or Cu wires connecting

gates) and the chip communication in general is the main design object instead of active

transistors or logic gates. The main design issues defining the make-or-break point in

each project is associated with power and signal distribution and bit/symbol

communication between functional blocks on-chip and off-chip. In the course we

provide a solid framework in understanding:

- Scaling of technology and their impact on interconnects

- Interconnects as design objects

- Noise in digital systems and its impact on system operation

- Power distribution schemes for low noise

- Signal and signalling conventions for on-chip and off-chip communication

- Timing and synchronisation for fundamental operations and signaling

The course objective is to provide the student with a solid understanding of the

underlying mechanism and solution techniques to the above key design issues, so that

the student, when working as industrial designer, is capable of identifying the key

problem points and focus his creative attention and 90% of available resources to right

issues for 1% of the circuitry and leave the remaining 99% of circuitry to computer

automated tools or unqualified engineers.

Recap

In this course you have learnt the following

• Motivation of the course

• Course Objectives

You might also like

- Lec 1 PDFDocument2 pagesLec 1 PDFSurendra GangarapuNo ratings yet

- VLSI Lec-1 PDFDocument2 pagesVLSI Lec-1 PDFSurendra GangarapuNo ratings yet

- Lec 1Document2 pagesLec 1Valmik GholapNo ratings yet

- Module 1: Introduction To VLSI Design Lecture 1: Motivation of The CourseDocument2 pagesModule 1: Introduction To VLSI Design Lecture 1: Motivation of The CourseGunjan JhaNo ratings yet

- Module 1: Introduction To VLSI Design Lecture 1: Motivation of The CourseDocument2 pagesModule 1: Introduction To VLSI Design Lecture 1: Motivation of The CourseVinay GargNo ratings yet

- Analog VLSI Design: Technology TrendsDocument31 pagesAnalog VLSI Design: Technology TrendsSathyaNarasimmanTiagarajNo ratings yet

- Analog VLSI Design: Technology TrendsDocument25 pagesAnalog VLSI Design: Technology TrendsSathyaNarasimmanTiagarajNo ratings yet

- 1 TO Vlsi: Vlsi Design by DR SP SinghDocument8 pages1 TO Vlsi: Vlsi Design by DR SP Singhendryas zewduNo ratings yet

- NIT 1 4 7040 Lecture 1 VLSI EC601Document26 pagesNIT 1 4 7040 Lecture 1 VLSI EC601SANDIP PODDARNo ratings yet

- Design CMOS Logic Gate LayoutDocument4 pagesDesign CMOS Logic Gate LayoutHieu Nguyen TriNo ratings yet

- Sri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsDocument122 pagesSri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsRAAJ KISHOR R HNo ratings yet

- Circuit Design and Component Choice for EMC ComplianceDocument156 pagesCircuit Design and Component Choice for EMC Compliancec_rodolfo_rodrigues5109No ratings yet

- Introduction To VLSI SystemDocument16 pagesIntroduction To VLSI SystemPrabakaran RajendranNo ratings yet

- VLSI ModulesDocument28 pagesVLSI Modulessai_karthik89No ratings yet

- UIT's Advanced Digital Electronics CourseDocument3 pagesUIT's Advanced Digital Electronics CourseSoftware EngineerNo ratings yet

- Signal Integrity CourseDocument6 pagesSignal Integrity CourseMohit JoshiNo ratings yet

- PHD Thesis On Vlsi DesignDocument5 pagesPHD Thesis On Vlsi DesignBuyEssaysTulsa100% (2)

- Analog Design Issues in Digital VLSI Circuits and Systems: S.S.JangamDocument3 pagesAnalog Design Issues in Digital VLSI Circuits and Systems: S.S.JangamMandar MuleNo ratings yet

- Verification of Complex Analog ICsDocument35 pagesVerification of Complex Analog ICsateeqsocNo ratings yet

- Design and AnalysisDocument4 pagesDesign and Analysisbonat07No ratings yet

- Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015Document2 pagesEce5015 Digital-Ic-Design Eth 1.0 40 Ece5015Sivanantham SadhasivamNo ratings yet

- Future University Faculty of Post Graduate StudiesDocument4 pagesFuture University Faculty of Post Graduate StudiesKhagw MohamedNo ratings yet

- Alberto Scandurra Auth., Ian OConnor, Gabriela Nicolescu Eds. Integrated Optical Interconnect Architectures For Embedded Systems1Document276 pagesAlberto Scandurra Auth., Ian OConnor, Gabriela Nicolescu Eds. Integrated Optical Interconnect Architectures For Embedded Systems1Anurag KumarNo ratings yet

- System On Chip PresentationDocument70 pagesSystem On Chip Presentationshree_rs81No ratings yet

- A Survey On SoCDocument51 pagesA Survey On SoCLEE KAH YI -No ratings yet

- Some Recent Developments in RF and Microwave Circuit IntegrationDocument2 pagesSome Recent Developments in RF and Microwave Circuit Integrationarunkr1No ratings yet

- Vlsi Design - Ec - 701 - Unit - IDocument37 pagesVlsi Design - Ec - 701 - Unit - Iangelcrystl4774No ratings yet

- UTM Course SynopsesDocument14 pagesUTM Course SynopsesSaravanan KerishnanNo ratings yet

- Program Name Semester Course Code Course Name Lecture / Tutorial (Per Week) Lect. No. Course Coordinator NameDocument33 pagesProgram Name Semester Course Code Course Name Lecture / Tutorial (Per Week) Lect. No. Course Coordinator Nameishan goyalNo ratings yet

- VLSI Design Lab NewDocument45 pagesVLSI Design Lab NewmtariqanwarNo ratings yet

- Chapter 1 - Analog Integrated Circuit Design by John ChomaDocument87 pagesChapter 1 - Analog Integrated Circuit Design by John ChomaAriana Ribeiro LameirinhasNo ratings yet

- Research Papers On Cmos TechnologyDocument7 pagesResearch Papers On Cmos Technologyxmniibvkg100% (1)

- VLSI Design 4 Course InfoDocument4 pagesVLSI Design 4 Course InfoSwati HayaranNo ratings yet

- Design and Implementation of VLSI SystemsDocument41 pagesDesign and Implementation of VLSI SystemsCuong HuynhNo ratings yet

- Networks On Chip (NOC) : Design ChallengesDocument8 pagesNetworks On Chip (NOC) : Design ChallengesMohammad Seemab AslamNo ratings yet

- VLSI Design: An Introduction to IC TechnologyDocument59 pagesVLSI Design: An Introduction to IC TechnologyDr. Pullareddy AvulaNo ratings yet

- New Design Methodologies For High-Speed Mixed-Mode Cmos Full Adder CircuitsDocument21 pagesNew Design Methodologies For High-Speed Mixed-Mode Cmos Full Adder CircuitsAnonymous e4UpOQEPNo ratings yet

- Introduction To The Design of Analogs by Allen and HollbergDocument14 pagesIntroduction To The Design of Analogs by Allen and HollbergKiran KirruNo ratings yet

- VLSI Design Lab NewDocument48 pagesVLSI Design Lab NewJubin JainNo ratings yet

- VLSI DesignDocument55 pagesVLSI DesignClique for Applied Research in Electronic TechnologyNo ratings yet

- Report On Mpsoc'04: Students' Summary of Lectures Xi ChenDocument45 pagesReport On Mpsoc'04: Students' Summary of Lectures Xi ChenRachana SrinivasNo ratings yet

- VLSI IntroductionDocument23 pagesVLSI IntroductionSreenivasulu MamillaNo ratings yet

- PHD Thesis in Telecommunications EngineeringDocument5 pagesPHD Thesis in Telecommunications Engineeringlauriegunlickssiouxfalls100% (2)

- Purihin, Dann Kervin M. - 03lab1Document2 pagesPurihin, Dann Kervin M. - 03lab1XDONENo ratings yet

- Embedded System Design and IC Technology Course DetailsDocument24 pagesEmbedded System Design and IC Technology Course DetailsHannan SatopayNo ratings yet

- RF Circuit Design WorkshopDocument2 pagesRF Circuit Design WorkshopRAJAMOHANNo ratings yet

- Systems On Chip: Evolutionary and Revolutionary TrendsDocument8 pagesSystems On Chip: Evolutionary and Revolutionary TrendsatsoumNo ratings yet

- Thesis On Vlsi DesignDocument7 pagesThesis On Vlsi Designbrendatorresalbuquerque100% (2)

- Low-Power Variation-Tolerant Design in Nanometer Silicon (Bhunia) (2010)Document456 pagesLow-Power Variation-Tolerant Design in Nanometer Silicon (Bhunia) (2010)Jon HimesNo ratings yet

- Floating Point MultiplierDocument35 pagesFloating Point Multiplierbindu_ankuNo ratings yet

- Signal Integrity Introduction Class 1: Reduction To Practice For High Speed Digital Design Reading Assignment: CH8 To 9.3Document21 pagesSignal Integrity Introduction Class 1: Reduction To Practice For High Speed Digital Design Reading Assignment: CH8 To 9.3MandrakeNo ratings yet

- SoC SyllabusDocument2 pagesSoC SyllabuslokeshNo ratings yet

- Me Gtu CurriculumDocument47 pagesMe Gtu CurriculumAnupam DevaniNo ratings yet

- VLSI DesignDocument181 pagesVLSI Designprabhug22No ratings yet

- EMC Techniques in Electronic Design Part 2 - Cables and ConnectorsDocument40 pagesEMC Techniques in Electronic Design Part 2 - Cables and Connectorsjax almarNo ratings yet

- Design Techniques For EMC & Signal Integrity - Part 5 PCB Design and LayoutDocument24 pagesDesign Techniques For EMC & Signal Integrity - Part 5 PCB Design and Layoutsanjeevss_200-No ratings yet

- System On ChipDocument12 pagesSystem On Chipimcoolsha999No ratings yet

- Design and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesFrom EverandDesign and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesNo ratings yet

- VLSI Assignment 1 AnswersDocument1 pageVLSI Assignment 1 AnswersValmik GholapNo ratings yet

- VLSI Assignment 1 QuestionsDocument2 pagesVLSI Assignment 1 QuestionsManikanta Reddy ManuNo ratings yet

- Digital System Design with PLDs and FPGAs Using VHDLDocument94 pagesDigital System Design with PLDs and FPGAs Using VHDLVishnu Vardhan ReddyNo ratings yet

- Solution Assignment 2Document1 pageSolution Assignment 2Valmik GholapNo ratings yet

- Solution Assignment 2Document1 pageSolution Assignment 2Valmik GholapNo ratings yet

- VLSI Assignment 1 AnswersDocument1 pageVLSI Assignment 1 AnswersValmik GholapNo ratings yet

- Module 2: MOSFET Lecture 3: Introduction To MOSFET: ObjectivesDocument3 pagesModule 2: MOSFET Lecture 3: Introduction To MOSFET: ObjectivesVivek AggarwalNo ratings yet

- Module 1: Introduction To VLSI Design Lecture 2: System Approach To VLSI DesignDocument3 pagesModule 1: Introduction To VLSI Design Lecture 2: System Approach To VLSI DesignValmik GholapNo ratings yet

- Module 2: MOSFET Lecture 4: MOS Capacitor: ObjectivesDocument4 pagesModule 2: MOSFET Lecture 4: MOS Capacitor: ObjectivesAruna ManiNo ratings yet

- Module 1: Introduction To VLSI Design Lecture 2: System Approach To VLSI DesignDocument3 pagesModule 1: Introduction To VLSI Design Lecture 2: System Approach To VLSI DesignValmik GholapNo ratings yet

- Module 2: MOSFET Lecture 3: Introduction To MOSFET: ObjectivesDocument3 pagesModule 2: MOSFET Lecture 3: Introduction To MOSFET: ObjectivesVivek AggarwalNo ratings yet

- Syllabus 5 - Module 7 - Using The Internet & EmailDocument5 pagesSyllabus 5 - Module 7 - Using The Internet & EmailBalachandran NavaratnasamyNo ratings yet

- Tyco Biffi Icon 2000 PDFDocument30 pagesTyco Biffi Icon 2000 PDFDarius GarbuNo ratings yet

- L78M00 Series: Positive Voltage RegulatorsDocument19 pagesL78M00 Series: Positive Voltage RegulatorsHenderson TshikwataNo ratings yet

- Quotation TemplateDocument7 pagesQuotation TemplateDaksh AsijaNo ratings yet

- Rx3852-3408-31 - Rfi RX Multicoupler Uhf 380-520mhzDocument2 pagesRx3852-3408-31 - Rfi RX Multicoupler Uhf 380-520mhzBao Quoc MaiNo ratings yet

- Evaluasi Desain WebsiteDocument14 pagesEvaluasi Desain WebsiteAgung NurhidayatNo ratings yet

- OperManual SB ST310U Rev112 09 12 2017 PDFDocument67 pagesOperManual SB ST310U Rev112 09 12 2017 PDFrichardNo ratings yet

- User Manual 2570817 RRU ZTEDocument24 pagesUser Manual 2570817 RRU ZTEGun TaNo ratings yet

- Chap1 3 Improving Warehouse Activityy in Cdo Foodsphere IncDocument47 pagesChap1 3 Improving Warehouse Activityy in Cdo Foodsphere IncPol Vince Bernard Salisi100% (1)

- Getting Started With PSCAD X4 (v4.6.3)Document16 pagesGetting Started With PSCAD X4 (v4.6.3)JHJH HNo ratings yet

- KTB-BD-003-F01 Customer Complaint Register 2013Document15 pagesKTB-BD-003-F01 Customer Complaint Register 2013info.glconsultinqNo ratings yet

- User Manual ADM PDFDocument464 pagesUser Manual ADM PDFLuis100% (1)

- Level 3 Troubleshooting GuideDocument44 pagesLevel 3 Troubleshooting GuideFabiomarferreira100% (1)

- Experienced Supply Chain AnalystDocument3 pagesExperienced Supply Chain Analystchandu rajuNo ratings yet

- A320m A Pro MaxDocument1 pageA320m A Pro MaxVonda ApriliantoNo ratings yet

- Citroen Xsara I - Wiring DiagramDocument20 pagesCitroen Xsara I - Wiring DiagramDavid VasNo ratings yet

- Pmguru OnlineDocument167 pagesPmguru OnlineGaurav KhamkarNo ratings yet

- 3 - 2 COMET Overview BrochureDocument6 pages3 - 2 COMET Overview BrochureDaniel Azuarte MendozaNo ratings yet

- Axis Statement Kirandeep KaurDocument2 pagesAxis Statement Kirandeep KaurTanvi DhingraNo ratings yet

- Caterpillar 988 Wheel Loader Operators Manual SN 87aDocument6 pagesCaterpillar 988 Wheel Loader Operators Manual SN 87aCarlos Cetina100% (1)

- The VLSI Ruby II Advanced Communication ProcessorDocument1 pageThe VLSI Ruby II Advanced Communication ProcessorvlkumashankardeekshithNo ratings yet

- Four-Stroke Diesel Engine ExperimentsDocument2 pagesFour-Stroke Diesel Engine ExperimentsPatricio Alarcon CastroNo ratings yet

- CS251 - Spring 2008 Barrel ShiftersDocument2 pagesCS251 - Spring 2008 Barrel Shiftersaarthi100No ratings yet

- Seat Belt UsageDocument2 pagesSeat Belt UsageAnkitRavalNo ratings yet

- Empowerment Technology Quarter 1 Week 2Document12 pagesEmpowerment Technology Quarter 1 Week 2BananaNo ratings yet

- Intel® Compute Stick Stk1Aw32Sc STK1A32SC: Technical Product SpecificationDocument27 pagesIntel® Compute Stick Stk1Aw32Sc STK1A32SC: Technical Product SpecificationjohnyredblueNo ratings yet

- Audio Catalogue: We Supply SoundDocument64 pagesAudio Catalogue: We Supply SoundAlvin Novandi Ega PradanaNo ratings yet

- An 01 en Opticum Xs65 HD Sat ReceiverDocument49 pagesAn 01 en Opticum Xs65 HD Sat ReceiverRoxana BirtumNo ratings yet

- Isca For ExamDocument60 pagesIsca For ExamBharathNo ratings yet

- Chart of Hindi TypingDocument4 pagesChart of Hindi TypingPranav TripathiNo ratings yet