Professional Documents

Culture Documents

Ate Lab5

Ate Lab5

Uploaded by

yashkaran singhOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ate Lab5

Ate Lab5

Uploaded by

yashkaran singhCopyright:

Available Formats

EXP: 06 DATE: 21/09/21

EXPERIMENT 6

AIM

To test by Boundary Scan testing method using QT 2251..

APPARATUS REQUIRED

1. QT-2251 Testing Equipment

2. JTAG interface

3. PCB with the SMTs under test

4. Power cable for QT-2251

5. Interactive Software and a PC

DESCRIPTION

• Using QT2251, one can perform all types of testing such as; OCFT, ICFT, QSMVI and

boundary scan.

• Boundary scan is used when the PCB is complex and on cannot test all the ICs separately.

Hence all the interconnects are tested. It is checked if the signals are passed properly or not.

• Unlike OCFT, ICFT, and QSMVI which uses Dual-in-Package (DIP) ICs which have limited

number of pins, and can be tested using a clip by making a contact; in boundary scan where

surface mount technology-based ICs such as processors are used, the number of pins increase

and performs complex function.

• The ICs can have a range up to 100 pins and manufactured uniquely. So, in this case boundary

scan is used because taking signal from each and every pin is not possible.

• In such cases, SMTs (maximum 5-6) that are placed on a PCB are configured on boundary scan

kits.

• The boundary scan kit has Vcc, gnd, TDI, TDO, TCK, TMS and TRST. Using these boundary

scan pins; the data is fetched from the SMTs while testing.

• The issues with interconnects can be identified. Moreover, the number of nets can be identified.

• Not necessary to test each SMT separately but interconnects can be tested for proper working.

• First Board (Demo board):

SMTs --> BSD1 & BSD2 --> PASS

• Second Board (FPGA):

Spartan 3E kit

XE3S500E (family name)

FG-320 (package) --> fauty board --> to identify shorts or

open circuits and identify the number of nets.

OUTPUT

--> Demo board

18BEI0149 1 HARSHITA PURI

EXP: 06 DATE: 21/09/21

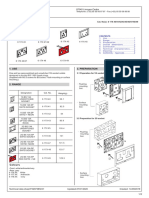

1. QT 2251

2. JTAG interface

18BEI0149 2 HARSHITA PURI

EXP: 06 DATE: 21/09/21

3. PCB under test

4. Interactive software

18BEI0149 3 HARSHITA PURI

EXP: 06 DATE: 21/09/21

5. Opening boundary scan test

6. Detecting boundary scan test

18BEI0149 4 HARSHITA PURI

EXP: 06 DATE: 21/09/21

7. Selecting corresponding device name

8. Learning characteristics

18BEI0149 5 HARSHITA PURI

EXP: 06 DATE: 21/09/21

9. Contact check

18BEI0149 6 HARSHITA PURI

EXP: 06 DATE: 21/09/21

10. Condition: pass/fail

18BEI0149 7 HARSHITA PURI

EXP: 06 DATE: 21/09/21

11. Nets stuck at one

--> FPGA board

18BEI0149 8 HARSHITA PURI

EXP: 06 DATE: 21/09/21

1. Spartan 3E kit

2. JTAG

18BEI0149 9 HARSHITA PURI

EXP: 06 DATE: 21/09/21

3. Detect scan path

18BEI0149 10 HARSHITA PURI

EXP: 06 DATE: 21/09/21

4. Number of nets

18BEI0149 11 HARSHITA PURI

EXP: 06 DATE: 21/09/21

5. System learnt

6. Verifying

18BEI0149 12 HARSHITA PURI

EXP: 06 DATE: 21/09/21

7. Test status

INFERENCES & RESULTS

The functionality of the unknown SMTs was verified successfully with Boundary scan technique

using QT 2251 test equipment.

18BEI0149 13 HARSHITA PURI

You might also like

- 12x8 .15" Pitch Stripboard: Input OutputDocument1 page12x8 .15" Pitch Stripboard: Input OutputRobWileyNo ratings yet

- NAVFAC BIM Project Execution PlanDocument7 pagesNAVFAC BIM Project Execution PlanKhalid Bin BreikNo ratings yet

- Project Management Lessons LearnedDocument236 pagesProject Management Lessons LearnedKamilly Protz100% (2)

- MTS-5800 Ethernet Layer 2 Traffic Testing Guide V25 - XDocument12 pagesMTS-5800 Ethernet Layer 2 Traffic Testing Guide V25 - XtheanhcbNo ratings yet

- Art & Design-Sunway University College 2011Document28 pagesArt & Design-Sunway University College 2011Sunway UniversityNo ratings yet

- Project Engineer Job DescriptionDocument7 pagesProject Engineer Job DescriptionProjectmanagement101No ratings yet

- Construction Economics B-Assignment 01Document9 pagesConstruction Economics B-Assignment 01swarnapuraNo ratings yet

- Construction Procurement Policy 160109-WebDocument12 pagesConstruction Procurement Policy 160109-WebTaha MadraswalaNo ratings yet

- Factory Acceptance Test Plan - LTE ENodeBDocument6 pagesFactory Acceptance Test Plan - LTE ENodeBLaura VillarrealNo ratings yet

- Ate Lab5Document7 pagesAte Lab5yashkaran singhNo ratings yet

- Ate Lab5Document8 pagesAte Lab5yashkaran singhNo ratings yet

- AIM Apparatus Required: Yashkaran Singh 18BEI0122Document8 pagesAIM Apparatus Required: Yashkaran Singh 18BEI0122yashkaran singhNo ratings yet

- Microcomputer Components: 8-Bit CMOS Single-Chip MicrocontrollerDocument62 pagesMicrocomputer Components: 8-Bit CMOS Single-Chip MicrocontrollerJose CNo ratings yet

- Paso A Paso Zte Gpon Solo InternetDocument29 pagesPaso A Paso Zte Gpon Solo InternetGabriel ForiguaNo ratings yet

- Summary Report of On-Board Radio ParametersDocument15 pagesSummary Report of On-Board Radio Parametersarthur asparelaNo ratings yet

- Site Acceptance Test Formats For RMU Automation: Drawing Number (4) - Page 1 of 9 Rev 0Document9 pagesSite Acceptance Test Formats For RMU Automation: Drawing Number (4) - Page 1 of 9 Rev 0Anonymous axyNzhNo ratings yet

- Gowtham Kanna M 18ec1026Document23 pagesGowtham Kanna M 18ec1026gayathriNo ratings yet

- MTS-5800 RFC 2544 Layer 3 IPv4 Testing Guide, V25 - XDocument14 pagesMTS-5800 RFC 2544 Layer 3 IPv4 Testing Guide, V25 - XtheanhcbNo ratings yet

- BPGIPV6Document18 pagesBPGIPV6Majo PortillaNo ratings yet

- Tala - Certificados Naval Star-2 2Document2 pagesTala - Certificados Naval Star-2 2Emilio Gustavo Saez DuroNo ratings yet

- Tahi TestsDocument6 pagesTahi TestsKiran PatilNo ratings yet

- LPC 2129Document44 pagesLPC 2129Pra ReddyNo ratings yet

- PCIE 2 0 System Board Test Agilent DSO81xxxxDocument39 pagesPCIE 2 0 System Board Test Agilent DSO81xxxxkaushal_patel_13No ratings yet

- Hardware Instruction Manual: Date: 21/09/2011Document45 pagesHardware Instruction Manual: Date: 21/09/2011Ting Siu HuiNo ratings yet

- NCU NetworlControlUnit DataSheetDocument17 pagesNCU NetworlControlUnit DataSheetcasapvaNo ratings yet

- UserGuide - SK FM4 216 ETHERNETDocument77 pagesUserGuide - SK FM4 216 ETHERNETSmart ClasseNo ratings yet

- Cam Nang Sua Chua T40-T43 - UploadDocument57 pagesCam Nang Sua Chua T40-T43 - Uploadandinguyen20046799No ratings yet

- Cxc-2000pvr Service ManualDocument63 pagesCxc-2000pvr Service ManualGoran StojkovicNo ratings yet

- FT Flexitest Family - Product - Guide - 1VAC394641-PG - Rev - H - 040221Document56 pagesFT Flexitest Family - Product - Guide - 1VAC394641-PG - Rev - H - 040221Walter EguizabalNo ratings yet

- Site Commission TestsDocument18 pagesSite Commission TestsAmit KumarNo ratings yet

- IOS Upgrade & Rommon RecoveryDocument23 pagesIOS Upgrade & Rommon RecoveryChanchal Kumar BiswasNo ratings yet

- SpaceWire-to-GigabitEther UesrGuide 20100930Document19 pagesSpaceWire-to-GigabitEther UesrGuide 20100930Isaac LopezNo ratings yet

- (Service Manual) SNP-6200RH Series - ENG-20160620Document143 pages(Service Manual) SNP-6200RH Series - ENG-20160620nicoibarraNo ratings yet

- Lab Manual CNDocument83 pagesLab Manual CNrenugasri100% (2)

- NLT 40 PanDocument46 pagesNLT 40 Panquangtiendt05No ratings yet

- A Briefing On IEEE 1149.1 - 1990 Standard Test Access Port and Boundary-Scan Architecture (AKA JTAG)Document12 pagesA Briefing On IEEE 1149.1 - 1990 Standard Test Access Port and Boundary-Scan Architecture (AKA JTAG)Raghul SambathkumarNo ratings yet

- Serial Peripheral InterfaceDocument24 pagesSerial Peripheral Interfacegangadharan2osho_210No ratings yet

- Paradip Final ReportDocument140 pagesParadip Final ReportArindam ChatterjeeNo ratings yet

- BOQ FormatDocument1 pageBOQ FormatAnil KumarNo ratings yet

- STM-8 InstructionsDocument34 pagesSTM-8 InstructionsAteDopicNo ratings yet

- Ngr-531 (Sirfstariii, Singlechip) Specification: Sirfstar Iii (Gsc3F) Ngr-531Document15 pagesNgr-531 (Sirfstariii, Singlechip) Specification: Sirfstar Iii (Gsc3F) Ngr-531alvarikokexNo ratings yet

- Spider 8 User ManualDocument34 pagesSpider 8 User ManualJacob MillerNo ratings yet

- Brksec 3020Document188 pagesBrksec 3020Alvaro J. SarmientoNo ratings yet

- User Manual CompactPCI BackplanesDocument26 pagesUser Manual CompactPCI BackplanesgeorgeNo ratings yet

- Arm Mini: Quick Start ManualDocument37 pagesArm Mini: Quick Start ManualFuture TechnovationNo ratings yet

- PCB Diagnostic & Functional Test System: Qmax QT-200 QT-200Document6 pagesPCB Diagnostic & Functional Test System: Qmax QT-200 QT-200Eslam SalahNo ratings yet

- 2016 Benedikt StockebrandDocument6 pages2016 Benedikt Stockebrandsalelg1980No ratings yet

- Aoc Lc32k0d3d Lc42k0d3dDocument116 pagesAoc Lc32k0d3d Lc42k0d3dmarcellobbNo ratings yet

- BB6631Document28 pagesBB6631mebratu908No ratings yet

- Revised AT ScheduleDocument6 pagesRevised AT SchedulevenkateshNo ratings yet

- Bist-Based Group Testing For Diagnosis of Embedded Fpga CoresDocument5 pagesBist-Based Group Testing For Diagnosis of Embedded Fpga Coresgssharma888No ratings yet

- DS-NG-6460-002-002 Test Form For SAS Fiber Obtic Cables Commissioning Rev01Document3 pagesDS-NG-6460-002-002 Test Form For SAS Fiber Obtic Cables Commissioning Rev01Makesh IndhuNo ratings yet

- Gps Tracker User Manual: PrefaceDocument14 pagesGps Tracker User Manual: Prefaceelyas drifNo ratings yet

- JTAG Domain ShareDocument26 pagesJTAG Domain SharevenkatNo ratings yet

- SAPL Data Center Co-Lo - RFQ - IS - Infrastructure - v1Document5 pagesSAPL Data Center Co-Lo - RFQ - IS - Infrastructure - v1Smithesh IsaacNo ratings yet

- Critical Issues Summary 05032021Document13 pagesCritical Issues Summary 05032021Joseph F ChikuseNo ratings yet

- F02973en 01Document2 pagesF02973en 01ANo ratings yet

- Daewoo SP115 Chassis DP42SM Plasma TV SM PDFDocument62 pagesDaewoo SP115 Chassis DP42SM Plasma TV SM PDFdann222No ratings yet

- Quick Installation Guide Gdc-600beDocument4 pagesQuick Installation Guide Gdc-600bexelavNo ratings yet

- Midas3.0 BMDocument139 pagesMidas3.0 BMMirosław WalasikNo ratings yet

- Historycal FlowcodeDocument4 pagesHistorycal FlowcodeJo DiNo ratings yet

- K8SCNB JanLFNDATF 2021Document17 pagesK8SCNB JanLFNDATF 2021long20091667No ratings yet

- User's Manual GPS TK102Document12 pagesUser's Manual GPS TK102ms.debora.verdonckNo ratings yet

- American Bureau of Shipping: Check Sheet On Solas Surveys-Slr/GmdssDocument9 pagesAmerican Bureau of Shipping: Check Sheet On Solas Surveys-Slr/GmdssajayiNo ratings yet

- Ra 0706Document11 pagesRa 0706Maria-Rafailia SaridakiNo ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- AIM Apparatus Required: Yashkaran Singh 18BEI0122Document8 pagesAIM Apparatus Required: Yashkaran Singh 18BEI0122yashkaran singhNo ratings yet

- Ate Lab5Document8 pagesAte Lab5yashkaran singhNo ratings yet

- Ate Lab5Document7 pagesAte Lab5yashkaran singhNo ratings yet

- Automated Test Engineering Experiment No 4 QSMVI Using QT 200Document6 pagesAutomated Test Engineering Experiment No 4 QSMVI Using QT 200yashkaran singhNo ratings yet

- A New Financial Advisory Practice in Detroit Assignment HelpDocument4 pagesA New Financial Advisory Practice in Detroit Assignment Helpscott harryNo ratings yet

- Inventor IDocument17 pagesInventor ICharlton Pretel DiazNo ratings yet

- Paul Clements Evaluating A Software ArchitectureDocument23 pagesPaul Clements Evaluating A Software ArchitectureDbluepengLumNo ratings yet

- NSD Prospectus 2019Document42 pagesNSD Prospectus 2019sanjay sharmaNo ratings yet

- Mohammed - C.V 2023 NewDocument1 pageMohammed - C.V 2023 NewAli AlharbiNo ratings yet

- Prototyping and Emulation: Technische Informatik Universitat Tiibingen Tiibingen, GermanyDocument2 pagesPrototyping and Emulation: Technische Informatik Universitat Tiibingen Tiibingen, Germanyshankar1577No ratings yet

- M.Tech MVLSI 2021 22Document1 pageM.Tech MVLSI 2021 22Mission BNo ratings yet

- Definition of DesignDocument4 pagesDefinition of DesignTehreem Asim100% (2)

- Industrial ArchitectureDocument107 pagesIndustrial ArchitectureJohn ChoudhuryNo ratings yet

- KAI Web Page V2Document30 pagesKAI Web Page V2Shala EdinNo ratings yet

- Thesis Proposal PDFDocument6 pagesThesis Proposal PDFAnonymous ST8TKSNo ratings yet

- Bahcesehir University Faculty of Architecture and Design Arch 5432 - Urban Housing Fall 2018-2019Document4 pagesBahcesehir University Faculty of Architecture and Design Arch 5432 - Urban Housing Fall 2018-2019cici mNo ratings yet

- Facilitator - S Guide To SAFe - Architect SyncDocument5 pagesFacilitator - S Guide To SAFe - Architect SyncgigiNo ratings yet

- Ec1461 Vlsi DesignDocument17 pagesEc1461 Vlsi DesignArunkumarNo ratings yet

- Unit IDocument12 pagesUnit IgayathriNo ratings yet

- Facility Planning - Layout Process 4Document102 pagesFacility Planning - Layout Process 4nouman khan100% (1)

- Site Planning - Design ProcessDocument14 pagesSite Planning - Design ProcessShaira Mae Tolentino CaliboNo ratings yet

- Zuberi Final Notes Directions PDFDocument45 pagesZuberi Final Notes Directions PDFAnonymous jmpYout244No ratings yet

- Checklist Mechanical Block-Outs and Pipe SleevesDocument2 pagesChecklist Mechanical Block-Outs and Pipe SleevesImho Tep100% (1)

- Review and Approval of Novel ConceptsDocument34 pagesReview and Approval of Novel ConceptsZhenghua WangNo ratings yet

- Rimini Street Corporate Style Guide PDFDocument11 pagesRimini Street Corporate Style Guide PDFBayCreativeNo ratings yet

- A Practical Approach To Jira Essentials For Scrum MastersDocument18 pagesA Practical Approach To Jira Essentials For Scrum MastersSuharshani WickramasingheNo ratings yet

- Pearson Current TextbooksDocument288 pagesPearson Current TextbooksBeenu Bhalla33% (3)