Professional Documents

Culture Documents

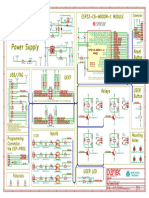

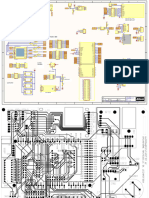

Down - Load - I/F: Assemble C113&L102 When Y101 Assemble Third Overtone Crystal

Uploaded by

Zeferino OlivOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Down - Load - I/F: Assemble C113&L102 When Y101 Assemble Third Overtone Crystal

Uploaded by

Zeferino OlivCopyright:

Available Formats

5 4 3 2 1

Notes:

1. Pin105 to pin203 of ZR36862/8 is 5V & 3.3V tolerant both.

2. ZR36868 is used for 6 or 8 CH audio out application.

ZR36862 is used for 2 CH audio out application, and pin111/112 could be used as GPCIO.

TACT_OFFSET

SPDL_SENS+

SPDL_SENS-

FACT_OFFSET

MD_DVD

DVD_LD

MD_CD

CD_LD

RFD

RFC

RFE

RFB

RFA

RFF

VC

R102 FB101 220Z

DSPVCC33

TRACK_S TRACK_S R128 51K 0R

D SLED_S SLED_S R105 30K SLED_PWM R115 100K D

SPINDLE_S SPINDLE_S R104 15K SPINDLE_PWM +

R140 NM [10K] R101 C121 C122 C113 L102

FS3 R141 NM [10K] FOCUS_S R127 43K FOCUS_PWM 20K 1% 0.1uF 100uF/16V

FS2 FOCUS_S

R142 NM [4K7] C103 VDDAFE NM NM

FS1 C104 C105 C101 C102 0.1uF 220pF 2.7uH

R113

HOMESW

D5V 1nF 1nF 27nF 22nF C114 OSCIN

CN101 VDDPWM FB102 220Z 33pF

CLOSE

75R

OPEN

1 D5V

OUTSW

DUPTD0 1nF C110

CD/DVD

2

DRVSB

INSW

3 DUPRD0 + Y101

4 DUPRD1 VDDPWM C119 C120 27.000MHz

DUPTD1 0.1uF 220uF/10V R112

CLOSE

1nF C109 220K Assemble C113&L102 when Y101

OPEN

RF

RFD

RFC

4P X 2.5MM

RFB

RFA

DOWN_LOAD_I/F assemble Third overtone

CD_DVD

OUTSW

DRVSB

IRRCV R129 Crystal

RFINN

RFINP

IRRCV

INSW

FPC_CLK 75R

FPC_CLK FPC_DOUT

FPC_DOUT C115

DSPVCC18

VDDDAC FB106 220Z OSCOUT

DSPVCC33 DSPVCC33

33pF

1

+ C124 1 PH1

.

208

207

206

205

204

203

202

201

200

199

198

197

196

195

194

193

192

191

190

189

188

187

186

185

184

183

182

181

180

179

178

177

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

C123 100uF/16V

.

U101A 0.1uF

RD1 TD1

Use it to connect the shell of the crystal to ground.

GPCIO[16]/SSCTXD

GPCIO[47]/SSCCLK

GPCIO[38]/DUPTD1

GPCIO[37]/DUPRD1

GPCIO[36]/DUPTD0

GPCIO[35]/DUPRD0

GPCIO[41]/PWMCO[0]

GNDPWM

VDD-IP

RFP

IDGPCIO[4]/PWMCO[6]

GPCIO[46]/PWMCO[5]

VDDPWM

GPCIO[45]/PWMCO[4]

GPCIO[44]/PWMCO[3]

GPCIO[43]/PWMCO[2]

IDGPCIO[7]/SPINDLEPULSE

IDGPCIO[6]/SLEDPULSE

ICGPCIO[7]

ICGPCIO[6]

GNDP

IDGPCIO[3]

VDDP

ICGPCIO[5]

ICGPCIO[4]

GNDC

GPCIO[32]

VDDC

AGND1

AGNDREF

DVD_LD

CD_LD

DVD_MD

CD_MD

RESOUT

VBGAP

VC

F

K

E

AGND

J

D

H

C

AVDD

SVDD

B

AVDD1

A

G

RFN

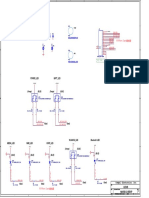

HYPER_TERMINAL I/F MARK5

.

FB103 220Z

DSPVCC18

1

C178 C116 + C117

0.1uF 1nF 100uF/16V

FPC_STB 1 156

FPC_STB SSCRXD/GPCIO[17] GNDDACBS2 R106 392R 1%

2 MEMCS#[1]/GPCIO[18] GNDDACP 155

3 VDDP RSET 154

MEMAD15 4 153

MEMAD16 MEMAD[15] C/B/U C_B_U

5 MEMAD[16] VDDDAC 152

MEMAD14 6 151

MEMAD13 MEMAD[14] Y/R/V Y_R_V

C 7 MEMAD[13] CVBS/C 150 CVBS_C

C

MEMAD12 8 149

MEMDA15 9

MEMAD[12]/PLLCFGA

MEMDA[15]

ZR36868 VDDDAC

CVBS/G/Y 148 G_Y

MEMAD11 10 147

MEMDA7 MEMAD[11]/PLLCFGP Y/C

11 MEMDA[7] GNDDACD 146

12 145 RESET DSPVCC33

MEMAD10 GNDP GNDDACD OSCIN

13 MEMAD[10] GCLK 144

MEMDA14 14 143 OSCOUT VGND R111 R110 R109 R108

MEMAD9 MEMDA[14] XO VDDA

15 MEMAD[9] VDDA 142 75R 1% 75R 1% 75R 1% 75R 1%

MEMDA6 16 141 RESET

MEMDA[6]

257

256

255

254

253

252

251

250

249

248

247

246

245

244

243

MEMAD8 RESET# R120

17 MEMAD[8] GNDA 140

MEMDA13 18 139 10K + C108

MEMDA5 MEMDA[13] GNDP 10uF

19 138

HOLE49

HOLE48

HOLE47

HOLE46

HOLE45

HOLE44

HOLE43

HOLE42

HOLE41

HOLE40

HOLE39

HOLE38

HOLE37

HOLE36

HOLE35

MEMDA[5] VDD VGND

20 137 R114

MEMAD[20]/GPCIO[19]/MEMCS#[2] IDGPCIO[2]

3

21 136 R143 100R 100R

MEMDA12 VDDP GPCIO[31] R144 100R I2CCLK Q101 VGND

22 MEMDA[12] DJTCK/ICGPCIO[3]/VID[0] 135 I2CDAT 1

MEMWR- 23 209 242 134 9014

MEMWR- MEMWR# HOLE1 HOLE34 DJTDO/GPCIO[30]/VID[1] MUTEC

MEMDA4 24 210 241 133

MEMDA[4] HOLE2 HOLE33 DJTDI/GPCIO[29]/VID[2]

2

C125

2

25 VDDC 211 HOLE3 HOLE32 240 DJTMS/GPCIO[28]/VID[3] 132

MEMDA11 26 212 239 131 0.1uF D101 R116

MEMDA3 MEMDA[11] HOLE4 U101B HOLE31 VDDC LL4148 10K

27 MEMDA[3] 213 HOLE5 HOLE30 238 GNDC 130

MEMAD19 28 214 ZR36862/8 237 129

MEMAD[19]/PLLSEL HOLE6 HOLE29 DJTCK2/ICETCK/GPCIO[27]/VID[4]

29 GNDC 215 HOLE7 HOLE28 236 DJTDO2/ICETDO/IDGPCIO[1]/VID[5] 128

MEMDA10

1

30 MEMDA[10] 216 HOLE8 HOLE27 235 DJTDI2/ICETDI/ICGPCIO[2]/VID[6] 127

MEMAD18 31 217 234 126

MEMAD[18] HOLE9 HOLE26 DJTMS2/ICETMS/GPCIO[26]/VID[7]

32 GNDP 218 HOLE10 HOLE25 233 VDDP 125

MEMDA2 33 219 232 124

MEMDA[2] HOLE11 HOLE24 COSYNC/CJTMS/ICGPCIO[1]/VCLKx2

HOLE12

HOLE13

HOLE14

HOLE15

HOLE16

HOLE17

HOLE18

HOLE19

HOLE20

HOLE21

HOLE22

HOLE23

MEMAD17 34 123

MEMDA9 MEMAD[17] GNDP

35 MEMDA[9] CJTDO/GPCIO[25]/HSYNC 122 HSYNC

MEMAD7 36 121

MEMDA1 MEMAD[7] CJTDI/GPCIO[24]/VSYNC R124 33R VSYNC AIN

37 120

RAMDAT10

RAMDAT11

RAMDAT12

RAMDAT13

RAMDAT14

RAMDAT15

RAMDAT10

RAMDAT11

RAMDAT12

RAMDAT13

RAMDAT14

RAMDAT15

RAMADD4

RAMADD5

RAMADD6

RAMADD7

RAMADD8

RAMADD9

RAMADD4

RAMADD5

RAMADD6

RAMADD7

RAMADD8

RAMADD9

RAMDAT8

RAMDAT9

MEMDA[1] CJTCK/GPCIO[23]/AIN AIN

RAMDQM

RAMDQM

RAMDAT8

RAMDAT9

MEMAD6 U102

220

221

222

223

224

225

226

227

228

229

230

231

38 MEMAD[6] VDDP-A2 119

MEMDA8 39 118 IAMCLK R117 33R AMCLK U103

PCLK

PCLK

MEMAD5 MEMDA[8] AMCLK AMCLK

40 MEMAD[5] GNDP-A2 117

41 116 IABCLK R118 33R ABCLK

MEMDA0 VDDP ABCLK R103 33R ALRCLK ABCLK

MEMDA[15:0] 42 MEMDA[0] ALRCLK 115 ALRCLK

MEMAD4 43 114

MEMRD- MEMAD[4] GPAIO MIC_DET IAOUT0 R190 33R

MEMRD- 44 MEMRD# AOUT[0] 113 AOUT0

MEMAD3 45 112 IAOUT1 R191 33R C126 C173 C174

MEMAD2 MEMAD[3] GPCIO[22]/AOUT[1] IAOUT2 R192 33R AOUT1 33pF 33pF 33pF

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

46 MEMAD[2] GPCIO[21]/AOUT[2] 111 AOUT2

MEMCS0- 47 110 SPDIF

B MEMCS0- MEMAD1 MEMCS#[0] SPDIF SPDIF B

48 109

VSS

A4

A5

A6

A7

A8

A9

NC

CKE

CLK

UDQM

NC

VDDQ

DQ8

DQ9

VSSQ

DQ10

DQ11

VDDQ

DQ12

DQ13

VSSQ

DQ14

DQ15

VSS

VSS

A4

A5

A6

A7

A8

A9

NC

CKE

CLK

UDQM

NC

VDDQ

DQ8

DQ9

VSSQ

DQ10

DQ11

VDDQ

DQ12

DQ13

VSSQ

DQ14

DQ15

VSS

MEMAD0 MEMAD[1]/BOOTSEL2 IDGPCIO[0]

MEMAD[19:0] 49 MEMAD[0]/BOOTSEL1 ICGPCIO[0] 108 MIC_ON

50 GNDP GNDP 107

51 VDD-IP CPUNMI/GPCIO[20] 106

52 105 K4S161622C-TC/L70 NM

RAMCS#[0]/RAMBA1

VDDP VDDP

A10/AP

A10/AP

LDQM

VDDQ

VDDQ

LDQM

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VDD

VDD

VDD

VDD

RAS

CAS

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

RAS

CAS

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

RAMADD[10]

RAMADD[11]

WE

WE

RAMDAT[10]

RAMDAT[11]

RAMDAT[12]

RAMDAT[13]

RAMDAT[14]

RAMDAT[15]

CS

CS

BA

BA

A3

A2

A1

A0

A3

A2

A1

A0

RAMADD[4]

RAMADD[3]

RAMADD[5]

RAMADD[2]

RAMADD[6]

RAMADD[1]

RAMADD[7]

RAMADD[0]

RAMADD[8]

RAMADD[9]

RAMDAT[8]

RAMDAT[7]

RAMDAT[9]

RAMDAT[6]

RAMDAT[5]

RAMDAT[4]

RAMDAT[3]

RAMDAT[2]

RAMDAT[1]

RAMDAT[0]

RAMCS#[1]

RAMRAS#

RAMCAS#

GNDPCLK

VDDPCLK

RAMBA[0]

RAMDQM

RAMWE#

MARK6

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

GNDC

GNDC

GNDP

GNDP

GNDP

GNDP

GNDP

VDDC

VDDC

VDDP

VDDP

VDDP

VDDP

VDDP

PCLK

9

8

7

6

5

4

3

2

1

9

8

7

6

5

4

3

2

1

DSPVCC33

1

100

101

102

103

104

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

RAMADD10

RAMADD10

RAMADD3

RAMADD2

RAMADD1

RAMADD0

RAMADD3

RAMADD2

RAMADD1

RAMADD0

RAMDAT7

RAMDAT6

RAMDAT5

RAMDAT4

RAMDAT3

RAMDAT2

RAMDAT1

RAMDAT0

RAMDAT7

RAMDAT6

RAMDAT5

RAMDAT4

RAMDAT3

RAMDAT2

RAMDAT1

RAMDAT0

RAMCS0-

RAMCS1-

RAMDQM

RAMDQM

RAMRAS-

RAMCAS-

RAMRAS-

RAMCAS-

RAMWE-

RAMWE-

RAMBA

RAMBA

NMI

RAMADD10

RAMDAT10

RAMDAT11

RAMDAT12

RAMDAT13

RAMDAT14

RAMDAT15

R125 R126

RAMADD4

RAMADD3

RAMADD5

RAMADD2

RAMADD6

RAMADD1

RAMADD7

RAMADD0

RAMADD8

RAMADD9

RAMDAT8

RAMDAT7

RAMDAT9

RAMDAT6

RAMDAT5

RAMDAT4

RAMDAT3

RAMDAT2

RAMDAT1

RAMDAT0

RAMCS0-

RAMCS1-

RAMDQM

R122

RAMWE-

IPCLK

RAMRAS-

RAMCAS-

RAMBA

1K 4K7 4K7

[NC] SDRAM speed <=7ns

R119

4K7

DSPVCC33

DSPVCC33

R123

PCLK

C152 C153 C154 C155 C156 C157

DSPVCC33

DSPVCC33

for PIN119

1

2

for PIN81

56R + C158 10nF 10nF 10nF 10nF 10nF 10nF

MODE: Play Download C106 47uF/16V

JP102 Open NM

JP102: Short [5pF]

BOOTSEL1

DSPVCC33 C179 C180 GND

DSPVCC33

1nF 1nF

A C130 C131 C132 C133 C134 C135 C136 C137 C138 C139 C140 C141 C142 C143 C144 C145 A

10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF + C159

47uF/16V

DSPVCC18

DSPVCC18 DSPVCC18 TECOBEST TECHNOLOGY

C146 C147 C148 C149 C150

10nF 10nF 10nF 10nF 10nF + C151 TB_V868

47uF/16V Title

PCB layout guy: please put these bypass capacitors close to main chip ZR36868 & SDRAM DV-405_PROCESSADOR

Size Document Number Rev

Date: Thursday, September 29, 2005 Sheet 2 of 6

5 4 3 2 1

You might also like

- TP - ms18VG - pb77 A13486 Schematic DiagramDocument7 pagesTP - ms18VG - pb77 A13486 Schematic DiagramJulian Andres RozoNo ratings yet

- Rasberry PiDocument1 pageRasberry PiMulyadi100% (1)

- KSGER STM32 Ver2 - 1S Schematic Rev 1 - Floobydust - 2Document1 pageKSGER STM32 Ver2 - 1S Schematic Rev 1 - Floobydust - 2Tom Tom100% (1)

- SM-T515 Esquematico Completo Anibal Garcia IrepairDocument51 pagesSM-T515 Esquematico Completo Anibal Garcia Irepairjuan lopezNo ratings yet

- Rene SchemDocument1 pageRene SchemKunal KhetaniNo ratings yet

- Boot Rom Program Memory: P0167 DSPDocument2 pagesBoot Rom Program Memory: P0167 DSPJorge MuñozNo ratings yet

- Behringer DDM4000Document12 pagesBehringer DDM4000Luis BagarelliNo ratings yet

- 17MB70 2Document16 pages17MB70 2Leandro RossiNo ratings yet

- ILI9486Document19 pagesILI9486bthcall3No ratings yet

- Usb Interface: KeyboardDocument18 pagesUsb Interface: KeyboardRedNo ratings yet

- m-4gq2 v01Document3 pagesm-4gq2 v01Aaron ZhengNo ratings yet

- 17mb81 2 SemaDocument11 pages17mb81 2 SemaelfrichNo ratings yet

- Mv1 6 FPCDocument1 pageMv1 6 FPCPatitoNo ratings yet

- Co-Locate: 3 GRN 4 REDDocument5 pagesCo-Locate: 3 GRN 4 REDguardia45No ratings yet

- ESP32-C6-EVB Rev ADocument1 pageESP32-C6-EVB Rev AGhiban ConstantinNo ratings yet

- 505 GX3235S-SCH MXL608Document6 pages505 GX3235S-SCH MXL608bbmp302No ratings yet

- VX5002 Circuit - 1Document3 pagesVX5002 Circuit - 1Juan Alejandro GonzalezNo ratings yet

- Contrast: "Menu/Esc" "Left" "Up" "Down" "Right" "OK"Document3 pagesContrast: "Menu/Esc" "Left" "Up" "Down" "Right" "OK"ZQumo100% (1)

- SCHEMATICS sr28c51351 - B - NA - VZ - PROD - 0302Document97 pagesSCHEMATICS sr28c51351 - B - NA - VZ - PROD - 0302wallison AndradeNo ratings yet

- RTS5209-GR: TP CN (TP To Board) CR/TP CNDocument4 pagesRTS5209-GR: TP CN (TP To Board) CR/TP CNRoberto MouraNo ratings yet

- Phone K33a42 Schematics L3 RepairDocument35 pagesPhone K33a42 Schematics L3 Repairprashanth handral0% (1)

- Compal LS-5654P r10 LED BoardDocument1 pageCompal LS-5654P r10 LED BoardQuenitoLucianoJoãoNo ratings yet

- Opencm904 Rev 10 Final SchematicDocument1 pageOpencm904 Rev 10 Final SchematicIvan SutiosoNo ratings yet

- NPCE885LA0DX DatasheetDocument2 pagesNPCE885LA0DX DatasheetHimanshu MishraNo ratings yet

- ESP32 CNCDocument1 pageESP32 CNCDada AndryNo ratings yet

- Samsung bn44-00508b-1 Ucc25600 Mcv14a spc1012t sn1108052dr sqt7011k SCHDocument6 pagesSamsung bn44-00508b-1 Ucc25600 Mcv14a spc1012t sn1108052dr sqt7011k SCHjamorNo ratings yet

- BN44 00508BDocument6 pagesBN44 00508BAntonio Carlos100% (1)

- 17mb35 2 SemaDocument12 pages17mb35 2 SemaHasan AKNo ratings yet

- PDF 文件以 "PDF 制作工厂" 试用版创建 ÿÿÿÿ ÿ: Vcc3.3 for analog Vcc3.3 For DigitalDocument11 pagesPDF 文件以 "PDF 制作工厂" 试用版创建 ÿÿÿÿ ÿ: Vcc3.3 for analog Vcc3.3 For DigitalJose BonillaNo ratings yet

- TIDMBP3Document5 pagesTIDMBP3PindiNo ratings yet

- Vga Input: Scart Video Output AmplifierDocument9 pagesVga Input: Scart Video Output AmplifierHoson AkNo ratings yet

- Vestel: Tuner Supply OpsionDocument20 pagesVestel: Tuner Supply OpsionQmichchou JaouadNo ratings yet

- Samyung Enc Co.,Ltd.: Inteface LCDDocument1 pageSamyung Enc Co.,Ltd.: Inteface LCDjasonelectronicsphilNo ratings yet

- Arduino UNO Rev3e SCH PDFDocument1 pageArduino UNO Rev3e SCH PDFHery Febrian DinogrohoNo ratings yet

- USBcablecrackerDocument1 pageUSBcablecrackersnyporNo ratings yet

- ALMA CORAZON Y VIDA (2da) (Final)Document1 pageALMA CORAZON Y VIDA (2da) (Final)Marlon C VNo ratings yet

- BLUEBERRY Guitar TABDocument3 pagesBLUEBERRY Guitar TABMatt BarnhardtNo ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFd4l170100% (1)

- Datasheet It8987e PDF FreeDocument1 pageDatasheet It8987e PDF Freemauri kñazovicNo ratings yet

- Datasheet It8987e PDF FreeDocument1 pageDatasheet It8987e PDF Freejhonnattan moreno casilimasNo ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFAnalia Madeled Tovar JimenezNo ratings yet

- Datasheet IT8987E PDFDocument1 pageDatasheet IT8987E PDFAnalia Madeled Tovar JimenezNo ratings yet

- Clean Chord Jam PDFDocument1 pageClean Chord Jam PDFshorovskyNo ratings yet

- Clean Chord JamDocument1 pageClean Chord JamshorovskyNo ratings yet

- SKR Pro V1.1 SCHDocument1 pageSKR Pro V1.1 SCHjulien tixadorNo ratings yet

- 1TB02011 011C44 Amp FF R1 SDW Ar 10001Document1 page1TB02011 011C44 Amp FF R1 SDW Ar 10001Sher DilNo ratings yet

- Usb Interface: BluerayDocument16 pagesUsb Interface: BluerayRedNo ratings yet

- ENG20009 - Arduino Board - SchematicDocument3 pagesENG20009 - Arduino Board - SchematicNisheli Perera100% (1)

- Pir402 Pir501 Pir201 Pir501 Pir402Document14 pagesPir402 Pir501 Pir201 Pir501 Pir402pabakNo ratings yet

- Place Only While ResetDocument4 pagesPlace Only While ResetRizwan SP100% (1)

- X3Document1 pageX3Richard AkelaNo ratings yet

- R9 MainPCB SCHDocument13 pagesR9 MainPCB SCHpradipto87No ratings yet

- Rt8223p With VoltagesDocument1 pageRt8223p With VoltagesVISHALNo ratings yet

- R1B S41M98HC1 (X600)Document8 pagesR1B S41M98HC1 (X600)Riza VirsadaNo ratings yet

- R5F10MMED: Magnetic Sensor (SMD)Document1 pageR5F10MMED: Magnetic Sensor (SMD)yash kumarNo ratings yet