Professional Documents

Culture Documents

Internal Assessment - II Subject: Ec5303 Digital System Design

Internal Assessment - II Subject: Ec5303 Digital System Design

Uploaded by

hello worldOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Internal Assessment - II Subject: Ec5303 Digital System Design

Internal Assessment - II Subject: Ec5303 Digital System Design

Uploaded by

hello worldCopyright:

Available Formats

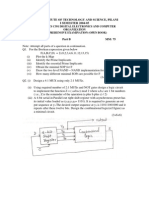

Department of ECE, Anna University, Chennai

Internal Assessment – II

Sem : III Programme : B.E Mon/Year : Oct 2020

Subject : EC5303 DIGITAL SYSTEM DESIGN

Time : 90 mins Answer All Questions Max Mark: 50

CO1 Use Boolean algebra and simplification procedures relevant to digital

logic.

CO2 Design various combinational digital circuits using logic gates.

CO3 Ability to analyse and design synchronous sequential circuits.

CO4 Ability to analyse and design asynchronous sequential circuits.

CO5 Ability to build logic gates and use programmable devices

S.No Questions Marks BL CO

PART – A 7 X 2 = 14

1 Implement the following Boolean function with a MUX 2 L3 2

F(A,B,C,D)= ∑ (0,1,3,4,8,9,15)

2 The serial adder of the given Figure uses two four bit registers. 2 L3 2

Register A holds the binary number 0101 and register B holds 0111.

The carry flip flop is initially reset to 0. List the binary

values in register A and the carry flip flop after each shift.

3 What is the function of priority Encoder. 2 L1 2

4 Write the function table of SR latch using NAND gate with control 2 L1 3

input.

5 Write the characteristic equation of all Flipflops 2 L1 3

6 A flip flops has a 5 ns delay from the time the clock edge occurs to 2 L2 3

the time the output is complemented. What is the maximum delay in a

10bit binary ripple counter that uses these flip flops? What is the

maximum frequency at which the counter can operate reliably?

7 How many states are possible for a K-bit Ring counter and K-bit 2 L1 3

Johnson Counter.

PART – B 2 X 12 = 24

8a (i). Construct a 5 to 32 line decoder with four 3 to 8 line 12 L2,L3 2

decoders with enable and a 2 to 4 line decoder. Use block

Diagram for the Component. (4)

(ii). Design a Decimal Adder circuit. (8)

Or

8b (i). Construct a 16x1 MUX with two 8x1 and 2x1 MUX. 12 L2,L3 2

Use block Diagram for the Component. (4)

(ii). Design a 3-bit Magnitude Comparator Circuit. (8)

9 .a Design a 3-bit synchronous counter using JK FF. 12 L3 3

Or

9.b A Sequential circuit has two JK FF's A and B, two inputs x and y and 12 L2,L3 3

one output z. The FF input equations and circuit output equations are:

JA=Bx+B'y' KA= B'xy' JB= A'x KB= A+xy'

Z=Ax'y'+Bx'y'

(i). Derive the state equations for A and B.

(ii). Tabulate the State table.

(iii). Draw the logic diagram of the circuit.

PART – C 1 X 12 =1 2

10 The counter of given Figure has two control inputs—Load (L) and 12 L4 3

Count (C)—and a data input, (I).

a. Obtain the characteristic table and equation

b. Derive the flip‐flop input equations for J and K of the first

stage in terms of L, C, and I

You might also like

- Stealth Amateur RadioDocument7 pagesStealth Amateur RadioJames ClarkNo ratings yet

- Basic Digital Signal Processing: Butterworths Basic SeriesFrom EverandBasic Digital Signal Processing: Butterworths Basic SeriesRating: 5 out of 5 stars5/5 (1)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (1)

- Esab PDFDocument66 pagesEsab PDFradomir46No ratings yet

- Digital Subscriber LineDocument91 pagesDigital Subscriber LinePrabudh BansalNo ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- Switching Theory and Logic Design (CSE-203) (Makeup)Document2 pagesSwitching Theory and Logic Design (CSE-203) (Makeup)Random ShitNo ratings yet

- DSDV Assignment 2Document1 pageDSDV Assignment 2h.s.surabhi2005No ratings yet

- LAB A-05 (Week 6) Construction and Implementation of Combinational Logic CircuitsDocument2 pagesLAB A-05 (Week 6) Construction and Implementation of Combinational Logic CircuitsEU JUN HONGNo ratings yet

- 9A04306 Digital Logic Design1Document4 pages9A04306 Digital Logic Design1Mahaboob SubahanNo ratings yet

- Digital ElectronicsDocument7 pagesDigital ElectronicsAlakaaa PromodNo ratings yet

- DLD Ques1Document2 pagesDLD Ques1mahbub mitulNo ratings yet

- 9a04306-Digital Logic DesignDocument1 page9a04306-Digital Logic DesignSheikh Noor MohammadNo ratings yet

- New Horizon College of Engineering, Bangalore: 19CSE33 USNDocument12 pagesNew Horizon College of Engineering, Bangalore: 19CSE33 USNAhmad RazaNo ratings yet

- Ec1312 DLCDocument5 pagesEc1312 DLCDeepak RavichandranNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- Nov - Dec 2018Document5 pagesNov - Dec 2018Pandyselvi BalasubramanianNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- UEC612Document1 pageUEC612wizard01.2022No ratings yet

- Q 6Document3 pagesQ 6Saranya MohanNo ratings yet

- BEE302ADocument2 pagesBEE302Ahrushithar27No ratings yet

- 15es3gcdec Jan 2018Document2 pages15es3gcdec Jan 2018MAHESHA GNo ratings yet

- SS07A4041 Digital IC ApplicationsDocument1 pageSS07A4041 Digital IC ApplicationsMahaboob SubahanNo ratings yet

- Code: 07A4041 B.Tech III Year I Semester (R07) Supplementary Examinations June 2015Document1 pageCode: 07A4041 B.Tech III Year I Semester (R07) Supplementary Examinations June 2015subbuNo ratings yet

- Apr - May 2023Document3 pagesApr - May 2023Pandyselvi BalasubramanianNo ratings yet

- Lab 4 Combinational Logic Design (K Maps)Document6 pagesLab 4 Combinational Logic Design (K Maps)Ifthakharul Alam ShuvoNo ratings yet

- Digital System Deisgn (ELE 2152) RCS (Makeup) Dec 19Document2 pagesDigital System Deisgn (ELE 2152) RCS (Makeup) Dec 19Abhinav KumarNo ratings yet

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- 21CS33 - ADE Question Bank 7876Document5 pages21CS33 - ADE Question Bank 7876AnshulNo ratings yet

- 2022 Dec. ECT203-CDocument2 pages2022 Dec. ECT203-CAthul RamNo ratings yet

- Bca 201 2022 25072022Document2 pagesBca 201 2022 25072022Nitimoy MondalNo ratings yet

- Dem QB Ut-1 110120Document2 pagesDem QB Ut-1 110120ABHI THORATNo ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- STLD3 - Question BankDocument6 pagesSTLD3 - Question Bankvidhya_bineeshNo ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- 9A04306 Digital Logic DesignDocument2 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- EES 311 - Digital Electronics MuranDocument4 pagesEES 311 - Digital Electronics MuranEusie JewelNo ratings yet

- Question Bank of Unit-III COADocument4 pagesQuestion Bank of Unit-III COAYamini BishtNo ratings yet

- Seat No.: InstructionsDocument4 pagesSeat No.: InstructionsYogesh KuteNo ratings yet

- DLD Question BankDocument5 pagesDLD Question BankHarshad ThiteNo ratings yet

- BCA I I Digital SystemDocument4 pagesBCA I I Digital SystemAmory Sabri AsmaroNo ratings yet

- IT - KOE 039 - ST2 Question Paper 2022-23Document2 pagesIT - KOE 039 - ST2 Question Paper 2022-23dhdw kwhdhwNo ratings yet

- L-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Document19 pagesL-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Sanjid ElahiNo ratings yet

- Be Winter 2020Document2 pagesBe Winter 2020SonuNo ratings yet

- COA Assignment - 3Document2 pagesCOA Assignment - 3KomalNo ratings yet

- COA QuestionBank - 1Document3 pagesCOA QuestionBank - 1itzzsandeshNo ratings yet

- Week 5 Digital - Logic - Design - Lab - Term2310Document1 pageWeek 5 Digital - Logic - Design - Lab - Term23101221108557No ratings yet

- DEM MidsemDocument3 pagesDEM MidsemSrishti anandNo ratings yet

- 2007 Anna University B.E Electrical and Electronics Digital Systems Question PaperDocument3 pages2007 Anna University B.E Electrical and Electronics Digital Systems Question PapernarencharuNo ratings yet

- Bec 3022Document4 pagesBec 3022h.s.surabhi2005No ratings yet

- 15es3gcdec Dec 2017Document4 pages15es3gcdec Dec 2017MAHESHA GNo ratings yet

- LDC AssignmentDocument3 pagesLDC Assignmentprateekagrawal812004No ratings yet

- Tugas 1 - 2Document6 pagesTugas 1 - 2Rizaldy Pahlevi Bin JamaluddinNo ratings yet

- Question Bank For DLCDocument8 pagesQuestion Bank For DLCAvina AshNo ratings yet

- Model Question Paper: Unit - I Questions Marks BLL CODocument2 pagesModel Question Paper: Unit - I Questions Marks BLL COViju JigajinniNo ratings yet

- Final Exam Paper 2016Document2 pagesFinal Exam Paper 20162016 01110No ratings yet

- BCS302Document2 pagesBCS302sagarblazaNo ratings yet

- Digital Logic Circuits PDFDocument8 pagesDigital Logic Circuits PDFnaina10691No ratings yet

- Ec 1202 Digital System DesignDocument8 pagesEc 1202 Digital System DesignworkubNo ratings yet

- Digital Electronics Question BankDocument6 pagesDigital Electronics Question BankReshna ShowkathNo ratings yet

- Digital Paper1Document5 pagesDigital Paper1Iyyakutti GanapathiNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Pioneer DEH-P3700MP - Radio CD-MP3 Installation ManualDocument6 pagesPioneer DEH-P3700MP - Radio CD-MP3 Installation ManualDharma InitiativeNo ratings yet

- Tantalum Surface Mount CapacitorsDocument24 pagesTantalum Surface Mount CapacitorsgausscanaveaNo ratings yet

- Ibs Site SurveyDocument5 pagesIbs Site SurveyminiiieeeeNo ratings yet

- Four Faith F3425Document3 pagesFour Faith F3425Sỹ TháiNo ratings yet

- Cobra Uniden Antenna Amplifiers Microphones CB Uniden Antenna Amplifiers MicrophonesDocument32 pagesCobra Uniden Antenna Amplifiers Microphones CB Uniden Antenna Amplifiers Microphonespetr lowNo ratings yet

- Fluorescent Multi-Layer Disc (FMD)Document19 pagesFluorescent Multi-Layer Disc (FMD)Gunjan ChaudharyNo ratings yet

- Part - I-Choose The Correct Answer: Debre Birh A N Polytechn I C College TechnologyDocument5 pagesPart - I-Choose The Correct Answer: Debre Birh A N Polytechn I C College TechnologyAbela DrrsNo ratings yet

- 132Kv Bus: Transformer 132/X KV Ynynd11Document8 pages132Kv Bus: Transformer 132/X KV Ynynd11karim_ouakliNo ratings yet

- Hexylon Datasheet (En)Document2 pagesHexylon Datasheet (En)dan r.No ratings yet

- Carbon DRWDocument121 pagesCarbon DRWEnrique Javier Contreras RamirezNo ratings yet

- Matlab DSP ToolboxDocument800 pagesMatlab DSP ToolboxChristian Fonseca RodriguezNo ratings yet

- STRF6654 (STR-F6654)Document16 pagesSTRF6654 (STR-F6654)Diki Al HabsyNo ratings yet

- ALL 02 ManualDocument47 pagesALL 02 ManualmcabreratNo ratings yet

- Current Sensor With 0.75 Inch Opening - SCT-0750 by MagnelabDocument1 pageCurrent Sensor With 0.75 Inch Opening - SCT-0750 by MagnelabEnrique MirazoNo ratings yet

- Coolermaster Rs 700 Asaa A1 700w ReportDocument1 pageCoolermaster Rs 700 Asaa A1 700w ReportRonan FranciscoNo ratings yet

- Block Diagram Regulated Power Supply System: WorkingDocument3 pagesBlock Diagram Regulated Power Supply System: Workingjunaid_bsNo ratings yet

- OptiX RTN 320 V100R005C00 Ethernet Service ConfigurationDocument38 pagesOptiX RTN 320 V100R005C00 Ethernet Service Configurationdanicoan50% (4)

- Govt. Job Preparation by Anowar HossainDocument19 pagesGovt. Job Preparation by Anowar HossainSaif Ar-ManNo ratings yet

- R36 User ManualDocument57 pagesR36 User ManualmiguelgordoNo ratings yet

- JVC FL3 Chassis LTZ32FX6 LCD TV SMDocument147 pagesJVC FL3 Chassis LTZ32FX6 LCD TV SMMy USERNAMENo ratings yet

- Mixer SheetDocument6 pagesMixer SheetBokamraNo ratings yet

- Passport 8600 Split Multi-Link Trunking Frequently Asked QuestionsDocument4 pagesPassport 8600 Split Multi-Link Trunking Frequently Asked Questionsnitesh_beNo ratings yet

- Experiment: 5: AIM: Study of CB & CE Characteristics of Transistor TheoryDocument5 pagesExperiment: 5: AIM: Study of CB & CE Characteristics of Transistor TheorysanjuNo ratings yet

- Harman / Kardon: Loudspeakers and Rooms For Multichannel Audio ReproductionDocument26 pagesHarman / Kardon: Loudspeakers and Rooms For Multichannel Audio ReproductionErling SanchezNo ratings yet

- LM2901 PDFDocument19 pagesLM2901 PDFFabio JuniorNo ratings yet

- Automatic Water Level Indicator & ControllerDocument11 pagesAutomatic Water Level Indicator & ControllertarunaNo ratings yet

- Siprotec 7sj85 ProfileDocument2 pagesSiprotec 7sj85 ProfileErnaniRCNo ratings yet