Professional Documents

Culture Documents

IT - KOE 039 - ST2 Question Paper 2022-23

Uploaded by

dhdw kwhdhwOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IT - KOE 039 - ST2 Question Paper 2022-23

Uploaded by

dhdw kwhdhwCopyright:

Available Formats

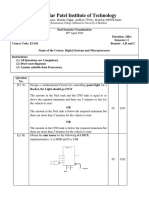

ROLL NO.

G.L. BAJAJ INSTITUTE OF TECHNOLOGY &MANAGEMENT

GREATER NOIDA

B. TECH(SEM-III)- (Branch-IT)

SECOND SESSIONAL TEST (ODD SEM 2022-23)

Digital Electronics (KOE-039)

Faculty Name: Dr. Mohan Singh/ Dr. Krishanu Kundu

Unit Covered: 2 & 3

Duration: 02:00Hrs ` Max. Marks:50

Note:

(i) No student will be allowed to leave the examination Room before end of exam.

(ii) Diagram should be neat and clean.

(iii) Mention Question number/section correctly.

(iv) Be precise in your answer.

(v) Do not write anything on question paper except Roll number.

Course Outcomes:

Following are the course outcomes of the subject: - Digital Electronics (KOE 039)

CO Code Course Outcome (CO) Bloom's Level

KOE 039.1 Apply concepts of Digital Binary System and implementation of Gates. L3- Apply

KOE 039.2 Analyze and design of Combinational logic circuits. L4 -Analyze

KOE 039.3 Analyze and design of Sequential logic circuits with their applications. L4 -Analyze

KOE 039.4 Implement the Design procedure of Synchronous & Asynchronous Sequential Circuits. L3- Apply

KOE 039.5 Apply the concept of Digital Logic Families with circuit implementation. L3- Apply

Section: A

1. Attempt all question: (2 x 5 = 10 Marks)

Q.No. Questions Marks CO BL

a) Implement 4:1 MUX using 2:1 MUX. 2 KOE 039.2 L3

b) Explain how BCD addition is carried out. 2 KOE 039.3 L2

c) Discus the Race Around Condition in JK Flip Flops and how it can 2 KOE 039.3 L2

be resolve?

d) What is the difference between Flip-Flop and Latch? 2 KOE 039.3 L2

e) Discuss the Difference between Asynchronous Counter and 2 KOE 039.3 L3

Synchronous Counter?

Section: B

2. Attempt any four of the following: (5 x 4 = 20 Marks)

Q.No. Questions Marks CO BL

a) Construct BCD adder using two 4-bit binary parallel adder and 5 KOE 039.2 L3

logic gates. Explain its working for two 4-bit binary numbers.

b) Design 5:32 Decoder using 3:8 Decoder. 5 KOE 039.2 L4

c) Convert SR Flip Flop to JK Flip Flop. 5 KOE 039.3 L3

d) Design a universal shift register that performs HOLD, SHIFT 5 KOE 039.3 L4

RIGHT, SHIFT LEFT, & LOAD.

e) Design and Implement the MOD 6 Asynchronous up counter using 5 KOE 039.3 L4

JK flip flop.

f) Write the Excitation Table & logic diagram of SR,JK,D & T flip 5 KOE 039.3 L2

flop.

Section: C

3. Attempt any one question (10 x 1 = 10 Marks)

Q.No. Questions Marks CO BL

a) Implement and design the following Boolean function 10 KOE 039.2 L4

𝒇(𝑨, 𝑩, 𝑪, 𝑫) = ∑𝒎(𝟎, 𝟏, 𝟑, 𝟒, 𝟕, 𝟖, 𝟗, 𝟏𝟏, 𝟏𝟒, 𝟏𝟓) using

(i) 4:1 MUX and

(ii) 2:1 MUX.

b) Draw 4-bit Johnson Counter using D flip flop. Explain the working 10 KOE 039.3 L4

with timing diagram and its applications. How many state produced

for the 4-bit Johnson Counter? Also find the output frequency if the

clock frequency is 12 MHz

4. Attempt any one question (10 x 1 = 10 Marks)

Q.No. Questions Marks CO BL

a) Design & Explain the 4 Bit Magnitude Comparator. 10 KOE 039.2 L4

b) Design 3 bit UP/DOWN counter with directional control Mode, M 10 KOE 039.3 L4

using T flip flop.

Course Outcome Wise Marks Distribution

70 48

32

20

-30 CO2 CO3

Checked By

(Head of Department)

You might also like

- New Horizon College of Engineering, Bangalore: 19CSE33 USNDocument12 pagesNew Horizon College of Engineering, Bangalore: 19CSE33 USNAhmad RazaNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Dhanalakshmi Srinivasan: College of EngineeringDocument3 pagesDhanalakshmi Srinivasan: College of Engineeringhamsalakshmi cNo ratings yet

- Information TechnologyDocument7 pagesInformation TechnologyDEVANAND ANo ratings yet

- Dhanalakshmi Srinivasan: College of EngineeringDocument3 pagesDhanalakshmi Srinivasan: College of Engineeringhamsalakshmi cNo ratings yet

- Sessional Test Format - ODD - SemesterDocument4 pagesSessional Test Format - ODD - SemesterAnkit SoniNo ratings yet

- Acseh0304 (DLD) 2Document5 pagesAcseh0304 (DLD) 2yt608118No ratings yet

- CVR College of Engineering: UGC Autonomous Institution - Affiliated To JNTUHDocument4 pagesCVR College of Engineering: UGC Autonomous Institution - Affiliated To JNTUHRAJESH ANo ratings yet

- Digital Electronics Circuits EC 33 SE EXAM 3RD SEM JAN 2017Document2 pagesDigital Electronics Circuits EC 33 SE EXAM 3RD SEM JAN 2017vinayakNo ratings yet

- Hours /-: ThirdDocument3 pagesHours /-: ThirdAhmad UmarNo ratings yet

- Veermata Jijabai Technological Institute: End Semester Examination December 2018 SEM-I, First Year MCADocument3 pagesVeermata Jijabai Technological Institute: End Semester Examination December 2018 SEM-I, First Year MCApradnya kingeNo ratings yet

- Sample Question Paper Digital Techniques PDFDocument5 pagesSample Question Paper Digital Techniques PDFAshutosh PatilNo ratings yet

- DSD Assessment 2Document3 pagesDSD Assessment 2hello worldNo ratings yet

- Digital ElectronicsDocument7 pagesDigital ElectronicsAlakaaa PromodNo ratings yet

- 14CS2005 April May 2018Document2 pages14CS2005 April May 2018Property RequestNo ratings yet

- DeDocument2 pagesDeUrvishNo ratings yet

- Ramaiah: Semester End Examinations FebruaryDocument3 pagesRamaiah: Semester End Examinations Februarysaikar.challaNo ratings yet

- S.Y. B.Tech. (Computer Science & Engineering) : End Semester Examination, December-2021Document1 pageS.Y. B.Tech. (Computer Science & Engineering) : End Semester Examination, December-2021A.K. GamingNo ratings yet

- III B.Tech. II Semester Regular Examinations Nov/Dec 2020: Code: 7G16DDocument7 pagesIII B.Tech. II Semester Regular Examinations Nov/Dec 2020: Code: 7G16DrameshNo ratings yet

- 2021 22 - Digital Electronics Koe049Document2 pages2021 22 - Digital Electronics Koe049ECE DepartmentNo ratings yet

- Coa 2021Document2 pagesCoa 2021jiumimyt0No ratings yet

- DD&CO Model Set1 Paper 2022 SchemeDocument2 pagesDD&CO Model Set1 Paper 2022 Schemeanveshrao024No ratings yet

- BCS302 Set 1Document2 pagesBCS302 Set 1Mina KimNo ratings yet

- BEE302ADocument2 pagesBEE302Ahrushithar27No ratings yet

- Digital System Design KEC302Document3 pagesDigital System Design KEC302Pragya AgrawalNo ratings yet

- DSD w20dsd GtuDocument1 pageDSD w20dsd GtuSandeep kumarNo ratings yet

- CSC219 - 356 - 132 CSC219 Dec 15Document5 pagesCSC219 - 356 - 132 CSC219 Dec 15Aniket AmbekarNo ratings yet

- BCS302 Set 2Document2 pagesBCS302 Set 2megumifushiguru999No ratings yet

- DSM 2022 EseDocument4 pagesDSM 2022 EsenarendraNo ratings yet

- Algorithms Modeexam Qp-NbaDocument3 pagesAlgorithms Modeexam Qp-NbaragunathNo ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- BCA I I Digital SystemDocument4 pagesBCA I I Digital SystemAmory Sabri AsmaroNo ratings yet

- Q.No Questions Marks CO BL: Part-A (10X 2 20) - Answer Any Ten QuestionsDocument2 pagesQ.No Questions Marks CO BL: Part-A (10X 2 20) - Answer Any Ten QuestionsKavin MartinNo ratings yet

- Bec 3022Document4 pagesBec 3022h.s.surabhi2005No ratings yet

- 18EC752 - Crypto - Model QP - 2 - 2021-22Document2 pages18EC752 - Crypto - Model QP - 2 - 2021-22Rohan SNo ratings yet

- CSC315 356 144-CSC315Document5 pagesCSC315 356 144-CSC315Aniket AmbekarNo ratings yet

- Dem 22421Document15 pagesDem 22421Payal VeerNo ratings yet

- Compiler DesignDocument4 pagesCompiler DesignSanidhya JadaunNo ratings yet

- SS 9A04306 Digital Logic DesignDocument1 pageSS 9A04306 Digital Logic DesignMahaboob SubahanNo ratings yet

- MP2 Coa BCS302 Paper 2022-23Document2 pagesMP2 Coa BCS302 Paper 2022-23mcuthor98No ratings yet

- 9A04306 Digital Logic Design1Document4 pages9A04306 Digital Logic Design1Mahaboob SubahanNo ratings yet

- Bca 201 2022 25072022Document2 pagesBca 201 2022 25072022Nitimoy MondalNo ratings yet

- Signal 2Document2 pagesSignal 2imvuuser1No ratings yet

- See AddDocument2 pagesSee Add1ms21ec132No ratings yet

- Seat No.: InstructionsDocument4 pagesSeat No.: InstructionsYogesh KuteNo ratings yet

- P18ec33 - W1Document2 pagesP18ec33 - W1aeunNo ratings yet

- Vlsi Model Question Paper 3 (June 2021)Document4 pagesVlsi Model Question Paper 3 (June 2021)PushpalathaNo ratings yet

- Kec 302 Digital System DesignDocument2 pagesKec 302 Digital System DesignAditya KasaudhanNo ratings yet

- CG Paper PUT - SECTION ADocument2 pagesCG Paper PUT - SECTION Akundan kumarNo ratings yet

- Question Bank DeldDocument3 pagesQuestion Bank DeldvkrNo ratings yet

- Switching Theory and Logic Design (CSE-203) (Makeup)Document2 pagesSwitching Theory and Logic Design (CSE-203) (Makeup)Random ShitNo ratings yet

- Metropolitan University, SylhetDocument1 pageMetropolitan University, SylhetJashon RoyNo ratings yet

- Verilog HDL 3rd - IA - 2020Document1 pageVerilog HDL 3rd - IA - 2020Mr girishNo ratings yet

- 9A04306 Digital Logic Design2Document1 page9A04306 Digital Logic Design2Mahaboob SubahanNo ratings yet

- Vlsi Model Question Paper 1 (June 2021)Document3 pagesVlsi Model Question Paper 1 (June 2021)PushpalathaNo ratings yet

- See Adld 2020Document2 pagesSee Adld 20201ms21ec132No ratings yet

- CD - R20 Model PaperDocument2 pagesCD - R20 Model PaperKappa yagnanandharajuNo ratings yet

- Digital Electronics Koe 039Document2 pagesDigital Electronics Koe 039Abhishek 8299No ratings yet

- 19EC303 DPSD Learners Copy 11 03 24Document56 pages19EC303 DPSD Learners Copy 11 03 24Marshmellow FFNo ratings yet

- YouGovPulse Windows Installation ManualDocument4 pagesYouGovPulse Windows Installation Manualdhdw kwhdhwNo ratings yet

- Assignment 4 DSDocument2 pagesAssignment 4 DSdhdw kwhdhwNo ratings yet

- Mini Project Report FormatDocument16 pagesMini Project Report Formatdhdw kwhdhwNo ratings yet

- DE - KOE 039 - Assignment #5Document1 pageDE - KOE 039 - Assignment #5dhdw kwhdhwNo ratings yet

- NullDocument2 pagesNulldhdw kwhdhwNo ratings yet

- SOP-Procedure Calibration of Metal TapesDocument12 pagesSOP-Procedure Calibration of Metal Tapeshaharamesh100% (1)

- Effect of Service Quality and Quality of Products To Customer Loyalty With Customer Satisfaction As Intervening Variable in PT. Nano Coating IndonesiaDocument13 pagesEffect of Service Quality and Quality of Products To Customer Loyalty With Customer Satisfaction As Intervening Variable in PT. Nano Coating IndonesiaCenter for Promoting Education and Research(CPER), USANo ratings yet

- Math5 q2 Mod8Document19 pagesMath5 q2 Mod8Pia JalandoniNo ratings yet

- ANSYS TurboGrid Users GuideDocument144 pagesANSYS TurboGrid Users GuideAndrés Edisson ÁguilaNo ratings yet

- Qualitative Data Analysis A Compendium of Techniques and A PDFDocument24 pagesQualitative Data Analysis A Compendium of Techniques and A PDFMARIANo ratings yet

- Calculus I ProjectDocument9 pagesCalculus I Projectapi-495320622No ratings yet

- Lecture11 PDFDocument22 pagesLecture11 PDFVrundNo ratings yet

- Surveying Lec1!16!17Document14 pagesSurveying Lec1!16!17brandonNo ratings yet

- Prediction of Airline Ticket Price: Motivation Models DiagnosticsDocument1 pagePrediction of Airline Ticket Price: Motivation Models DiagnosticsQa SimNo ratings yet

- MSC Mathematics - Part-I - Part-IIDocument16 pagesMSC Mathematics - Part-I - Part-IIDonka RaviNo ratings yet

- Pharm-D 2nd Scheme of StudiesDocument11 pagesPharm-D 2nd Scheme of StudiesEyssa MalikNo ratings yet

- Delphi XE2 Foundations - Part 1 - Rolliston, ChrisDocument160 pagesDelphi XE2 Foundations - Part 1 - Rolliston, ChrisJoel Quezada100% (2)

- Exam Sta1506 Assessment04 PDFDocument8 pagesExam Sta1506 Assessment04 PDFporschaveNo ratings yet

- Array PseudocodeDocument6 pagesArray PseudocodeMehabunnisaaNo ratings yet

- PENDULUMEXPERIMENTDocument14 pagesPENDULUMEXPERIMENTUyenNo ratings yet

- ApmDocument11 pagesApmsreyoshiNo ratings yet

- Network LayerDocument134 pagesNetwork Layershivang pandeyNo ratings yet

- Class 7 - IMO 2 PDFDocument5 pagesClass 7 - IMO 2 PDFChadwick TgrNo ratings yet

- Ge6253 Engineering Mechanics L T P c3 1 0 4Document1 pageGe6253 Engineering Mechanics L T P c3 1 0 4VarunNo ratings yet

- Title: Performance OF Digital Communication System Corrupted by Noise ObjectivesDocument16 pagesTitle: Performance OF Digital Communication System Corrupted by Noise ObjectivesAzie BasirNo ratings yet

- Apprentice Cable Splicer (2902)Document14 pagesApprentice Cable Splicer (2902)andresboy123No ratings yet

- Waqas Educational Academy Larkana Basic Maths Test Class: 9, 10, 11Document2 pagesWaqas Educational Academy Larkana Basic Maths Test Class: 9, 10, 11Mansoor Ali LaghariNo ratings yet

- Lampiran Hasil Pengolahan Data SemDocument5 pagesLampiran Hasil Pengolahan Data SemErwinia CartovoraNo ratings yet

- Dynamic Blocks-Hands OnDocument24 pagesDynamic Blocks-Hands OnPaul AlcantaraNo ratings yet

- MYJAVACAFE - Java Interview Questions (Delivered by Nageswara Rao From Inetsolv Institute of Hyderabad)Document21 pagesMYJAVACAFE - Java Interview Questions (Delivered by Nageswara Rao From Inetsolv Institute of Hyderabad)haibye424No ratings yet

- Looping Case StudyDocument9 pagesLooping Case StudyMukesh Kumar SinghNo ratings yet

- MCA SyllabusDocument38 pagesMCA Syllabusvijayrugi99No ratings yet

- Short Column AnalysisDocument1 pageShort Column Analysisrelu59No ratings yet

- 2.1 Random Variables 2.1.1 Definition: PX PX XDocument13 pages2.1 Random Variables 2.1.1 Definition: PX PX XMichael Hsiao100% (1)