Professional Documents

Culture Documents

24c04a, 24c08a, 24c16a

Uploaded by

rıdvan71Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

24c04a, 24c08a, 24c16a

Uploaded by

rıdvan71Copyright:

Available Formats

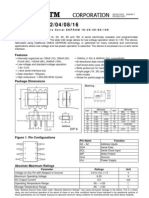

24C04A, 24C08A, 24C16A

Two-Wire Serial EEPROM

4K, 8K and 16K (8-bit wide)

FEATURES

Low voltage and low power operations:

FT24C04A/08A/16A: VCC = 1.8V to 5.5V

Maximum Standby current < 1µA (typically 0.02µA and 0.06µA @ 1.8V and 5.5V respectively).

16 bytes page write mode.

Partial page write operation allowed.

Internally organized: 512 8 (4K), 1024 8 (8K), 2048 8 (16K).

Standard 2-wire bi-directional serial interface.

Schmitt trigger, filtered inputs for noise protection.

Self-timed Write Cycle (5ms maximum).

1 MHz (5V), 400 kHz (1.8V, 2.5V, 2.7V) Compatibility.

Automatic erase before write operation.

Write protect pin for hardware data protection.

High reliability: typically 1, 000,000 cycles endurance.

100 years data retention.

Industrial temperature range (-40o C to 85o C).

Standard 8-pin DIP/SOP/TSSOP/DFN/MSOP and 5-pin SOT-23/TSOT-23 Pb-free packages.

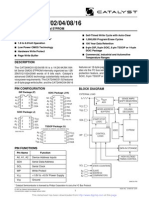

DESCRIPTION

The FT24C04A/08A/16A series are 4096/8192/16384 bits of serial Electrical Erasable and Programmable Read Only

Memory, commonly known as EEPROM. They are organized as 512/1024/2048 words of 8 bits (1 byte) each. The

devices are fabricated with proprietary advanced CMOS process for low power and low voltage applications. These

devices are available in standard 8-lead DIP, 8-lead SOP, 8-lead TSSOP, 8-lead DFN, 8-lead MSOP, and 5-lead SOT-

23/TSOT-23 packages. A standard 2-wire serial interface is used to address all read and write functions. Our

extended VCC range (1.8V to 5.5V) devices enables wide spectrum of applications.

PIN CONFIGURATION

Pin Name Pin Function

A2, A1, A0 Device Address Inputs

SDA Serial Data Input / Open Drain Output

SCL Serial Clock Input

WP Write Protect

NC No-Connect

© 2009 Fremont Micro Devices Inc. DS3001M-page1

24C04A, 24C08A, 24C16A

All these packaging types come in conventional or Pb-free certified.

FT24C04A/08A/16A

FT24C04A/08A/16A

A0 1 8 VCC

A1 2 7 WP SCL 1 5 WP

A2 3 6 SCL GND 2

GND 4 5 SDA SDA 3 4 VCC

8L DIP SOT-23-5

8L SOP TSOT-23-5

8L TSSOP

8L DFN

8L MSOP

ABSOLUTE MAXIMUM RATINGS

Industrial operating temperature: -40oC to 85oC

Storage temperature: -50oC to 125oC

Input voltage on any pin relative to ground: -0.3V to VCC + 0.3V

Maximum voltage: 8V

ESD protection on all pins: >2000V

* Stresses exceed those listed under “Absolute Maximum Rating” may cause permanent damage to the device.

Functional operation of the device at conditions beyond those listed in the specification is not guaranteed. Prolonged

exposure to extreme conditions may affect device reliability or functionality.

DS3001M-page2 © 2009 Fremont Micro Devices Inc.

24C04A, 24C08A, 24C16A

PIN DESCRIPTIONS

(A) SERIAL CLOCK (SCL)

The rising edge of this SCL input is to latch data into the EEPROM device while the falling edge of this clock is to

clock data out of the EEPROM device.

(B) DEVICE / CHIP SELECT ADDRESSES (A2, A1, A0)

These are the chip select input signals for the serial EEPROM devices. Typically, these signals are hardwired to

either VIH or VIL. If left unconnected, they are internally recognized as VIL. FT24C04A has A0 pin as no-connect.

FT24C08A has both A0 and A1 pins as no-connect. For FT24C16A, all device address pins (A0-A2) are no-

connect.

(C) SERIAL DATA LINE (SDA)

SDA data line is a bi-directional signal for the serial devices. It is an open drain output signal and can be wired-

OR with other open-drain output devices.

(D) WRITE PROTECT (WP)

The FT24C04A/08A/16A devices have a WP pin to protect the whole EEPROM array from programming.

Programming operations are allowed if WP pin is left un-connected or input to VIL. Conversely all programming

functions are disabled if WP pin is connected to VIH or VCC. Read operations is not affected by the WP pin’s input

level.

Table A

Chip Select/Device Max number of similar

Device No-Connect Pins

Address Pins Used devices on the same bus

FT24C04A A2, A1 A0 4

FT24C08A A2, A1, A0 2

FT24C16A (None) A2, A1, A0 1

MEMORY ORGANIZATION

The FT24C04A/08A/16A devices have 32/64/128 pages respectively. Since each page has 16 bytes, random word

addressing to FT24C04A/08A/16A will require 9/10/11 bits data word addresses respectively.

DEVICE OPERATION

(A) SERIAL CLOCK AND DATA TRANSITIONS

The SDA pin is typically pulled to high by an external resistor. Data is allowed to change only when Serial clock

SCL is at VIL. Any SDA signal transition may interpret as either a START or STOP condition as described below.

(B) START CONDITION

With SCL VIH, a SDA transition from high to low is interpreted as a START condition. All valid commands

must begin with a START condition.

© 2009 Fremont Micro Devices Inc. DS3001M-page3

24C04A, 24C08A, 24C16A

(C) STOP CONDITION

With SCL VIH, a SDA transition from low to high is interpreted as a STOP condition. All valid read or write

commands end with a STOP condition. The device goes into the STANDBY mode if it is after a read command.

A STOP condition after page or byte write command will trigger the chip into the STANDBY mode after the self-

timed internal programming finish.

(D) ACKNOWLEDGE

The 2-wire protocol transmits address and data to and from the EEPROM in 8 bit words. The EEPROM

acknowledges the data or address by outputting a "0" after receiving each word. The ACKNOWLEDGE signal

occurs on the 9th serial clock after each word.

(E) STANDBY MODE

The EEPROM goes into low power STANDBY mode after a fresh power up, after receiving a STOP bit in read

mode, or after completing a self-time internal programming operation.

Figure 1: Timing diagram for START and STOP conditions

SCL

SDA

START Data Data STOP

Condition Valid Transition Condition

Figure 2: Timing diagram for output ACKNOWLEDGE

START Condition

SCL

Data in

Data out ACK

DS3001M-page4 © 2009 Fremont Micro Devices Inc.

24C04A, 24C08A, 24C16A

DEVICE ADDRESSING

The 2-wire serial bus protocol mandates an 8 bits device address word after a START bit condition to invoke valid read

or write command. The first four most significant bits of the device address must be 1010, which is common to all

serial EEPROM devices. The next three bits are device address bits. These three device address bits (5th, 6th and 7th) are

to match with the external chip select/address pin states. If a match is made, the EEPROM device outputs an

ACKNOWLEDGE signal after the 8th read/write bit, otherwise the chip will go into STANDBY mode. However,

matching may not be needed for some or all device address bits (5th, 6th and 7th) as noted below. The last or 8th bit is a

read/write command bit. If the 8th bit is at VIH then the chip goes into read mode. If a “0” is detected, the device enters

programming mode.

FT24C04A uses A2 (5th) and A1 (6th) device address bits. Only four FT24C04A devices can be wired-OR on the same

2-wire bus. Their corresponding chip select address pins A2 and A1 must be hard wired and coded from 00 (b) to 11

(b). Chip select address pin A0 is not used.

FT24C08A uses only A2 (5th) device address bit. Only two FT24C08A devices can be wired-OR on the same 2-wire

bus. Their corresponding chip select address pin A2 must be hard-wired and coded from 0 (b) to 1 (b). Chip select

address pins A1 and A0 are not used.

FT24C16A does not use any device address bit. Only one FT24C16A device can be used on the on 2-wire bus. Chip

Select address pins A2, A1, and A0 are not used.

WRITE OPERATIONS

(A) BYTE WRITE

A byte write operation starts when a micro-controller sends a START bit condition, follows by a proper EEPROM

device address and then a write command. If the device address bits match the chip select address, the EEPROM

device will acknowledge at the 9th clock cycle. The micro-controller will then send the rest of the lower 8 bits word

address. At the 18th cycle, the EEPROM will acknowledge the 8-bit address word. The micro-controller will then

transmit the 8 bit data. Following an ACKNOWLDEGE signal from the EEPROM at the 27th clock cycle, the

micro-controller will issue a STOP bit. After receiving the STOP bit, the EEPROM will go into a self-timed

programming mode during which all external inputs will be disabled. After a programming time of TWC, the byte

programming will finish and the EEPROM device will return to the STANDBY mode.

(B) PAGE WRITE

A page write is similar to a byte write with the exception that one to sixteen bytes can be programmed along the

same page or memory row. All FT24C04A/08A/16A are organized to have 16 bytes per memory row or page.

With the same write command as the byte write, the micro-controller does not issue a STOP bit after sending the

1st byte data and receiving the ACKNOWLEDGE signal from the EEPROM on the 27th clock cycle. Instead it

sends out a second 8-bit data word, with the EEPROM acknowledging at the 36th cycle. This data sending and

EEPROM acknowledging cycle repeats until the micro-controller sends a STOP bit after the n 9th clock cycle.

After which the EEPROM device will go into a self-timed partial or full page programming mode. After the page

programming completes after a time of TWC, the devices will return to the STANDBY mode.

© 2009 Fremont Micro Devices Inc. DS3001M-page5

24C04A, 24C08A, 24C16A

The least significant 4 bits of the word address (column address) increments internally by one after receiving each

data word. The rest of the word address bits (row address) do not change internally, but pointing to a specific

memory row or page to be programmed. The first page write data word can be of any column address. Up to 16

data words can be loaded into a page. If more then 16 data words are loaded, the 17th data word will be loaded to

the 1st data word column address. The 18th data word will be loaded to the 2nd data word column address and so on.

In other word, data word address (column address) will “roll” over the previously loaded data.

(C) ACKNOWLEDGE POLLING

ACKNOWLEDGE polling may be used to poll the programming status during a self-timed internal programming.

By issuing a valid read or write address command, the EEPROM will not acknowledge at the 9th clock cycle if the

device is still in the self-timed programming mode. However, if the programming completes and the chip has

returned to the STANDBY mode, the device will return a valid ACKNOWLEDGE signal at the 9th clock cycle.

READ OPERATIONS

The read command is similar to the write command except the 8th read/write bit in address word is set to “1”. The three

read operation modes are described as follows:

(A) CURRENT ADDRESS READ

The EEPROM internal address word counter maintains the last read or write address plus one if the power supply

to the device has not been cut off. To initiate a current address read operation, the micro-controller issues a

START bit and a valid device address word with the read/write bit (8th) set to “1”. The EEPROM will response

with an ACKNOWLEDGE signal on the 9th serial clock cycle. An 8-bit data word will then be serially clocked out.

The internal address word counter will then automatically increase by one. For current address read the micro-

controller will not issue an ACKNOWLEDGE signal on the 18th clock cycle. The micro-controller issues a valid

STOP bit after the 18th clock cycle to terminate the read operation. The device then returns to STANDBY mode.

(B) SEQUENTIAL READ

The sequential read is very similar to current address read. The micro-controller issues a START bit and a valid

device address word with read/write bit (8th) set to “1”. The EEPROM will response with an ACKNOWLEDGE

signal on the 9th serial clock cycle. An 8-bit data word will then be serially clocked out. Meanwhile the internally

address word counter will then automatically increase by one. Unlike current address read, the micro-controller

sends an ACKNOWLEDGE signal on the 18th clock cycle signaling the EEPROM device that it wants another byte

of data. Upon receiving the ACKNOWLEDGE signal, the EEPROM will serially clocked out an 8-bit data word

based on the incremented internal address counter. If the micro-controller needs another data, it sends out an

ACKNOWLEDGE signal on the 27th clock cycle. Another 8-bit data word will then be serially clocked out. This

sequential read continues as long as the micro-controller sends an ACKNOWLEDGE signal after receiving a new

data word. When the internal address counter reaches its maximum valid address, it rolls over to the beginning of

the memory array address. Similar to current address read, the micro-controller can terminate the sequential read

by not acknowledging the last data word received, but sending a STOP bit afterwards instead.

(C) RANDOM READ

Random read is a two-steps process. The first step is to initialize the internal address counter with a target read

address using a “dummy write” instruction. The second step is a current address read.

To initialize the internal address counter with a target read address, the micro-controller issues a START bit first,

follows by a valid device address with the read/write bit (8th) set to “0”. The EEPROM will then acknowledge.

The micro-controller will then send the address word. Again the EEPROM will acknowledge. Instead of

sending a valid written data to the EEPROM, the micro-controller performs a current address read instruction to

read the data. Note that once a START bit is issued, the EEPROM will reset the internal programming process and

continue to execute the new instruction - which is to read the current address.

DS3001M-page6 © 2009 Fremont Micro Devices Inc.

24C04A, 24C08A, 24C16A

© 2009 Fremont Micro Devices Inc. DS3001M-page7

24C04A, 24C08A, 24C16A

Figure 8: SCL and SDA Bus Timing

AC CHARACTERISTICS

1.8 V 2.5-5.0 V

Symbol Parameter Unit

Min Max Min Max

fSCL Clock frequency, SCL 400 1000 kHz

tLOW Clock pulse width low 1.3 0.4 µs

tHIGH Clock pulse width high 0.6 0.4 µs

tI Noise suppression time(1) 180 120 ns

tAA Clock low to data out valid 0.3 0.9 0.2 0.55 µs

Time the bus must be free before a

tBUF new transmission can start(1)

1.3 0.5 µs

tHD.STA START hold time 0.6 0.25 µs

tSU.STA START set-up time 0.6 0.25 µs

tHD.DAT Data in hold time 0 0 µs

tSU.DAT Data in set-up time 100 100 ns

tR Input rise time (1)

0.3 0.3 µs

tF Input fall time (1)

300 100 ns

tSU.STO STOP set-up time 0.6 0.25 µs

tDH Date out hold time 50 50 ns

WR Write cycle time 5 5 ms

(1) o

Endurance 25 C, Page Mode, 3.3V 1,000,000 Write Cycles

Notes: 1. This Parameter is expected by characterization but are not fully screened by test.

2. AC Measurement conditions:

RL (Connects to Vcc): 1.3KΩ

Input Pulse Voltages: 0.3Vcc to 0.7Vcc

Input and output timing reference Voltages: 0.5Vcc

DS3001M-page8 © 2009 Fremont Micro Devices Inc.

24C04A, 24C08A, 24C16A

DC CHARACTERISTICS

Symbol Parameter Test Conditions Min Typical Max Units

VCC1 24CA supply VCC 1.8 5.5 V

ICC Supply read current VCC @ 5.0V SCL = 400 kHz 0.5 1.0 mA

ICC Supply write current VCC @ 5.0V SCL = 400 kHz 2.0 3.0 mA

ISB1 Supply current VCC @ 1.8V, VIN = VCC or VSS 1.0 µA

ISB2 Supply current VCC @ 2.5V, VIN = VCC or VSS 1.0 µA

ISB3 Supply current VCC @ 5.0V, VIN = VCC or VSS 0.07 1.0 µA

IIL Input leakage current VIN = VCC or VSS 3.0 µA

ILO Output leakage current VIN = VCC or VSS 3.0 µA

VIL Input low level -0.6 VCC 0.3 V

VIH Input high level VCC0.7 VCC + 0.5 V

VOL1 Output low level VCC @ 1.8V, IOL = 0.15 mA 0.2 V

VOL2 Output low level VCC @ 3.0V, IOL = 2.1 mA 0.4 V

© 2009 Fremont Micro Devices Inc. DS3001M-page9

24C04A, 24C08A, 24C16A

ORDER CODE:

FT24CXXA – XXX - X

Packaging

B: Tube

T: Tape and Reel

Temperature Range

U: -40 to 85 oC

Package

D: DIP

S: SOP Option

M: MSOP G: Green Package RoHS Compliant

T: TSSOP R: RoHS Compliant

L: SOT23

P: TSOT23

N: DFN

ORDER INFORMATION

Order code Temperature

Vcc Package Option Packaging

Range

FT24C04A-UDG-B Green Package Tube

DIP8

FT24C04A-UDR-B RoHS Tube

FT24C04A-USG-B Green Package Tube

FT24C04A-USG-T Green Package T/R

SOP8

FT24C04A-USR-B RoHS Tube

FT24C04A-USR-T RoHS T/R

FT24C04A-UTG-B Green Package Tube

1.8v-5.5v -40-850C

FT24C04A-UTG-T Green Package T/R

TSSOP8

FT24C04A-UTR-B RoHS Tube

FT24C04A-UTR-T RoHS T/R

FT24C04A-ULG-T Green Package T/R

SOT23-5

FT24C04A-ULR-T RoHS T/R

FT24C04A-UPG-T Green Package T/R

TSOT23-5

FT24C04A-UPR-T RoHS T/R

DS3001M-page10 © 2009 Fremont Micro Devices Inc.

24C04A, 24C08A, 24C16A

ORDER INFORMATION(CONTINUED)

Temperature

Order code Vcc Package Option Packaging

Range

FT24C08A-UDG-B Green Package Tube

DIP8

FT24C08A-UDR-B RoHS Tube

FT24C08A-USG-B Green Package Tube

FT24C08A-USG-T SOP8 Green Package T/R

FT24C08A-USR-B RoHS Tube

FT24C08A-USR-T RoHS T/R

FT24C08A-UTG-B Green Package Tube

FT24C08A-UTG-T Green Package T/R

TSSOP8

FT24C08A-UTR-B RoHS Tube

FT24C08A-UTR-T RoHS T/R

FT24C08A-ULG-T Green Package T/R

SOT23-5

FT24C08A-ULR-T RoHS T/R

FT24C08A-UPG-T Green Package T/R

TSOT23-5

FT24C08A-UPR-T 1.8v-5.5v -40-850C RoHS T/R

FT24C16A-UDG-B Green Package Tube

DIP8

FT24C16A-UDR-B RoHS Tube

FT24C16A-USG-B Green Package Tube

FT24C16A-USG-T Green Package T/R

SOP8

FT24C16A-USR-B RoHS Tube

FT24C16A-USR-T RoHS T/R

FT24C16A-UTG-B Green Package Tube

FT24C16A-UTG-T Green Package T/R

TSSOP8

FT24C16A-UTR-B RoHS Tube

FT24C16A-UTR-T RoHS T/R

FT24C16A-ULG-T Green Package T/R

SOT23-5

FT24C16A-ULR-T RoHS T/R

FT24C16A-UPG-T Green Package T/R

TSOT23-5

FT24C16A-UPR-T RoHS T/R

© 2009 Fremont Micro Devices Inc. DS3001M-page11

24C04A, 24C08A, 24C16A

DIP8 PACKAGE OUTLINE DIMENSIONS

Dimensions In Millimeters Dimensions In Inches

Symbol

Min Max Min Max

A 3.710 4.310 0.146 0.170

A1 0.510 0.020

A2 3.200 3.600 0.126 0.142

B 0.380 0.570 0.015 0.022

B1 1.524(BSC) 0.060(BSC)

C 0.204 0.360 0.008 0.014

D 9.000 9.400 0.354 0.370

E 6.200 6.600 0.244 0.260

E1 7.320 7.920 0.288 0.312

e 2.540 (BSC) 0.100(BSC)

L 3.000 3.600 0.118 0.142

E2 8.400 9.000 0.331 0.354

DS3001M-page12 © 2009 Fremont Micro Devices Inc.

24C04A, 24C08A, 24C16A

SOP8 PACKAGE OUTLINE DIMENSIONS

Dimensions In Millimeters Dimensions In Inches

Min Max Min Max

Symbol

A 1.350 1.750 0.053 0.069

A1 0.100 0.250 0.004 0.010

A2 1.350 1.550 0.053 0.061

b 0.330 0.510 0.013 0.020

c 0.170 0.250 0.006 0.010

D 4.700 5.100 0.185 0.200

E 3.800 4.000 0.150 0.157

E1 5.800 6.200 0.228 0.244

e 1.270 (BSC) 0.050 (BSC)

L 0.400 1.270 0.016 0.050

θ 0° 8° 0° 8°

© 2009 Fremont Micro Devices Inc. DS3001M-page13

24C04A, 24C08A, 24C16A

TSSOP8 PACKAGE OUTLINE DIMENSIONS

Dimensions In Millimeters Dimensions In Inches

Symbol

Min Max Min Max

D 2.900 3.100 0.114 0.122

E 4.300 4.500 0.169 0.177

b 0.190 0.300 0.007 0.012

c 0.090 0.200 0.004 0.008

E1 6.250 6.550 0.246 0.258

A 1.100 0.043

A2 0.800 1.000 0.031 0.039

A1 0.020 0.150 0.001 0.006

e 0.65 (BSC) 0.026 (BSC)

L 0.500 0.700 0.020 0.028

H 0.25 (TYP) 0.01 (TYP)

θ 1° 7° 1° 7°

MSOP8 PACKAGE OUTLINE DIMENSIONS

DS3001M-page14 © 2009 Fremont Micro Devices Inc.

24C04A, 24C08A, 24C16A

Dimensions In Millimeters Dimensions In Inches

Symbol Min Max Min Max

A 0.820 1.100 0.320 0.043

A1 0.020 0.150 0.001 0.006

A2 0.750 0.950 0.030 0.037

b 0.250 0.380 0.010 0.015

c 0.090 0.230 0.004 0.009

D 2.900 3.100 0.114 0.122

e 0.65 (BSC) 0.026 (BSC)

E 2.900 3.100 0.114 0.122

E1 4.750 5.050 0.187 0.199

L 0.400 0.800 0.016 0.031

θ 0° 6° 0° 6°

DFN8 PACKAGE OUTLINE DIMENSIONS

© 2009 Fremont Micro Devices Inc. DS3001M-page15

24C04A, 24C08A, 24C16A

Dimensions In Millimeters

Symbol

Min Nom Max

A 0.70 0.75 0.80

A1 - 0.02 0.05

b 0.18 0.25 0.03

c 0.18 0.20 0.25

D 1.90 2.00 2.10

D2 1.50REF

e 0.50BSC

Nd 1.50BSC

E 2.90 3.00 3.10

E2 1.60REF

L 0.30 0.40 0.50

h 0.20 0.25 0.30

L/F Surface Electroplate NIPdAu (Nickel, Pd, Metal)

Dimension(mil) 67*75

DS3001M-page16 © 2009 Fremont Micro Devices Inc.

24C04A, 24C08A, 24C16A

SOT-23-5 PACKAGE OUTLINE DIMENSIONS

Dimensions In Millimeters Dimensions In Inches

Symbol

Min Max Min Max

A 1.050 1.250 0.041 0.049

A1 0.000 0.100 0.000 0.004

A2 1.050 1.150 0.041 0.045

b 0.300 0.500 0.012 0.020

c 0.100 0.200 0.004 0.008

D 2.820 3.020 0.111 0.119

E 1.500 1.700 0.059 0.067

E1 2.650 2.950 0.104 0.116

e 0.95 (BSC) 0.037 (BSC)

e1 1.800 2.000 0.071 0.079

L 0.300 0.600 0.012 0.024

0° 8° 0° 6°

© 2009 Fremont Micro Devices Inc. DS3001M-page17

24C04A, 24C08A, 24C16A

TSOT-23-5 PACKAGE OUTLINE DIMENSIONS

Dimensions In Millimeters Dimensions In Inches

Symbol

Min Max Min Max

A 0.700 0.900 0.028 0.035

A1 0.000 0.100 0.000 0.004

A2 0.700 0.800 0.028 0.031

b 0.350 0.500 0.014 0.020

c 0.080 0.200 0.003 0.008

D 2.820 3.020 0.111 0.119

E 1.600 1.700 0.063 0.067

E1 2.650 2.950 0.104 0.116

e 0.95 (BSC) 0.037 (BSC)

e1 1.90 (BSC) 0.075 (BSC)

L 0.300 0.600 0.012 0.024

0° 8° 0° 8°

DS3001M-page18 © 2009 Fremont Micro Devices Inc.

24C04A, 24C08A, 24C16A

© 2009 Fremont Micro Devices Inc. DS3001M-page19

24C04A, 24C08A, 24C16A

Information furnished is believed to be accurate and reliable. However, Fremont Micro

Devices.,Ltd.(FMD) assumes no responsibility for the consequences of use of such information or for

any infringement of patents of other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent rights of Fremont Micro Devices.,Ltd.(FMD).

Specifications mentioned in this publication are subject to change without notice. This publication

supersedes and replaces all information previously supplied. Fremont Micro Devices.,Ltd.(FMD)

products are not authorized for use as critical components in life support devices or systems without

express written approval of Fremont Micro Devices.,Ltd.(FMD).

The FMD logo is a registered trademark of Fremont Micro Devices.,Ltd.

All other names are the property of their respective owners

©2007Fremont Micro Devices.,Ltd.-All rights reserved

www.fremontmicro.com

DS3001M-page20 © 2009 Fremont Micro Devices Inc.

You might also like

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Fremont Micro Devices, Inc.: FeaturesDocument9 pagesFremont Micro Devices, Inc.: FeaturesNikitaNo ratings yet

- Two-Wire Automotive Temperature Serial EEPROM: FeaturesDocument20 pagesTwo-Wire Automotive Temperature Serial EEPROM: Features강종운No ratings yet

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument22 pagesTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ASergioNo ratings yet

- 2-Wire Serial EEPROM: FeaturesDocument26 pages2-Wire Serial EEPROM: FeaturesLinkyNo ratings yet

- Atmel 752 24c08aDocument13 pagesAtmel 752 24c08aEngin UzunNo ratings yet

- Eeprom 24c08Document15 pagesEeprom 24c08X-traNo ratings yet

- 24C02 24C04 24C08 24C16: Bookly MicroDocument10 pages24C02 24C04 24C08 24C16: Bookly MicroHùng Nguyễn VănNo ratings yet

- Atmel 24C02Document24 pagesAtmel 24C02chichedemorenoNo ratings yet

- 2-Wire Serial EEPROM: FeaturesDocument23 pages2-Wire Serial EEPROM: FeaturesgillupilluNo ratings yet

- 24C64WPDocument15 pages24C64WPaldo_suviNo ratings yet

- 2-Wire Serial Eeprom: FeaturesDocument21 pages2-Wire Serial Eeprom: FeaturesRenato Peñaloza CallaNo ratings yet

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument21 pagesTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64Anordio2No ratings yet

- 2-Wire Serial EEPROM: FeaturesDocument22 pages2-Wire Serial EEPROM: FeaturesNikolay MikolkinNo ratings yet

- 2-Wire Serial EEPROM: FeaturesDocument19 pages2-Wire Serial EEPROM: FeaturesAgustin AndrokaitesNo ratings yet

- AT24C01A/02/04/08/16: FeaturesDocument14 pagesAT24C01A/02/04/08/16: FeaturesVeronica GonzalezNo ratings yet

- Write Protect Pin For Hardware Data ProtectionDocument16 pagesWrite Protect Pin For Hardware Data Protectionisc44242100% (2)

- At24c08 PDFDocument23 pagesAt24c08 PDFVeronicaGonzalezNo ratings yet

- Data SheetDocument15 pagesData Sheetbootas860No ratings yet

- AT24C16BDocument20 pagesAT24C16Blucio perezNo ratings yet

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument22 pagesTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64AmedNo ratings yet

- 24C08 AtmelDocument19 pages24C08 AtmelCarlos Daniel Nery de OliveiraNo ratings yet

- 24 C 32Document19 pages24 C 32teroplasNo ratings yet

- Two-Wire Serial EEPROM: FeaturesDocument28 pagesTwo-Wire Serial EEPROM: FeaturesdobsrdjanNo ratings yet

- 24C02-8 EepromDocument16 pages24C02-8 EepromJesus Almanzar SantosNo ratings yet

- Eeproms 24CXXDocument18 pagesEeproms 24CXXAlberto YepezNo ratings yet

- MR44V100A: General DescriptionDocument19 pagesMR44V100A: General DescriptionseacerNo ratings yet

- ST24 25C04, ST24 25W04Document16 pagesST24 25C04, ST24 25W04Zoran KovacevicNo ratings yet

- Atmel 8568 SEEPROM AT24C256C Datasheet PDFDocument21 pagesAtmel 8568 SEEPROM AT24C256C Datasheet PDFhanifNo ratings yet

- 24C512Document13 pages24C512kimbo23No ratings yet

- Atmel 8766 Seeprom At24cs04 08 Datasheet ATMLH236Document23 pagesAtmel 8766 Seeprom At24cs04 08 Datasheet ATMLH236berrumeNo ratings yet

- Eeprom 24w04Document15 pagesEeprom 24w04davixformusicNo ratings yet

- Hgsemi-At24c02m-Tr C356696 PDFDocument13 pagesHgsemi-At24c02m-Tr C356696 PDFfiras sonomiNo ratings yet

- EEPROM 24C256 - Atmel PDFDocument20 pagesEEPROM 24C256 - Atmel PDFValdir DerlannNo ratings yet

- Atmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetDocument20 pagesAtmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetalaitsevNo ratings yet

- FOR EEPROM DOCUMENTDocument9 pagesFOR EEPROM DOCUMENTIram Loya ValladaresNo ratings yet

- Mikroe 5623-3132216Document32 pagesMikroe 5623-3132216yajujotosNo ratings yet

- SPI Serial Eeprom: FeaturesDocument22 pagesSPI Serial Eeprom: FeaturesHmcc HoangNo ratings yet

- 24 C 04Document15 pages24 C 04roberto caiadoNo ratings yet

- 24 LC 2561Document12 pages24 LC 2561ricardo_MassisNo ratings yet

- At24c02a 04a 08aDocument16 pagesAt24c02a 04a 08aretno.endah ekowatiNo ratings yet

- 24C02Document27 pages24C02Biswajit SarkarNo ratings yet

- 24 LC 64Document12 pages24 LC 64achuthkumarNo ratings yet

- Atmel 24C1024Document19 pagesAtmel 24C1024vax1No ratings yet

- At24c16sc 09etDocument14 pagesAt24c16sc 09etJananrdhana CpNo ratings yet

- AT25080A, 160A, 320A, 640A Rev04Document23 pagesAT25080A, 160A, 320A, 640A Rev04Bobby HancockNo ratings yet

- S 24 Cs 08Document34 pagesS 24 Cs 08mj15015100% (1)

- 2-Wire Serial Eeproms: FeaturesDocument16 pages2-Wire Serial Eeproms: FeaturesTuan Pham AnhNo ratings yet

- 24 LC 02Document13 pages24 LC 02MoshikoRanNo ratings yet

- 24C 04Document15 pages24C 04Diego AsiconaNo ratings yet

- 2-Wire Serial Eeprom: FeaturesDocument2 pages2-Wire Serial Eeprom: Featuresinsomnium86No ratings yet

- 24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsDocument12 pages24Lc04B/08B: 4K/8K 2.5V I C Serial EepromsBoris PopovNo ratings yet

- 3Document10 pages3jovel lanat100% (1)

- Atmel AT250x0 MemoryDocument19 pagesAtmel AT250x0 MemoryNamburi NandanNo ratings yet

- MC14099B 8-Bit Addressable Latches: Marking DiagramsDocument8 pagesMC14099B 8-Bit Addressable Latches: Marking Diagramsgreentea601No ratings yet

- PCF8582C-2: 1. DescriptionDocument21 pagesPCF8582C-2: 1. DescriptionroozbehxoxNo ratings yet

- RM Cycloneiii Dev Kit Host BoardDocument80 pagesRM Cycloneiii Dev Kit Host Boardrıdvan71No ratings yet

- Service Manual: Viewsonic Va1616W-6Document52 pagesService Manual: Viewsonic Va1616W-6rıdvan71No ratings yet

- 8K/16K 5.0V SPI Bus Serial EEPROM: Features Package TypesDocument12 pages8K/16K 5.0V SPI Bus Serial EEPROM: Features Package Typesrıdvan71No ratings yet

- 74LVC14A: 1. General DescriptionDocument18 pages74LVC14A: 1. General Descriptionrıdvan71No ratings yet

- DCCN 3Document68 pagesDCCN 3Nati ZemeteNo ratings yet

- How To Use Click OnceDocument2 pagesHow To Use Click Oncekormhmd33720% (1)

- Beginners Guide To Embedded C Programming EbookDocument3 pagesBeginners Guide To Embedded C Programming Ebooknalinagc0% (1)

- SE6155 C-Bus Technical Selection GuideDocument128 pagesSE6155 C-Bus Technical Selection GuideTrong LeNo ratings yet

- IBM M A S Q R (1.0) : Aximo Utomation Cripts Uick EferenceDocument2 pagesIBM M A S Q R (1.0) : Aximo Utomation Cripts Uick EferenceVishnu VickyNo ratings yet

- 04 - Velocity Control PWM PDFDocument87 pages04 - Velocity Control PWM PDFTonyNo ratings yet

- JSE Market Data and Trading ServicesDocument17 pagesJSE Market Data and Trading ServicesSam GvmxdxNo ratings yet

- FPGA Implementation of A Trained Neural Network: Seema Singh, Shreyashree Sanjeevi, Suma V, Akhil TalashiDocument10 pagesFPGA Implementation of A Trained Neural Network: Seema Singh, Shreyashree Sanjeevi, Suma V, Akhil TalashiHaiNguyenNo ratings yet

- Julia TutorialDocument75 pagesJulia TutorialphieuxuatkhoNo ratings yet

- Pit Viper Control System Training OverviewDocument29 pagesPit Viper Control System Training OverviewMarcos Matias MedinaNo ratings yet

- Timer0 Code ATmega328pDocument3 pagesTimer0 Code ATmega328pmladen divacNo ratings yet

- 122 Audio Amplifier ConstructionDocument57 pages122 Audio Amplifier ConstructionsilviaNo ratings yet

- Rre Ry Ry1 A2a MP014 Pe DD Tel A0 DWG 00146Document1 pageRre Ry Ry1 A2a MP014 Pe DD Tel A0 DWG 00146waz ahmedNo ratings yet

- Project Report On Share A Ride ApplicationDocument33 pagesProject Report On Share A Ride ApplicationRana NiraliNo ratings yet

- Network Automation Cookbook Pdf00016Document5 pagesNetwork Automation Cookbook Pdf00016Dang KhueNo ratings yet

- Android Application Development With Maven - Sample ChapterDocument32 pagesAndroid Application Development With Maven - Sample ChapterPackt PublishingNo ratings yet

- LabVIEW Core 3 2013 - Course ManualDocument135 pagesLabVIEW Core 3 2013 - Course Manualtalaindio100% (2)

- IBM Power Facts and FeaturesDocument19 pagesIBM Power Facts and Featuresivan Dario Correa RestrepoNo ratings yet

- Rational Rose UML DiagramsDocument34 pagesRational Rose UML DiagramsVivy FonNo ratings yet

- DDoS Attack Detection in SDNs Using Improved KNN and Degree of AttackDocument10 pagesDDoS Attack Detection in SDNs Using Improved KNN and Degree of AttackAhmedNo ratings yet

- Geofencing and Background Tracking - The Next Features in LBSDocument15 pagesGeofencing and Background Tracking - The Next Features in LBSRupam PrasadNo ratings yet

- Report Medicine AlertDocument22 pagesReport Medicine Alertkunal0% (2)

- Oracle TimesTen In-Memory Database Error Messages and SNMP Traps, Release 18.1Document444 pagesOracle TimesTen In-Memory Database Error Messages and SNMP Traps, Release 18.1errr33No ratings yet

- NXOpen How To Use A Modeless WinForm and Still Unload Your DLL ImmediatelyDocument2 pagesNXOpen How To Use A Modeless WinForm and Still Unload Your DLL Immediatelysanjayeds100% (1)

- Astable Multivibrator Using TransistorsDocument24 pagesAstable Multivibrator Using TransistorsChalez ZengeretsiNo ratings yet

- ScanTools II User GuideDocument114 pagesScanTools II User Guidecyberget100% (1)

- STM Notes Notes stm32 PDFDocument38 pagesSTM Notes Notes stm32 PDFpriyaNo ratings yet

- Hybrid Material PCB Circuit BoardDocument24 pagesHybrid Material PCB Circuit BoardjackNo ratings yet

- Citect SCADA 6 (1) .10 Modbus Driver HelpDocument28 pagesCitect SCADA 6 (1) .10 Modbus Driver HelpKannan IceNo ratings yet

- Bascom Avr ProgrammingDocument236 pagesBascom Avr Programmingpriyo100% (2)