Professional Documents

Culture Documents

2-Wire Serial Eeprom: Features

Uploaded by

insomnium86Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2-Wire Serial Eeprom: Features

Uploaded by

insomnium86Copyright:

Available Formats

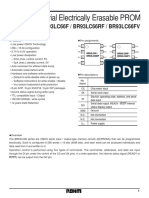

Features

• Low Voltage and Standard Voltage Operation

– 5.0 (VCC = 4.5V to 5.5V)

– 2.7 (VCC = 2.7V to 5.5V)

– 1.8 (VCC = 1.8V to 3.6V)

• Internally Organized 65,536 x 8

• 2-Wire Serial Interface

• Schmitt Triggers, Filtered Inputs for Noise Suppression

• Bidirectional Data Transfer Protocol

• 1 MHz (5V), 400 kHz (2.7V) and 100 kHz (1.8V) Compatibility

•

•

Write Protect Pin for Hardware and Software Data Protection

128-Byte Page Write Mode (Partial Page Writes Allowed)

2-Wire Serial

• Self-Timed Write Cycle (5 ms typical)

• High Reliability EEPROM

– Endurance: 100,000 Write Cycles

– Data Retention: 40 Years 512K (65,536 x 8)

– ESD Protection: > 4000V

• Automotive Grade and Extended Temperature Devices Available

• 8-Pin PDIP and 20-Pin JEDEC SOIC and 8-Pin LAP Packages

AT24C512

Description Preliminary

The AT24C512 provides 524,288 bits of serial electrically erasable and programmable

read only memory (EEPROM) organized as 65,536 words of 8 bits each. The device’s

cascadable feature allows up to 4 devices to share a common 2-wire bus. The device

is optimized for use in many industrial and commercial applications where low-power

and low-voltage operation are essential. The devices are available in space-saving 8-

pin PDIP, 20-pin JEDEC SOIC, and 8-pin Leadless Array (LAP) packages. In addition,

the entire family is available in 5.0V (4.5V to 5.5V), 2.7V (2.7V to 5.5V) and 1.8V (1.8V

to 3.6V) versions.

Pin Configurations

8-Pin PDIP

Pin Name Function

A0 to A1 Address Inputs A0 1 8 VCC

A1 2 7 WP

SDA Serial Data NC 3 6 SCL 2-Wire Serial

GND 4 5 SDA

SCL Serial Clock Input

WP Write Protect

EEPROM 512K

NC No Connect (65,536 x 8)

20-Pin SOIC

A0 1 20 VCC

8-Pin Leadless Array A1 2 19 WP

NC 3 18 NC

VCC 8 1 A0 NC 4 17 NC

WP 7 2 A1 NC 5 16 NC

NC 6 15 NC

SCL 6 3 NC NC 7 14 NC

SDA 5 4 GND NC 8 13 NC

NC 9 12 SCL

Bottom View GND 10 11 SDA

Rev. 1116A–07/98

Note: Please contact Atmel Corporation for more

information on this product. 1

Absolute Maximum Ratings*

Operating Temperature .................................. -55°C to +125°C *NOTICE: Stresses beyond those listed under “Absolute

Maximum Ratings” may cause permanent dam-

Storage Temperature ..................................... -65°C to +150°C age to the device. This is a stress rating only and

functional operation of the device at these or any

Voltage on Any Pin other conditions beyond those indicated in the

with Respect to Ground .....................................-1.0V to +7.0V operational sections of this specification is not

implied. Exposure to absolute maximum rating

Maximum Operating Voltage........................................... 6.25V conditions for extended periods may affect device

reliability.

DC Output Current........................................................ 5.0 mA

Block Diagram

Pin Description

SERIAL CLOCK (SCL): The SCL input is used to positive WRITE PROTECT (WP): The write protect input, when tied

edge clock data into each EEPROM device and negative to GND, allows normal write operations. When WP is tied

edge clock data out of each device. high to VCC, all write operations to the memory are inhib-

SERIAL DATA (SDA): The SDA pin is bidirectional for ited. If left unconnected, WP is internally pulled down to

serial data transfer. This pin is open-drain driven and may GND. Switching WP to VCC prior to a write operation cre-

be wire-ORed with any number of other open-drain or open ates a software write protect function.

collector devices.

DEVICE/PAGE ADDRESSES (A1, A0): The A1 and A0 Memory Organization

pins are device address inputs that are hardwired or left not AT24C512, 512K SERIAL EEPROM: The 512K is inter-

connected for hardware compatibility with AT24C512. nally organized as 512 pages of 128-bytes each. Random

When the pins are hardwired, as many as four 512K word addressing requires a 16-bit data word address.

devices may be addressed on a single bus system (device

addressing is discussed in detail under the Device

Addressing section). When the pins are not hardwired, the

default A1 and A0 are zero.

2 AT24C512

You might also like

- DatasheetDocument12 pagesDatasheetKlan ZangoNo ratings yet

- 2-Wire Serial Eeprom: FeaturesDocument20 pages2-Wire Serial Eeprom: FeaturesAgustin AndrokaitesNo ratings yet

- 2-Wire Serial Eeproms: FeaturesDocument16 pages2-Wire Serial Eeproms: FeaturesTuan Pham AnhNo ratings yet

- 24c1024 Ic DatasheetDocument20 pages24c1024 Ic DatasheetVikas AttardeNo ratings yet

- Two-Wire Serial Eeprom: FeaturesDocument19 pagesTwo-Wire Serial Eeprom: FeaturesVikrant SharmaNo ratings yet

- Two-Wire Serial Eeprom: FeaturesDocument22 pagesTwo-Wire Serial Eeprom: Featureskasiab19859266No ratings yet

- Two-Wire Serial Eeprom: FeaturesDocument19 pagesTwo-Wire Serial Eeprom: Featuresvladimir_p80No ratings yet

- EEPROM 24C256 - Atmel PDFDocument20 pagesEEPROM 24C256 - Atmel PDFValdir DerlannNo ratings yet

- AT24C16BDocument20 pagesAT24C16Blucio perezNo ratings yet

- At24c02a 04a 08aDocument16 pagesAt24c02a 04a 08aretno.endah ekowatiNo ratings yet

- Write Protect Pin For Hardware Data ProtectionDocument16 pagesWrite Protect Pin For Hardware Data Protectionisc44242100% (2)

- 2-Wire Serial EEPROM: FeaturesDocument19 pages2-Wire Serial EEPROM: FeaturesAgustin AndrokaitesNo ratings yet

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument21 pagesTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64Anordio2No ratings yet

- 2-Wire Serial EEPROM: FeaturesDocument22 pages2-Wire Serial EEPROM: FeaturesNikolay MikolkinNo ratings yet

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument22 pagesTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64AmedNo ratings yet

- 2-Wire Serial Eeproms: FeaturesDocument18 pages2-Wire Serial Eeproms: FeaturesAgustin AndrokaitesNo ratings yet

- Low Voltage 2-Wire Serial EEPROM with 16K MemoryDocument11 pagesLow Voltage 2-Wire Serial EEPROM with 16K Memoryjavier venturaNo ratings yet

- 24C08 AtmelDocument19 pages24C08 AtmelCarlos Daniel Nery de OliveiraNo ratings yet

- At 25080Document21 pagesAt 25080sabNo ratings yet

- At24c08 PDFDocument23 pagesAt24c08 PDFVeronicaGonzalezNo ratings yet

- Atmel 8766 Seeprom At24cs04 08 Datasheet ATMLH236Document23 pagesAtmel 8766 Seeprom At24cs04 08 Datasheet ATMLH236berrumeNo ratings yet

- Mikroe 5623-3132216Document32 pagesMikroe 5623-3132216yajujotosNo ratings yet

- Fm24c64a Ds EngDocument22 pagesFm24c64a Ds EngHamza Abbasi AbbasiNo ratings yet

- Atmel 8517 Seeprom At24c01b 02b 04b 08b Auto DatasheetDocument18 pagesAtmel 8517 Seeprom At24c01b 02b 04b 08b Auto DatasheetAlhassan Ahmed OmranNo ratings yet

- AT24C1024B - DatasheetDocument25 pagesAT24C1024B - DatasheetEngin UzunNo ratings yet

- Atmel 752 24c08aDocument13 pagesAtmel 752 24c08aEngin UzunNo ratings yet

- At24c16sc 09etDocument14 pagesAt24c16sc 09etJananrdhana CpNo ratings yet

- Two-Wire Serial EEPROM: FeaturesDocument28 pagesTwo-Wire Serial EEPROM: FeaturesGabriel GodoyNo ratings yet

- Two-Wire Serial EEPROM: FeaturesDocument28 pagesTwo-Wire Serial EEPROM: FeaturesThế TùngNo ratings yet

- AT24C01A/02/04/08/16: FeaturesDocument14 pagesAT24C01A/02/04/08/16: FeaturesVeronica GonzalezNo ratings yet

- AT25080A, 160A, 320A, 640A Rev04Document23 pagesAT25080A, 160A, 320A, 640A Rev04Bobby HancockNo ratings yet

- Atmlh034 Atmel PDFDocument12 pagesAtmlh034 Atmel PDFAlexander RinconNo ratings yet

- 24C02BN Su18Document26 pages24C02BN Su18Dwp BhaskaranNo ratings yet

- FM24C04D 2-Wire Serial EEPROM Data SheetDocument28 pagesFM24C04D 2-Wire Serial EEPROM Data SheetJuan Daniel Angeles AnguloNo ratings yet

- Two-Wire Serial EEPROM: FeaturesDocument12 pagesTwo-Wire Serial EEPROM: Featuresssrao2211No ratings yet

- Features: Two-Wire Serial Electrically Erasable and Programmable Read-Only MemoryDocument23 pagesFeatures: Two-Wire Serial Electrically Erasable and Programmable Read-Only MemoryLi JamesNo ratings yet

- FM24C02A Ds EngDocument20 pagesFM24C02A Ds EngJacques YuitNo ratings yet

- At25f512a 844895Document19 pagesAt25f512a 844895mirage0706No ratings yet

- 2-Wire Serial Eeprom: FeaturesDocument11 pages2-Wire Serial Eeprom: FeaturesRomel Ranin CalangNo ratings yet

- 2-Wire Serial Eeprom: FeaturesDocument10 pages2-Wire Serial Eeprom: FeaturesPablo Diego Cecere CasadoNo ratings yet

- Datasheet 24c01 EepromDocument26 pagesDatasheet 24c01 EepromItalo Vasquez LeonNo ratings yet

- 3-Wire Serial Eeproms: FeaturesDocument18 pages3-Wire Serial Eeproms: FeaturesAriana ScheiderNo ratings yet

- Three-Wire Serial Eeprom: FeaturesDocument21 pagesThree-Wire Serial Eeprom: FeaturesАлександр СаральповNo ratings yet

- 24C512Document13 pages24C512kimbo23No ratings yet

- At Melee Prom DatasheetDocument26 pagesAt Melee Prom Datasheetlodde2No ratings yet

- A. Atmel ProductsDocument16 pagesA. Atmel ProductsJuan Jose MendozaNo ratings yet

- Atmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetDocument20 pagesAtmel 5082 Seeprom At25080a 160a 320a 640a Auto DatasheetalaitsevNo ratings yet

- Eeproms 24CXXDocument18 pagesEeproms 24CXXAlberto YepezNo ratings yet

- Atmel 24c02 PDFDocument30 pagesAtmel 24c02 PDFMAX GNo ratings yet

- SPI Serial Eeproms: FeaturesDocument15 pagesSPI Serial Eeproms: FeaturesMarcus SilvaNo ratings yet

- SPI Serial Memory: FeaturesDocument17 pagesSPI Serial Memory: Featuresyuni supriatinNo ratings yet

- 1K 5.0V I C™ Serial EEPROM: Features: DescriptionDocument36 pages1K 5.0V I C™ Serial EEPROM: Features: DescriptionDanna PerezNo ratings yet

- 2-Wire Serial EEPROM Smart Card Module: FeaturesDocument12 pages2-Wire Serial EEPROM Smart Card Module: FeaturesMaikol DominguezNo ratings yet

- AT24C02Document20 pagesAT24C02Kenys VillenaNo ratings yet

- Two-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ADocument22 pagesTwo-Wire Serial EEPROM 32K (4096 X 8) 64K (8192 X 8) AT24C32A AT24C64ASergioNo ratings yet

- Two-Wire Serial EEPROM: FeaturesDocument28 pagesTwo-Wire Serial EEPROM: FeaturesdobsrdjanNo ratings yet

- 24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMDocument34 pages24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMKhalid BenaribaNo ratings yet

- At25128b 5eb PDFDocument22 pagesAt25128b 5eb PDFMurat BaybükeNo ratings yet

- Atmel 8568 SEEPROM AT24C256C Datasheet PDFDocument21 pagesAtmel 8568 SEEPROM AT24C256C Datasheet PDFhanifNo ratings yet

- Nonvolatile Memory 8-Kbit E Prom With C Bus Interface SDA 2586-5Document12 pagesNonvolatile Memory 8-Kbit E Prom With C Bus Interface SDA 2586-5insomnium86No ratings yet

- FM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- FM93C86A 16K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C86A 16K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- NM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- NM93CS66 (MICROWIRE™ Bus Interface) 4096-Bit Serial EEPROM With Data Protect and Sequential ReadDocument16 pagesNM93CS66 (MICROWIRE™ Bus Interface) 4096-Bit Serial EEPROM With Data Protect and Sequential Readinsomnium86No ratings yet

- HT93LC56: 2K 3-Wire CMOS Serial EEPROMDocument10 pagesHT93LC56: 2K 3-Wire CMOS Serial EEPROMinsomnium86No ratings yet

- NM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- 93LC66A/B: 4K 2.5V Microwire Serial EEPROMDocument12 pages93LC66A/B: 4K 2.5V Microwire Serial EEPROMinsomnium86No ratings yet

- SPI Serial Eeproms: FeaturesDocument16 pagesSPI Serial Eeproms: FeaturesBachi403No ratings yet

- 1K 5.0V Microwire Serial EEPROM: Features Block DiagramDocument12 pages1K 5.0V Microwire Serial EEPROM: Features Block Diagraminsomnium86No ratings yet

- FM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- HT93LC56: 2K 3-Wire CMOS Serial EEPROMDocument10 pagesHT93LC56: 2K 3-Wire CMOS Serial EEPROMinsomnium86No ratings yet

- 2,048-Bit Serial Electrically Erasable PROM: BR93LC56 / BR93LC56F / BR93LC56RF / BR93LC56FVDocument12 pages2,048-Bit Serial Electrically Erasable PROM: BR93LC56 / BR93LC56F / BR93LC56RF / BR93LC56FVinsomnium86No ratings yet

- Interfacing The X24C44-45Document4 pagesInterfacing The X24C44-45insomnium86No ratings yet

- 93c56 DatasheetDocument15 pages93c56 DatasheetsakerhetfreakNo ratings yet

- 32K 2.5V I C Serial EEPROM: Features Package TypesDocument12 pages32K 2.5V I C Serial EEPROM: Features Package Typesinsomnium86No ratings yet

- 93LC66A/B: 4K 2.5V Microwire Serial EEPROMDocument12 pages93LC66A/B: 4K 2.5V Microwire Serial EEPROMinsomnium86No ratings yet

- 25AA080/25LC080/25C080: 8K Spi Bus Serial EEPROMDocument16 pages25AA080/25LC080/25C080: 8K Spi Bus Serial EEPROMinsomnium86No ratings yet

- Memory ICs Guide to 4,096-Bit Serial EEPROM BR93LC66Document12 pagesMemory ICs Guide to 4,096-Bit Serial EEPROM BR93LC66insomnium86No ratings yet

- 25AA640/25LC640: 64K Spi Bus Serial EEPROMDocument12 pages25AA640/25LC640: 64K Spi Bus Serial EEPROMinsomnium86No ratings yet

- Application Note An-00160: Considerations For Sending Data With The HP SeriesDocument6 pagesApplication Note An-00160: Considerations For Sending Data With The HP Seriesinsomnium86No ratings yet

- FM Tranciever AppsDocument7 pagesFM Tranciever Appsinsomnium86No ratings yet

- Application Note An-00100: RF 101 Information For The RF ChallengedDocument5 pagesApplication Note An-00100: RF 101 Information For The RF Challengedinsomnium86No ratings yet

- FM Tranceiver DataDocument9 pagesFM Tranceiver Datainsomnium86No ratings yet

- FMT M - Fmtx1-Xxxx: Ransmitter OdulesDocument6 pagesFMT M - Fmtx1-Xxxx: Ransmitter Odulesinsomnium86No ratings yet

- 32K 5.0V I C Serial EEPROM: Features Package TypesDocument12 pages32K 5.0V I C Serial EEPROM: Features Package Typesinsomnium86No ratings yet

- Application Note An-00500: Antennas: Design, Application, PerformanceDocument7 pagesApplication Note An-00500: Antennas: Design, Application, PerformanceAnonymous 0qYv7WpgNo ratings yet

- Product Technical Data: 418Mhz Am Miniature Transmitter Module (Micro TX) Nv08JDocument4 pagesProduct Technical Data: 418Mhz Am Miniature Transmitter Module (Micro TX) Nv08Jinsomnium86No ratings yet

- Ness Lux Wired Pir With Nightlight: REV1.1 LUX Hardwired - Installation NotesDocument8 pagesNess Lux Wired Pir With Nightlight: REV1.1 LUX Hardwired - Installation NotesTimNo ratings yet

- Schneider NS MCCBDocument42 pagesSchneider NS MCCBEnder Ali Leon Valero100% (1)

- 8085 Programming Examples - CollegeekDocument6 pages8085 Programming Examples - CollegeekH Aries OñaNo ratings yet

- GV58VSseries Configuration and Instructions Ver1.0-20190515Document1 pageGV58VSseries Configuration and Instructions Ver1.0-20190515الحسين اومارير67% (3)

- Net Metering SopDocument14 pagesNet Metering Sopamad khanNo ratings yet

- Pepperl and Fuchs 1.51 Zeneer Barrier 2Document4 pagesPepperl and Fuchs 1.51 Zeneer Barrier 2Cost RootsNo ratings yet

- Vacon NX Products For Common DC Bus SystemsDocument20 pagesVacon NX Products For Common DC Bus SystemsSilvian IonescuNo ratings yet

- Alia AUF760 Ultrasonic Flange FlowmeterDocument4 pagesAlia AUF760 Ultrasonic Flange FlowmeterRexCrazyMindNo ratings yet

- Section 55 - Electrical Systems - Chapter 11Document60 pagesSection 55 - Electrical Systems - Chapter 11احمد الشبراوى الشبراوىNo ratings yet

- TLE IA Learning Activity SheetsDocument4 pagesTLE IA Learning Activity SheetsMichael Edward De VillaNo ratings yet

- Kaycee Industries Limited: Price ListDocument39 pagesKaycee Industries Limited: Price ListVlady Lopez CastroNo ratings yet

- Station Erection 1stDocument2 pagesStation Erection 1stPRADEEP basannavarNo ratings yet

- NJM11100 E-1917008Document21 pagesNJM11100 E-1917008Rafael BrunoNo ratings yet

- Topik 2 - DiodesDocument61 pagesTopik 2 - DiodesfaizahNo ratings yet

- GROUNDING SYSTEMS UNDER 40 CHARACTERSDocument5 pagesGROUNDING SYSTEMS UNDER 40 CHARACTERSAfzal Asif100% (2)

- TV Deflection TubesDocument2 pagesTV Deflection Tubesdavid reyesNo ratings yet

- Ordering Spare PartsDocument5 pagesOrdering Spare PartsPeryna WstydNo ratings yet

- Mobile device component diagramDocument35 pagesMobile device component diagramStefanus NgodhuNo ratings yet

- Instruction Manual: Installation Operation Maintenance Voltage RegulatorDocument21 pagesInstruction Manual: Installation Operation Maintenance Voltage RegulatorWahyu DiyonoNo ratings yet

- The Role of The Via: Home Defining The Via Types For Use With Your Board in Altium DesignerDocument5 pagesThe Role of The Via: Home Defining The Via Types For Use With Your Board in Altium DesignerBenyamin Farzaneh AghajarieNo ratings yet

- Electrical Safety Course ModuleDocument4 pagesElectrical Safety Course ModuleRaman GuptaNo ratings yet

- Palmtop Size Variable DC Power Supply: SeriesDocument8 pagesPalmtop Size Variable DC Power Supply: SeriesVăn Lê100% (1)

- ATV-S07-SS06-Air Controlled Suspension (ACS) - Shop Manual - OUT-REN - Version 5AA - ENDocument23 pagesATV-S07-SS06-Air Controlled Suspension (ACS) - Shop Manual - OUT-REN - Version 5AA - ENJakub TubekNo ratings yet

- VK Y CT PDFDocument6 pagesVK Y CT PDFMD. Mazidul Islam MahfujNo ratings yet

- 12 Direct SensingDocument3 pages12 Direct SensingPooja MehraNo ratings yet

- Cable Gland Selection GuideDocument4 pagesCable Gland Selection GuideJomy GeorgeNo ratings yet

- Haier Biomedical Constant Temperature Transport CoolerDocument2 pagesHaier Biomedical Constant Temperature Transport CoolerMandalika Putri PratamaNo ratings yet

- Crystal Slant CabinetDocument32 pagesCrystal Slant Cabinet張斯朗No ratings yet

- HPPA Data SheetDocument8 pagesHPPA Data SheetFredy CabrejoNo ratings yet

- GP106 Memory Test Reveals Bit ErrorsDocument3 pagesGP106 Memory Test Reveals Bit ErrorsKavinda Jayasinghege DonNo ratings yet