Professional Documents

Culture Documents

1K 5.0V Microwire Serial EEPROM: Features Block Diagram

Uploaded by

insomnium86Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

1K 5.0V Microwire Serial EEPROM: Features Block Diagram

Uploaded by

insomnium86Copyright:

Available Formats

M 93C46B

1K 5.0V Microwire Serial EEPROM

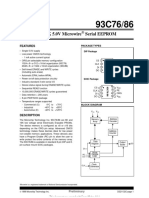

FEATURES BLOCK DIAGRAM

• Single supply 5.0V operation

• Low power CMOS technology MEMORY ADDRESS

ARRAY DECODER

- 1 mA active current (typical)

- 1 µA standby current (maximum)

• 64 x 16 bit organization

ADDRESS

• Self-timed ERASE and WRITE cycles (including COUNTER

auto-erase)

• Automatic ERAL before WRAL DATA OUTPUT

REGISTER DO

• Power on/off data protection circuitry BUFFER

• Industry standard 3-wire serial interface DI

• Device status signal during ERASE/WRITE cycles MEMORY

• Sequential READ function DECODE

CS LOGIC

• 1,000,000 E/W cycles guaranteed

• Data retention > 200 years VCC

CLK CLOCK

• 8-pin PDIP/SOIC and 8-pin TSSOP packages GENERATOR VSS

• Available for the following temperature ranges:

- Commercial (C): 0°C to +70°C

- Industrial (I): -40°C to +85°C DESCRIPTION

- Automotive (E): -40°C to +125°C

The Microchip Technology Inc. 93C46B is a 1K-bit,

low-voltage serial Electrically Erasable PROM. The

device memory is configured as 64 x 16 bits. Advanced

CMOS technology makes this device ideal for

low-power, nonvolatile memory applications. The

93C46B is available in standard 8-pin DIP, surface

mount SOIC, and TSSOP packages. The 93C46BX are

only offered in a 150 mil SOIC package.

PACKAGE TYPE

DIP SOIC SOIC TSSOP

CS 1 8 VCC CS 1 8 VCC

93C46B

CS 1 8 VCC NU 1 8 NC CLK 2 7 NC

93C46BX

6

93C46B

DI 3 NC

93C46B

CLK 2 7 NC

2 7 NC VCC 2 7 VSS DO 4 5 VSS

CLK

DI 3 6 NC

DI 3 6 NC CS 3 6 DO

DO 4 5 VSS

DO 4 5 VSS CLK 4 5 DI

Microwire is a registered trademark of National Semiconductor Incorporated.

1997 Microchip Technology Inc. Preliminary DS21172D-page 1

93C46B

1.0 ELECTRICAL TABLE 1-1 PIN FUNCTION TABLE

CHARACTERISTICS Name Function

1.1 Maximum Ratings* CS Chip Select

VCC...................................................................................7.0V CLK Serial Data Clock

All inputs and outputs w.r.t. VSS ...............-0.6V to VCC +1.0V DI Serial Data Input

Storage temperature .....................................-65°C to +150°C

DO Serial Data Output

Ambient temp. with power applied.................-65°C to +125°C

Soldering temperature of leads (10 seconds) ............. +300°C VSS Ground

ESD protection on all pins................................................4 kV NC No Connect

*Notice: Stresses above those listed under “Maximum ratings” may VCC Power Supply

cause permanent damage to the device. This is a stress rating only and

functional operation of the device at those or any other conditions

above those indicated in the operational listings of this specification is

not implied. Exposure to maximum rating conditions for extended peri-

ods may affect device reliability.

TABLE 1-2 DC AND AC ELECTRICAL CHARACTERISTICS

All parameters apply over the Commercial (C) VCC = +4.5V to +5.5V Tamb = 0°C to +70°C

specified operating ranges Industrial (I) VCC = +4.5V to +5.5V Tamb = -40°C to +85°C

unless otherwise noted Automotive (E) VCC = +4.5V to +5.5V Tamb = -40°C to +125°C

Parameter Symbol Min. Max. Units Conditions

High level input voltage VIH 2.0 VCC +1 V (Note 2)

Low level input voltage VIL -0.3 0.8 V

Low level output voltage VOL — 0.4 V IOL = 2.1 mA; VCC = 4.5V

High level output voltage VOH 2.4 — V IOH = -400 µA; VCC = 4.5V

Input leakage current ILI -10 10 µA VIN = VSS to VCC

Output leakage current ILO -10 10 µA VOUT = VSS to VCC

Pin capacitance VIN/VOUT = 0 V (Notes 1 & 2)

CIN, COUT — 7 pF

(all inputs/outputs) Tamb = +25°C, FCLK = 1 MHz

ICC read — 1 mA

Operating current ICC write — 1.5 mA

Standby current ICCS — 1 µA CS = VSS

Clock frequency FCLK — 2 MHz VCC = 4.5V

Clock high time TCKH 250 — ns

Clock low time TCKL 250 — ns

Chip select setup time TCSS 50 — ns Relative to CLK

Chip select hold time TCSH 0 — ns Relative to CLK

Chip select low time TCSL 250 — ns

Data input setup time TDIS 100 — ns Relative to CLK

Data input hold time TDIH 100 — ns Relative to CLK

Data output delay time TPD — 400 ns CL = 100 pF

Data output disable time TCZ — 100 ns CL = 100 pF (Note 2)

Status valid time TSV — 500 ns CL = 100 pF

TWC — 2 ms ERASE/WRITE mode

Program cycle time TEC — 6 ms ERAL mode

TWL — 15 ms WRAL mode

Endurance — 1M — cycles 25°C, VCC = 5.0V, Block Mode (Note 3)

Note 1: This parameter is tested at Tamb = 25°C and FCLK = 1 MHz.

2: This parameter is periodically sampled and not 100% tested.

3: This application is not tested but guaranteed by characterization. For endurance estimates in a specific appli-

cation, please consult the Total Endurance Model which may be obtained on Microchip’s BBS or website.

DS21172D-page 2 Preliminary 1997 Microchip Technology Inc.

93C46B

2.0 PIN DESCRIPTION After detecting a START condition, the specified num-

ber of clock cycles (respectively low to high transitions

2.1 Chip Select (CS) of CLK) must be provided. These clock cycles are

required to clock in all required opcodes, addresses,

A high level selects the device; a low level deselects the and data bits before an instruction is executed

device and forces it into standby mode. However, a pro- (Table 2-1). CLK and DI then become don't care inputs

gramming cycle which is already in progress will be waiting for a new START condition to be detected.

completed, regardless of the Chip Select (CS) input

signal. If CS is brought low during a program cycle, the Note: CS must go low between consecutive

device will go into standby mode as soon as the pro- instructions.

gramming cycle is completed.

2.3 Data In (DI)

CS must be low for 250 ns minimum (TCSL) between

consecutive instructions. If CS is low, the internal con- Data In (DI) is used to clock in a START bit, opcode,

trol logic is held in a RESET status. address, and data synchronously with the CLK input.

2.2 Serial Clock (CLK) 2.4 Data Out (DO)

The Serial Clock (CLK) is used to synchronize the com- Data Out (DO) is used in the READ mode to output data

munication between a master device and the 93C46B. synchronously with the CLK input (TPD after the posi-

Opcodes, addresses, and data bits are clocked in on tive edge of CLK).

the positive edge of CLK. Data bits are also clocked out This pin also provides READY/BUSY status information

on the positive edge of CLK. during ERASE and WRITE cycles. READY/BUSY sta-

CLK can be stopped anywhere in the transmission tus information is available on the DO pin if CS is

sequence (at high or low level) and can be continued brought high after being low for minimum chip select

anytime with respect to clock high time (TCKH) and low time (TCSL) and an ERASE or WRITE operation has

clock low time (TCKL). This gives the controlling master been initiated.

freedom in preparing the opcode, address, and data. The status signal is not available on DO, if CS is held

CLK is a “Don't Care” if CS is low (device deselected). low during the entire ERASE or WRITE cycle. In this

If CS is high, but START condition has not been case, DO is in the HIGH-Z mode. If status is checked

detected, any number of clock cycles can be received after the ERASE/WRITE cycle, the data line will be high

by the device, without changing its status (i.e., waiting to indicate the device is ready.

for a START condition).

CLK cycles are not required during the self-timed

WRITE (i.e., auto ERASE/WRITE) cycle.

TABLE 2-1 INSTRUCTION SET FOR 93C46B

Instruction SB Opcode Address Data In Data Out Req. CLK Cycles

ERASE 1 11 A5 A4 A3 A2 A1 A0 — (RDY/BSY) 9

ERAL 1 00 1 0 X X X X — (RDY/BSY) 9

EWDS 1 00 0 0 X X X X — HIGH-Z 9

EWEN 1 00 1 1 X X X X — HIGH-Z 9

READ 1 10 A5 A4 A3 A2 A1 A0 — D15 - D0 25

WRITE 1 01 A5 A4 A3 A2 A1 A0 D15 - D0 (RDY/BSY) 25

WRAL 1 00 0 1 X X X X D15 - D0 (RDY/BSY) 25

1997 Microchip Technology Inc. Preliminary DS21172D-page 3

93C46B

3.0 FUNCTIONAL DESCRIPTION 3.2 Data In (DI) and Data Out (DO)

Instructions, addresses and write data are clocked into It is possible to connect the Data In (DI)and Data Out

the DI pin on the rising edge of the clock (CLK). The DO (DO) pins together. However, with this configuration, if

pin is normally held in a HIGH-Z state except when A0 is a logic-high level, it is possible for a “bus conflict”

reading data from the device, or when checking the to occur during the “dummy zero” that precedes the

READY/BUSY status during a programming operation. READ operation. Under such a condition, the voltage

The READY/BUSY status can be verified during an level seen at DO is undefined and will depend upon the

ERASE/WRITE operation by polling the DO pin; DO relative impedances of DO and the signal source driv-

low indicates that programming is still in progress, while ing A0. The higher the current sourcing capability of A0,

DO high indicates the device is ready. The DO will enter the higher the voltage at the DO pin.

the HIGH-Z state on the falling edge of the CS.

3.3 Data Protection

3.1 START Condition

During power-up, all programming modes of operation

The START bit is detected by the device if CS and DI are inhibited until Vcc has reached a level greater than

are both high with respect to the positive edge of CLK 3.8V. During power-down, the source data protection

for the first time. circuitry acts to inhibit all programming modes when

Before a START condition is detected, CS, CLK, and DI Vcc has fallen below 3.8V at nominal conditions.

may change in any combination (except to that of a The ERASE/SRITE Disable (EWDS) and ERASE/

START condition), without resulting in any device oper- WRITE Enable (EWEN) commands give additional pro-

ation (ERASE, ERAL, EWDS, EWEN, READ, WRITE, tection against accidental programming during normal

and WRAL). As soon as CS is high, the device is no operation.

longer in the standby mode.

After power-up, the device is automatically in the

An instruction following a START condition will only be EWDS mode. Therefore, an EWEN instruction must be

executed if the required amount of opcodes, performed before any ERASE or WRITE instruction can

addresses, and data bits for any particular instruction is be executed.

clocked in.

After execution of an instruction (i.e., clock in or out of

the last required address or data bit) CLK and DI

become don't care bits until a new START condition is

detected.

FIGURE 3-1: SYNCHRONOUS DATA TIMING

VIH

CS

VIL TCSS TCKH TCKL

TCSH

VIH

CLK

VIL

TDIS TDIH

VIH

DI

VIL

TCZ

TPD

TPD

VOH

DO

(READ) TCZ

VOL

TSV

DO VOH

(PROGRAM) STATUS VALID

VOL

Note: AC test conditions: VIL = 0.4V, VIH = 2.4V

DS21172D-page 4 Preliminary 1997 Microchip Technology Inc.

93C46B

3.4 ERASE 3.5 Erase All (ERAL)

The ERASE instruction forces all data bits of the spec- The Erase All (ERAL) instruction will erase the entire

ified address to the logical “1” state. This cycle begins memory array to the logical “1” state. The ERAL cycle

on the rising clock edge of the last address bit. is identical to the ERASE cycle, except for the different

The DO pin indicates the READY/BUSY status of the opcode. The ERAL cycle is completely self-timed and

device if CS is brought high after a minimum of 250 ns commences at the rising clock edge of the last address

low (TCSL). DO at logical “0” indicates that program- bit. Clocking of the CLK pin is not necessary after the

ming is still in progress. DO at logical “1” indicates that device has entered the ERAL cycle.

the register at the specified address has been erased The DO pin indicates the READY/BUSY status of the

and the device is ready for another instruction. device, if CS is brought high after a minimum of 250 ns

low (TCSL) and before the entire ERAL cycle is

complete.

FIGURE 3-2: ERASE TIMING

TCSL

CS

CHECK STATUS

CLK

DI 1 1 1 AN AN-1 AN-2 ••• A0

TSV TCZ

HIGH-Z

DO BUSY READY

HIGH-Z

TWC

FIGURE 3-3: ERAL TIMING

TCSL

CS

CHECK STATUS

CLK

DI 1 0 0 1 0 X ••• X

TSV TCZ

HIGH-Z

DO BUSY READY

HIGH-Z

TEC

1997 Microchip Technology Inc. Preliminary DS21172D-page 5

93C46B

3.6 ERASE/WRITE Disable and Enable 3.7 READ

(EWDS/EWEN)

The READ instruction outputs the serial data of the

The device powers up in the ERASE/WRITE Disable addressed memory location on the DO pin. A dummy

(EWDS) state. All programming modes must be pre- zero bit precedes the 16-bit output string. The output

ceded by an Erase/Write Enable (EWEN) instruction. data bits will toggle on the rising edge of the CLK and

Once the EWEN instruction is executed, programming are stable after the specified time delay (TPD). Sequen-

remains enabled until an EWDS instruction is executed tial read is possible when CS is held high. The memory

or Vcc is removed from the device. To protect against data will automatically cycle to the next register and

accidental data disturbance, the EWDS instruction can output sequentially.

be used to disable all ERASE/WRITE functions and

should follow all programming operations. Execution of

a READ instruction is independent of both the EWDS

and EWEN instructions.

FIGURE 3-4: EWDS TIMING

TCSL

CS

CLK

DI 1 0 0 0 0 X ••• X

FIGURE 3-5: EWEN TIMING

TCSL

CS

CLK

1 0 0 1 1 X ••• X

DI

FIGURE 3-6: READ TIMING

CS

CLK

DI 1 1 0 An ••• A0

HIGH-Z

DO 0 Dx ••• D0 Dx ••• D0 Dx ••• D0

DS21172D-page 6 Preliminary 1997 Microchip Technology Inc.

93C46B

3.8 WRITE 3.9 Write All (WRAL)

The WRITE instruction is followed by 16 bits of data, The Write All (WRAL) instruction will write the entire

which are written into the specified address. After the memory array with the data specified in the command.

last data bit is clocked into the DI pin, the self-timed The WRAL cycle is completely self-timed and com-

auto-erase and programming cycle begins. mences at the rising clock edge of the last data bit.

The DO pin indicates the READY/BUSY status of the Clocking of the CLK pin is not necessary after the

device, if CS is brought high after a minimum of 250 ns device has entered the WRAL cycle. The WRAL com-

low (TCSL) and before the entire write cycle is complete. mand does include an automatic ERAL cycle for the

DO at logical “0” indicates that programming is still in device. Therefore, the WRAL instruction does not

progress. DO at logical “1” indicates that the register at require an ERAL instruction, but the chip must be in the

the specified address has been written with the data EWEN status.

specified and the device is ready for another instruc- The DO pin indicates the READY/BUSY status of the

tion. device if CS is brought high after a minimum of 250 ns

low (TCSL).

FIGURE 3-7: WRITE TIMING

TCSL

CS

CLK

DI 1 0 1 An ••• A0 Dx ••• D0

TSV TCZ

HIGH-Z

DO BUSY READY

HIGH-Z

Twc

FIGURE 3-8: WRAL TIMING

TCSL

CS

CLK

DI 1 0 0 0 1 X ••• X Dx ••• D0

TSV TCZ

HIGH-Z

DO BUSY READY

HIGH-Z

TWL

1997 Microchip Technology Inc. Preliminary DS21172D-page 7

93C46B

NOTES:

DS21172D-page 8 Preliminary 1997 Microchip Technology Inc.

93C46B

NOTES:

1997 Microchip Technology Inc. Preliminary DS21172D-page 9

93C46B

NOTES:

DS21172D-page 10 Preliminary 1997 Microchip Technology Inc.

93C46B

93C46B PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

93C46B — /P

P = Plastic DIP (300 mil Body), 8-lead

SN = Plastic SOIC (150 mil Body), 8-lead

Package:

SM = Plastic SOIC (208 mil Body), 8-lead

ST = TSSOP, 8-lead

Blank = 0 °C to +70°C

Temperature

I = -40°C to +85°C

Range:

E = -40°C to +125°C

Device: 93C46B = 1K Microwire Serial EEPROM

93C46BT = 1K Microwire Serial EEPROM Tape and Reel

93C46BX = 1K Microwire Serial EEPROM in alternate pinout

(SN only)

93C46BXT = 1K Microwire Serial EEPROM in alternate pinout,

Tape and Reel (SN only)

Sales and Support

Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-

mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office.

2. The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277.

3. The Microchip’s Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).

1997 Microchip Technology Inc. Preliminary DS21172D-page 11

WORLDWIDE SALES & SERVICE

AMERICAS ASIA/PACIFIC EUROPE

Corporate Office Hong Kong United Kingdom

Microchip Technology Inc. Microchip Asia Pacific Arizona Microchip Technology Ltd.

2355 West Chandler Blvd. RM 3801B, Tower Two Unit 6, The Courtyard

Chandler, AZ 85224-6199 Metroplaza Meadow Bank, Furlong Road

Tel: 602-786-7200 Fax: 602-786-7277 223 Hing Fong Road Bourne End, Buckinghamshire SL8 5AJ

Technical Support: 602 786-7627 Kwai Fong, N.T., Hong Kong Tel: 44-1628-851077 Fax: 44-1628-850259

Web: http://www.microchip.com Tel: 852-2-401-1200 Fax: 852-2-401-3431 France

Atlanta India Arizona Microchip Technology SARL

Microchip Technology Inc. Microchip Technology India Zone Industrielle de la Bonde

500 Sugar Mill Road, Suite 200B No. 6, Legacy, Convent Road 2 Rue du Buisson aux Fraises

Atlanta, GA 30350 Bangalore 560 025, India 91300 Massy, France

Tel: 770-640-0034 Fax: 770-640-0307 Tel: 91-80-229-0061 Fax: 91-80-229-0062 Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Boston Korea Germany

Microchip Technology Inc. Microchip Technology Korea Arizona Microchip Technology GmbH

5 Mount Royal Avenue 168-1, Youngbo Bldg. 3 Floor Gustav-Heinemann-Ring 125

Marlborough, MA 01752 Samsung-Dong, Kangnam-Ku D-81739 Müchen, Germany

Tel: 508-480-9990 Fax: 508-480-8575 Seoul, Korea Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

Chicago Tel: 82-2-554-7200 Fax: 82-2-558-5934 Italy

Microchip Technology Inc. Shanghai Arizona Microchip Technology SRL

333 Pierce Road, Suite 180 Microchip Technology Centro Direzionale Colleone

Itasca, IL 60143 RM 406 Shanghai Golden Bridge Bldg. Palazzo Taurus 1 V. Le Colleoni 1

Tel: 630-285-0071 Fax: 630-285-0075 2077 Yan’an Road West, Hongiao District 20041 Agrate Brianza

Dallas Shanghai, PRC 200335 Milan, Italy

Tel: 86-21-6275-5700 Tel: 39-39-6899939 Fax: 39-39-6899883

Microchip Technology Inc.

Fax: 86 21-6275-5060

14651 Dallas Parkway, Suite 816

Dallas, TX 75240-8809 Singapore

Tel: 972-991-7177 Fax: 972-991-8588 Microchip Technology Taiwan

JAPAN

Singapore Branch Microchip Technology Intl. Inc.

Dayton Benex S-1 6F

200 Middle Road

Microchip Technology Inc. 3-18-20, Shin Yokohama

#10-03 Prime Centre

Two Prestige Place, Suite 150 Kohoku-Ku, Yokohama

Singapore 188980

Miamisburg, OH 45342 Kanagawa 222 Japan

Tel: 65-334-8870 Fax: 65-334-8850

Tel: 937-291-1654 Fax: 937-291-9175 Tel: 81-4-5471- 6166 Fax: 81-4-5471-6122

Taiwan, R.O.C

Los Angeles

Microchip Technology Taiwan 5/8/97

Microchip Technology Inc.

10F-1C 207

18201 Von Karman, Suite 1090

Tung Hua North Road

Irvine, CA 92612

Taipei, Taiwan, ROC

Tel: 714-263-1888 Fax: 714-263-1338

Tel: 886 2-717-7175 Fax: 886-2-545-0139

New York

Microchip Technology Inc.

150 Motor Parkway, Suite 416

Hauppauge, NY 11788

Tel: 516-273-5305 Fax: 516-273-5335

San Jose

Microchip Technology Inc.

2107 North First Street, Suite 590

San Jose, CA 95131

Tel: 408-436-7950 Fax: 408-436-7955

Toronto

Microchip Technology Inc.

5925 Airport Road, Suite 200

M

Mississauga, Ontario L4V 1W1, Canada

Tel: 905-405-6279 Fax: 905-405-6253

All rights reserved. © 1997, Microchip Technology Incorporated, USA. 6/97

Printed on recycled paper.

Information contained in this publication regarding device applications and the like is intended for suggestion only and may be superseded by updates. No representation or

warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other

intellectual property rights arising from such use or otherwise. Use of Microchip’s products as critical components in life support systems is not authorized except with express

written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights. The Microchip logo and name are registered trademarks

of Microchip Technology Inc. in the U.S.A. and other countries. All rights reserved. All other trademarks mentioned herein are the property of their respective companies.

DS21172D-page 12 Preliminary 1997 Microchip Technology Inc.

You might also like

- 93 LC 46 BDocument12 pages93 LC 46 Bwabp_23No ratings yet

- Data SheetDocument12 pagesData SheetPrasetyo Muhammad SaktiNo ratings yet

- 93LC66A/B: 4K 2.5V Microwire Serial EEPROMDocument12 pages93LC66A/B: 4K 2.5V Microwire Serial EEPROMinsomnium86No ratings yet

- 2K 5.0V Automotive Temperature Microwire Serial EEPROM: Features Package TypeDocument12 pages2K 5.0V Automotive Temperature Microwire Serial EEPROM: Features Package TypeDanielNo ratings yet

- 256 Bit/1K 5.0V CMOS Serial EEPROM: Features Package TypeDocument8 pages256 Bit/1K 5.0V CMOS Serial EEPROM: Features Package TypeAgustin AndrokaitesNo ratings yet

- 1K/2K/4K 2.5V Microwire Serial EEPROM: Features: Package TypesDocument20 pages1K/2K/4K 2.5V Microwire Serial EEPROM: Features: Package TypesJoão PauloNo ratings yet

- 93C66Document12 pages93C66Alex AlvarezNo ratings yet

- 8K/16K 5.0V Microwire Serial EEPROM: FeaturesDocument12 pages8K/16K 5.0V Microwire Serial EEPROM: FeaturesStephensonNo ratings yet

- 8K/16K 5.0V Microwire Serial EEPROM: Features: Package TypesDocument20 pages8K/16K 5.0V Microwire Serial EEPROM: Features: Package Typesfarhood ranjbarkhanghahNo ratings yet

- 1K-16K Microwire Compatible Serial Eeproms: Features: DescriptionDocument38 pages1K-16K Microwire Compatible Serial Eeproms: Features: DescriptionStuxnetNo ratings yet

- Bus Serial EEPROMDocument12 pagesBus Serial EEPROMMatiasNo ratings yet

- 93C86Document20 pages93C86cgmannerheimNo ratings yet

- 2K Microwire Compatible Serial EEPROM: 93AA56A/B/C, 93LC56A/B/C, 93C56A/B/CDocument30 pages2K Microwire Compatible Serial EEPROM: 93AA56A/B/C, 93LC56A/B/C, 93C56A/B/CAndrea MartinezNo ratings yet

- 93C66 PDFDocument22 pages93C66 PDFCristian Esteban TamashiroNo ratings yet

- 93LC46ADocument34 pages93LC46AmordiscoverdeNo ratings yet

- 24AA00/24LC00/24C00: 128 Bit I C™ Bus Serial EEPROMDocument12 pages24AA00/24LC00/24C00: 128 Bit I C™ Bus Serial EEPROMmacepaNo ratings yet

- 24C320-EP MicrochipTechnologyDocument12 pages24C320-EP MicrochipTechnologyMateus CorrêaNo ratings yet

- 24AA64/24LC64/24FC64: 64K I C™ Serial EEPROMDocument45 pages24AA64/24LC64/24FC64: 64K I C™ Serial EEPROMJuan Carlos CrespoNo ratings yet

- Macronix Nbit Memory Family: 64M-Bit (X 1) Cmos Serial Elite Flash MemoryDocument24 pagesMacronix Nbit Memory Family: 64M-Bit (X 1) Cmos Serial Elite Flash MemoryJavierNo ratings yet

- 25AA640/25LC640/25C640: 64K Spi Bus Serial EEPROMDocument11 pages25AA640/25LC640/25C640: 64K Spi Bus Serial EEPROMAndrey OliveiraNo ratings yet

- Ic PDFDocument36 pagesIc PDFdharamNo ratings yet

- 93LC46Document30 pages93LC46DCTRONICSNo ratings yet

- 42 45S32200LDocument59 pages42 45S32200LNelson Pimiento SerranoNo ratings yet

- En25qa64a EonDocument68 pagesEn25qa64a Eongbjhasd344No ratings yet

- 25AA640/25LC640: 64K Spi Bus Serial EEPROMDocument12 pages25AA640/25LC640: 64K Spi Bus Serial EEPROMinsomnium86No ratings yet

- MCP79410/MCP79411/MCP79412: I C™ Real-Time Clock/Calendar With EEPROM, SRAM, Unique ID and Battery SwitchoverDocument38 pagesMCP79410/MCP79411/MCP79412: I C™ Real-Time Clock/Calendar With EEPROM, SRAM, Unique ID and Battery SwitchoverDaniel CortelettiNo ratings yet

- AK93C45A / 55A / 65A / 75A: 1K / 2K / 4K / 8kbit Serial CMOS EEPROMDocument14 pagesAK93C45A / 55A / 65A / 75A: 1K / 2K / 4K / 8kbit Serial CMOS EEPROMmansoorhayatNo ratings yet

- EEPROM 24LC256 - Microchip PDFDocument28 pagesEEPROM 24LC256 - Microchip PDFValdir DerlannNo ratings yet

- 24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMDocument34 pages24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMKhalid BenaribaNo ratings yet

- I2c EEPROM 24xx256 DsDocument28 pagesI2c EEPROM 24xx256 DsRizwan AmirNo ratings yet

- IS42S32800D IS45S32800D: 8Mx32 256Mb Synchronous DramDocument60 pagesIS42S32800D IS45S32800D: 8Mx32 256Mb Synchronous Dramcruz yorisNo ratings yet

- 24 LC 256Document38 pages24 LC 256johnNo ratings yet

- MX25L8005 MxicDocument41 pagesMX25L8005 Mxicdanehcan graNo ratings yet

- Datasheet PDFDocument26 pagesDatasheet PDFNicoli LourençoNo ratings yet

- Infineon S27KL0643 S27KS0643 3 0 V 1 8 V 64 MB 8 - 3107371Document58 pagesInfineon S27KL0643 S27KS0643 3 0 V 1 8 V 64 MB 8 - 3107371ManunoghiNo ratings yet

- Three-Wire Serial EEPROM: 1. FeaturesDocument17 pagesThree-Wire Serial EEPROM: 1. FeatureskppsadiNo ratings yet

- Datashet Etron TechDocument54 pagesDatashet Etron TechAndres OrjuelaNo ratings yet

- 24CW16X 24CW32X 24CW64X 24CW128X Data Sheet 200057-1397638Document51 pages24CW16X 24CW32X 24CW64X 24CW128X Data Sheet 200057-1397638ManunoghiNo ratings yet

- 24aa08 - 24lc08 Eeprom PDFDocument40 pages24aa08 - 24lc08 Eeprom PDFEdgar DauzonNo ratings yet

- 24LC04B PDFDocument22 pages24LC04B PDFEddy RosarioNo ratings yet

- 24LC08 PDFDocument30 pages24LC08 PDFJaime BarrancoNo ratings yet

- M24256-BW M24256-BR M24256-BF M24256-DR M24256-DF: 256-Kbit Serial I C Bus EEPROMDocument47 pagesM24256-BW M24256-BR M24256-BF M24256-DR M24256-DF: 256-Kbit Serial I C Bus EEPROMNguyễn Thế MạnhNo ratings yet

- IS42S32800G IS45S32800G: 8Mx32 256Mb Synchronous DramDocument58 pagesIS42S32800G IS45S32800G: 8Mx32 256Mb Synchronous Dramcruz yorisNo ratings yet

- 24AA64/24LC64/24FC64: 64K I C Serial EEPROMDocument28 pages24AA64/24LC64/24FC64: 64K I C Serial EEPROMJuan Luis Pineda GonzálezNo ratings yet

- 24AA16/24LC16B: 16K I C Serial EEPROMDocument25 pages24AA16/24LC16B: 16K I C Serial EEPROMDaniel VásquezNo ratings yet

- AT93CXXDocument15 pagesAT93CXXcallkalaiNo ratings yet

- 24AA08/24LC08B: 8KI C Serial EEPROMDocument30 pages24AA08/24LC08B: 8KI C Serial EEPROMjoseNo ratings yet

- Xmc-Xm25qh64ahig C328461Document75 pagesXmc-Xm25qh64ahig C328461c4rl0slinuxNo ratings yet

- EN25Q32C 32 Megabit Serial Flash Memory With 4kbyte Uniform SectorDocument62 pagesEN25Q32C 32 Megabit Serial Flash Memory With 4kbyte Uniform Sectoramir baroughNo ratings yet

- 24lc512 DatasheetDocument27 pages24lc512 DatasheetLeonardo QuevedoNo ratings yet

- M24C64-W M24C64-R M24C64-F M24C64-DF: 64-Kbit Serial I C Bus EEPROMDocument54 pagesM24C64-W M24C64-R M24C64-F M24C64-DF: 64-Kbit Serial I C Bus EEPROMSafi SapidoNo ratings yet

- 25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118Document39 pages25AA640A 25LC640A 64K SPI Bus Serial EEPROM 200018-2449118ManunoghiNo ratings yet

- Doc0172 PDFDocument20 pagesDoc0172 PDFnarayanNo ratings yet

- 4M (512K 8/256K 16) BIT: Flash MemoryDocument55 pages4M (512K 8/256K 16) BIT: Flash MemorytecrgoNo ratings yet

- EN25Q32A 32 Megabit Serial Flash Memory With 4kbyte Uniform SectorDocument52 pagesEN25Q32A 32 Megabit Serial Flash Memory With 4kbyte Uniform SectorDavid Zuccarini BarroetaNo ratings yet

- Microprocessor Architectures and Systems: RISC, CISC and DSPFrom EverandMicroprocessor Architectures and Systems: RISC, CISC and DSPRating: 4 out of 5 stars4/5 (1)

- Microprocessor Architectures: RISC, CISC and DSPFrom EverandMicroprocessor Architectures: RISC, CISC and DSPRating: 5 out of 5 stars5/5 (1)

- Nonvolatile Memory 8-Kbit E Prom With C Bus Interface SDA 2586-5Document12 pagesNonvolatile Memory 8-Kbit E Prom With C Bus Interface SDA 2586-5insomnium86No ratings yet

- FM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- HT93LC56: 2K 3-Wire CMOS Serial EEPROMDocument10 pagesHT93LC56: 2K 3-Wire CMOS Serial EEPROMinsomnium86No ratings yet

- NM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- NM93CS66 (MICROWIRE™ Bus Interface) 4096-Bit Serial EEPROM With Data Protect and Sequential ReadDocument16 pagesNM93CS66 (MICROWIRE™ Bus Interface) 4096-Bit Serial EEPROM With Data Protect and Sequential Readinsomnium86No ratings yet

- NM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- FM93C86A 16K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C86A 16K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- FM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C66 4096-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- HT93LC56: 2K 3-Wire CMOS Serial EEPROMDocument10 pagesHT93LC56: 2K 3-Wire CMOS Serial EEPROMinsomnium86No ratings yet

- 2,048-Bit Serial Electrically Erasable PROM: BR93LC56 / BR93LC56F / BR93LC56RF / BR93LC56FVDocument12 pages2,048-Bit Serial Electrically Erasable PROM: BR93LC56 / BR93LC56F / BR93LC56RF / BR93LC56FVinsomnium86No ratings yet

- 93c56 DatasheetDocument15 pages93c56 DatasheetsakerhetfreakNo ratings yet

- SPI Serial Eeproms: FeaturesDocument16 pagesSPI Serial Eeproms: FeaturesBachi403No ratings yet

- 2-Wire Serial Eeprom: FeaturesDocument2 pages2-Wire Serial Eeprom: Featuresinsomnium86No ratings yet

- 2-Wire Serial Eeproms: FeaturesDocument16 pages2-Wire Serial Eeproms: FeaturesTuan Pham AnhNo ratings yet

- 25AA640/25LC640: 64K Spi Bus Serial EEPROMDocument12 pages25AA640/25LC640: 64K Spi Bus Serial EEPROMinsomnium86No ratings yet

- 32K 2.5V I C Serial EEPROM: Features Package TypesDocument12 pages32K 2.5V I C Serial EEPROM: Features Package Typesinsomnium86No ratings yet

- 32K 5.0V I C Serial EEPROM: Features Package TypesDocument12 pages32K 5.0V I C Serial EEPROM: Features Package Typesinsomnium86No ratings yet

- 4,096-Bit Serial Electrically Erasable PROM: BR93LC66 / BR93LC66F / BR93LC66RF / BR93LC66FVDocument12 pages4,096-Bit Serial Electrically Erasable PROM: BR93LC66 / BR93LC66F / BR93LC66RF / BR93LC66FVinsomnium86No ratings yet

- Interfacing The X24C44-45Document4 pagesInterfacing The X24C44-45insomnium86No ratings yet

- 25AA080/25LC080/25C080: 8K Spi Bus Serial EEPROMDocument16 pages25AA080/25LC080/25C080: 8K Spi Bus Serial EEPROMinsomnium86No ratings yet

- Application Note An-00100: RF 101 Information For The RF ChallengedDocument5 pagesApplication Note An-00100: RF 101 Information For The RF Challengedinsomnium86No ratings yet

- Application Note An-00160: Considerations For Sending Data With The HP SeriesDocument6 pagesApplication Note An-00160: Considerations For Sending Data With The HP Seriesinsomnium86No ratings yet

- FM Tranciever AppsDocument7 pagesFM Tranciever Appsinsomnium86No ratings yet

- FM Tranceiver DataDocument9 pagesFM Tranceiver Datainsomnium86No ratings yet

- Application Note An-00500: Antennas: Design, Application, PerformanceDocument7 pagesApplication Note An-00500: Antennas: Design, Application, PerformanceAnonymous 0qYv7WpgNo ratings yet

- FMT M - Fmtx1-Xxxx: Ransmitter OdulesDocument6 pagesFMT M - Fmtx1-Xxxx: Ransmitter Odulesinsomnium86No ratings yet

- Product Technical Data: 418Mhz Am Miniature Transmitter Module (Micro TX) Nv08JDocument4 pagesProduct Technical Data: 418Mhz Am Miniature Transmitter Module (Micro TX) Nv08Jinsomnium86No ratings yet

- Exceptions: Dr. E. Papanasam Ap-Iii SocDocument16 pagesExceptions: Dr. E. Papanasam Ap-Iii SocThomas NivethaNo ratings yet

- Compaq AlphaserverDocument30 pagesCompaq AlphaserverTsure11No ratings yet

- Marantz Complete Catalogue 2015/16Document31 pagesMarantz Complete Catalogue 2015/16Klementina MlakarNo ratings yet

- Protection in 400kvDocument18 pagesProtection in 400kvmanoharmanishNo ratings yet

- 02 PDFDocument39 pages02 PDFbond29No ratings yet

- Bollet Point To Lodha LetterDocument3 pagesBollet Point To Lodha Letterchief engineer CommercialNo ratings yet

- Digital Links: Point-to-Point LinksDocument3 pagesDigital Links: Point-to-Point LinksTisha KhatriNo ratings yet

- ABV Full-Line CatalogDocument40 pagesABV Full-Line CatalogJulio ConfortoNo ratings yet

- Fundamentals of Led Lighting: What Are The Benefits, What Are The Limita0onsDocument43 pagesFundamentals of Led Lighting: What Are The Benefits, What Are The Limita0onsAdi IsmantoNo ratings yet

- Transient Stability StudiesDocument12 pagesTransient Stability StudiesAbhijeet Kumar SinghNo ratings yet

- Zenitel - ESC-1 - 1023000000Document4 pagesZenitel - ESC-1 - 1023000000amir11601No ratings yet

- Demand Factor-Diversity Factor-Utilization Factor-Load FactorDocument13 pagesDemand Factor-Diversity Factor-Utilization Factor-Load FactorYousif_Abdalhalim100% (1)

- Topic 10 - AVR IO in C (ISMAIL - FKEUTM 2018)Document93 pagesTopic 10 - AVR IO in C (ISMAIL - FKEUTM 2018)Aya AmirNo ratings yet

- WPS 2Document41 pagesWPS 2Armin PatelNo ratings yet

- MOS T1,.T3 SUPERIM. 110..250vac/dc New: General InformationDocument2 pagesMOS T1,.T3 SUPERIM. 110..250vac/dc New: General InformationJhonny Velasquez PerezNo ratings yet

- Analysis of Series RC Circuit Using MatlabDocument5 pagesAnalysis of Series RC Circuit Using MatlabAbdul MubinNo ratings yet

- ELC4536 Standar 6 Años GarantiaDocument3 pagesELC4536 Standar 6 Años GarantiaDilham BerrioNo ratings yet

- IOT Based Automatic Water Container Filler Using ArduinoDocument6 pagesIOT Based Automatic Water Container Filler Using ArduinoInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Bu00a02b02 60e 4Document84 pagesBu00a02b02 60e 4Marcos AldrovandiNo ratings yet

- Novatek NT96650 PDFDocument35 pagesNovatek NT96650 PDFRenatoNo ratings yet

- AC Circuit 1 (Single-Phase)Document2 pagesAC Circuit 1 (Single-Phase)marlon desaculaNo ratings yet

- Week 16: Electronics System Engineering Flat-Sat For IgosatDocument10 pagesWeek 16: Electronics System Engineering Flat-Sat For IgosatJuan VALVERDENo ratings yet

- Artist Series: 1001RB-II/700RB-II Owner's ManualDocument16 pagesArtist Series: 1001RB-II/700RB-II Owner's ManualmaxNo ratings yet

- Brgy Road Brgy Mangitayag Piddig Ilocos Norte IEPDocument8 pagesBrgy Road Brgy Mangitayag Piddig Ilocos Norte IEPLei GalzoteNo ratings yet

- d301673x012 Modulo de Comunicaciones Serial ControlwaveDocument4 pagesd301673x012 Modulo de Comunicaciones Serial ControlwaveMisael Castillo CamachoNo ratings yet

- On Line Ups 6-10kva User ManualDocument32 pagesOn Line Ups 6-10kva User ManualADY Resources100% (1)

- Logic Circuit & Switching Theory Pre - Final Quiz 1Document14 pagesLogic Circuit & Switching Theory Pre - Final Quiz 1Russel Mendoza100% (1)

- JVS Manual JRP 011Document12 pagesJVS Manual JRP 011Tamilventhan_sNo ratings yet

- D0996 Af en PDFDocument165 pagesD0996 Af en PDFZdravko Josifoski67% (3)

- Ethio Telecom Back GroundDocument15 pagesEthio Telecom Back GroundSeid Takele80% (10)